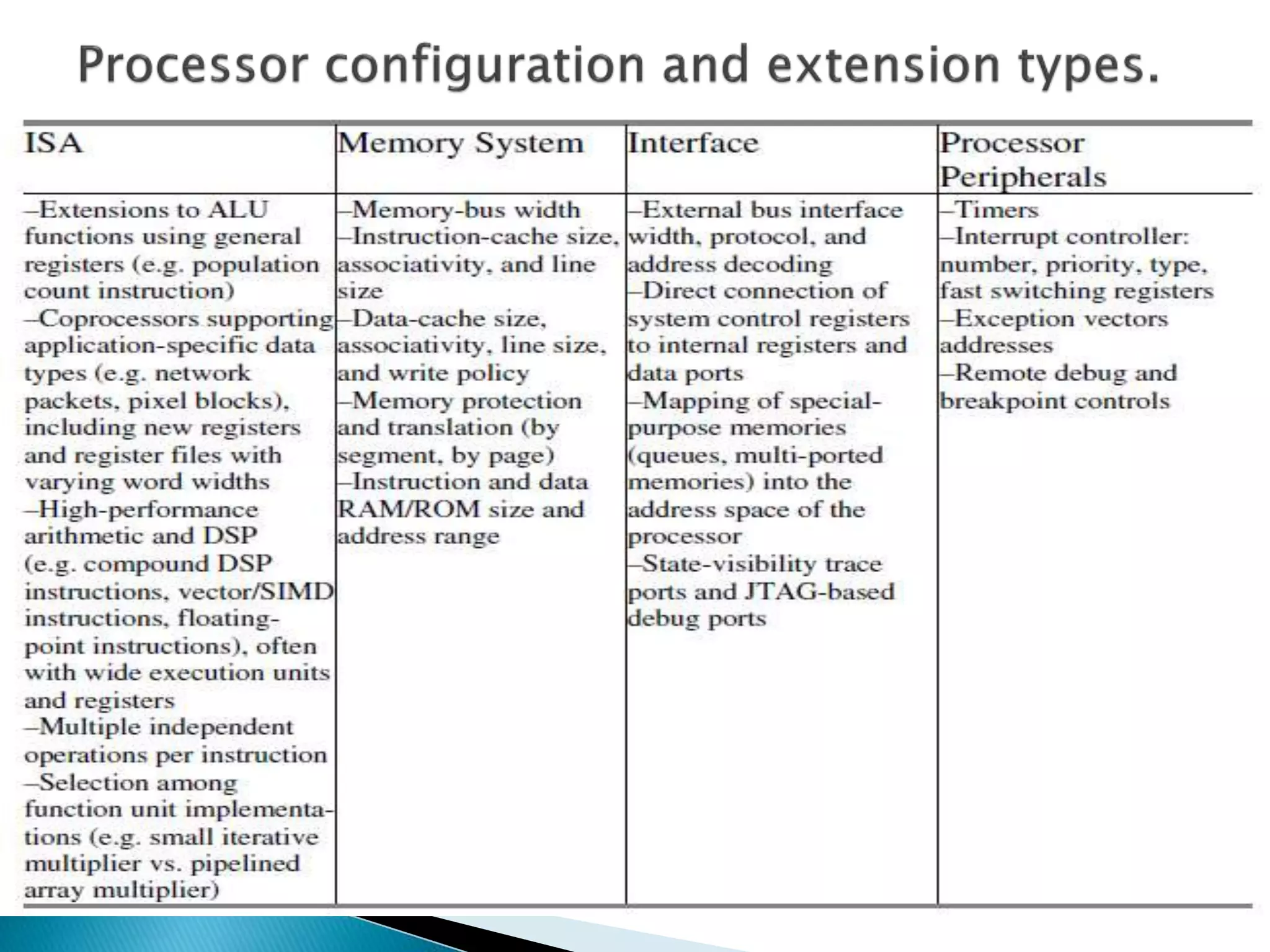

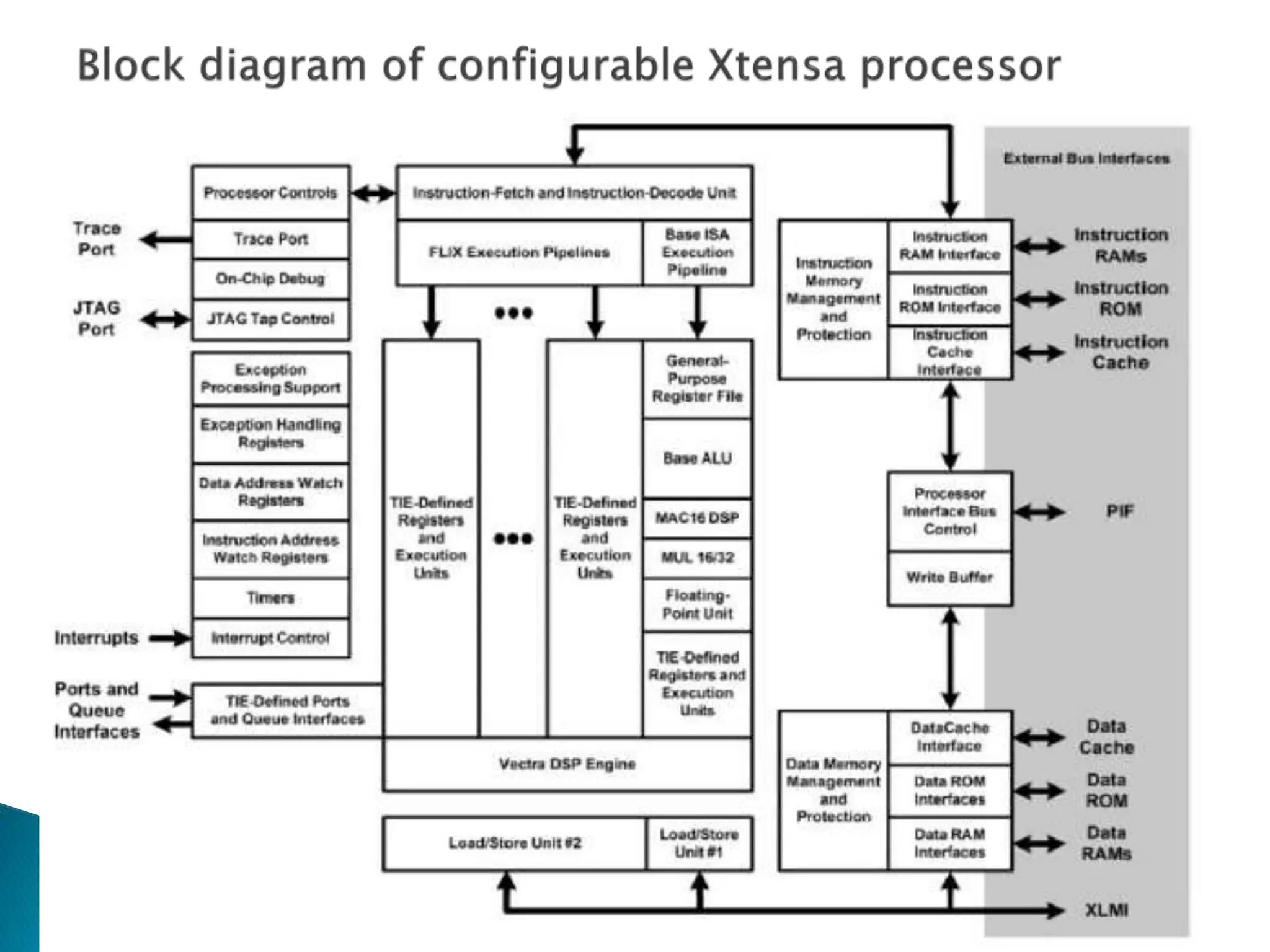

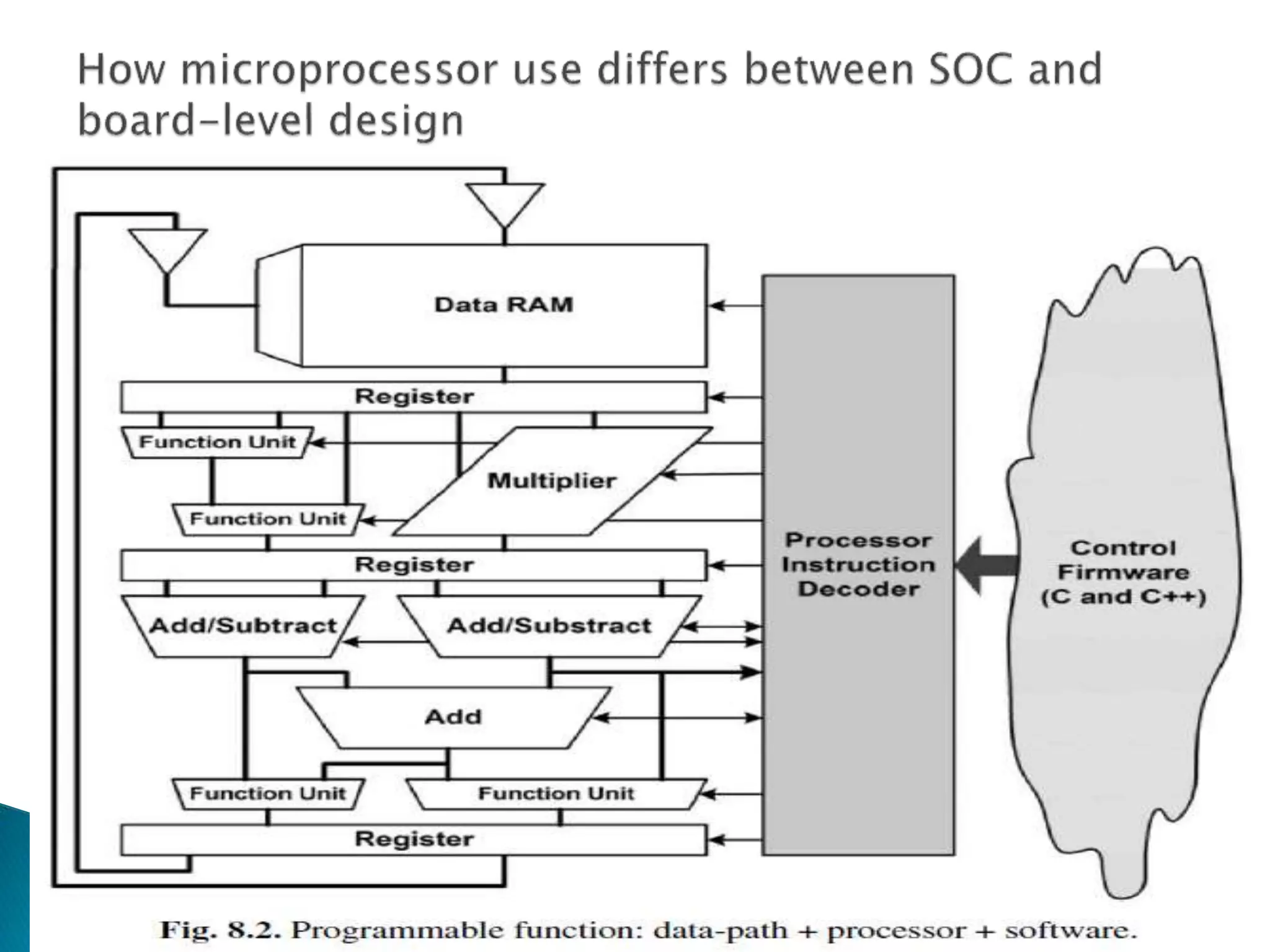

This document discusses customizable processors and processor customization. It describes how customizable processors incorporate task-specific hardware acceleration into the processor's execution pipeline rather than using external accelerators. This improves efficiency by bringing the acceleration hardware into close contact with the processor's registers and interfaces. The document also discusses the benefits of using microprocessor cores in system-on-chip designs, such as improving flexibility so new systems don't require new chip designs and simplifying the design process.