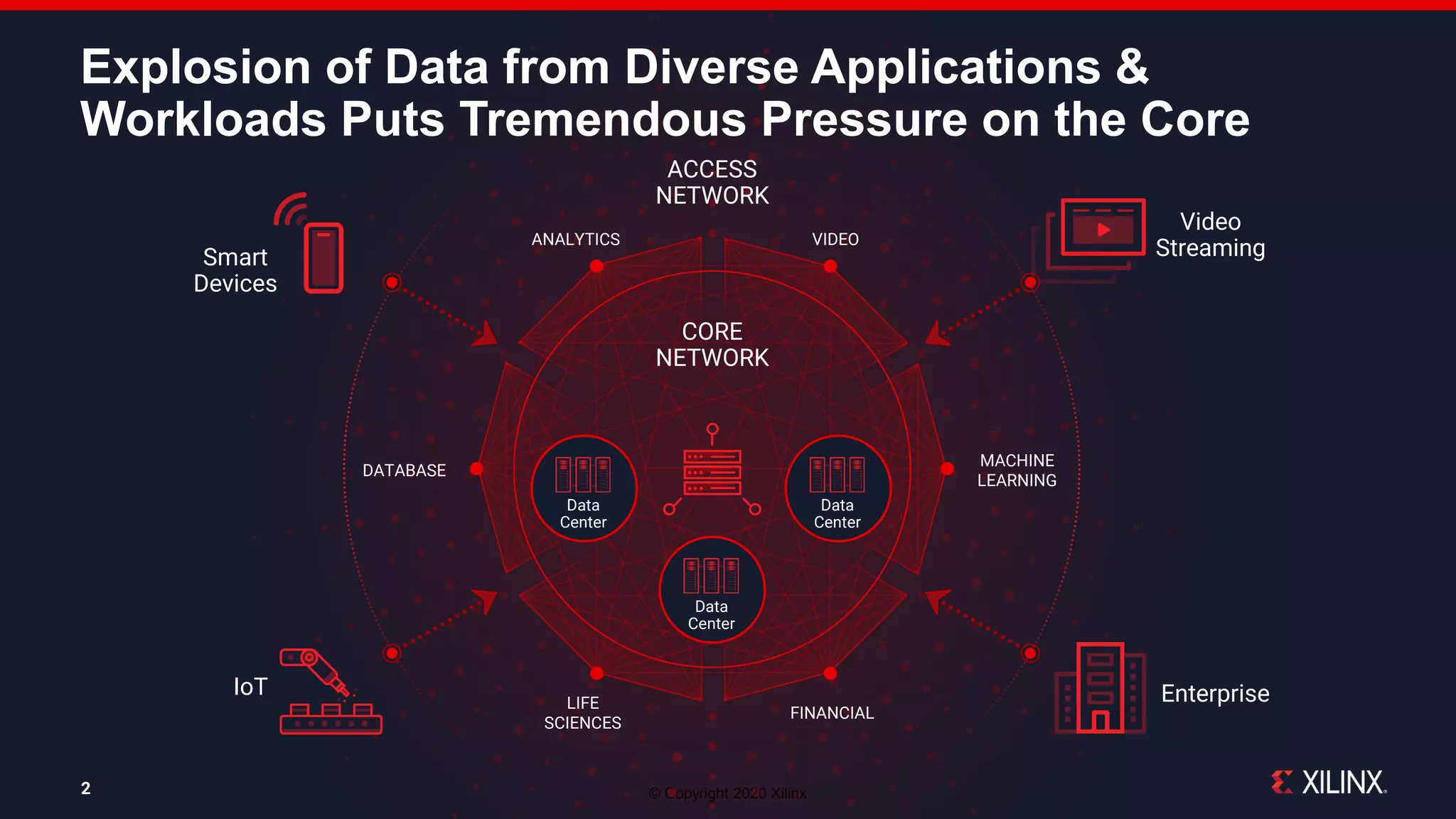

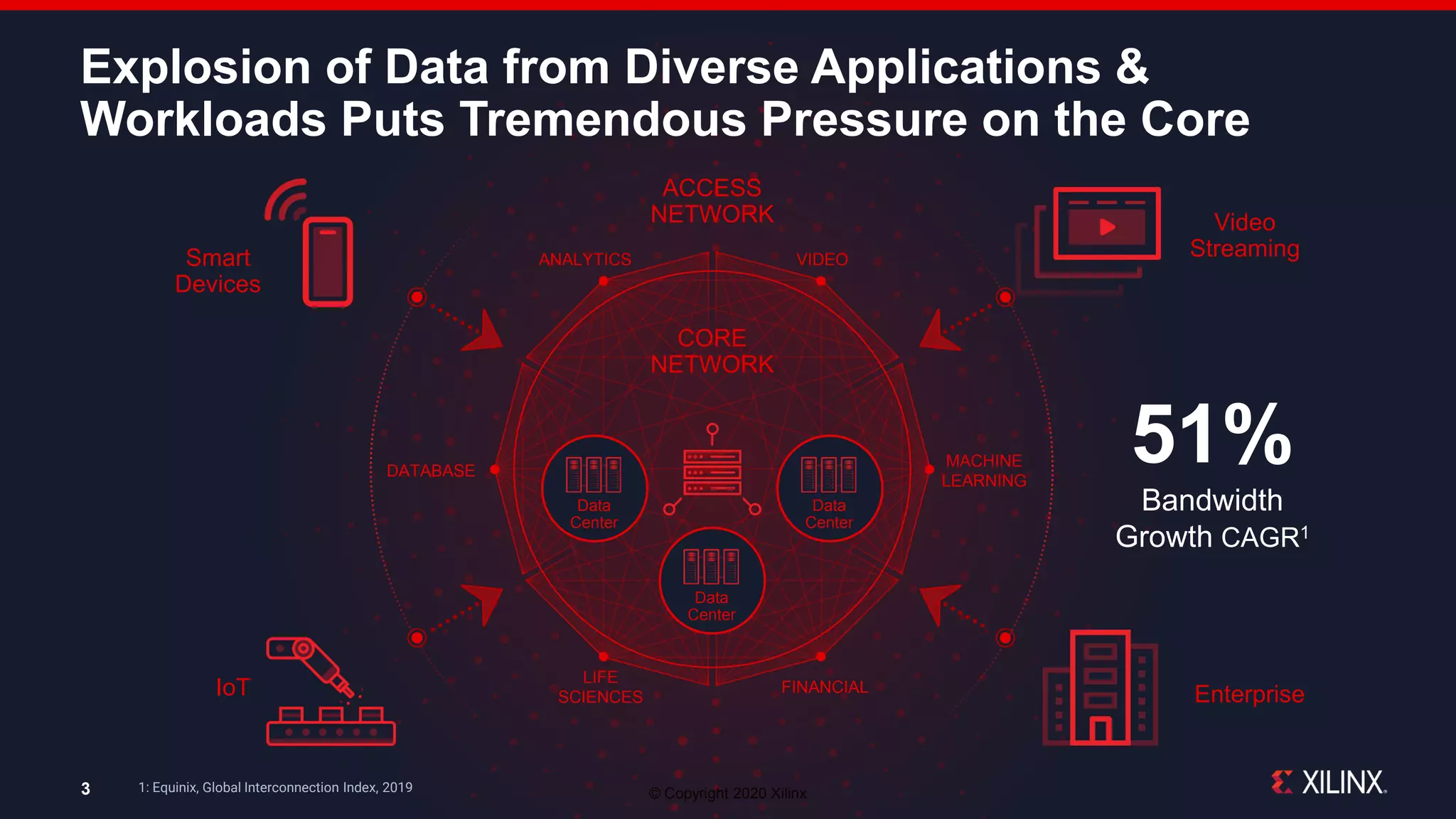

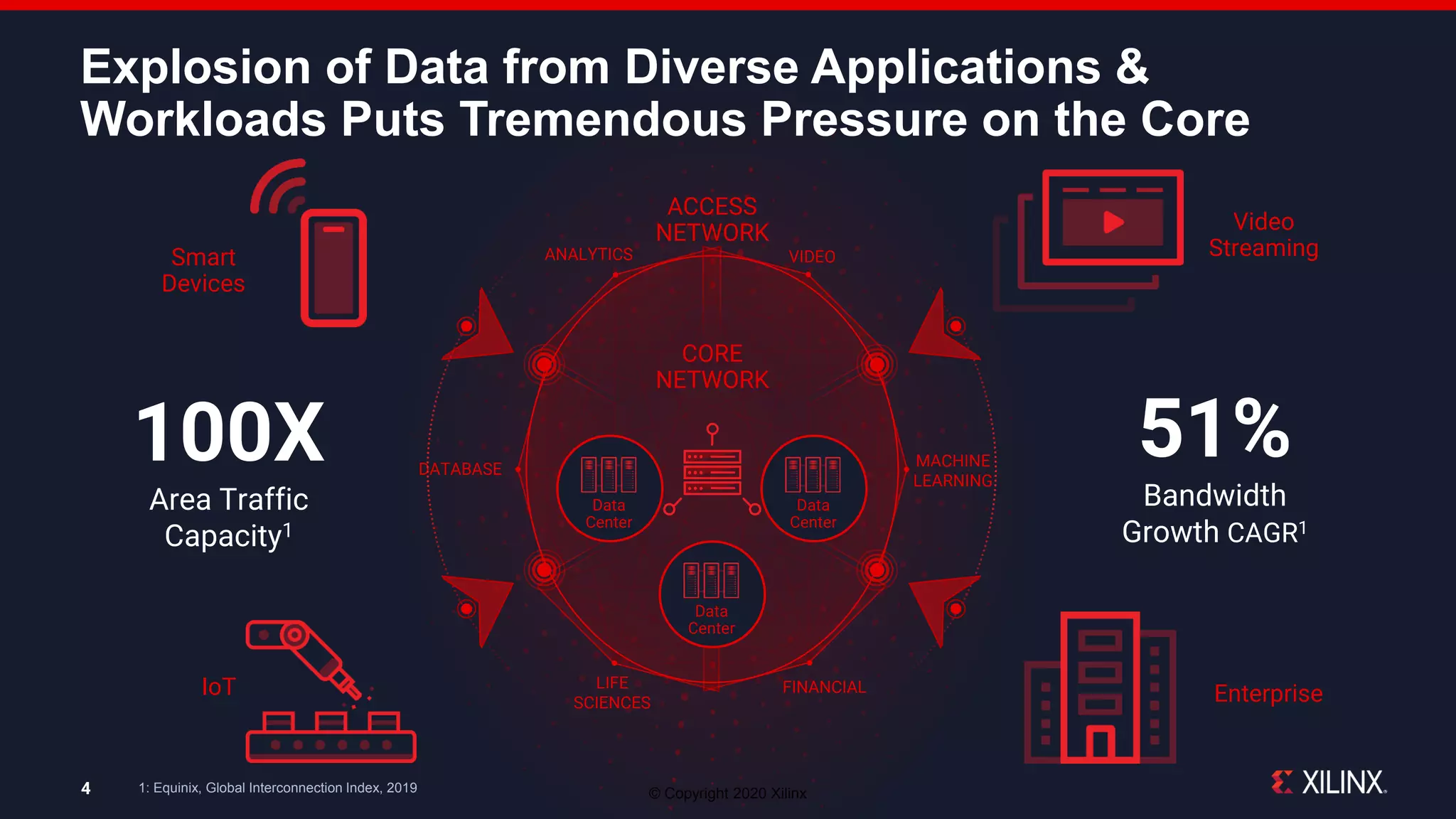

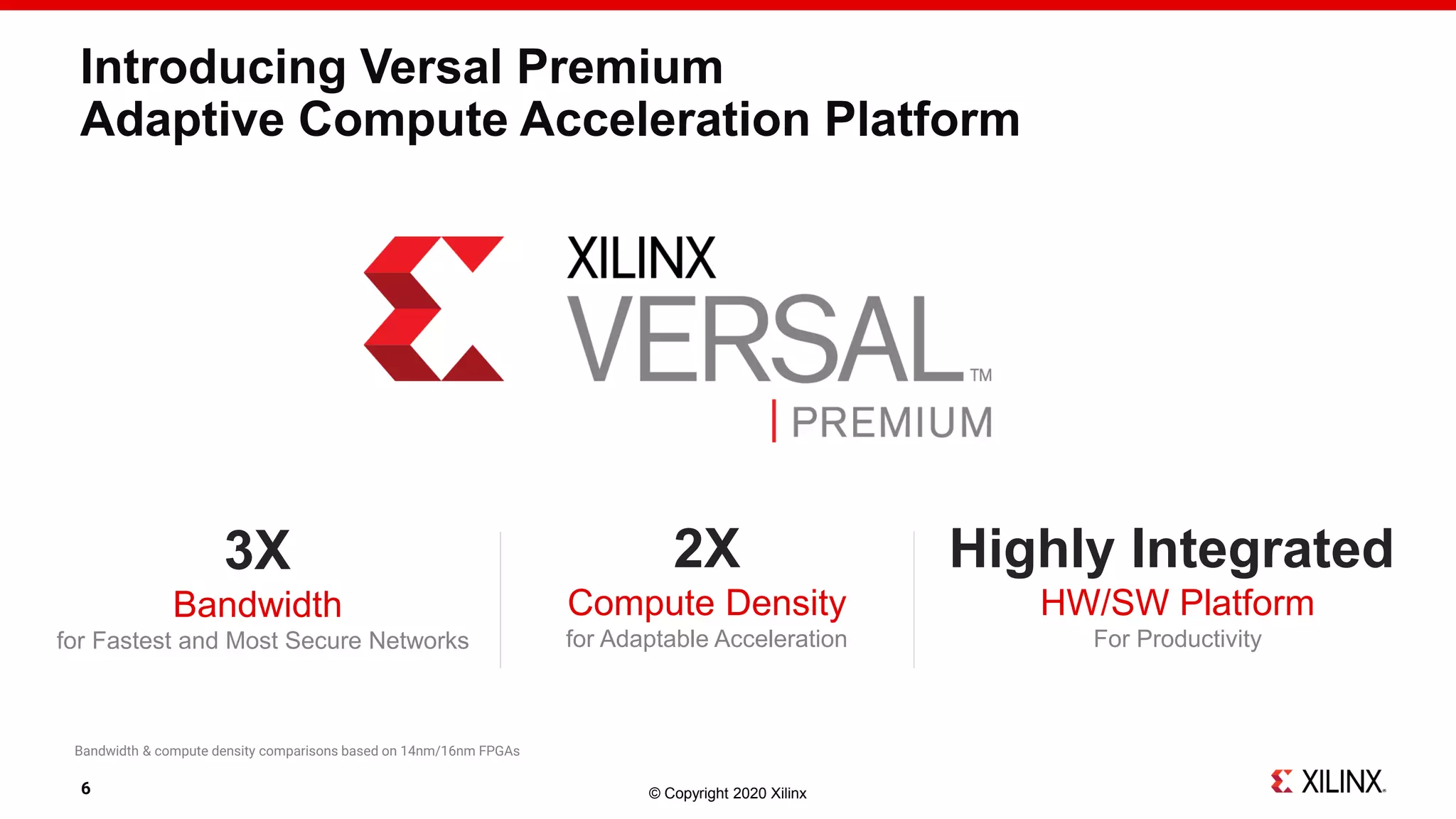

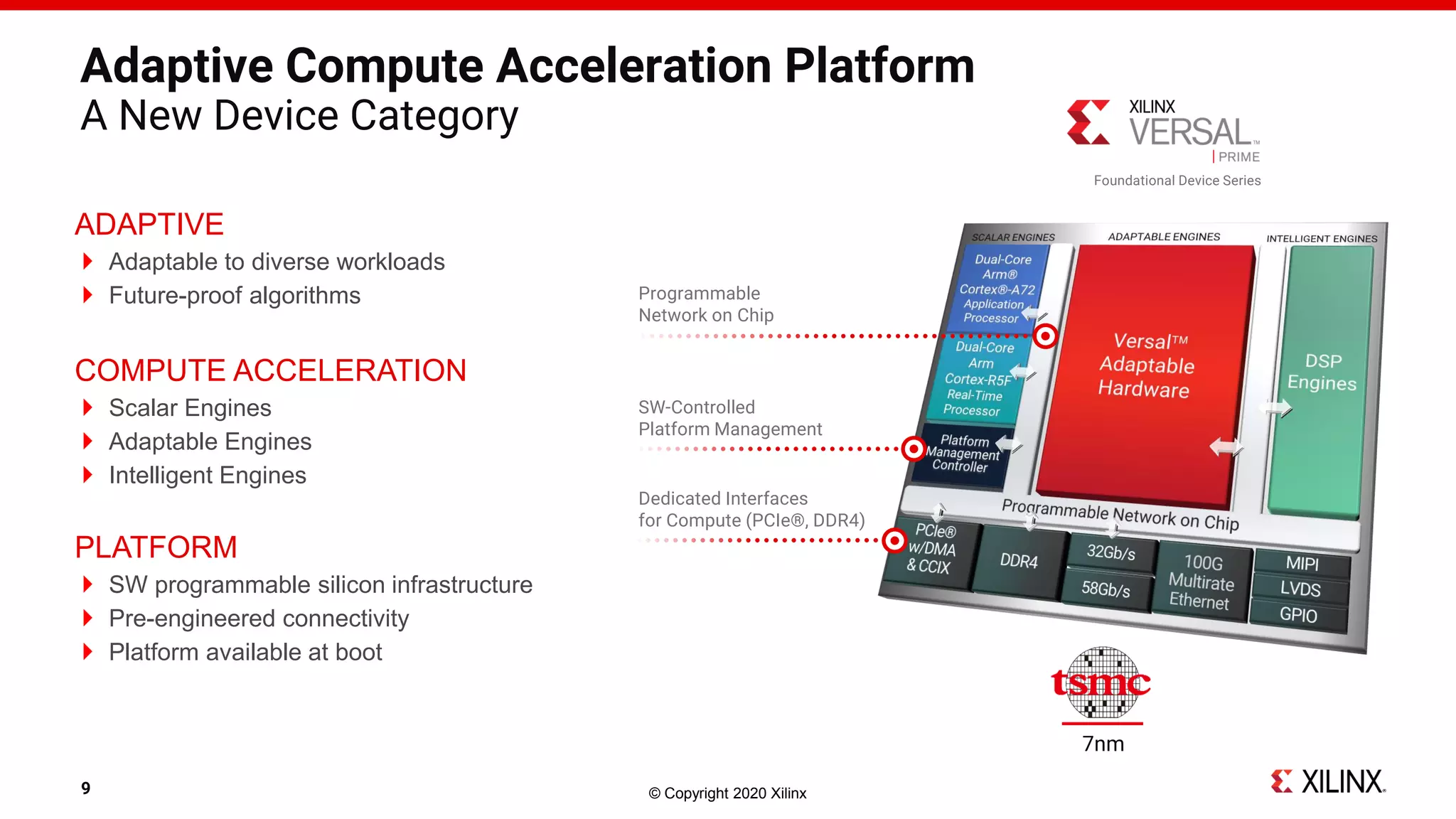

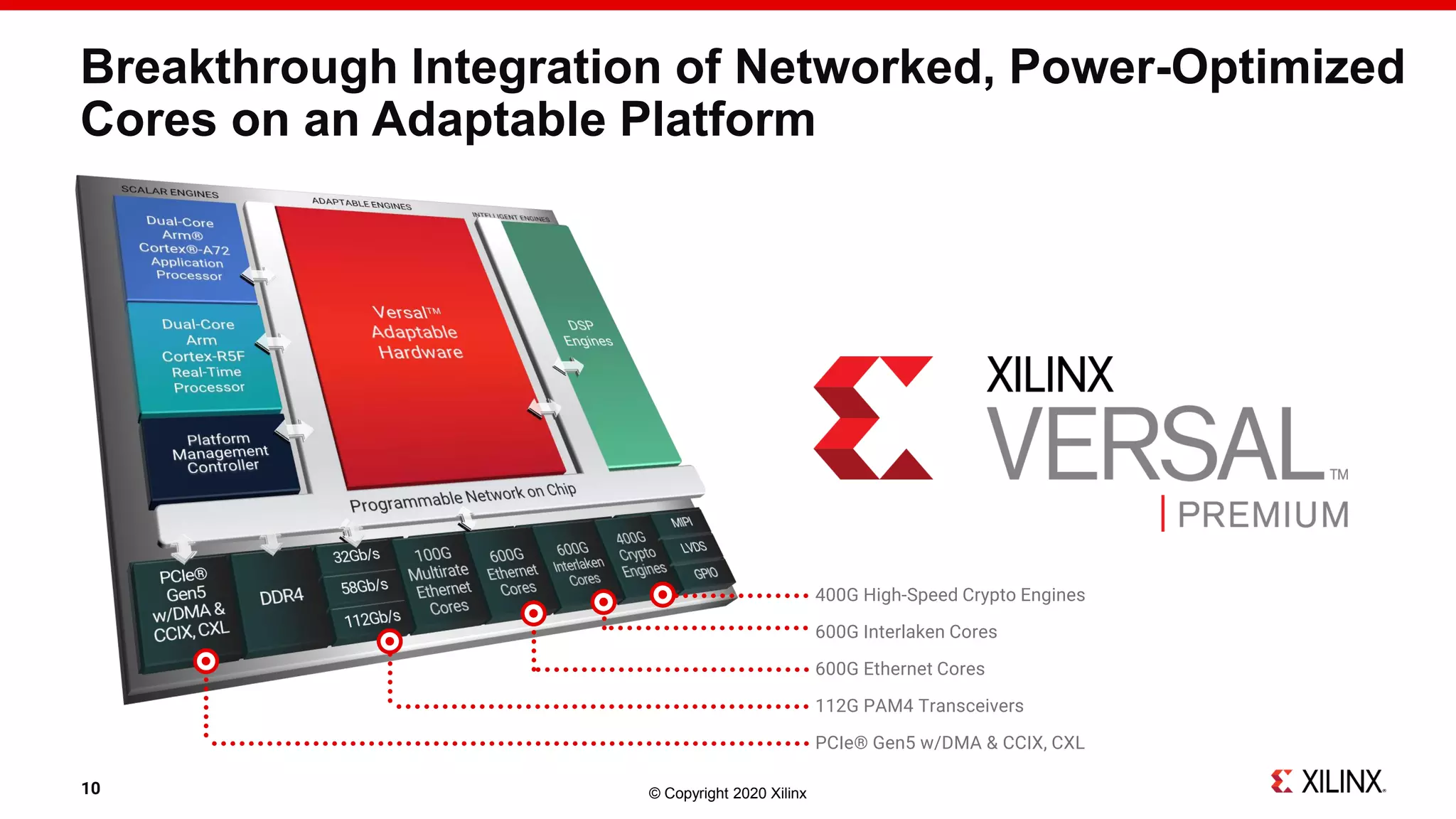

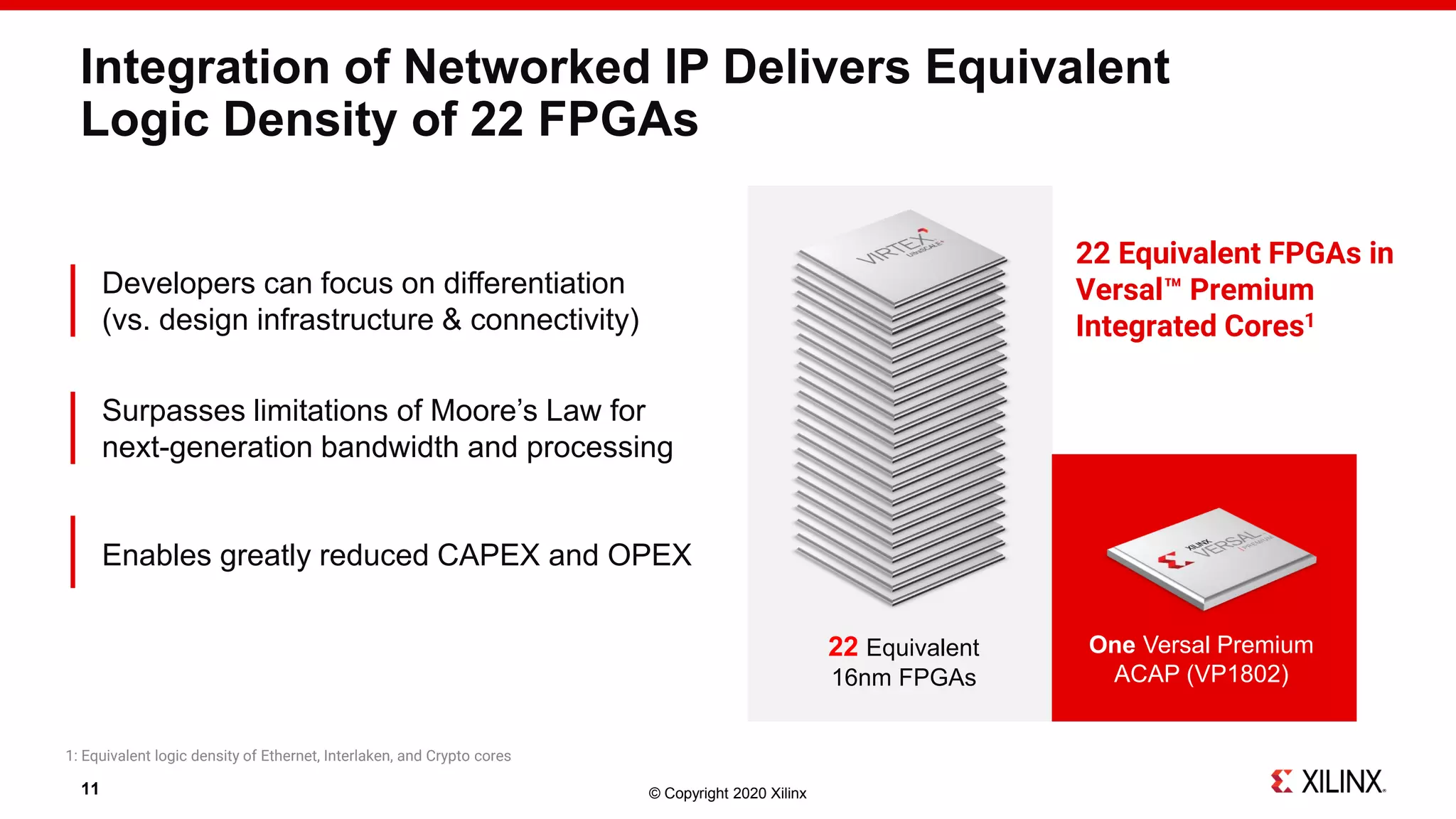

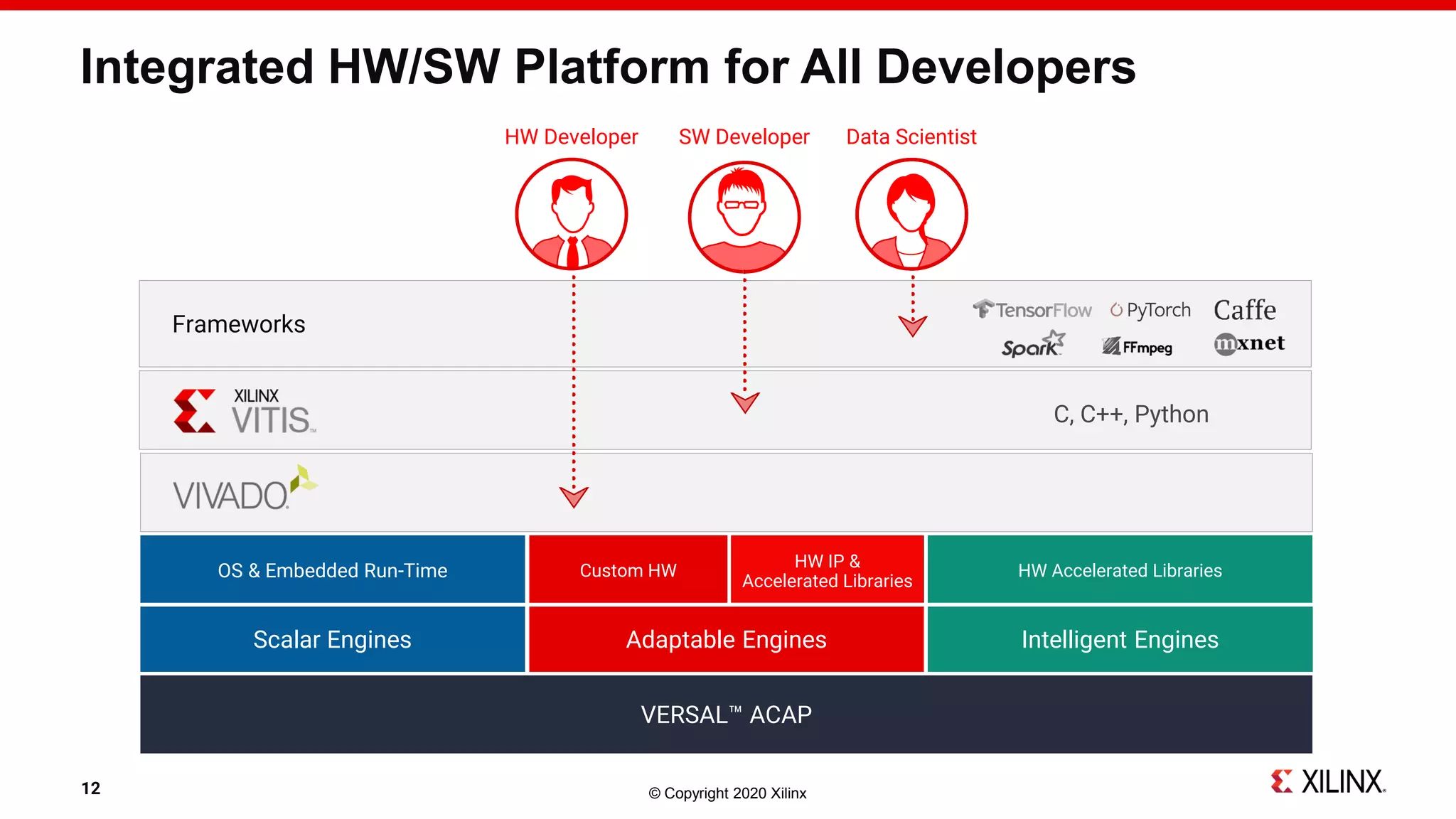

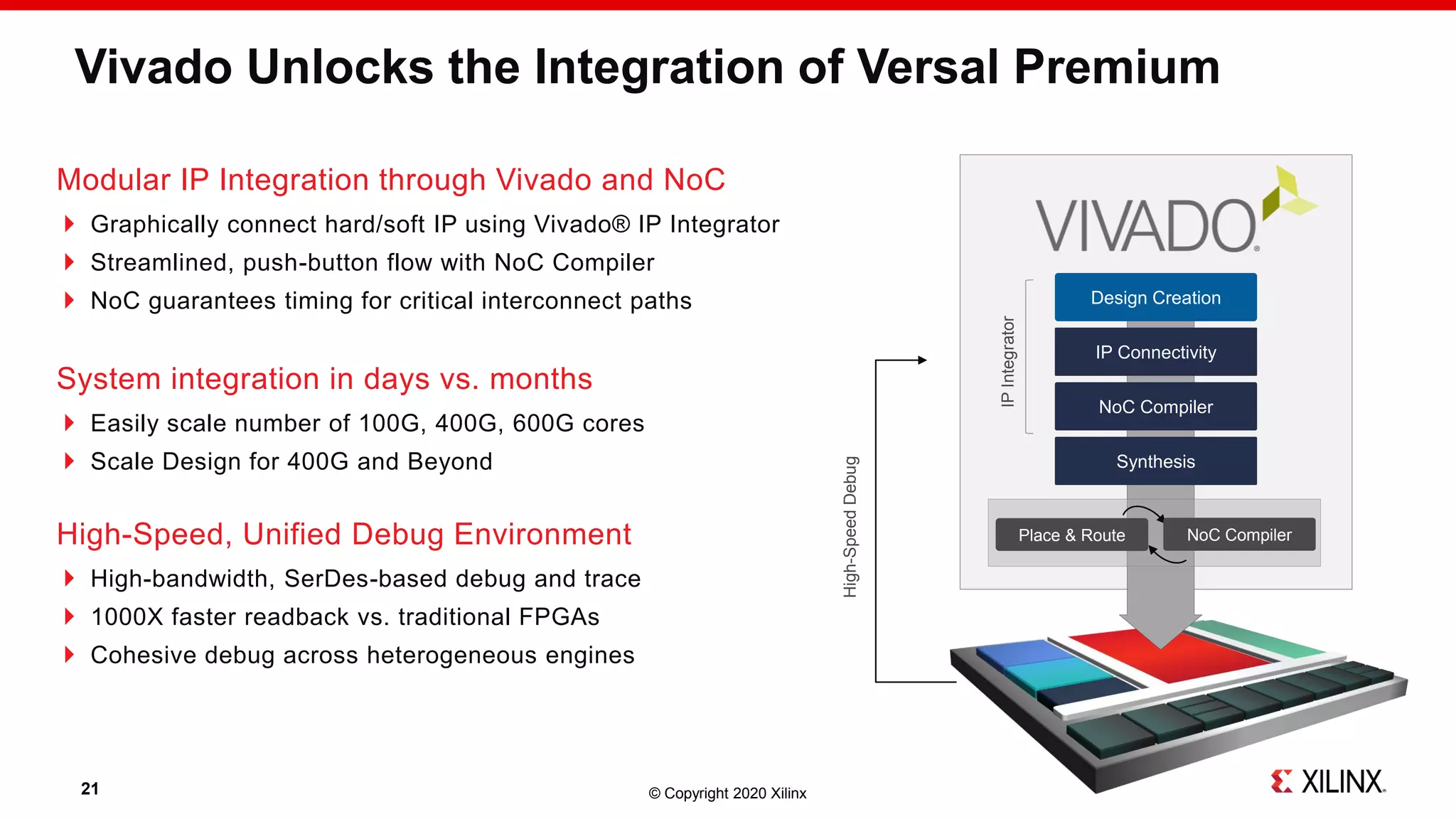

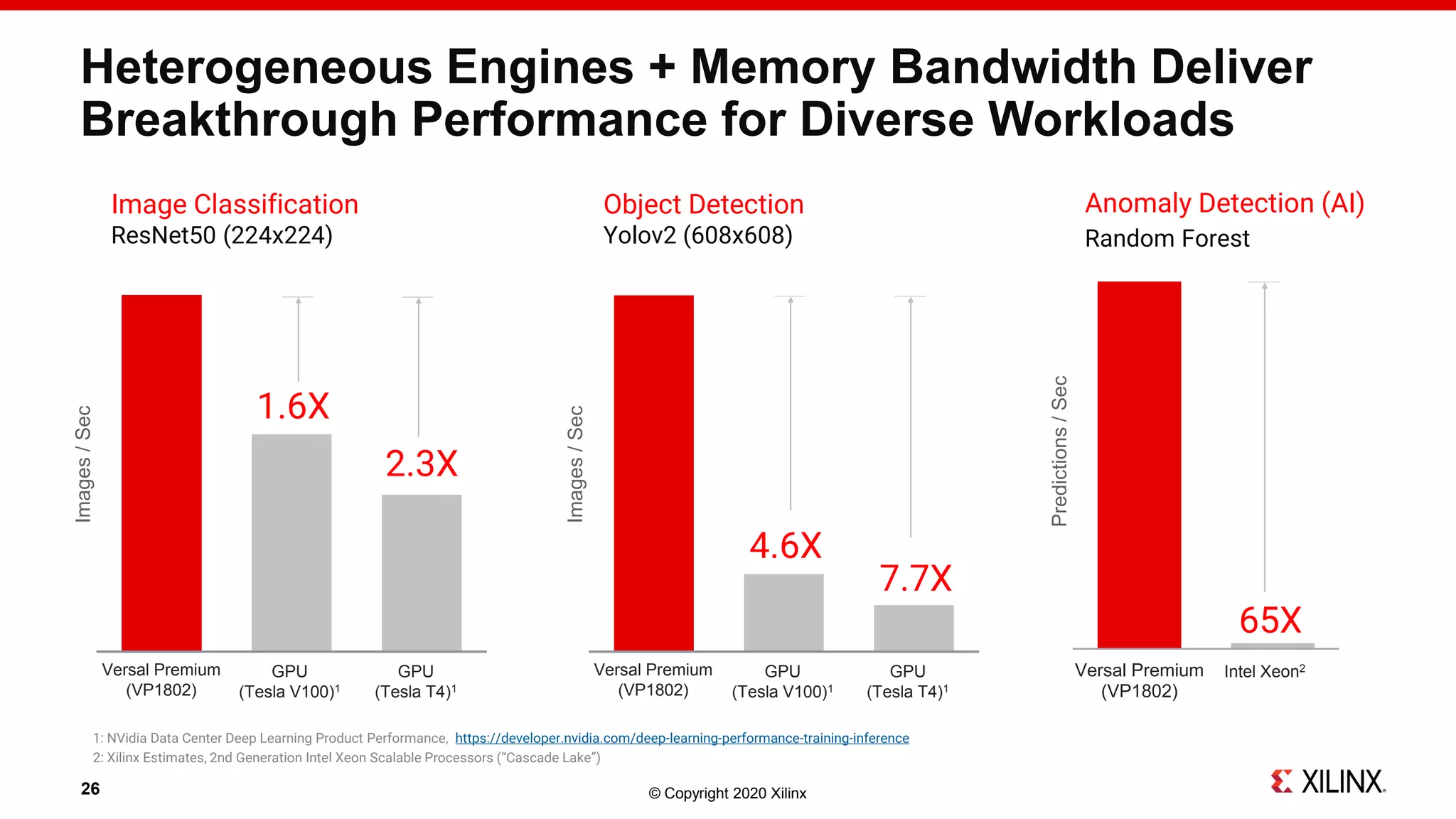

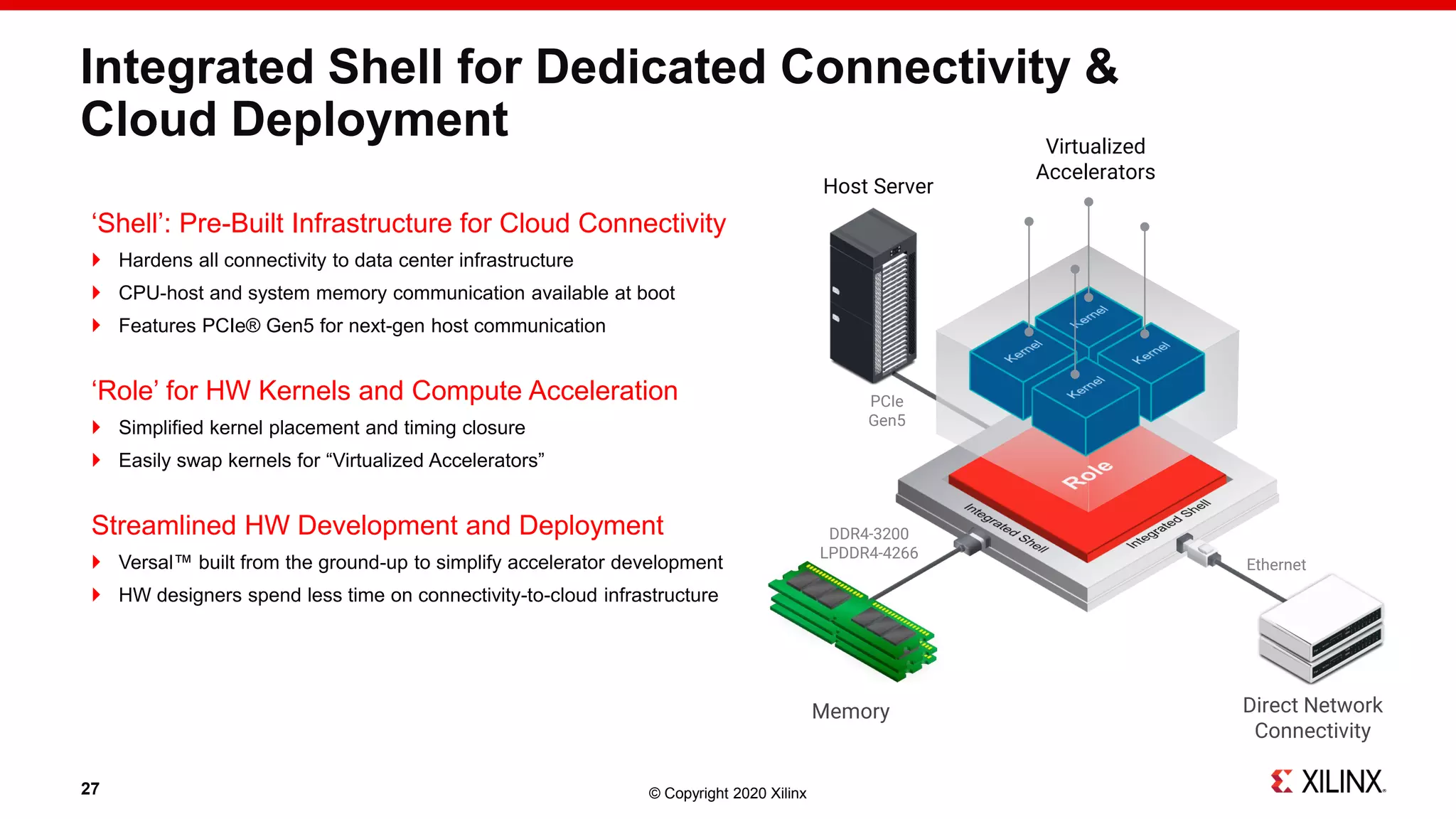

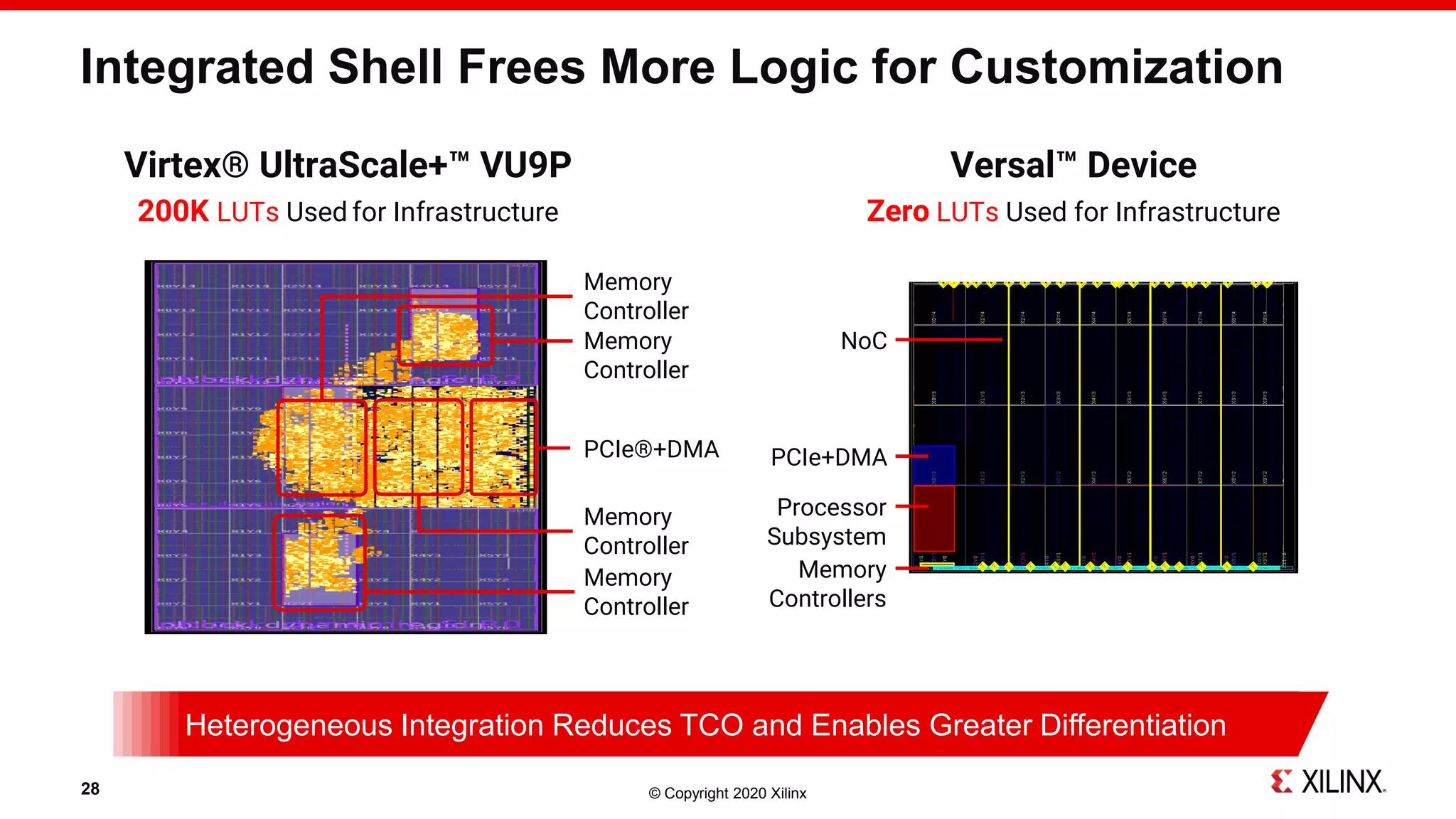

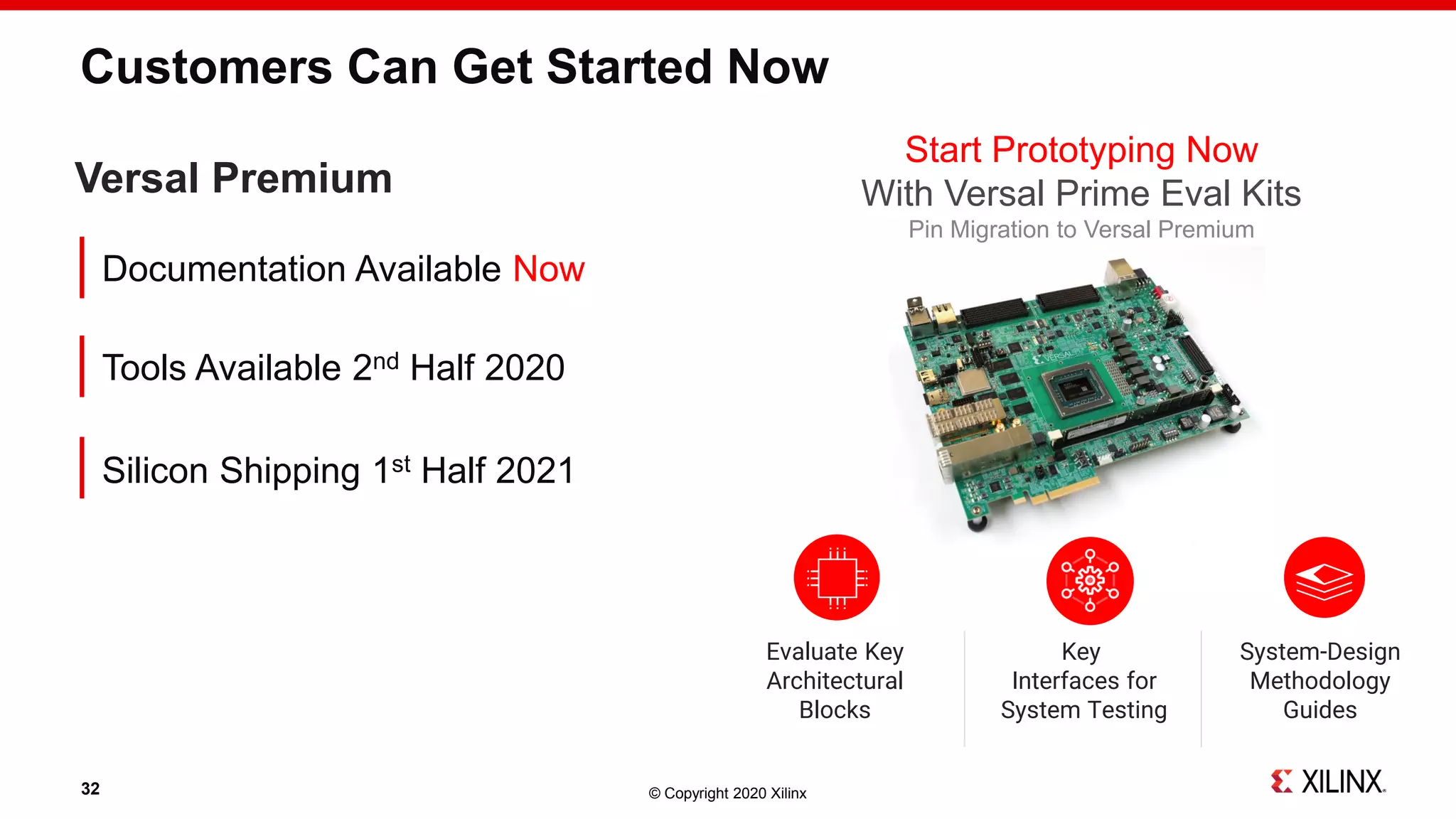

Xilinx has announced the Versal Premium Adaptive Compute Acceleration Platform (ACAP), designed to address the increasing demands of diverse data workloads by offering 3x bandwidth and 2x compute density. This platform integrates high-speed, power-optimized cores, enabling significant improvements in network performance and flexibility for various applications. The solution aims to reduce overall costs and enhance productivity for developers through its unified hardware and software framework.