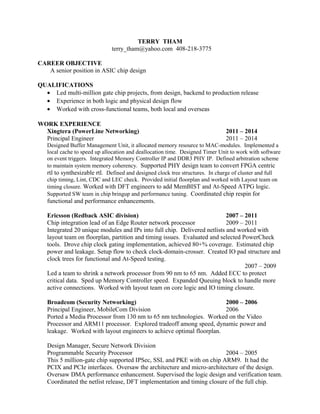

Terry Tham Resume

- 1. TERRY THAM terry_tham@yahoo.com 408-218-3775 CAREER OBJECTIVE A senior position in ASIC chip design QUALIFICATIONS • Led multi-million gate chip projects, from design, backend to production release • Experience in both logic and physical design flow • Worked with cross-functional teams, both local and overseas WORK EXPERIENCE Xingtera (PowerLine Networking) 2011 – 2014 Principal Engineer 2011 – 2014 Designed Buffer Management Unit, it allocated memory resource to MAC-modules. Implemented a local cache to speed up allocation and deallocation time. Designed Timer Unit to work with software on event triggers. Integrated Memory Controller IP and DDR3 PHY IP. Defined arbitration scheme to maintain system memory coherency. Supported PHY design team to convert FPGA centric rtl to synthesizable rtl. Defined and designed clock tree structures. In charge of cluster and full chip timing, Lint, CDC and LEC check. Provided initial floorplan and worked with Layout team on timing closure. Worked with DFT engineers to add MemBIST and At-Speed ATPG logic. Supported SW team in chip bringup and performance tuning. Coordinated chip respin for functional and performance enhancements. Ericsson (Redback ASIC division) 2007 – 2011 Chip integration lead of an Edge Router network processor 2009 – 2011 Integrated 20 unique modules and IPs into full chip. Delivered netlists and worked with layout team on floorplan, partition and timing issues. Evaluated and selected PowerCheck tools. Drove chip clock gating implementation, achieved 80+% coverage. Estimated chip power and leakage. Setup flow to check clock-domain-crosser. Created IO pad structure and clock trees for functional and At-Speed testing. 2007 – 2009 Led a team to shrink a network processor from 90 nm to 65 nm. Added ECC to protect critical data. Sped up Memory Controller speed. Expanded Queuing block to handle more active connections. Worked with layout team on core logic and IO timing closure. Broadcom (Security Networking) 2000 – 2006 Principal Engineer, MobileCom Division 2006 Ported a Media Processor from 130 nm to 65 nm technologies. Worked on the Video Processor and ARM11 processor. Explored tradeoff among speed, dynamic power and leakage. Worked with layout engineers to achieve optimal floorplan. Design Manager, Secure Network Division Programmable Security Processor 2004 – 2005 This 5 million-gate chip supported IPSec, SSL and PKE with on chip ARM9. It had the PCIX and PCIe interfaces. Oversaw the architecture and micro-architecture of the design. Oversaw DMA performance enhancement. Supervised the logic design and verification team. Coordinated the netlist release, DFT implementation and timing closure of the full chip.

- 2. Security IPs 2003 – 2004 Delivered Security IPs to other groups for integration. 4.8 Gbps IPSec processor 2001 – 2002 Managed four design engineers on this 4 million-gate chip. It supported the IPSec ESP and AH functions. Coordinated the logic verification and physical design efforts. Supervised the test vector and system bring up efforts. Released to production with first tapeout. Security Processor 2000 – 2001 Managed a team to gate shrink a security coprocessor from 0.25 um to 0.18 um. Refined the DMA and balanced the flow control. These enhancements allowed the 3 million-gate chip to increase its throughput by 50%. Worked closely with the physical design team to implement the timing critical 3DES logic and PCI64 IO logic. Datapath Systems (Hard Drive Read Channel) 1997 – 1999 Principal Engineer/Design Manager Managed a team to design an 800 Mbit/sec Read Channel with a 0.18 um process. Supervised and managed digital logic design, block integration and verification. Designed a 500 Mbit/sec Read Channel. Responsible for the design of the digital logic - Write path and Read path. Performed timing verification with Synopsys and TimeMill. Setup environment to facilitate design database tracking and Synopsys synthesis flow. Silicon Graphics (Desktop Graphic Division) 1995 – 1997 Design Engineer Designed the front-end data path of the rasterizer. Designed the coverage, the barycentric coord. and perspective correction blocks. Designed a packet bus interface, flow control, context switch and async. interface of a graphic controller. Used LSI 0.35 um. Used Motive to verify the 250K-gate full chip timing. Worked with CAD engineers to develop a program that identified clock domain crossing signals. Sun Microsystems Inc. (Microprocessor Division) 1988 – 1995 Staff Engineer Led a team to characterize a 90 MHz SPARC CPU on tester. Used DFT-scandump features to locate functional and speed problems. Quickturn Hardware Emulation of a CPU. Design of a BiCMOS RISC Floating Point Unit. Responsible for the logic and circuit design of the register file, data dispatcher, normalizer and special operand processor. Worked with CAD engineers to develop Design-For-Test tools. Design of a BiCMOS RISC Integer Unit. Responsible for the circuit design of data dispatcher, execution unit and program counter. Synthesis and speed optimization of control logic. Timing verification using Motive/Pearl/Hspice. Oversaw the layout integration. TECHNICAL SKILLS Verilog HDL, Synopsys Design Compiler, Conformal, Spyglass Lint, PwrChk and CDC. Timing flow and Design for Test Methodology. EDUCATION The University of California, Berkeley. M.S. Electrical Engineering The University of Texas at Austin. B.S. Electrical Engineering