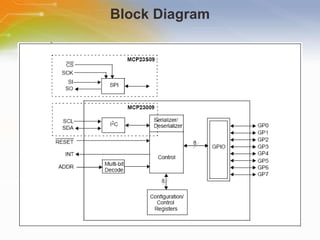

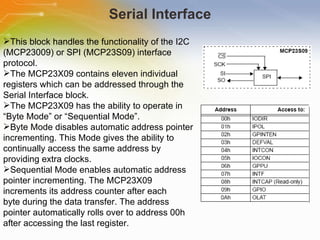

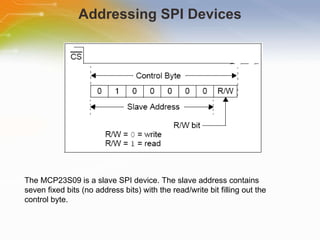

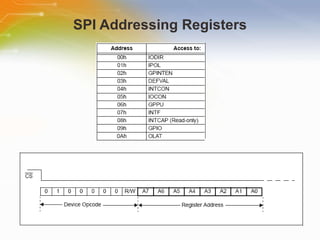

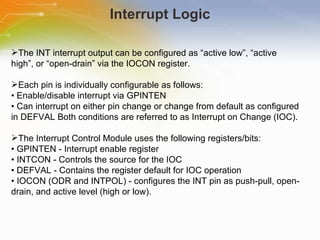

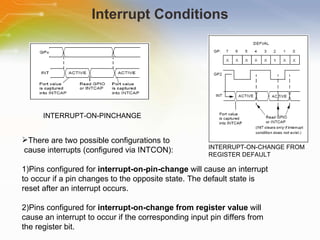

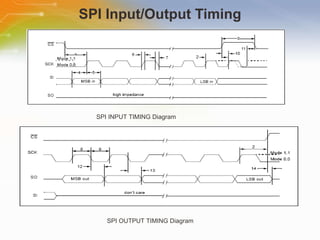

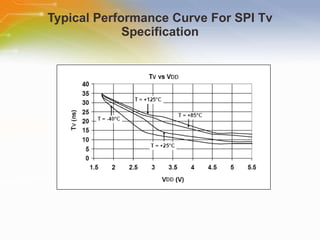

The document provides an overview of the MCP23S09 I/O expander with an SPI interface. It describes the device's features such as 8 bidirectional I/O pins, interrupt output pins, and SPI interface. It also covers the device's block diagram, addressing over SPI, interrupt logic and conditions, and SPI timing diagrams. The document is intended to help learn about the working and operation of the MCP23S09 I/O expander.