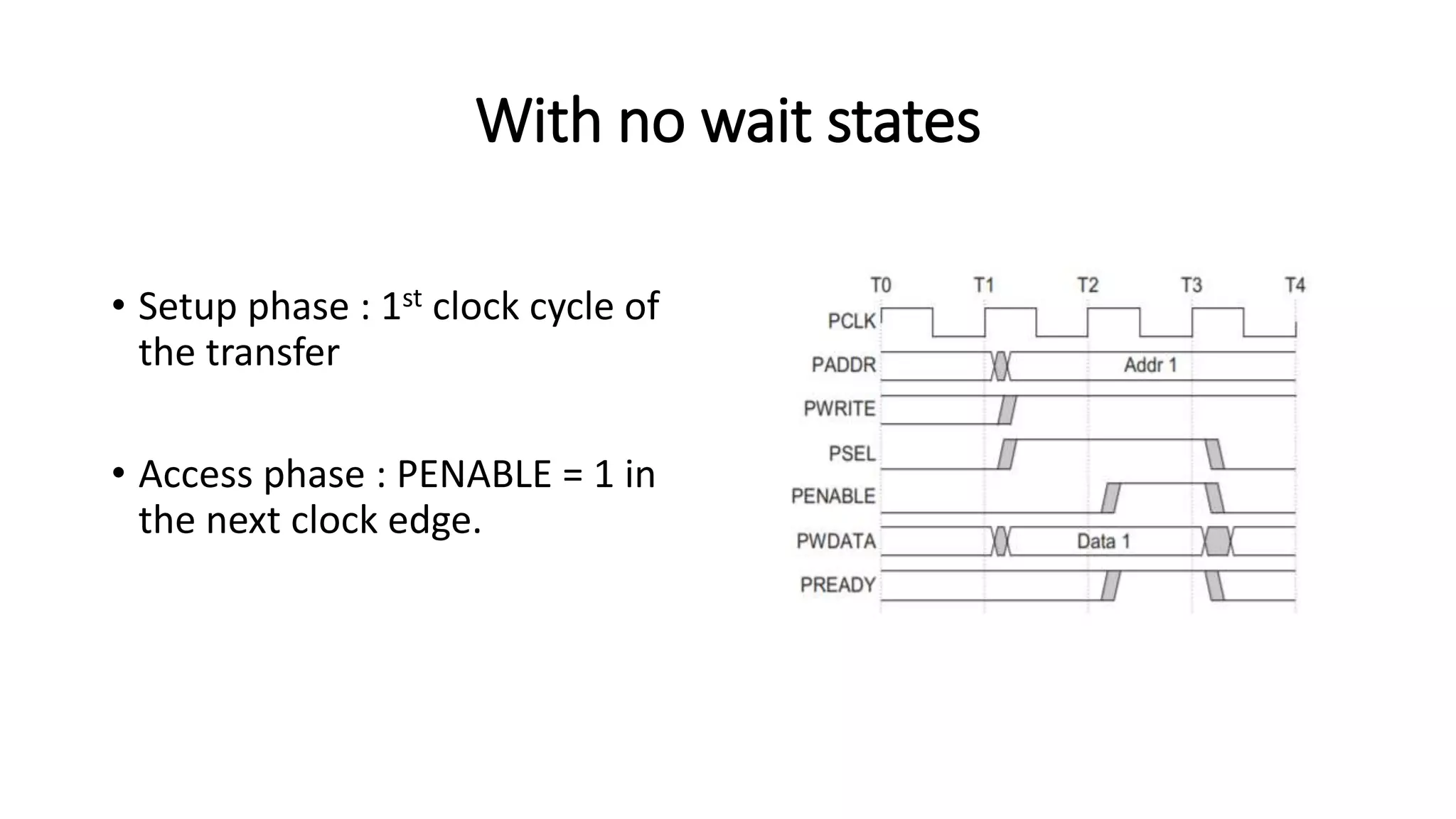

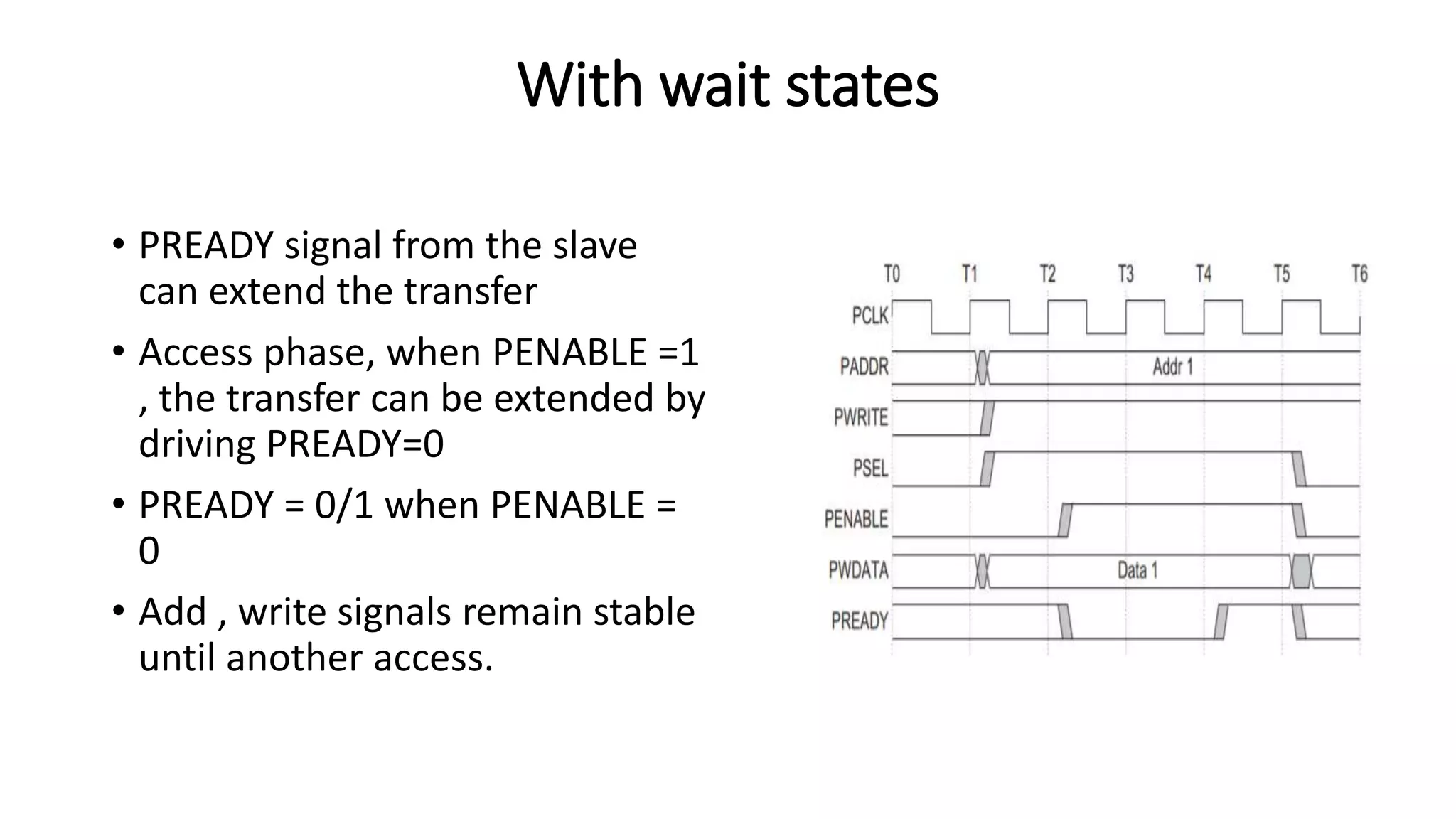

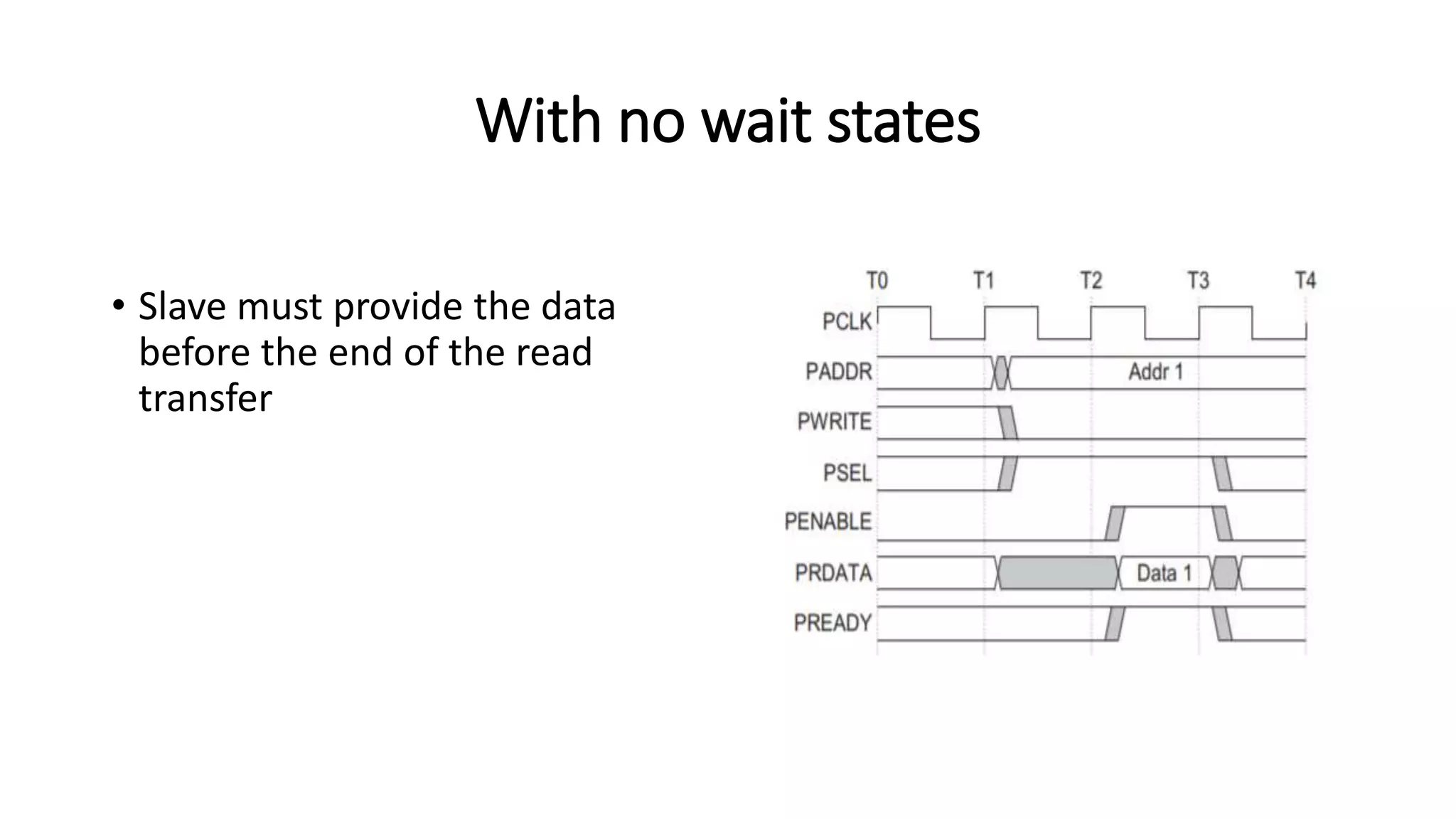

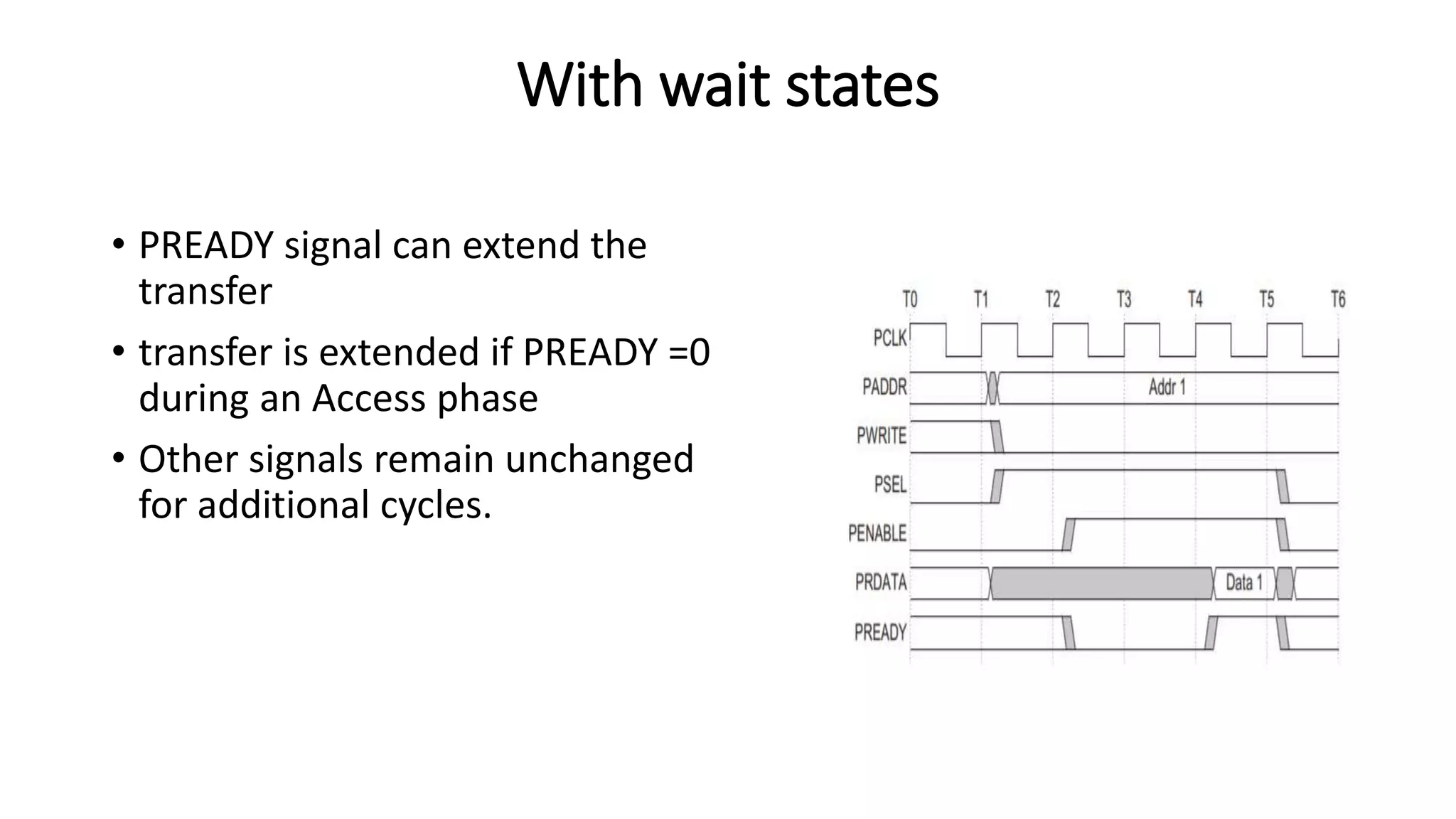

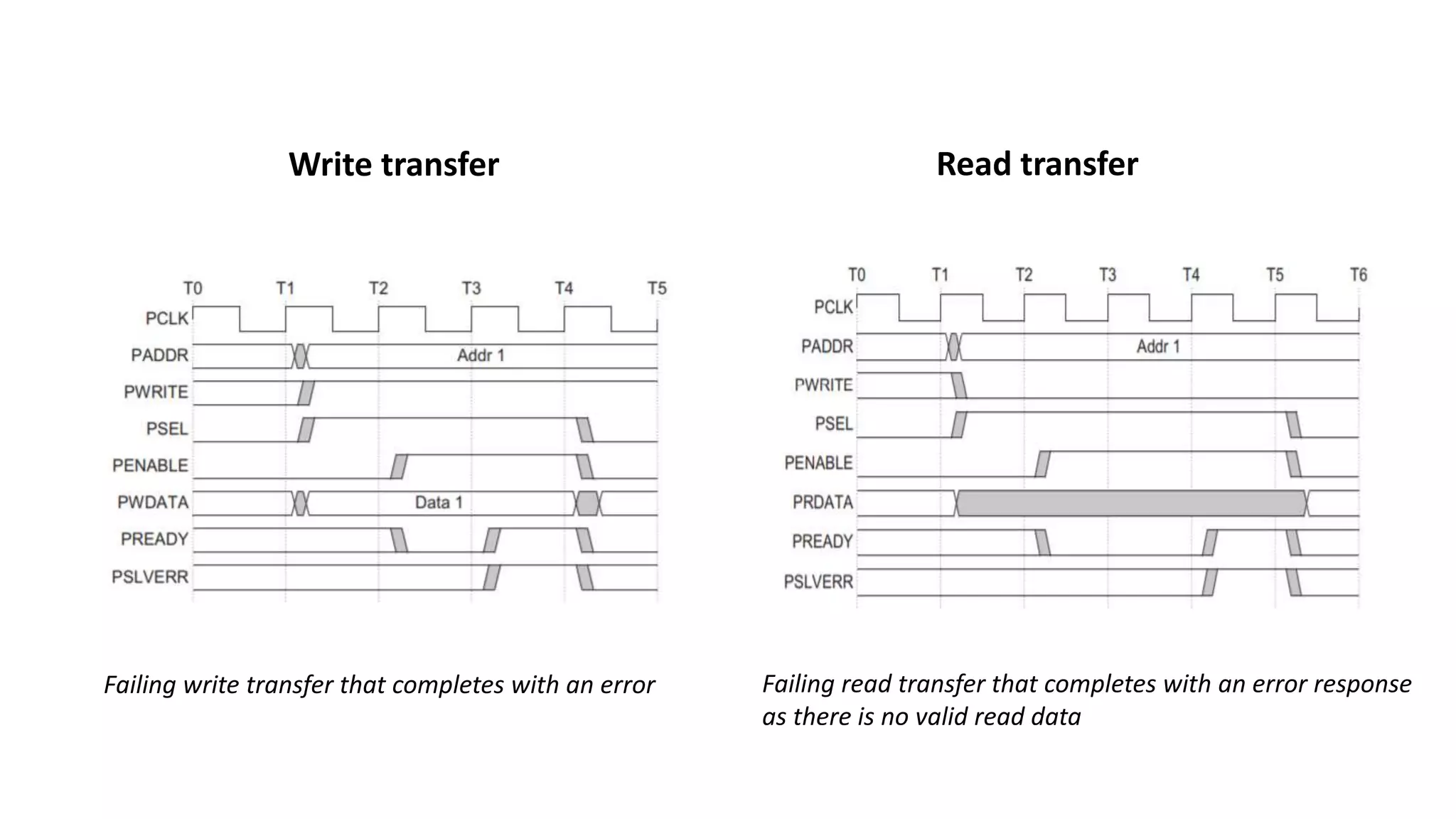

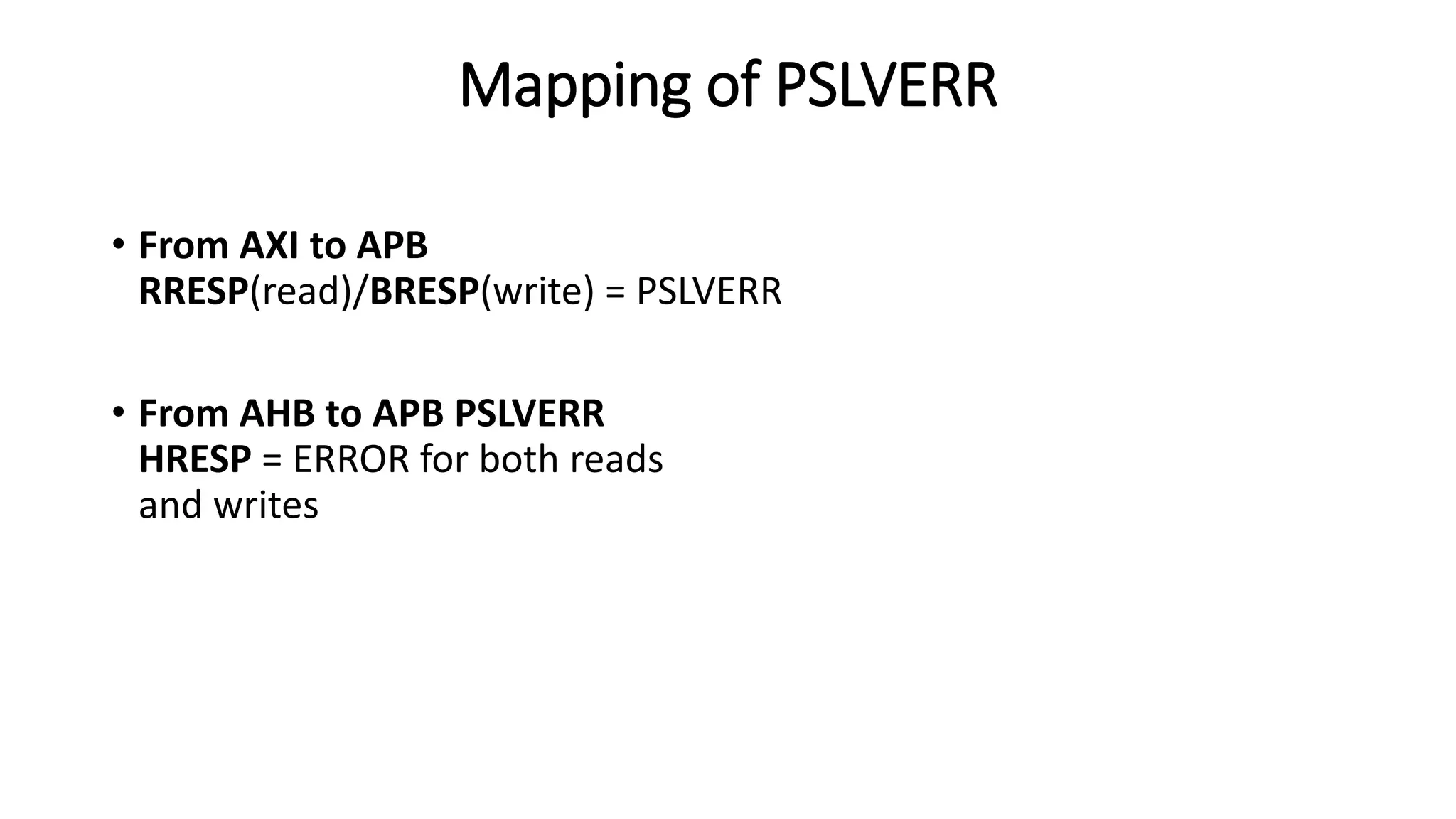

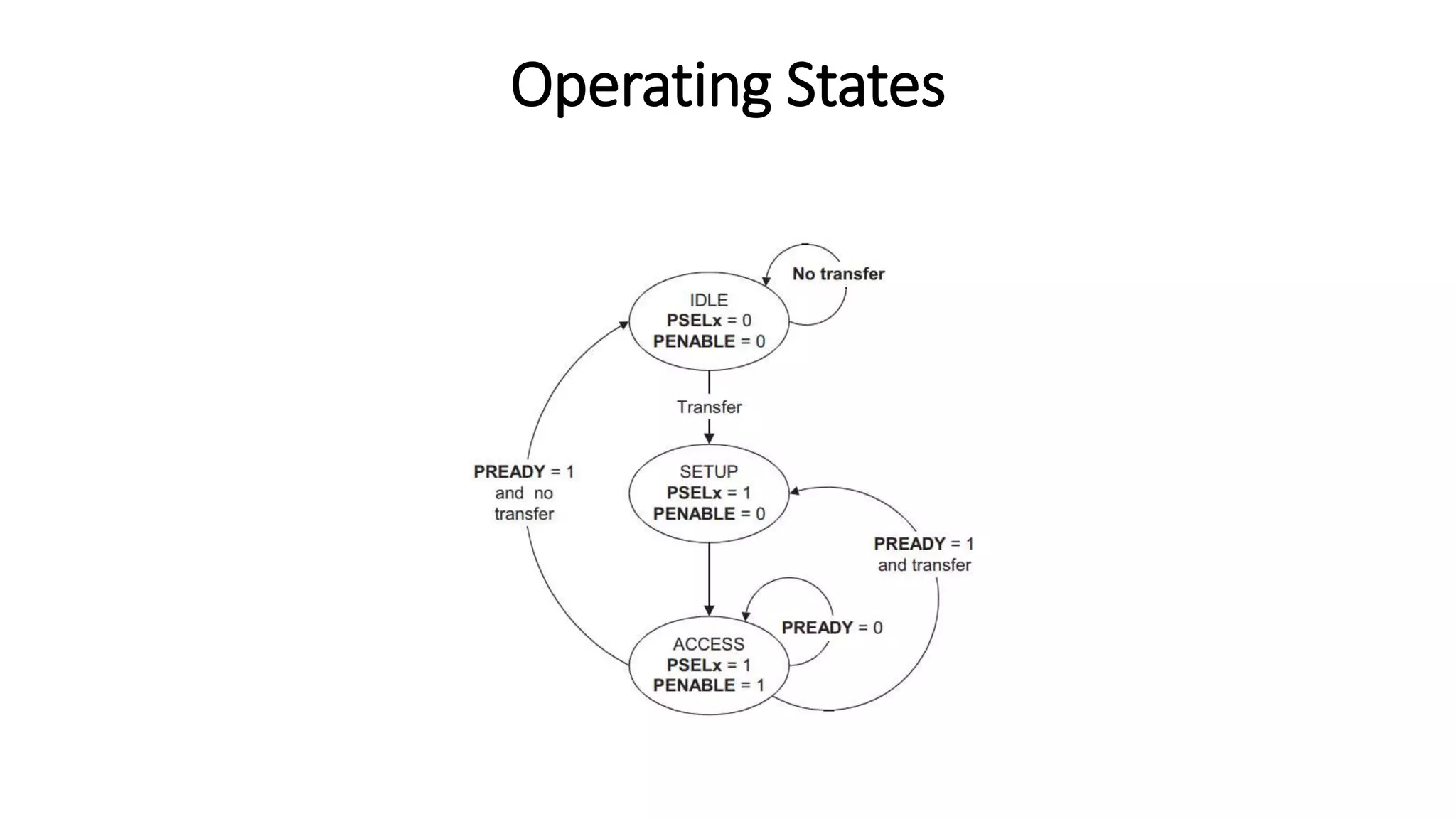

The AMBA 3 APB protocol is designed for low-cost, low-power interface connecting to low-bandwidth peripherals, with all signal transitions tied to the clock's rising edge. It outlines two types of transfers—write and read, each with options for wait states and error response mechanisms using the pslverr signal. The document details the transfer phases, error handling, and the mapping of error responses from other protocols to APB.