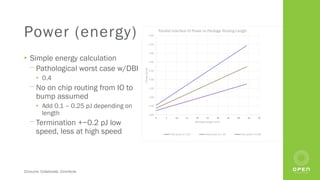

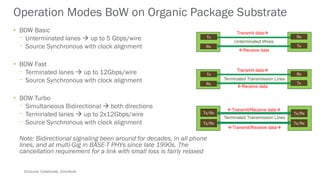

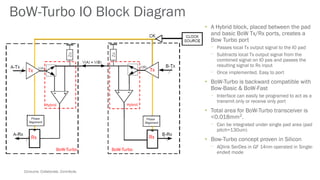

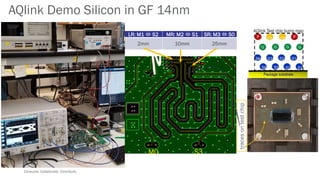

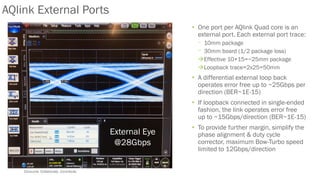

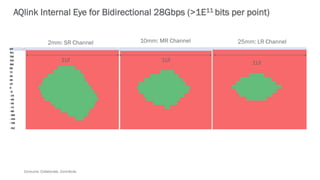

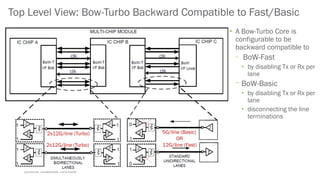

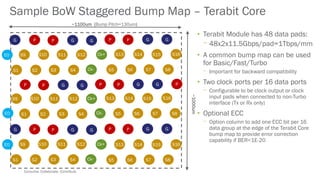

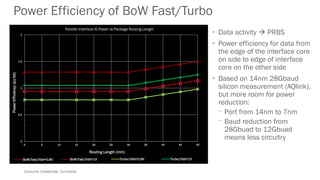

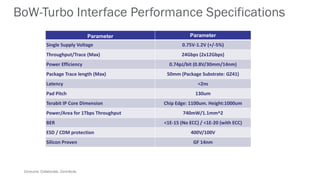

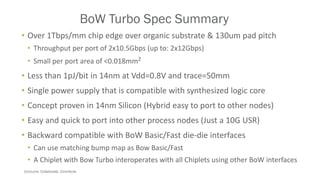

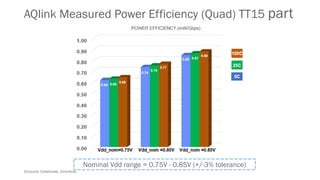

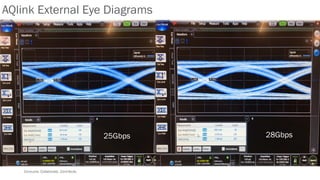

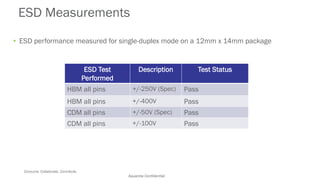

The document proposes the Bow interface standard for chiplet-based systems. Bow would use simple CMOS IO to enable communication between dies up to 4Gbps per line untetherminated (Bow Basic), up to 12Gbps per line with termination (Bow Fast), and bidirectional up to 2x12Gbps per line with hybrid termination (Bow Turbo). It details the motivation and benefits of Bow, provides example configurations and power estimates, and discusses testing and calls for volunteers to help define the open standard. Measurements from prototype silicon demonstrate error-free communication up to 25Gbps using the Bow Turbo concept.