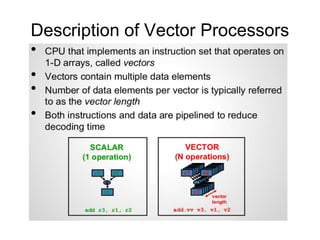

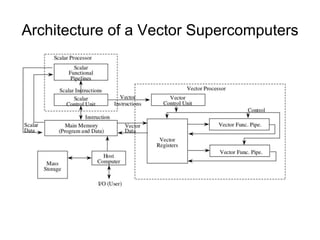

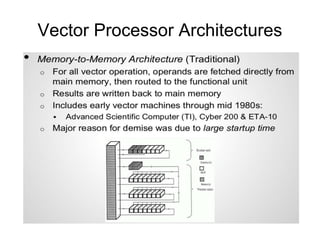

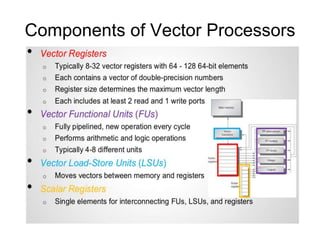

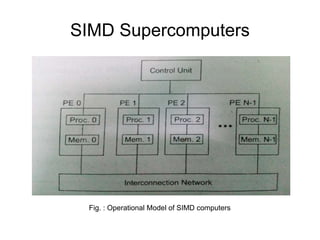

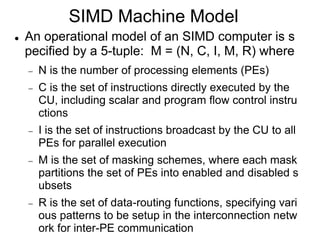

Vector supercomputers and SIMD computers are types of parallel computer models that can perform the same operation on multiple data elements simultaneously. Vector supercomputers have vector processors that are attached to scalar processors and use vector control units to supervise the flow of vector data between main memory and vector functional pipelines in a register-to-register or memory-to-memory fashion. SIMD computers have a number of processing elements that execute the same instruction broadcast by a control unit, along with masking and data routing functions to partition and communicate between processing elements.