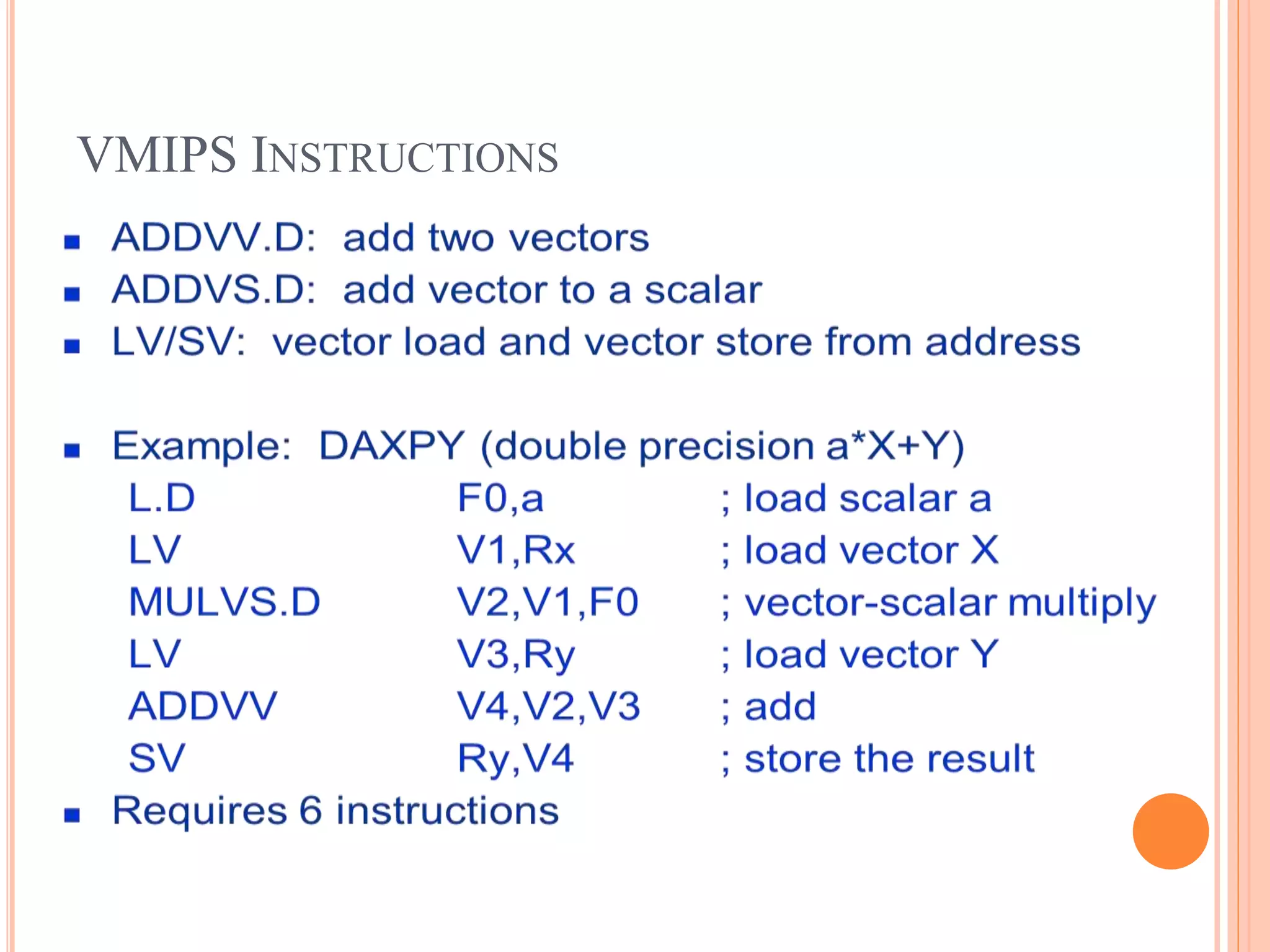

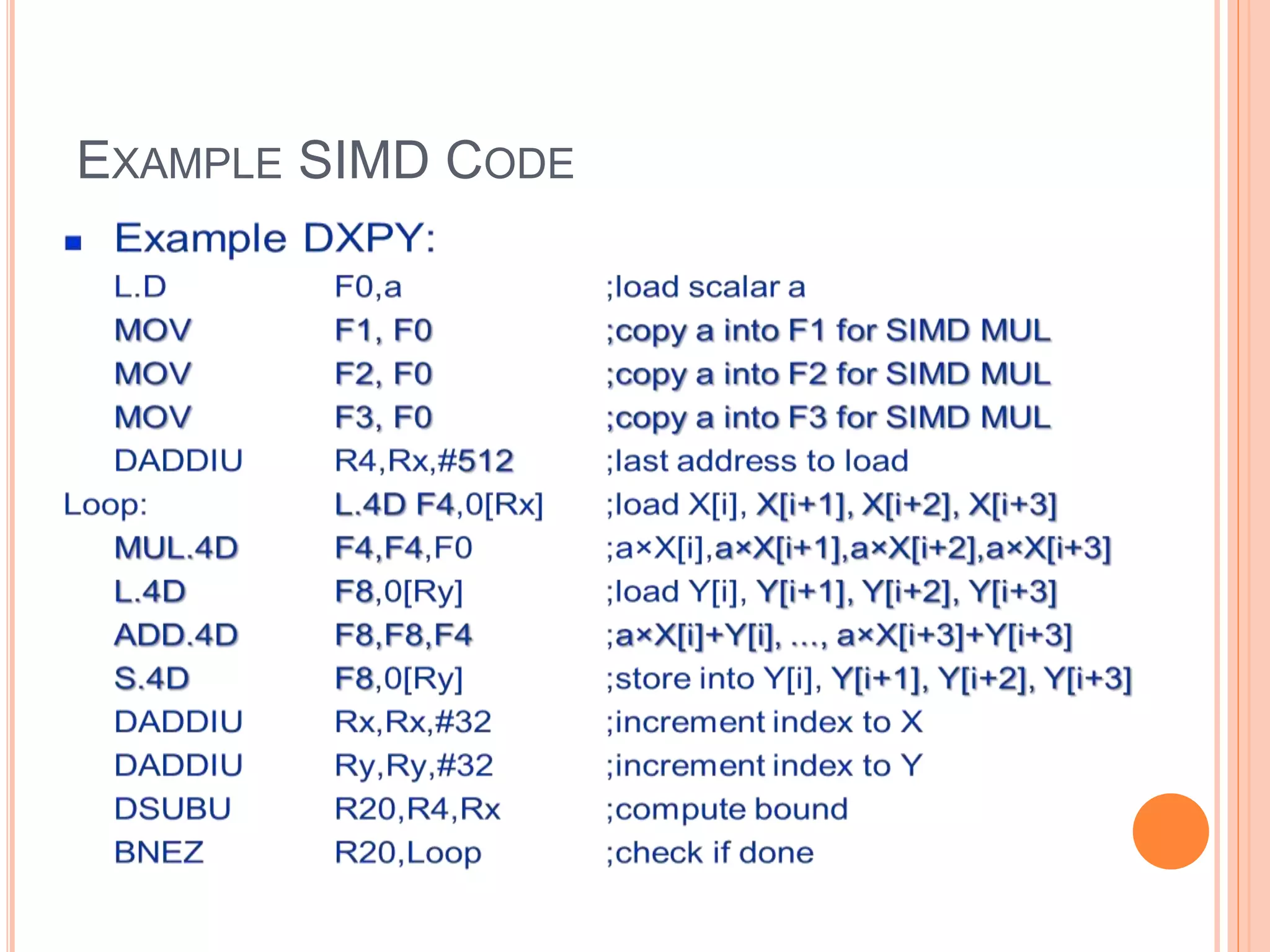

Seymour Cray introduced the concept of vector architecture in 1970 as an elegant interpretation of SIMD (Single Instruction Multiple Data). Vector architecture exploits data parallelism by performing the same operations on different pieces of data concurrently. This contrasts with dataflow architectures, which achieve concurrency by executing different operations in parallel in a data-driven manner, and thread parallelism, which uses different threads of control. Vector processors implement SIMD by executing the same instructions across multiple data elements concurrently.