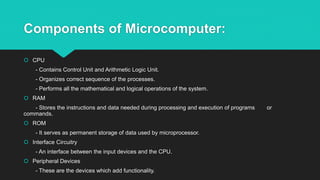

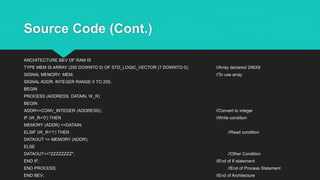

The document discusses microcomputers, detailing their components such as the CPU, RAM, and ROM, and their functions within a computing system. It explains RAM's role in storing changing information necessary for program execution and introduces two types of RAM: SRAM and DRAM. Additionally, VHDL source code for RAM implementation is provided, illustrating its read and write functionality.