High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m)

•Download as DOCX, PDF•

1 like•359 views

High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m) High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m) High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m) High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m)

Report

Share

Report

Share

Recommended

Graph based transistor network generation method for supergate design

Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design

A high performance fir filter architecture for fixed and reconfigurable appli...

A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications

High performance nb-ldpc decoder with reduction of message exchange

High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange

Flexible dsp accelerator architecture exploiting carry save arithmetic

Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic

Graph based transistor network generation method for supergate design

Chennai Office: JP INFOTECH, Old No.31, New No.86, 1st Floor, 1st Avenue, Ashok Nagar, Chennai-83. Landmark: Next to Kotak Mahendra Bank/Bharath Scans

Landline: (044) - 43012642 / Mobile: (0)9952649690

Pondicherry Office: JP INFOTECH, #45, Kamaraj Salai, Thattanchavady, Puducherry - 9

Landmark: Opp. to Thattanchavady Industrial Estate & Next to VVP Nagar Arch.

Landline: (0413) - 4300535 / Mobile: (0)8608600246 / (0)9952649690

Flexible dsp accelerator architecture exploiting carry save arithmetic

2016 ieee project ,2016-2017 ieee projects, application projects, best ieee projects, bulk final year projects, bulk ieee projects ,diploma projects electrical engineering electrical engineering projects ,final year application projects, final year csc projects, final year cse project, final year it projects ,final year project, final year projects, final year projects in chennai ,final year projects in coimabtore, final year projects in hyderabad, final year projects in pondicherry final year projects in rajasthan ,ieee based projects for ece, ieee final year projects, ieee master, ieee project, ieee project 2015 ,ieee project 2016, ieee project centers in pondicherry ,ieee project for eee, ieee projects, ieee projects ,2015-2016 ieee projects, 2016-2017 ieee projects, cse ieee projects, cse 2015 ieee projects, cse 2016 ieee projects for cse ,ieee projects for it, ieee projects in bangalore, ieee projects in chennai, ieee projects in coimbatore, ieee projects in hyderabad ,ieee projects in madurai ,ieee projects in maharashtra ,ieee projects in mumbai, ieee projects in odisha, ieee projects in orissa, ieee projects in pondicherry, ieee projects in pondy ,ieee projects in pune, ieee projects in uttarakhand, ieee projects titles, 2015-2016 latest projects for eee, NEXGEN TECHNOLOGY mtech ieee projects mtech projects 2016-2017 mtech projects in chennai mtech, projects in cuddalore ,mtech projects in neyveli, mtech projects in panruti, mtech projects in pondicherry, mtech projects in tindivanam, mtech projects in villupuram, online ieee projects ,phd guidance, project for engineering ,project titles for ece

DUAL FIELD DUAL CORE SECURE CRYPTOPROCESSOR ON FPGA PLATFORM

This paper is devoted to the design of dual core crypto processor for executing both Prime field and binary field instructions. The proposed design is specifically optimized for Field programmable gate array (FPGA) platform. Combination of two different field (prime field GF(p) and Binary field GF(2m)) instructions execution is analysed.The design is implemented in Spartan 3E and virtex5. Both the performance results are compared. The implementation result shows the execution of parallelism using dual field instructions

High Performance MAC Unit for FFT Implementation

Information Technology,Enviornmental Engineering,VLSI Design,Nano Technology,Mathematics,Test & Testability,Communication Engineering,Rural Technology,Textile Engineering ,Robotics,Embedded System,Plastic EngineeringSoftware engineering

Recommended

Graph based transistor network generation method for supergate design

Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design Graph based transistor network generation method for supergate design

A high performance fir filter architecture for fixed and reconfigurable appli...

A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications A high performance fir filter architecture for fixed and reconfigurable applications

High performance nb-ldpc decoder with reduction of message exchange

High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange

Flexible dsp accelerator architecture exploiting carry save arithmetic

Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic Flexible dsp accelerator architecture exploiting carry save arithmetic

Graph based transistor network generation method for supergate design

Chennai Office: JP INFOTECH, Old No.31, New No.86, 1st Floor, 1st Avenue, Ashok Nagar, Chennai-83. Landmark: Next to Kotak Mahendra Bank/Bharath Scans

Landline: (044) - 43012642 / Mobile: (0)9952649690

Pondicherry Office: JP INFOTECH, #45, Kamaraj Salai, Thattanchavady, Puducherry - 9

Landmark: Opp. to Thattanchavady Industrial Estate & Next to VVP Nagar Arch.

Landline: (0413) - 4300535 / Mobile: (0)8608600246 / (0)9952649690

Flexible dsp accelerator architecture exploiting carry save arithmetic

2016 ieee project ,2016-2017 ieee projects, application projects, best ieee projects, bulk final year projects, bulk ieee projects ,diploma projects electrical engineering electrical engineering projects ,final year application projects, final year csc projects, final year cse project, final year it projects ,final year project, final year projects, final year projects in chennai ,final year projects in coimabtore, final year projects in hyderabad, final year projects in pondicherry final year projects in rajasthan ,ieee based projects for ece, ieee final year projects, ieee master, ieee project, ieee project 2015 ,ieee project 2016, ieee project centers in pondicherry ,ieee project for eee, ieee projects, ieee projects ,2015-2016 ieee projects, 2016-2017 ieee projects, cse ieee projects, cse 2015 ieee projects, cse 2016 ieee projects for cse ,ieee projects for it, ieee projects in bangalore, ieee projects in chennai, ieee projects in coimbatore, ieee projects in hyderabad ,ieee projects in madurai ,ieee projects in maharashtra ,ieee projects in mumbai, ieee projects in odisha, ieee projects in orissa, ieee projects in pondicherry, ieee projects in pondy ,ieee projects in pune, ieee projects in uttarakhand, ieee projects titles, 2015-2016 latest projects for eee, NEXGEN TECHNOLOGY mtech ieee projects mtech projects 2016-2017 mtech projects in chennai mtech, projects in cuddalore ,mtech projects in neyveli, mtech projects in panruti, mtech projects in pondicherry, mtech projects in tindivanam, mtech projects in villupuram, online ieee projects ,phd guidance, project for engineering ,project titles for ece

DUAL FIELD DUAL CORE SECURE CRYPTOPROCESSOR ON FPGA PLATFORM

This paper is devoted to the design of dual core crypto processor for executing both Prime field and binary field instructions. The proposed design is specifically optimized for Field programmable gate array (FPGA) platform. Combination of two different field (prime field GF(p) and Binary field GF(2m)) instructions execution is analysed.The design is implemented in Spartan 3E and virtex5. Both the performance results are compared. The implementation result shows the execution of parallelism using dual field instructions

High Performance MAC Unit for FFT Implementation

Information Technology,Enviornmental Engineering,VLSI Design,Nano Technology,Mathematics,Test & Testability,Communication Engineering,Rural Technology,Textile Engineering ,Robotics,Embedded System,Plastic EngineeringSoftware engineering

A comparative study of different multiplier designs

A Comparative Study of Different Multiplier Designs

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

https://irjet.net/archives/V4/i3/IRJET-V4I3507.pdf

Modified montgomery modular multiplier for cryptosystems

Modified montgomery modular multiplier for cryptosystems

International Journal of Engineering Research and Development (IJERD)

journal publishing, how to publish research paper, Call For research paper, international journal, publishing a paper, IJERD, journal of science and technology, how to get a research paper published, publishing a paper, publishing of journal, publishing of research paper, reserach and review articles, IJERD Journal, How to publish your research paper, publish research paper, open access engineering journal, Engineering journal, Mathemetics journal, Physics journal, Chemistry journal, Computer Engineering, Computer Science journal, how to submit your paper, peer reviw journal, indexed journal, reserach and review articles, engineering journal, www.ijerd.com, research journals,

yahoo journals, bing journals, International Journal of Engineering Research and Development, google journals, hard copy of journal

A novel area efficient vlsi architecture for recursion computation in lte tur...

Chennai Office: JP INFOTECH, Old No.31, New No.86, 1st Floor, 1st Avenue, Ashok Nagar, Chennai-83. Landmark: Next to Kotak Mahendra Bank/Bharath Scans

Landline: (044) - 43012642 / Mobile: (0)9952649690

Pondicherry Office: JP INFOTECH, #45, Kamaraj Salai, Thattanchavady, Puducherry - 9

Landmark: Opp. to Thattanchavady Industrial Estate & Next to VVP Nagar Arch.

Landline: (0413) - 4300535 / Mobile: (0)8608600246 / (0)9952649690.

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

All processor consisting ALU and adder plays important role for design of ALU. Design of low area and power efficient adder helps to reduce power consumption and area of any processor. Now a day’s major area of research in VLSI system is design of area, high speed and low power data path logic systems. In digital adders, the speed of addition is restricted by the time necessary to send a carry signal through the adder. The area and power consumption is reduced by modifying regular CSLA architecture. The proposed architecture is developed with the help of a simple ripple carry adder (RCA) and gate-level architecture. It consists of single RCA which improves the performance of the proposed designs then the regular designs in terms of power consumption and area.

Aw4102359364

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

High speed Full-Adder (FA) module is a critical element in designing high performance arithmetic circuits. In this paper, we propose a new high speed multiple-valued logic FA module. The proposed FA is constructed by 14 transistors and 3 capacitors, using carbon nano-tube field effect transistor (CNFET) technology. Furthermore, our proposed technique has been examined in different voltages (i.e., 0.65v and 0.9v). The observed results reveal power consumption and power delay product (PDP) improvements compared to existing FA counterparts.

Eq36876880

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Multiplier and Accumulator Using Csla

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) vol.10 issue.1 version.1

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

This paper presents the advantage of using a new modulation scheme called dual carrier Modulation (DCM) compared to classical Quadrature Phase Shift Keying (QPSK) modulation.

This comparison is done at data transmission broadband in Multiband OFDM system (MBOFDM) based on Ultra Wide Band UWB. Simulation results show that the use of the modulation DCM for high data rates is more efficient compared with QPSK.

Efficient register renaming and recovery for high-performance processors.

Register renaming is a technique which is used to improve the performance and speed for a high-performance processors. It can be done using RAM , CAM and hybrid combination of RAM & CAM.

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

More Related Content

What's hot

A comparative study of different multiplier designs

A Comparative Study of Different Multiplier Designs

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

https://irjet.net/archives/V4/i3/IRJET-V4I3507.pdf

Modified montgomery modular multiplier for cryptosystems

Modified montgomery modular multiplier for cryptosystems

International Journal of Engineering Research and Development (IJERD)

journal publishing, how to publish research paper, Call For research paper, international journal, publishing a paper, IJERD, journal of science and technology, how to get a research paper published, publishing a paper, publishing of journal, publishing of research paper, reserach and review articles, IJERD Journal, How to publish your research paper, publish research paper, open access engineering journal, Engineering journal, Mathemetics journal, Physics journal, Chemistry journal, Computer Engineering, Computer Science journal, how to submit your paper, peer reviw journal, indexed journal, reserach and review articles, engineering journal, www.ijerd.com, research journals,

yahoo journals, bing journals, International Journal of Engineering Research and Development, google journals, hard copy of journal

A novel area efficient vlsi architecture for recursion computation in lte tur...

Chennai Office: JP INFOTECH, Old No.31, New No.86, 1st Floor, 1st Avenue, Ashok Nagar, Chennai-83. Landmark: Next to Kotak Mahendra Bank/Bharath Scans

Landline: (044) - 43012642 / Mobile: (0)9952649690

Pondicherry Office: JP INFOTECH, #45, Kamaraj Salai, Thattanchavady, Puducherry - 9

Landmark: Opp. to Thattanchavady Industrial Estate & Next to VVP Nagar Arch.

Landline: (0413) - 4300535 / Mobile: (0)8608600246 / (0)9952649690.

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

All processor consisting ALU and adder plays important role for design of ALU. Design of low area and power efficient adder helps to reduce power consumption and area of any processor. Now a day’s major area of research in VLSI system is design of area, high speed and low power data path logic systems. In digital adders, the speed of addition is restricted by the time necessary to send a carry signal through the adder. The area and power consumption is reduced by modifying regular CSLA architecture. The proposed architecture is developed with the help of a simple ripple carry adder (RCA) and gate-level architecture. It consists of single RCA which improves the performance of the proposed designs then the regular designs in terms of power consumption and area.

Aw4102359364

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

High speed Full-Adder (FA) module is a critical element in designing high performance arithmetic circuits. In this paper, we propose a new high speed multiple-valued logic FA module. The proposed FA is constructed by 14 transistors and 3 capacitors, using carbon nano-tube field effect transistor (CNFET) technology. Furthermore, our proposed technique has been examined in different voltages (i.e., 0.65v and 0.9v). The observed results reveal power consumption and power delay product (PDP) improvements compared to existing FA counterparts.

Eq36876880

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Multiplier and Accumulator Using Csla

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) vol.10 issue.1 version.1

What's hot (19)

IJERD (www.ijerd.com) International Journal of Engineering Research and Devel...

IJERD (www.ijerd.com) International Journal of Engineering Research and Devel...

Iaetsd pipelined parallel fft architecture through folding transformation

Iaetsd pipelined parallel fft architecture through folding transformation

A comparative study of different multiplier designs

A comparative study of different multiplier designs

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

Modified montgomery modular multiplier for cryptosystems

Modified montgomery modular multiplier for cryptosystems

International Journal of Engineering Research and Development (IJERD)

International Journal of Engineering Research and Development (IJERD)

A novel area efficient vlsi architecture for recursion computation in lte tur...

A novel area efficient vlsi architecture for recursion computation in lte tur...

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

Iaetsd vlsi architecture for exploiting carry save arithmetic using verilog hdl

Iaetsd vlsi architecture for exploiting carry save arithmetic using verilog hdl

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

Research Inventy : International Journal of Engineering and Science is publis...

Research Inventy : International Journal of Engineering and Science is publis...

Similar to High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m)

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

This paper presents the advantage of using a new modulation scheme called dual carrier Modulation (DCM) compared to classical Quadrature Phase Shift Keying (QPSK) modulation.

This comparison is done at data transmission broadband in Multiband OFDM system (MBOFDM) based on Ultra Wide Band UWB. Simulation results show that the use of the modulation DCM for high data rates is more efficient compared with QPSK.

Efficient register renaming and recovery for high-performance processors.

Register renaming is a technique which is used to improve the performance and speed for a high-performance processors. It can be done using RAM , CAM and hybrid combination of RAM & CAM.

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

J045075661

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Design and Implementation of an Efficient Carry Skip Adder

https://www.irjet.net/archives/V4/i6/IRJET-V4I6364.pdf

Low cost high-performance vlsi architecture for montgomery modular multiplica...

Chennai Office: JP INFOTECH, Old No.31, New No.86, 1st Floor, 1st Avenue, Ashok Nagar, Chennai-83. Landmark: Next to Kotak Mahendra Bank/Bharath Scans

Landline: (044) - 43012642 / Mobile: (0)9952649690

Pondicherry Office: JP INFOTECH, #45, Kamaraj Salai, Thattanchavady, Puducherry - 9

Landmark: Opp. to Thattanchavady Industrial Estate & Next to VVP Nagar Arch.

Landline: (0413) - 4300535 / Mobile: (0)8608600246 / (0)9952649690 .

CFA based SBOX and Modified Mixcolumn Implementation of 8 Bit Datapath for AES

Secure data transmission is very important in any communication systems.

Network Security provides many techniques for efficient data transmission through

unprotected network. Cryptography provides a method for securing the transmission of

information by the process of encryption. Encryption converts the message in to unreadable

form (Cipher Text) . Decryption converts this Cipher Text back to original message.

Advanced Encryption Standard (AES) has been used as the first choice of cryptographic

algorithm for many security based applications because of the high level of security and

flexibility of implementation in hardware and software. This paper presents an area

efficient, low power design for AES based on an 8-bit data path making it suitable for

wireless security applications. It has a significant power-area-latency performance

improvements over other existing AES designs. For high performance applications, AES S-

box and inverse S-box implemented using composite field Arithmetic (CFA). Also low

resource Mixcolumn structure is used in this structure. The 8 bit data path architecture is

implemented in XILINX 13.2 and simulated using MODELSIM 6.5 software. Also the

power and area calculation is done with the help of SYNOPSYS software.

International Journal of Engineering Research and Development

Electrical, Electronics and Computer Engineering,

Information Engineering and Technology,

Mechanical, Industrial and Manufacturing Engineering,

Automation and Mechatronics Engineering,

Material and Chemical Engineering,

Civil and Architecture Engineering,

Biotechnology and Bio Engineering,

Environmental Engineering,

Petroleum and Mining Engineering,

Marine and Agriculture engineering,

Aerospace Engineering.

Implementation of High Throughput Radix-16 FFT Processor

The extension of radix-4 algorithm to radix-16 to achieve the high throughput of 2.59 giga-samples/s for WPAN’s.We are also reformulating radix-16 algorithm to achieve low-complexity and

low area cost and high performance. Radix-16 FFT is obtained by cascaded the radix -4 butterfly

units. It facilitates low-complexity realization of radix-16 butterfly operation and high operation speed

due to its optimized pipelined structure. Besides, a new three-stage multiplier for twiddle factor

multiplication is also proposed, which has lower area and power consumption than conventional

complex multipliers

BER Performance Improvement for 4 X 4 MIMO Single Carrier FDMA System Using M...

https://irjet.net/archives/V3/i1/IRJET-V3I1211.pdf

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

https://www.irjet.net/archives/V6/i5/IRJET-V6I5123.pdf

Implementation of OFDM System Using Various Channel Modulation Schemes

This report discusses the planning Associate in

nursing the implementation of an OFDM system

in several information module schemes like MQPSK,

M-QAM. First, a short introduction is

provided by explaining the background and the

specification of the project. Then the report deals

with the system model, every block of the OFDM

system is represented (IFFT, FFT, Cyclic prefix,

modulation / reception, Channel estimation, bit

error rate). System design is analyzed. The

transmission techniques, further because the

system parameters for transmission and reception

are explained well. Finally, the results are

provided.

International Journal of Engineering Research and Development (IJERD)

journal publishing, how to publish research paper, Call For research paper, international journal, publishing a paper, IJERD, journal of science and technology, how to get a research paper published, publishing a paper, publishing of journal, publishing of research paper, reserach and review articles, IJERD Journal, How to publish your research paper, publish research paper, open access engineering journal, Engineering journal, Mathemetics journal, Physics journal, Chemistry journal, Computer Engineering, Computer Science journal, how to submit your paper, peer reviw journal, indexed journal, reserach and review articles, engineering journal, www.ijerd.com, research journals,

yahoo journals, bing journals, International Journal of Engineering Research and Development, google journals, hard copy of journal

Performance analysis of NOR CAM cell using CMOS-HP, CMOS-LP and FinFET 16nm t...

https://www.irjet.net/archives/V10/i4/IRJET-V10I4183.pdf

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

This report examines the subject of sub threshold leakage on carry save adder. When the gate to source voltage reduces to the threshold voltage at that place is yet some amount of current flow in the circuit and that is undesired. As the process technology advancing much rapidly the threshold voltage of MOS devices reduces very drastically, and it must be applied in lower power devices since it contributes to low amount of leakage current which confine increases the power consumption of the devices. Adders are the basic building blocks for any digital circuit design and used in almost all arithmetic’s. The CSA proves efficient adders due to its quick and precise computations. Hence this paper performs sub threshold analysis on CSA and the scrutinize results that the total average power is around 4.93µW, the propagation delay for complete operation is 16.3ns and since this design uses GDI cell so there is a reduction in area with 37%.

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

This report examines the subject of sub threshold leakage on carry save adder. When the gate to source voltage reduces to the threshold voltage at that place is yet some amount of current flow in the circuit and that is undesired. As the process technology advancing much rapidly the threshold voltage of MOS devices reduces very drastically, and it must be applied in lower power devices since it contributes to low amount

of leakage current which confine increases the power consumption of the devices. Adders are the basic

building blocks for any digital circuit design and used in almost all arithmetic’s. The CSA proves efficient adders due to its quick and precise computations. Hence this paper performs sub threshold analysis on CSA and the scrutinize results that the total average power is around 4.93µW, the propagation delay for complete operation is 16.3ns and since this design uses GDI cell so there is a reduction in area with 37%.

Similar to High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m) (20)

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

Efficient register renaming and recovery for high-performance processors.

Efficient register renaming and recovery for high-performance processors.

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

High-Speed and Low-Latency ECC Processor Implementation Over GF(2m) on FPGA

Overview of signal integrity simulation for sfp+ interface serial links with ...

Overview of signal integrity simulation for sfp+ interface serial links with ...

Design and Implementation of an Efficient Carry Skip Adder

Design and Implementation of an Efficient Carry Skip Adder

Low cost high-performance vlsi architecture for montgomery modular multiplica...

Low cost high-performance vlsi architecture for montgomery modular multiplica...

Iaetsd gmsk modulation implementation for gsm in dsp

Iaetsd gmsk modulation implementation for gsm in dsp

CFA based SBOX and Modified Mixcolumn Implementation of 8 Bit Datapath for AES

CFA based SBOX and Modified Mixcolumn Implementation of 8 Bit Datapath for AES

International Journal of Engineering Research and Development

International Journal of Engineering Research and Development

Implementation of High Throughput Radix-16 FFT Processor

Implementation of High Throughput Radix-16 FFT Processor

BER Performance Improvement for 4 X 4 MIMO Single Carrier FDMA System Using M...

BER Performance Improvement for 4 X 4 MIMO Single Carrier FDMA System Using M...

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

Implementation of OFDM System Using Various Channel Modulation Schemes

Implementation of OFDM System Using Various Channel Modulation Schemes

International Journal of Engineering Research and Development (IJERD)

International Journal of Engineering Research and Development (IJERD)

Performance analysis of NOR CAM cell using CMOS-HP, CMOS-LP and FinFET 16nm t...

Performance analysis of NOR CAM cell using CMOS-HP, CMOS-LP and FinFET 16nm t...

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

PERFORMANCE EVALUATION OF LOW POWER CARRY SAVE ADDER FOR VLSI APPLICATIONS

Recently uploaded

Premium MEAN Stack Development Solutions for Modern Businesses

Stay ahead of the curve with our premium MEAN Stack Development Solutions. Our expert developers utilize MongoDB, Express.js, AngularJS, and Node.js to create modern and responsive web applications. Trust us for cutting-edge solutions that drive your business growth and success.

Know more: https://www.synapseindia.com/technology/mean-stack-development-company.html

RMD24 | Retail media: hoe zet je dit in als je geen AH of Unilever bent? Heid...

Grote partijen zijn al een tijdje onderweg met retail media. Ondertussen worden in dit domein ook de kansen zichtbaar voor andere spelers in de markt. Maar met die kansen ontstaan ook vragen: Zelf retail media worden of erop adverteren? In welke fase van de funnel past het en hoe integreer je het in een mediaplan? Wat is nu precies het verschil met marketplaces en Programmatic ads? In dit half uur beslechten we de dilemma's en krijg je antwoorden op wanneer het voor jou tijd is om de volgende stap te zetten.

Search Disrupted Google’s Leaked Documents Rock the SEO World.pdf

The world of search engine optimization (SEO) is buzzing with discussions after Google confirmed that around 2,500 leaked internal documents related to its Search feature are indeed authentic. The revelation has sparked significant concerns within the SEO community. The leaked documents were initially reported by SEO experts Rand Fishkin and Mike King, igniting widespread analysis and discourse. For More Info:- https://news.arihantwebtech.com/search-disrupted-googles-leaked-documents-rock-the-seo-world/

Discover the innovative and creative projects that highlight my journey throu...

Discover the innovative and creative projects that highlight my journey through Full Sail University. Below, you’ll find a collection of my work showcasing my skills and expertise in digital marketing, event planning, and media production.

Digital Transformation and IT Strategy Toolkit and Templates

This Digital Transformation and IT Strategy Toolkit was created by ex-McKinsey, Deloitte and BCG Management Consultants, after more than 5,000 hours of work. It is considered the world's best & most comprehensive Digital Transformation and IT Strategy Toolkit. It includes all the Frameworks, Best Practices & Templates required to successfully undertake the Digital Transformation of your organization and define a robust IT Strategy.

Editable Toolkit to help you reuse our content: 700 Powerpoint slides | 35 Excel sheets | 84 minutes of Video training

This PowerPoint presentation is only a small preview of our Toolkits. For more details, visit www.domontconsulting.com

Recruiting in the Digital Age: A Social Media Masterclass

In this masterclass, presented at the Global HR Summit on 5th June 2024, Luan Wise explored the essential features of social media platforms that support talent acquisition, including LinkedIn, Facebook, Instagram, X (formerly Twitter) and TikTok.

Kseniya Leshchenko: Shared development support service model as the way to ma...

Kseniya Leshchenko: Shared development support service model as the way to make small projects with small budgets profitable for the company (UA)

Kyiv PMDay 2024 Summer

Website – www.pmday.org

Youtube – https://www.youtube.com/startuplviv

FB – https://www.facebook.com/pmdayconference

Business Valuation Principles for Entrepreneurs

This insightful presentation is designed to equip entrepreneurs with the essential knowledge and tools needed to accurately value their businesses. Understanding business valuation is crucial for making informed decisions, whether you're seeking investment, planning to sell, or simply want to gauge your company's worth.

一比一原版加拿大渥太华大学毕业证(uottawa毕业证书)如何办理

一模一样【q/微:1954292140】【加拿大渥太华大学毕业证(uottawa毕业证书)成绩单Offer】【q/微:1954292140】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

【业务选择办理准则】

一、工作未确定,回国需先给父母、亲戚朋友看下文凭的情况,办理一份就读学校的毕业证【q/微:1954292140】文凭即可

二、回国进私企、外企、自己做生意的情况,这些单位是不查询毕业证真伪的,而且国内没有渠道去查询国外文凭的真假,也不需要提供真实教育部认证。鉴于此,办理一份毕业证【q/微:1954292140】即可

三、进国企,银行,事业单位,考公务员等等,这些单位是必需要提供真实教育部认证的,办理教育部认证所需资料众多且烦琐,所有材料您都必须提供原件,我们凭借丰富的经验,快捷的绿色通道帮您快速整合材料,让您少走弯路。

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

falcon-invoice-discounting-a-premier-platform-for-investors-in-india

Falcon stands out as a top-tier P2P Invoice Discounting platform in India, bridging esteemed blue-chip companies and eager investors. Our goal is to transform the investment landscape in India by establishing a comprehensive destination for borrowers and investors with diverse profiles and needs, all while minimizing risk. What sets Falcon apart is the elimination of intermediaries such as commercial banks and depository institutions, allowing investors to enjoy higher yields.

Exploring Patterns of Connection with Social Dreaming

Exploring Patterns of Connection -Introduction to Social Dreaming

#Systems Psychodynamics

#Innovation

#Creativity

#Consultancy

#Coaching

Maksym Vyshnivetskyi: PMO Quality Management (UA)

Maksym Vyshnivetskyi: PMO Quality Management (UA)

Lemberg PMO School 2024

Website – https://lembs.com/pmoschool

Youtube – https://www.youtube.com/startuplviv

FB – https://www.facebook.com/pmdayconference

ModelingMarketingStrategiesMKS.CollumbiaUniversitypdf

Implicitly or explicitly all competing businesses employ a strategy to select a mix

of marketing resources. Formulating such competitive strategies fundamentally

involves recognizing relationships between elements of the marketing mix (e.g.,

price and product quality), as well as assessing competitive and market conditions

(i.e., industry structure in the language of economics).

LA HUG - Video Testimonials with Chynna Morgan - June 2024

Have you ever heard that user-generated content or video testimonials can take your brand to the next level? We will explore how you can effectively use video testimonials to leverage and boost your sales, content strategy, and increase your CRM data.🤯

We will dig deeper into:

1. How to capture video testimonials that convert from your audience 🎥

2. How to leverage your testimonials to boost your sales 💲

3. How you can capture more CRM data to understand your audience better through video testimonials. 📊

Recently uploaded (20)

Premium MEAN Stack Development Solutions for Modern Businesses

Premium MEAN Stack Development Solutions for Modern Businesses

RMD24 | Retail media: hoe zet je dit in als je geen AH of Unilever bent? Heid...

RMD24 | Retail media: hoe zet je dit in als je geen AH of Unilever bent? Heid...

Search Disrupted Google’s Leaked Documents Rock the SEO World.pdf

Search Disrupted Google’s Leaked Documents Rock the SEO World.pdf

Discover the innovative and creative projects that highlight my journey throu...

Discover the innovative and creative projects that highlight my journey throu...

Digital Transformation and IT Strategy Toolkit and Templates

Digital Transformation and IT Strategy Toolkit and Templates

Recruiting in the Digital Age: A Social Media Masterclass

Recruiting in the Digital Age: A Social Media Masterclass

Kseniya Leshchenko: Shared development support service model as the way to ma...

Kseniya Leshchenko: Shared development support service model as the way to ma...

Set off and carry forward of losses and assessment of individuals.pptx

Set off and carry forward of losses and assessment of individuals.pptx

falcon-invoice-discounting-a-premier-platform-for-investors-in-india

falcon-invoice-discounting-a-premier-platform-for-investors-in-india

Exploring Patterns of Connection with Social Dreaming

Exploring Patterns of Connection with Social Dreaming

ModelingMarketingStrategiesMKS.CollumbiaUniversitypdf

ModelingMarketingStrategiesMKS.CollumbiaUniversitypdf

LA HUG - Video Testimonials with Chynna Morgan - June 2024

LA HUG - Video Testimonials with Chynna Morgan - June 2024

High performance pipelined architecture of elliptic curve scalar multiplication over gf(2m)

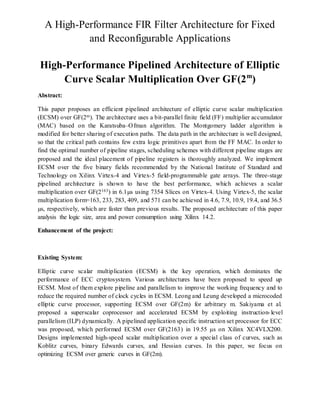

- 1. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications High-Performance Pipelined Architecture of Elliptic Curve Scalar Multiplication Over GF(2m ) Abstract: This paper proposes an efficient pipelined architecture of elliptic curve scalar multiplication (ECSM) over GF(2m). The architecture uses a bit-parallel finite field (FF) multiplier accumulator (MAC) based on the Karatsuba–Ofman algorithm. The Montgomery ladder algorithm is modified for better sharing of execution paths. The data path in the architecture is well designed, so that the critical path contains few extra logic primitives apart from the FF MAC. In order to find the optimal number of pipeline stages, scheduling schemes with different pipeline stages are proposed and the ideal placement of pipeline registers is thoroughly analyzed. We implement ECSM over the five binary fields recommended by the National Institute of Standard and Technology on Xilinx Virtex-4 and Virtex-5 field-programmable gate arrays. The three-stage pipelined architecture is shown to have the best performance, which achieves a scalar multiplication over GF(2163) in 6.1µs using 7354 Slices on Virtex-4. Using Virtex-5, the scalar multiplication form=163, 233, 283, 409, and 571 can be achieved in 4.6, 7.9, 10.9, 19.4, and 36.5 µs, respectively, which are faster than previous results. The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2. Enhancement of the project: Existing System: Elliptic curve scalar multiplication (ECSM) is the key operation, which dominates the performance of ECC cryptosystem. Various architectures have been proposed to speed up ECSM. Most of them explore pipeline and parallelism to improve the working frequency and to reduce the required number of clock cycles in ECSM. Leong and Leung developed a microcoded elliptic curve processor, supporting ECSM over GF(2m) for arbitrary m. Sakiyama et al. proposed a superscalar coprocessor and accelerated ECSM by exploiting instruction-level parallelism (ILP) dynamically. A pipelined application specific instruction set processor for ECC was proposed, which performed ECSM over GF(2163) in 19.55 μs on Xilinx XC4VLX200. Designs implemented high-speed scalar multiplication over a special class of curves, such as Koblitz curves, binary Edwards curves, and Hessian curves. In this paper, we focus on optimizing ECSM over generic curves in GF(2m).

- 2. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Some designs duplicate arithmetic blocks to maximize the parallelism in ECSM. For GF(2163), Kim et al. used three Gaussian normal basis multipliers to achieve ECSM in 10 μs on Xilinx XC4VLX80. Zhang et al. developed three finite-field (FF) cores and a main controller to achieve ECSM in 7.7 μs on Xilinx XC4VLX80. The best design in performed ECSM in 5.5 μs on Xilinx Virtex-5 using three digit-serial FF multipliers and one FF divider. Despite high speed, these deigns require massive logic resources, and thus, they are not practical for FPGA implementation. Considering the tradeoff between area and speed, many designs use word-serial or digit-serial FF multipliers to implement ECSM. These designs usually require a large number of clock cycles for a scalar multiplication. Ansari and Hasan proposed an efficient scheme, which kept the pseudopipelined word-serial FF multiplier working without idle cycles. A scalar multiplication over GF(2163) costs 4050 clock cycles and 21 μs on Xilinx XC4VLX200. FF multipliers with different word sizes (w) were developed, and the best design with w = 55 performed ECSM over GF(2163) in 2751 clock cycles and 9.6 μs on Xilinx XC4VLX200. Disadvantages: Area coverage is high Performance speed is slow Proposed System: Data Dependence Analysis of ECSM The modified Montgomery ladder scalar multiplication totally takes m(6M + 5S + 3A) + (11M + 5A + I) operations, where M, S, A, and I denote multiplication, square, addition, and inversion in GF(2m), respectively, and m is the dimension of the binary field GF(2m). The original Montgomery ladder scalar multiplication requires (m − 1)(6M + 5S + 3A) + (10M +7A+3S+ I) operations. The increased operations are due to the merged initialization and the modified postprocess for better sharing the data path with the main loop. As square and addition are much cheaper than multiplication, and inversion occurs only once, we can see that optimizing operations in the main loop, especially the FF multiplication, is the key to realize high- performance ECSM.

- 3. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 1. Data dependence graph of (a) point addition and (b) point doubling in the Montgomery ladder algorithm. Each iteration in the main loop performs point addition and point doubling, which take 6M + 5S + 3A together. The data dependence of point addition and doubling in the Montgomery ladder algorithm is shown in Fig. 1. The critical path lies in calculating the X-coordinate of point addition, which takes 2M + 1S + 2A, as is shaded in Fig. 1. Thus, it may use at most three FF multipliers to achieve maximum parallelism in scalar multiplication. PROPOSED ARCHITECTURE OF ELLIPTIC CURVE SCALAR MULTIPLICATION: we propose the high-performance architecture based on the improved Montgomery ladder scalar multiplication algorithm, as shown in Fig. 2.

- 4. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 2. Proposed architecture of ECSM. The proposed ECSM architecture consists of one bit-parallel FF MAC, one FF squarer, a register bank, a finite-state machine, and a 6 × 18 control ROM. The FF MAC is implemented using the Karatsuba–Ofman algorithm, and is well pipelined. The n-stage pipelined FF MAC takes n clock cycles to finish one multiplication. The FF squarer is not pipelined, and one clock cycle is required to finish one square. The inputs to FF MAC, A, B, and C, and the input to FF squarer, S, are all registered. Another four registers T1, T2, T3, and T4 are used in the data path for data caching.

- 5. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 3. Data path of ECSM using a three-stage pipelined FF MAC. The data path of ECSM using a three-stage pipelined FF MAC is given for example in Fig. 6. The terms X1, X2, Z1, and Z2 are not presented, because they are the intermediate results of the FF MAC or FF Squarer. The bold dashed line in Fig. 6 shows the critical path of the three-stage pipelined architecture, which consists of a pipelined FF MAC, an addition (XOR), and a 4:1 MUX. Data paths with other pipeline stages are similar to Fig. 6 except for different data connections. Control signals stored in the control ROM are also different. But, the critical path delay remains unchanged. Advantages: Area reduction Speed is increased

- 6. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Software implementation: Modelsim Xilinx ISE