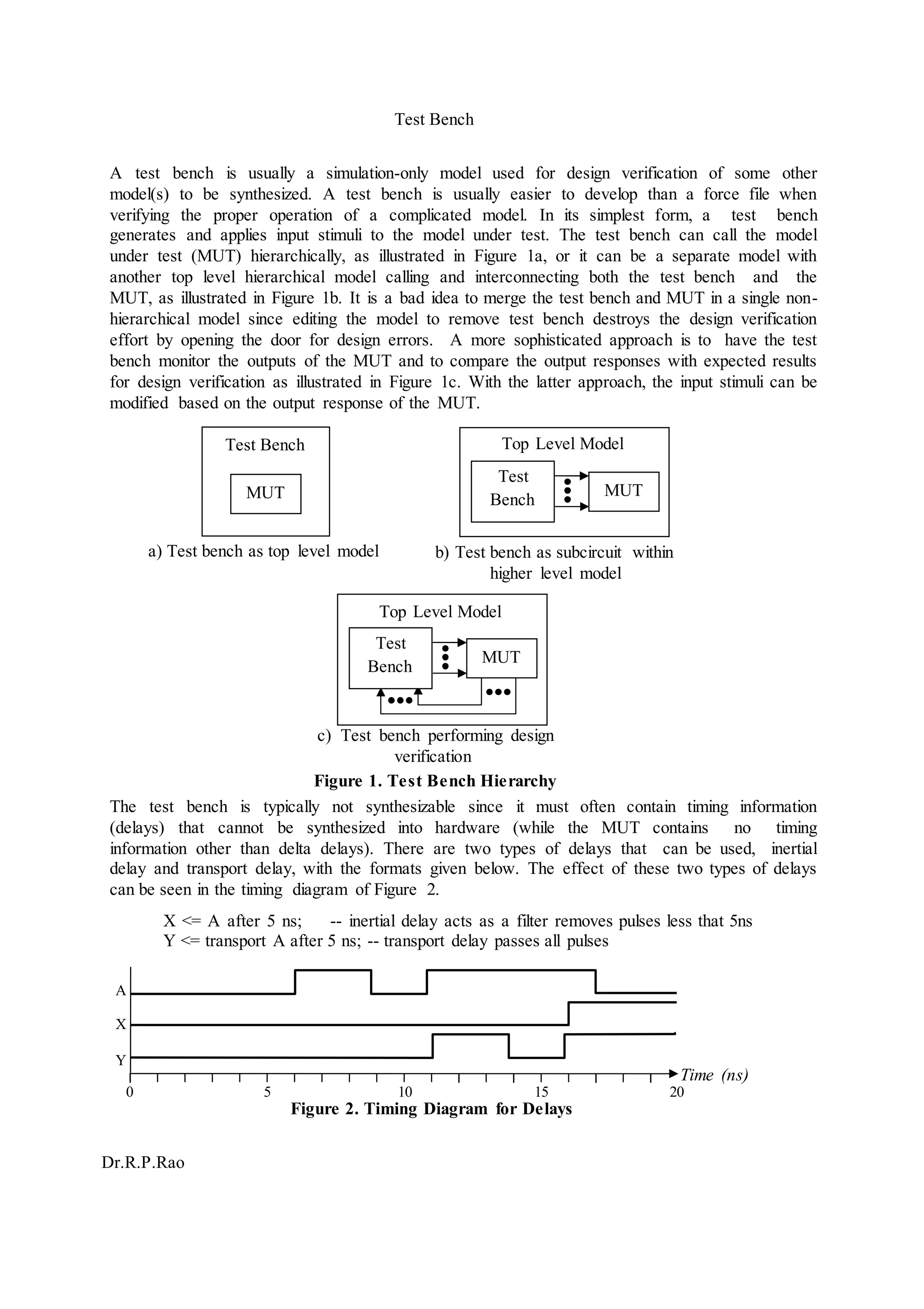

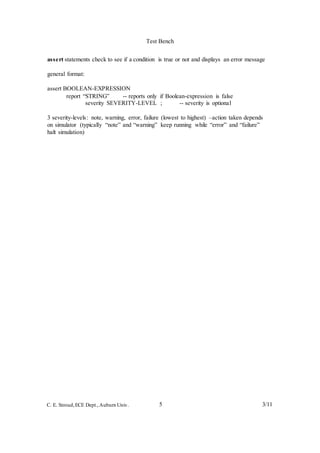

The document describes a test bench used for design verification of other models. A test bench generates and applies input stimuli to the model under test (MUT) and monitors the MUT's outputs to verify proper operation by comparing responses to expected results. The document provides examples of simple test benches that apply test patterns to a MUT and a more sophisticated test bench that reads input stimuli from a file and writes output responses to a file for verification.