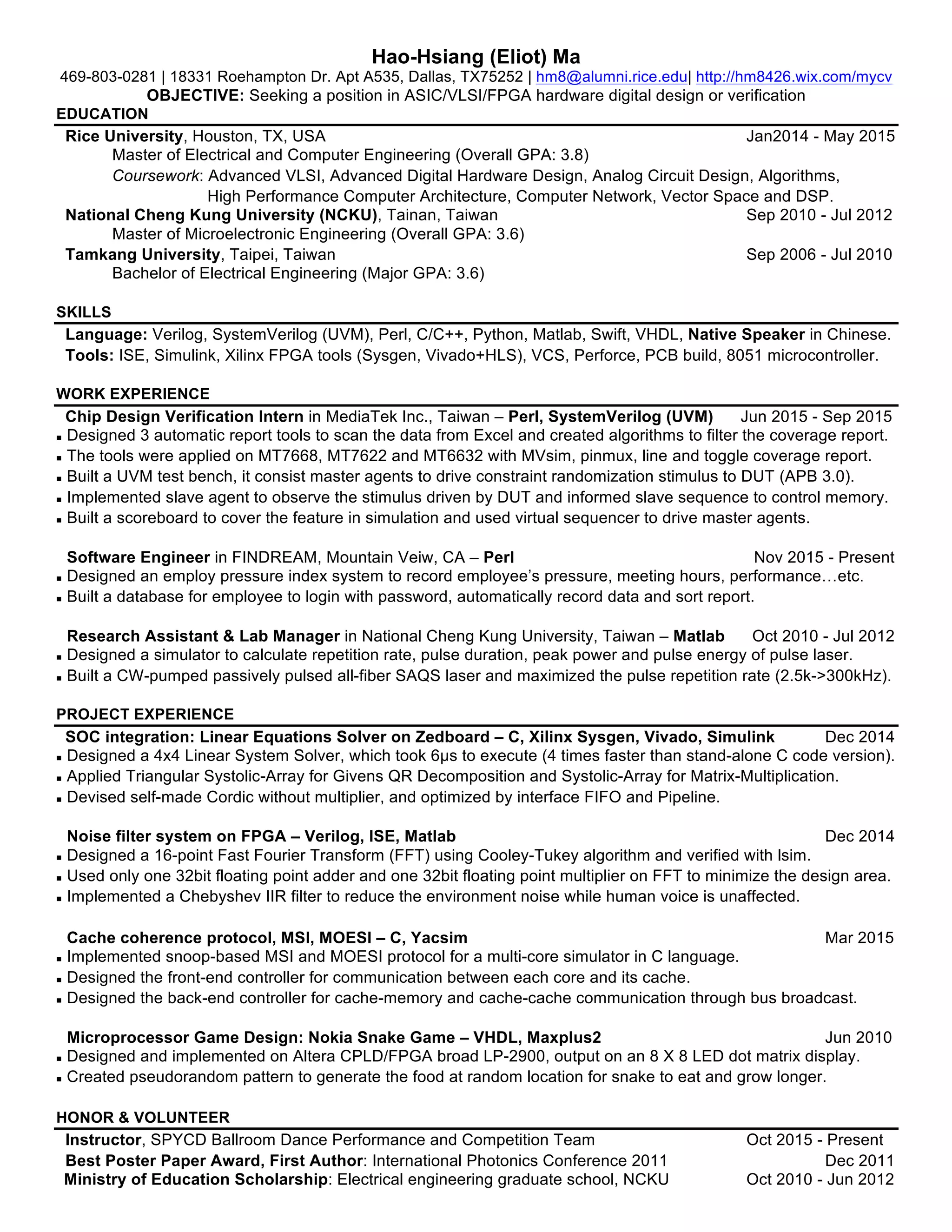

Hao-Hsiang Ma is seeking a position in ASIC/VLSI/FPGA hardware design or verification. He has a Master's degree in Electrical and Computer Engineering from Rice University and previous degrees from National Cheng Kung University and Tamkang University in Taiwan. He has skills in Verilog, SystemVerilog, C/C++, and FPGA tools. His work experience includes internships at MediaTek doing verification and as a software engineer at FINDREAM. He has also completed projects involving linear equation solvers on FPGA boards, noise filtering, and cache coherence protocols.