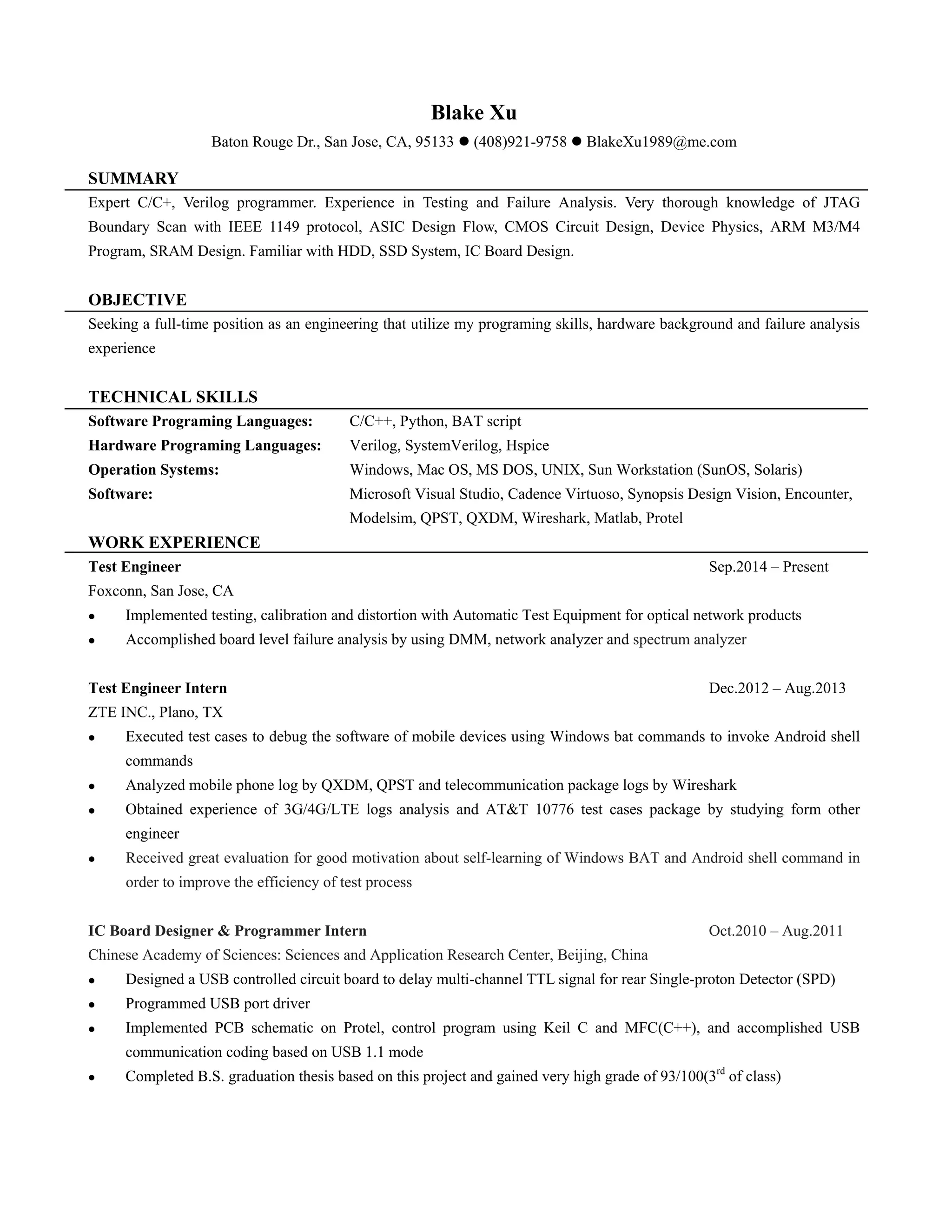

This document is a resume for Blake Xu summarizing his background and experience. He has expertise in C/C++ and Verilog programming along with experience in testing and failure analysis. His technical skills include software languages like C/C++ and Python as well as hardware languages like Verilog and SystemVerilog. He has worked as a test engineer and interned as a test engineer and IC board designer. He holds a Master's degree in Electrical and Electronics Engineering and a Bachelor's degree in Applied Physics.