This document describes a digital VLSI circuit design project created by two students for a course. The project uses Verilog and ModelSim to design a circuit that performs multiple functions including multiplication and addition. Modules were created for common components like AND gates, OR gates, half adders, and full adders. A test bench was developed to simulate inputs and verify the correct outputs were produced. Simulation results confirmed the circuit was functioning as intended.

![4054 Digital VLSI Circuit Design -- Final Project Dayus & Ferguson

1

Design Specifications:

The Arithmetic Logic Unit (ALU) was designed having two, four-bit inputs (A [3:0] and B [3:0])

that were to be used for one of four operations. The project operates each of the modules

corresponding to a two-bit selection input (ALU_OP [1:0]) displayed in table 1. The arithmetic

operations are: bit-wise ‘or’, ‘and’, ‘addition’ and ‘multiplication’. These functions cause the unit

to have an eight-bit output (Dout [7:0]) with a single bit carry out (Cout). The ALU will be a

synchronized system where the inputs and outputs are synchronized with respect to the same

clock signal.

Operation ALU_OP Operation Performed

AND(bitwise) 00 Dout = A&B

OR(bitwise) 01 Dout = A|B

ADDITION 10 Dout = A+B

MULTIPLICATION 11 Dout = A*B

Table 1 - ALU Operation

The ‘and’, ‘or’, and ‘addition’ operations are implemented with structural logic, whereas the

‘multiplication’ operation was implemented by utilizing the add and shift technique. The ‘and’,

‘or’, and ‘addition’ functions will only use the first four bits of the output (Dout). With the

exception of the ‘addition’ function, which will contain an extra Cout bit. The Multiplication

module is the only function that will use the entire eight-bit output.](https://image.slidesharecdn.com/23524347-2c12-439f-8c65-da1ac896b881-170105145407/85/Example-Report-VLSI-6-320.jpg)

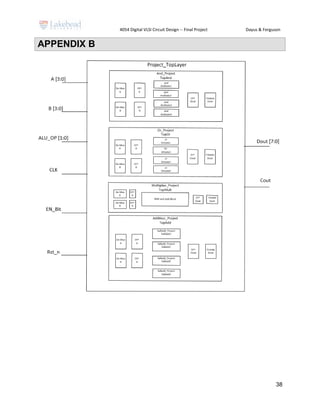

![4054 Digital VLSI Circuit Design -- Final Project Dayus & Ferguson

15

Figure 20 - General Structure of the Addition Module

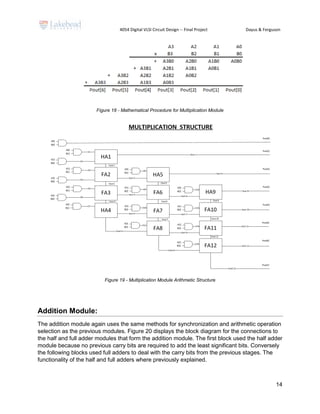

Figure 20 illustrates an example calculation of A = 5 and B =7 in the addition module.

1. In Module halfadd1, the least significant bits are logically ‘xor’ together to get

Sum_Add[0] = 0 then logically ‘and’ together to get Cout1 = 1.

2. In the fulladd1 block, input B_Sync_Add[1] =1 which is ‘xor’ with the carry in bit from the

previous stage resulting in Sum_Add[1] = 0 and Cout2=1.

3. In the module fulladd2 all inputs are true and the carry in bit is true therefore

Sum_Add[2] = 1 and Cout3 =1.

4. Finally both inputs are false however the carry bit is true in module fulladd3 which results

in Sum_Add[3] = 1 and Cout=0.

Figure 21 - Addition Module Example Calculation](https://image.slidesharecdn.com/23524347-2c12-439f-8c65-da1ac896b881-170105145407/85/Example-Report-VLSI-20-320.jpg)

![4054 Digital VLSI Circuit Design -- Final Project Dayus & Ferguson

39

References:

[1]N. Weste and D. Harris, CMOS VLSI Design - A Circuit and System Persective, 4th ed.

Boston: Pearson Education, 2011.

[2]"DFF", En.wikipedia.org, 2016. [Online]. Available: https://en.wikipedia.org/wiki/DFF.

[Accessed: 27- Nov- 2016].

[3]"Multiplexer", En.wikipedia.org, 2016. [Online]. Available:

https://en.wikipedia.org/wiki/Multiplexer. [Accessed: 27- Nov- 2016].

[4] Lee, "Vector Boolean Algebra and Calculus", IEEE Transactions on Computers, vol. -25, no.

9, pp. 865-874, 1976.

[5]"Verilog® quickstart", Computers & Mathematics with Applications, vol. 35, no. 5, p. 133,

1998.

[6]"What's a Tri-state Buffer?", Cs.umd.edu, 2016. [Online]. Available:

https://www.cs.umd.edu/class/sum2003/cmsc311/Notes/CompOrg/tristate.html. [Accessed: 27-

Nov- 2016].

[7]D. Chen, "ECE 425 - Intro to VLSI System Design", Courses.engr.illinois.edu, 2016. [Online].

Available: https://courses.engr.illinois.edu/ece425/. [Accessed: 28- Nov- 2016].

[8]"Demultiplexer(Demux)", Electronics Hub, 2016. [Online]. Available:

http://www.electronicshub.org/demultiplexerdemux/. [Accessed: 28- Nov- 2016].

[9]"Monostables", Learnabout-electronics.org, 2016. [Online]. Available: http://www.learnabout-

electronics.org/Digital/dig55.php. [Accessed: 28- Nov- 2016].](https://image.slidesharecdn.com/23524347-2c12-439f-8c65-da1ac896b881-170105145407/85/Example-Report-VLSI-44-320.jpg)