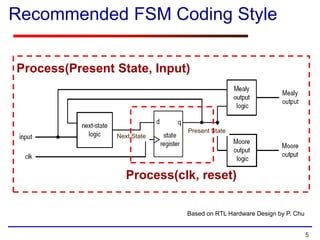

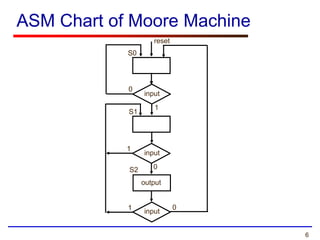

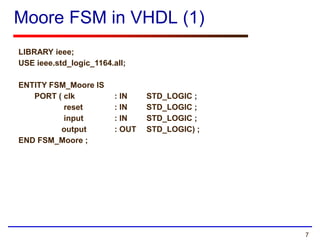

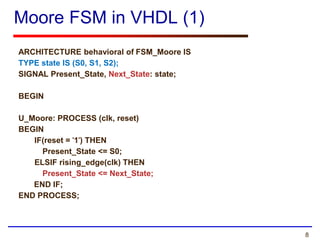

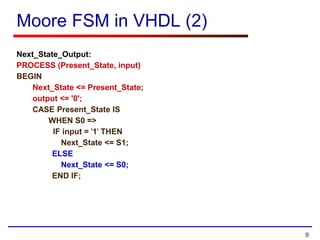

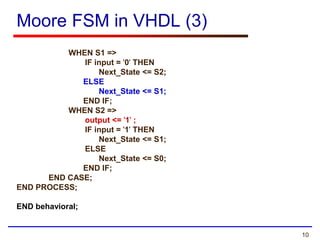

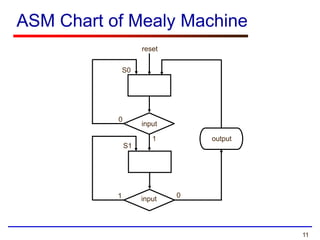

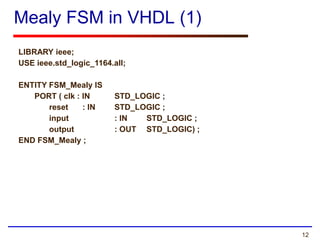

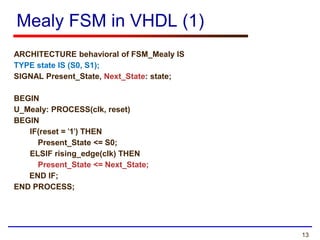

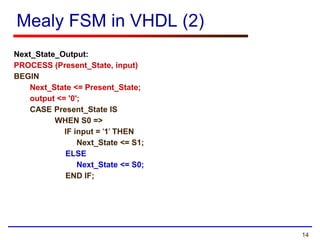

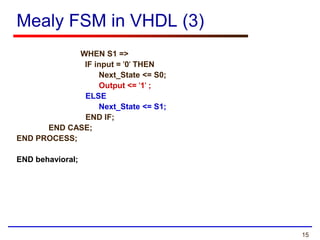

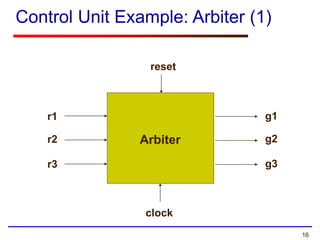

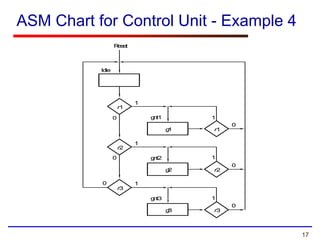

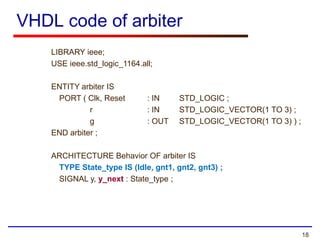

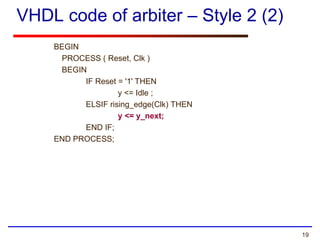

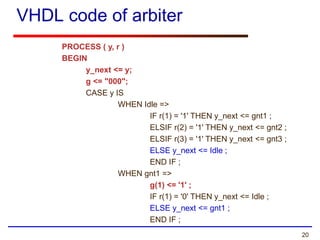

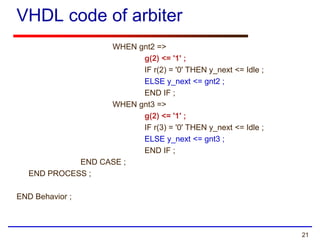

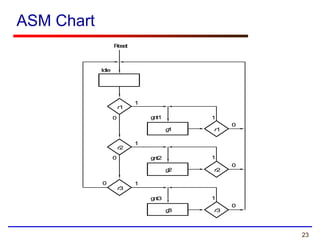

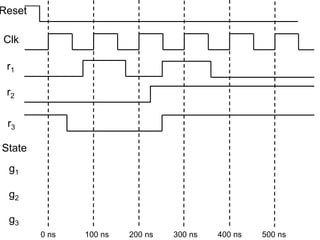

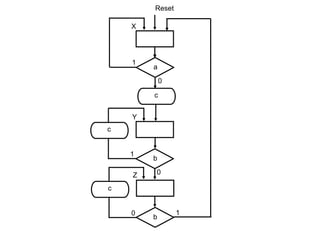

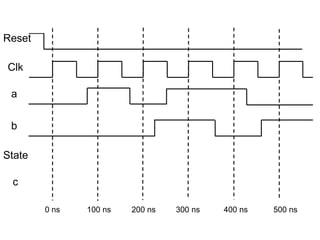

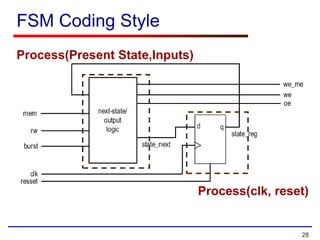

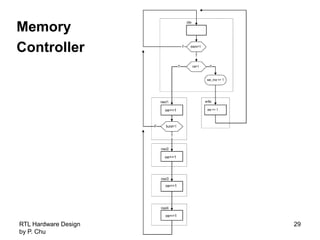

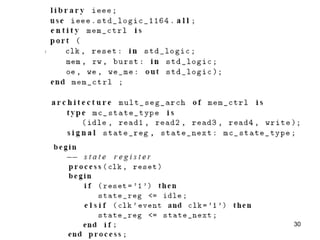

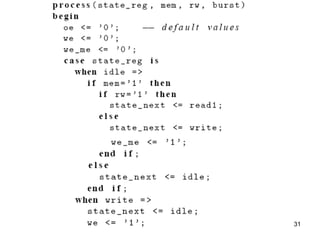

This document discusses finite state machines (FSM) and algorithmic state machine (ASM) charts. It provides examples of Moore and Mealy FSM implementations in VHDL, including ASM charts and VHDL code. It also provides an example of an arbiter control unit design using an ASM chart and VHDL code. Recommended reading materials on FSMs and ASM charts in VHDL are listed.