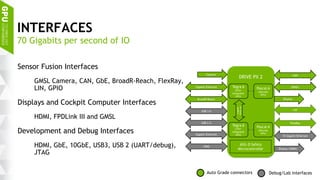

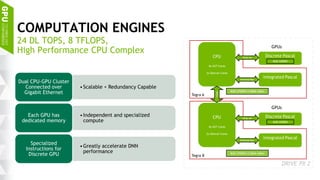

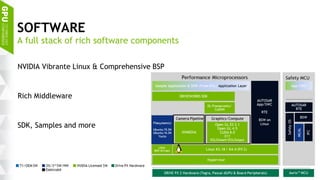

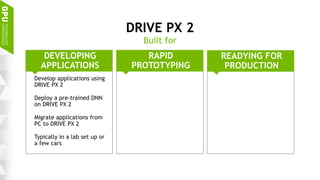

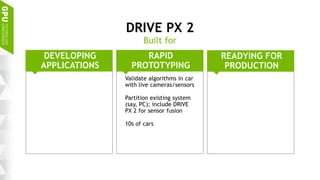

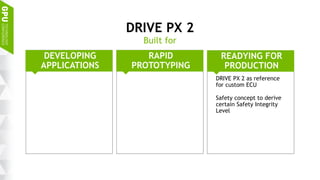

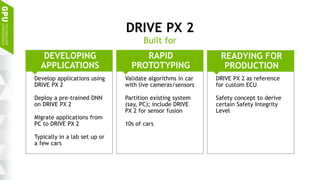

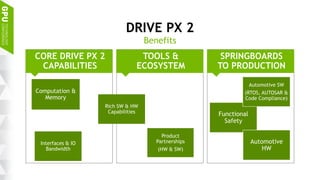

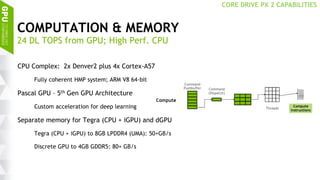

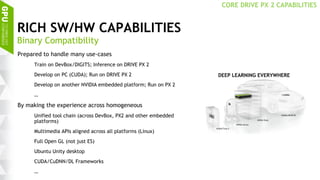

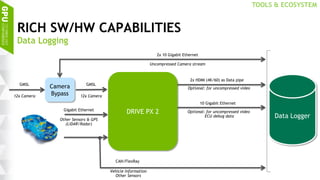

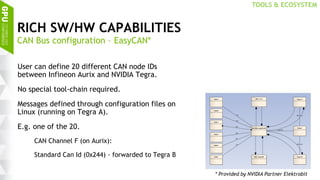

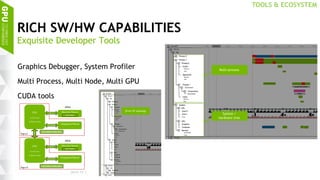

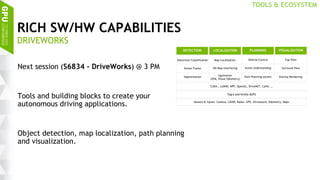

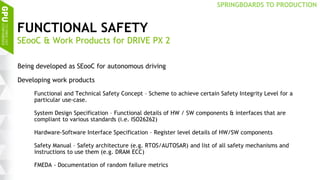

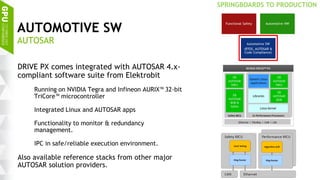

The document describes NVIDIA's DRIVE PX 2, an AI supercomputer purpose-built for self-driving cars. It has 12 CPU cores, a Pascal GPU providing 8 TFLOPS of processing power and 24 DL TOPS for deep learning. The DRIVE PX 2 features various interfaces to connect to sensors, displays and development tools. It also includes software like NVIDIA DRIVEWORKS and supports AUTOSAR for automotive software development. The DRIVE PX 2 is designed to help developers create self-driving applications and migrate them from testing to production vehicles.