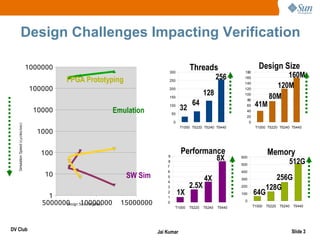

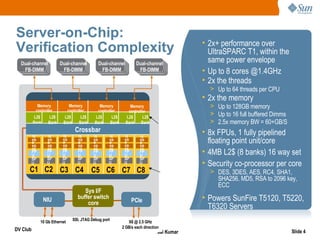

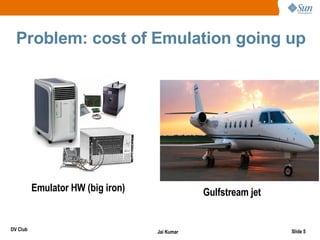

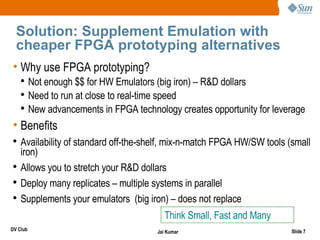

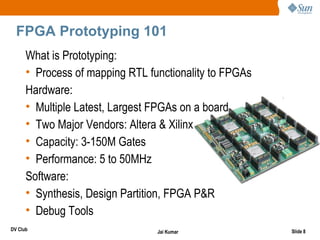

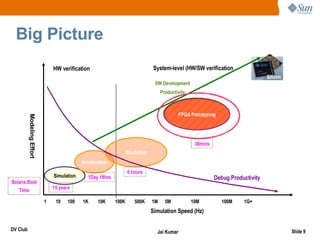

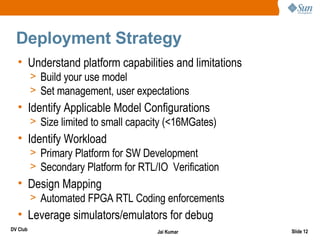

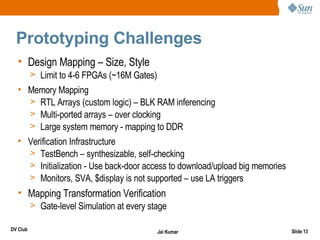

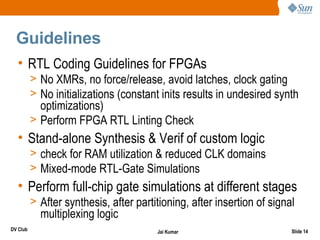

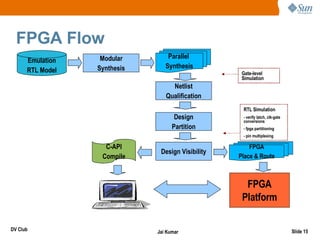

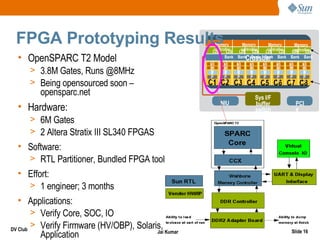

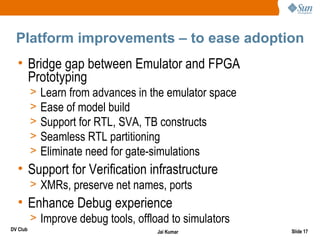

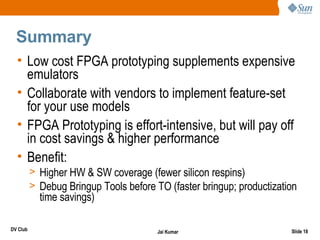

This document discusses leveraging low-cost FPGA prototyping for validation of highly threaded server-on-chip designs. It outlines the increasing verification challenges for such designs due to their large size, high performance, and number of threads. FPGA prototyping provides faster simulation speeds compared to software simulation and emulation for validating complex multi-core, multi-threaded server-on-chip designs. The document provides guidelines on FPGA prototyping and discusses the results and benefits it can provide for both engineering teams and management.