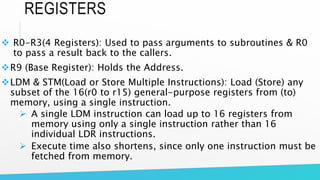

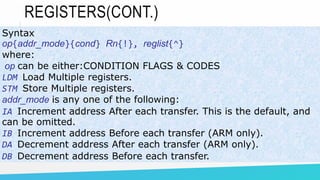

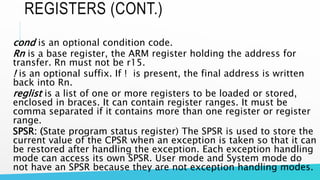

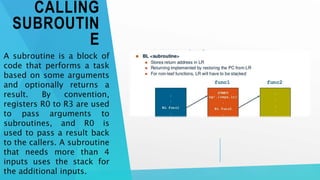

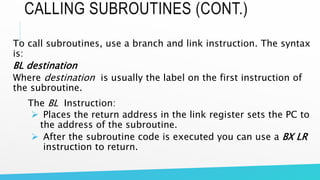

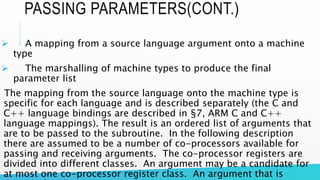

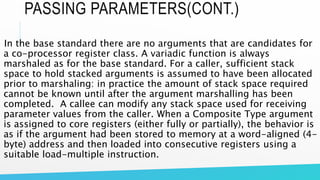

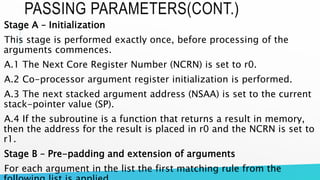

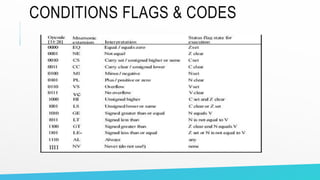

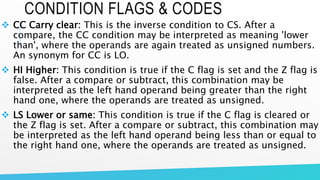

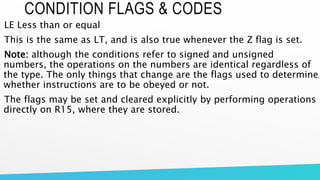

The document provides a detailed overview of subroutines, functions, and parameter passing in programming, primarily focusing on the ARM architecture. It defines key terminologies, describes different types of functions and their implementation, and discusses registers and condition codes crucial for subroutine execution. Furthermore, it outlines the specifics of calling subroutines, including the use of stack and core registers for parameter passing.