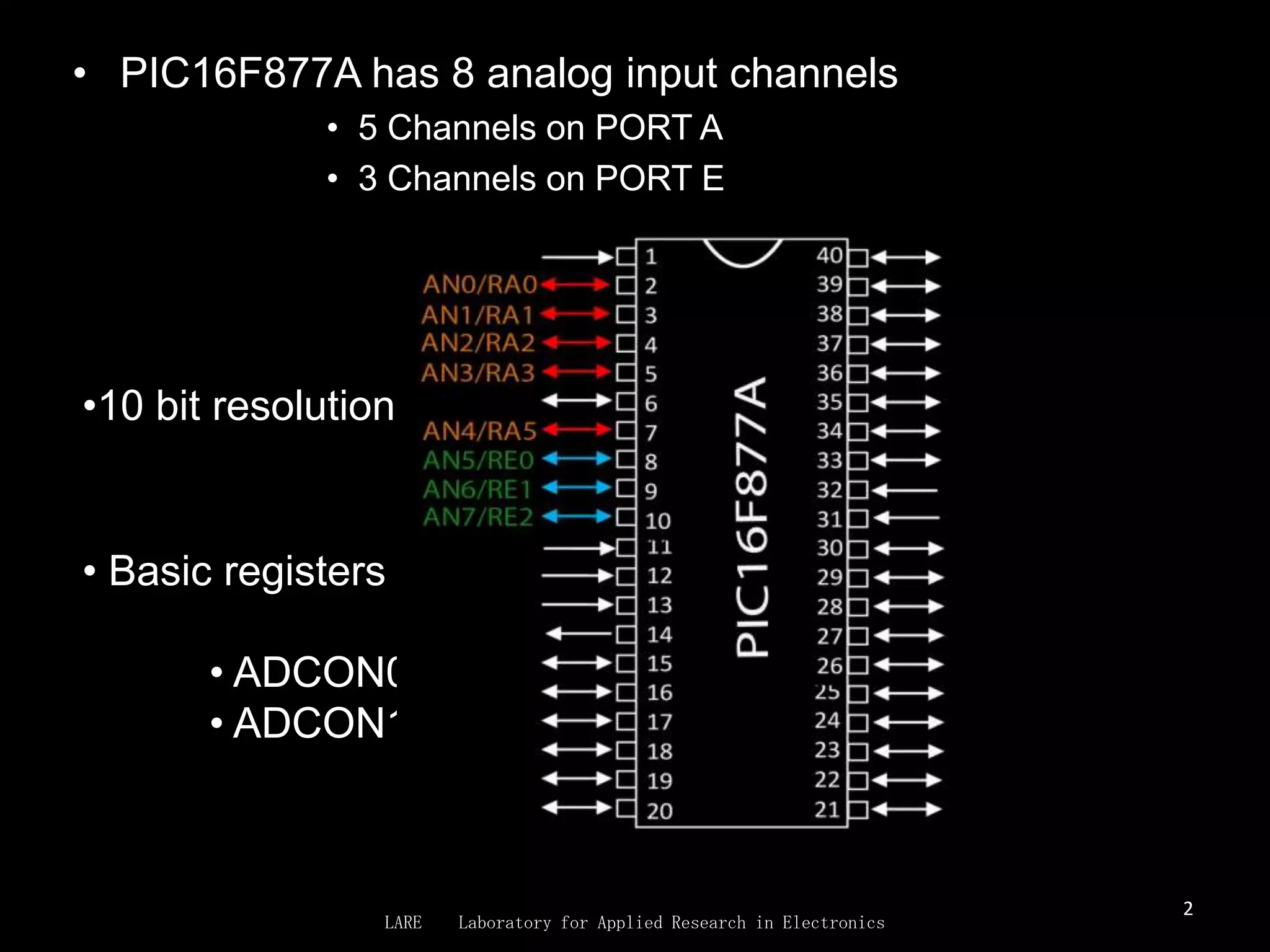

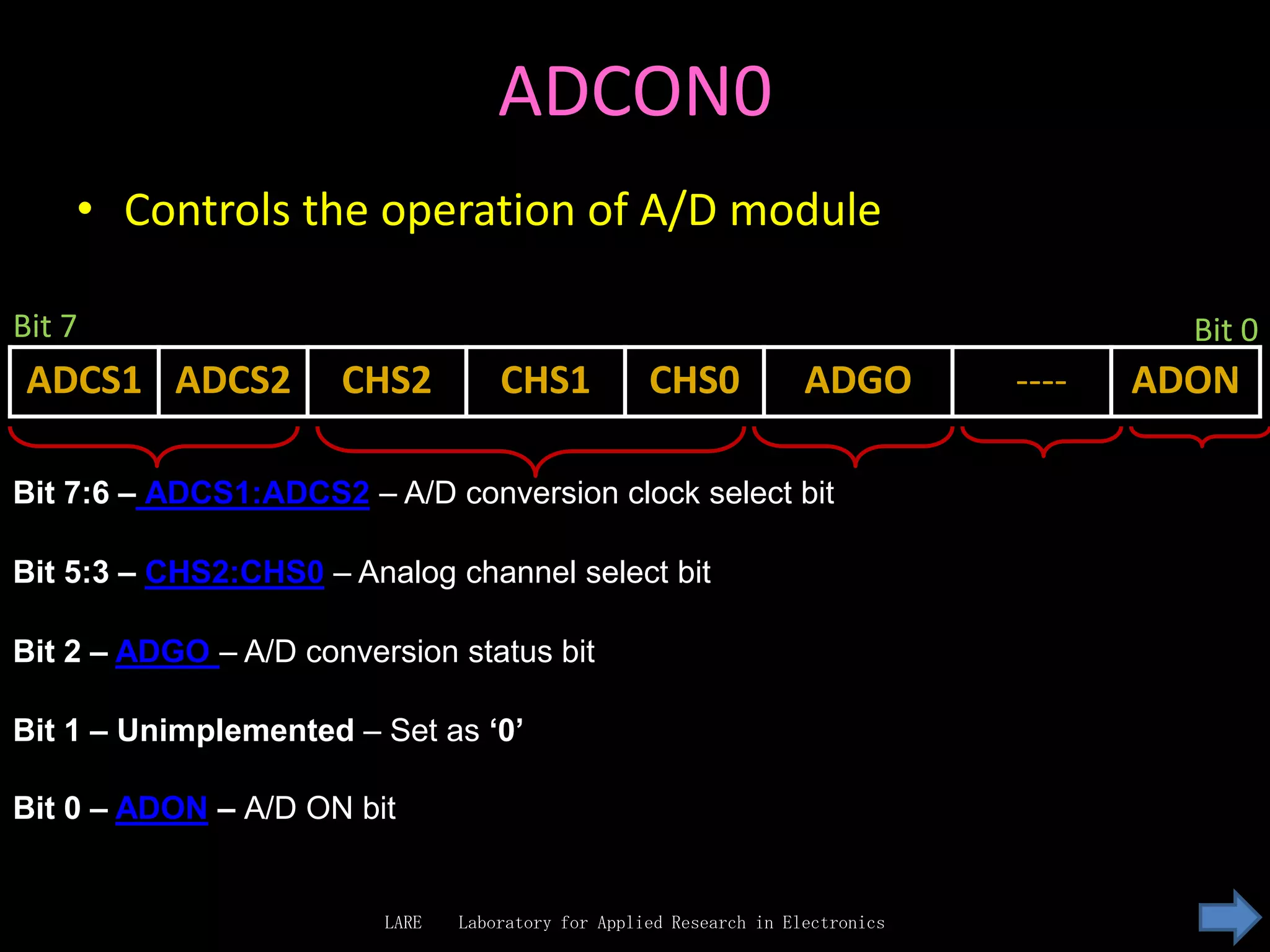

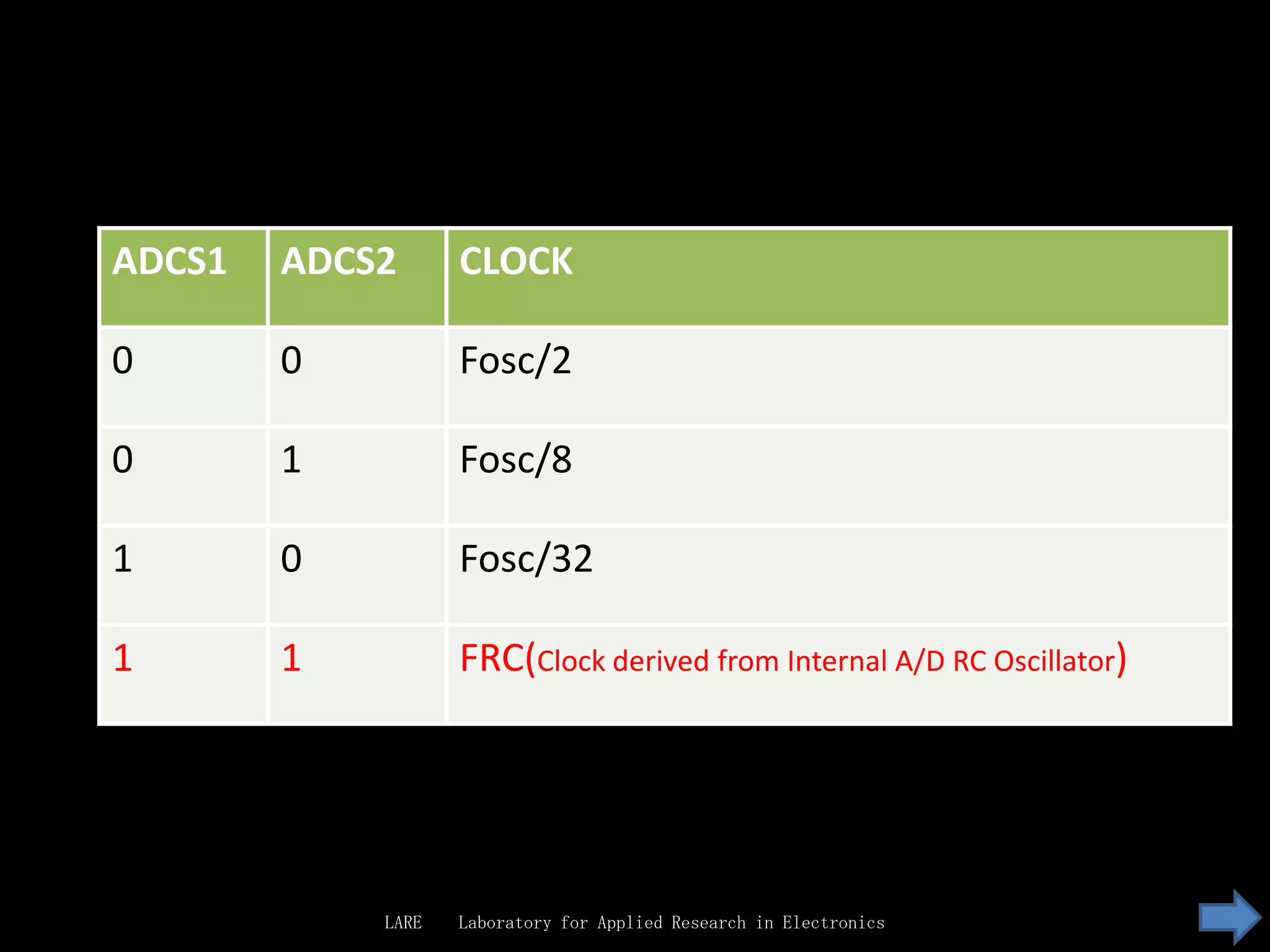

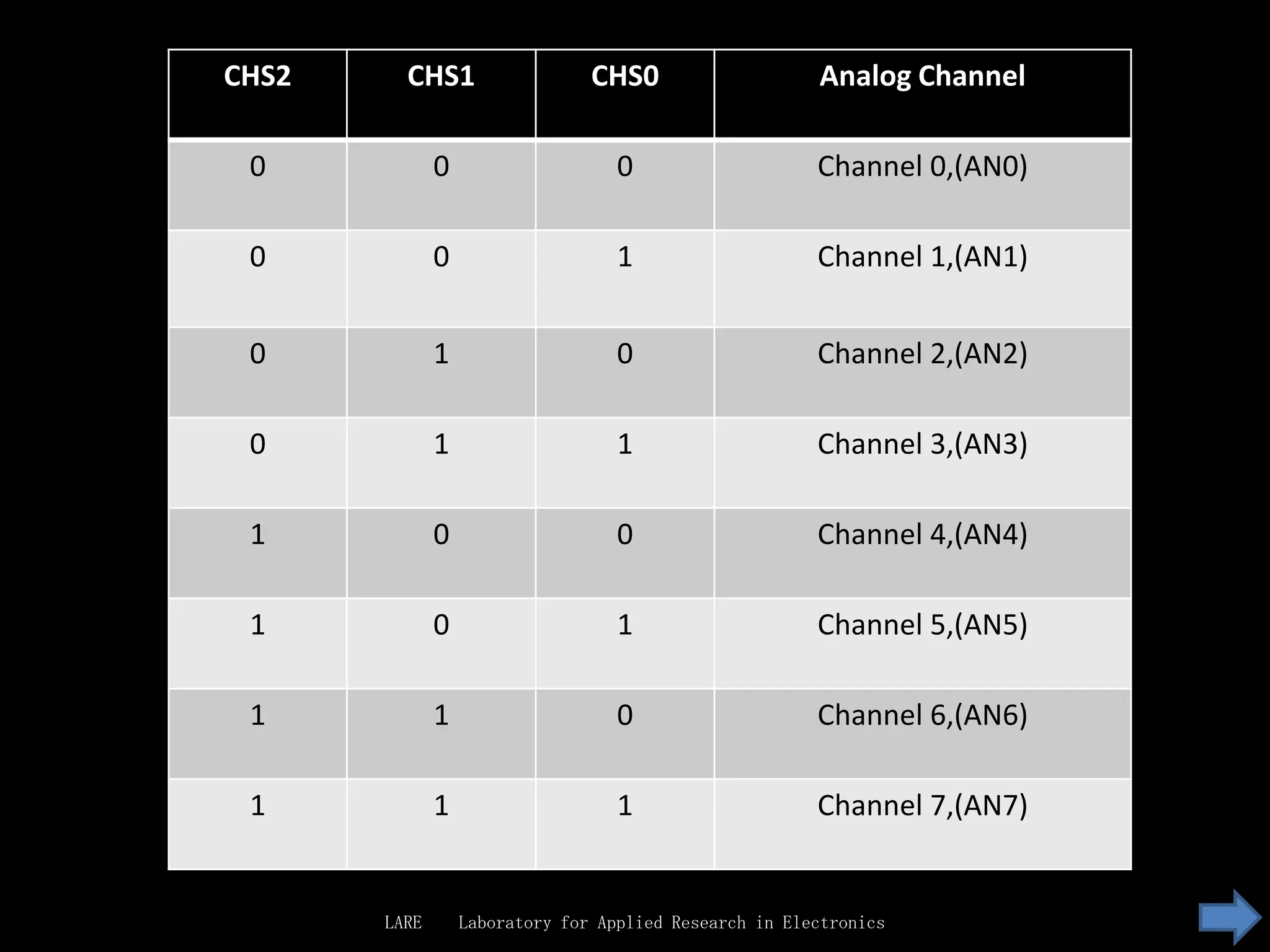

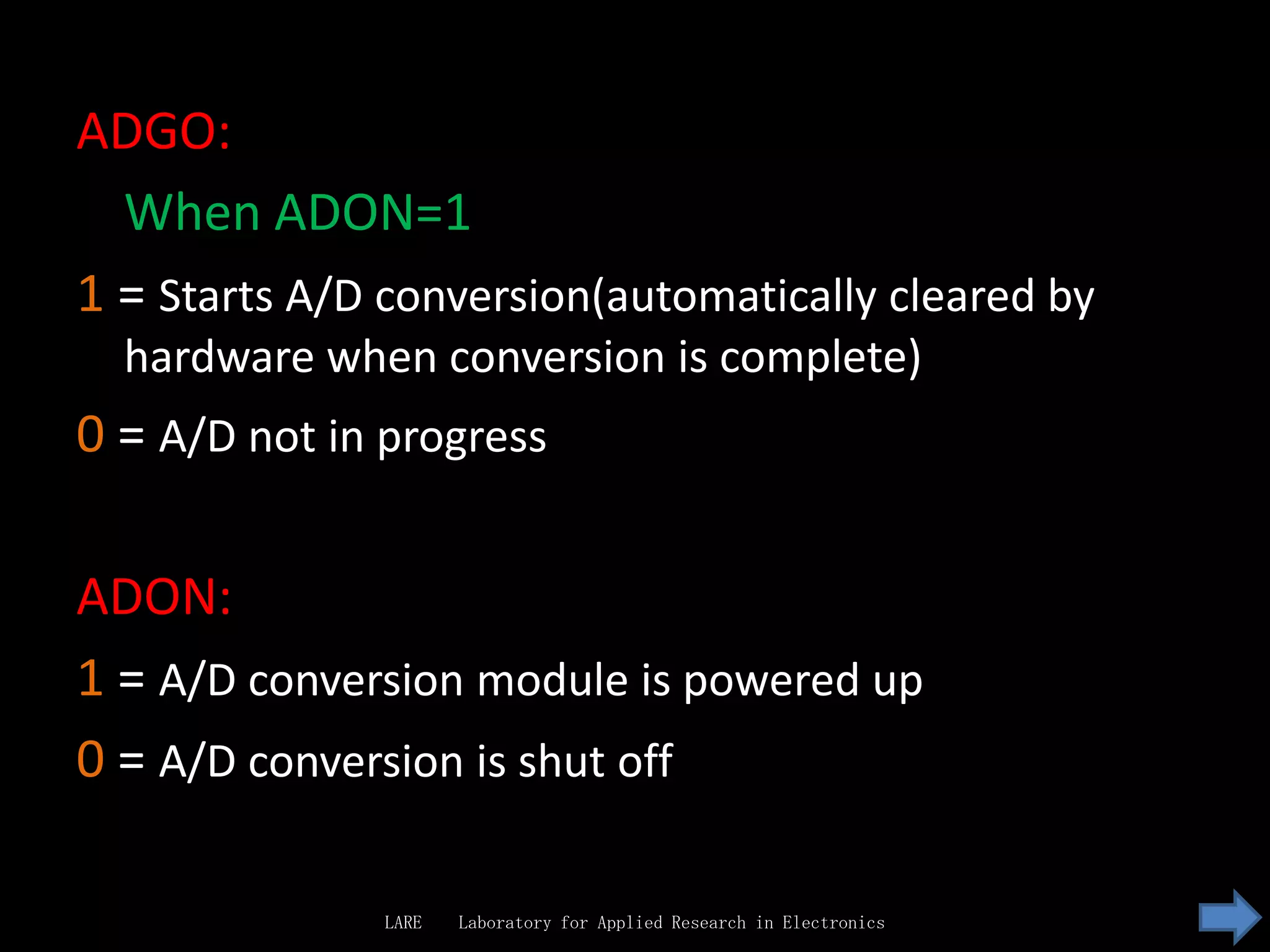

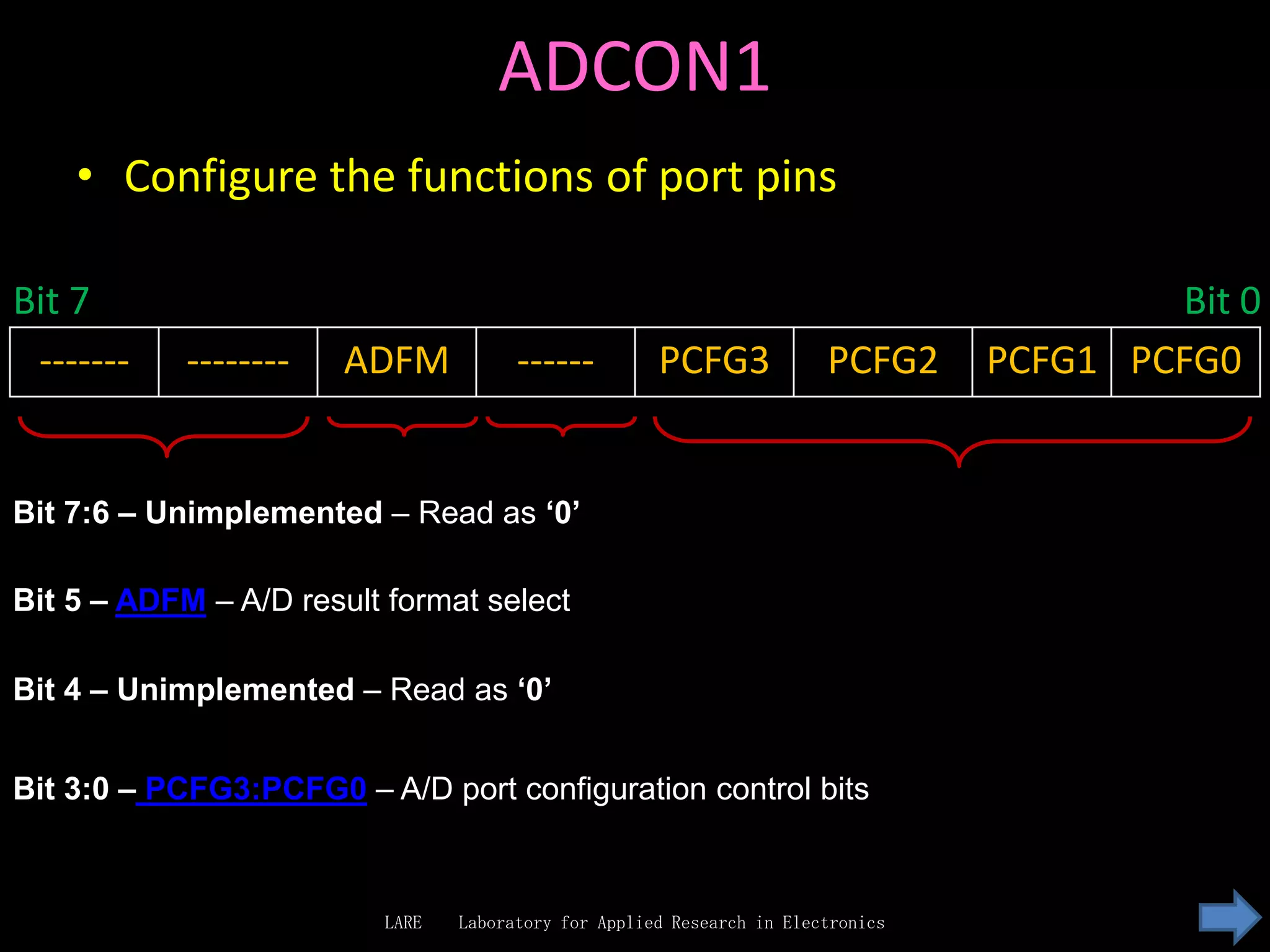

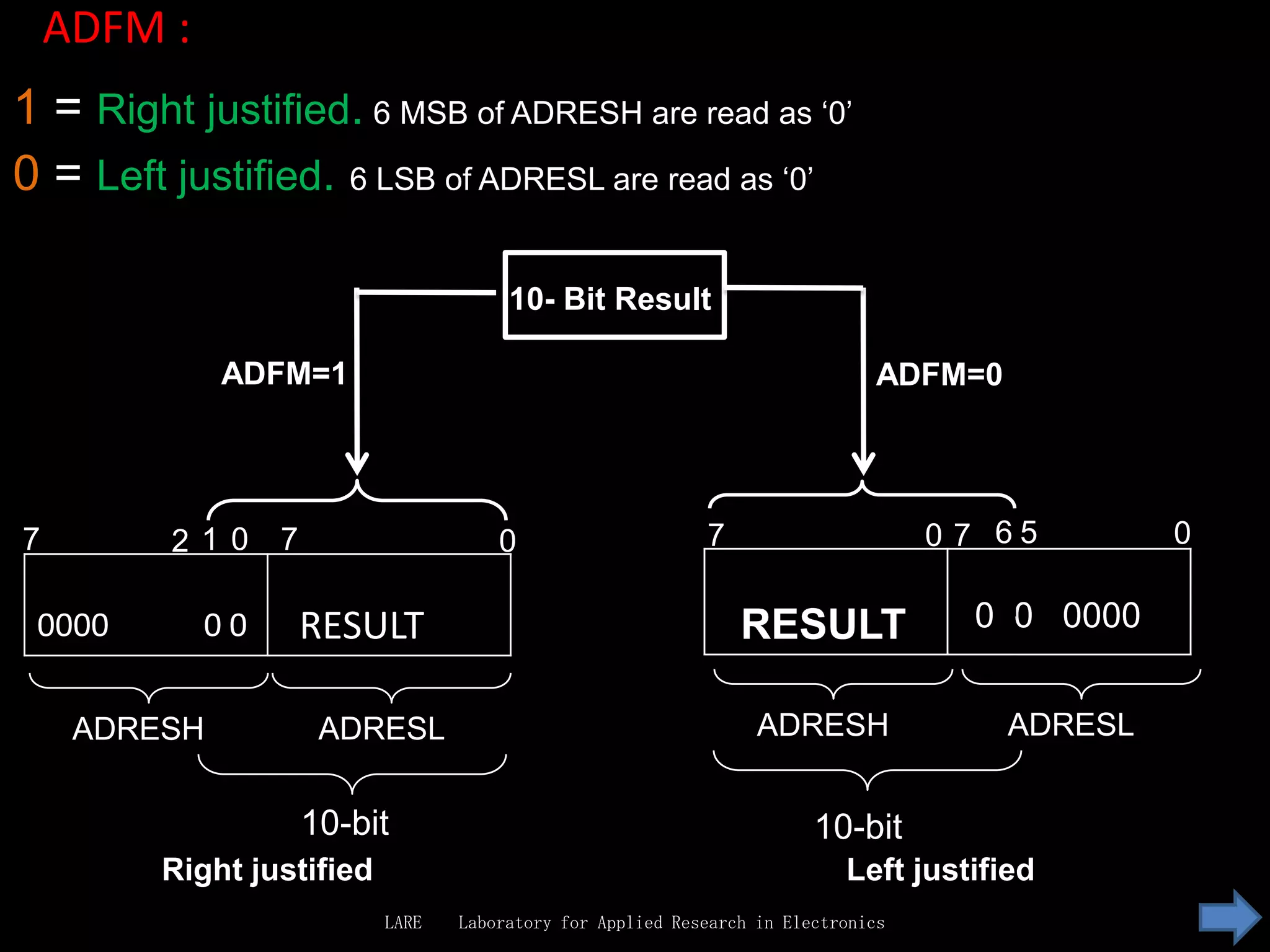

The document discusses the analog to digital converter (ADC) functionality of the PIC16F877A microcontroller. It has 8 analog input channels, with 5 on PORTA and 3 on PORTE. It has a 10-bit resolution. The basic registers used for ADC conversion are ADCON0 and ADCON1. ADCON0 controls ADC operation and channel selection. ADCON1 configures port pin functions.