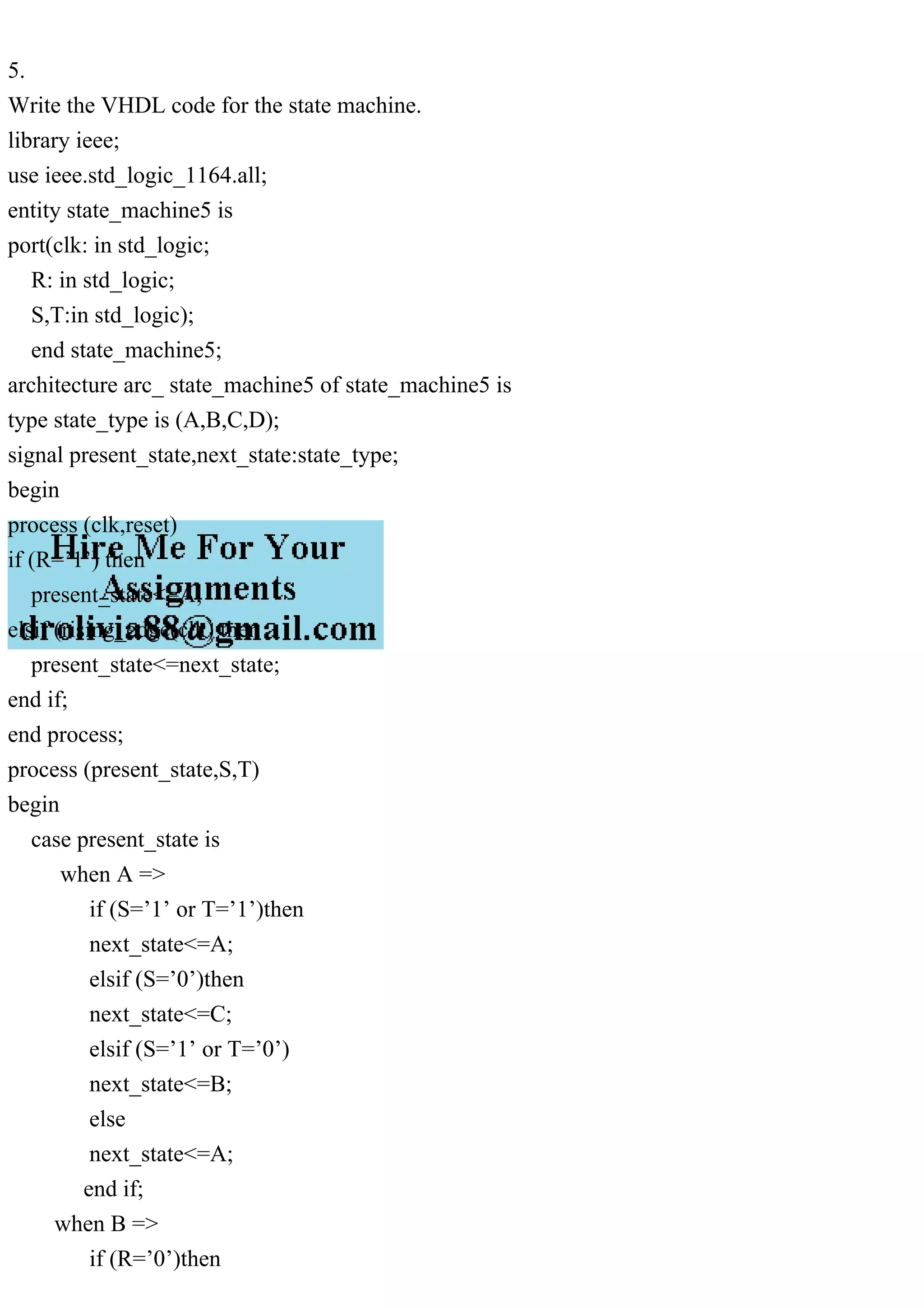

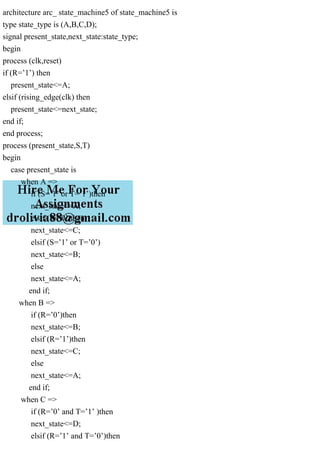

The document provides a VHDL code implementation for a state machine with four states (a, b, c, d) and describes the behavior of state transitions based on input signals. It includes processes for managing the current and next state based on clock and reset signals, as well as a test bench to simulate and validate the state machine's performance. The architecture and overall structure enable the design and simulation of the state machine effectively.