This document describes the design and simulation of a two-stage differential operational amplifier (op-amp) integrator in 180nm CMOS technology. It discusses the stability analysis of op-amps using gain and phase margin curves. The circuits were simulated and analyzed at different bias voltages. The unity gain bandwidth of the op-amp was 15MHz at 0.7V and 21MHz at 0.4V, with power consumptions of 7.158mW and 6.998mW respectively. The power of the integrator circuit was 7.844mW when operated at a frequency of 10kHz. Simulation results showed the circuits had positive gain and phase margins, indicating stability.

![Design and Simulation of High Stability 2-Stage

Differential Op-Amp Integrator in 180nm CMOS

Technology

Anu1

, Amit Kumar2

and Neeraj Kr. Shukla3

VLSI Design Group, Department of Electrical, Electronics & Communication Engineering

ITM University, Gurgaon (Haryana), India

Abstract— Integrator is an Op-Amp circuit application which does the mathematical

operation of integration, i.e. the output voltage is proportional to the integral of input

voltage. The stability of Op-Amp circuit is analyzed by Gain and Phase Margin curves. This

paper also discusses the power consumption of Op-Amp as well as Integrator analog circuit.

The circuits are simulated and analyzed at 180nm standard CMOS process. The Gain-

Bandwidth product of Operational Amplifier is analyzed at different bias voltages. The

power of Integrator is 7.844mW which is evaluated by using the Op-Amp as the lower block

of the Integrator. The Unity Gain Bandwidth of Operational Amplifier is 15 MHz at 0.7V

biasing voltage and 21 MHz at 0.4V biasing voltage with power consumption of 7.158mW

and 6.998mW, respectively.

Index Terms— Gain Margin, Integrator, Low Power, Operational Amplifier, Phase Margin.

I. INTRODUCTION

Over the last few years, the electronics industry is evolving in VLSI domain where its major segment of total

worldwide sales is dominated by CMOS Chips. In CMOS chips, transistors are scaled down to small

geometries which results in higher chip density and improved functionalities. The device scaling helps to

accommodate more number of transistors in a chip in addition to lower voltage requirement and improved

speed of operation. In low-distortion applications, signals can be scaled down at the expense of lower signal

power [1]. However, with decreasing supply voltage, the conflicting requirements of large signal swing and

low distortion makes the design task more challenging design task [1].

The aim of the design methodology is to propose simple yet accurate results for the design of Op-Amp and

integrator that could be used for analog to digital converter in various applications like sensor signal

conditioning, voice-band and audio signal processing.

In the literature, the reported techniques for low-voltage and high stability circuit design [2]–[8] enabled

integrators to operate with low-voltage power supplies with certain issues with the stability. However, these

techniques have rarely resulted in low power consumption with improved stability which is required for

portable applications [9]. Double-Sampling Scheme (DSS) is one possible solution for reducing power

consumption of an integrator. However, it requires complex bootstrapping schemes in low-voltage systems

because previously proposed, non-bootstrapping design techniques such as switch Op-Amp and Op-Amp

reset-switching techniques [5]–[7] are applicable only to Single-Sampling Scheme (SSS). Dynamic-Source-

Follower Integrators [10] used low-power Switched-Capacitor Integrator which could be applied to a 2nd-

DOI: 02.ITC.2014.5.525

© Association of Computer Electronics and Electrical Engineers, 2014

Proc. of Int. Conf. on Recent Trends in Information, Telecommunication and Computing, ITC](https://image.slidesharecdn.com/525-192-198-140325041503-phpapp01/85/525-192-198-1-320.jpg)

![193

order ∑∆ modulator. At 0.18 μm CMOS technology, the Integrator offers a reduction in power dissipation

(compared with conventional Op-Amp-based Integrators) upto 9.8 μW with an input capacitance of 0.1 pF,

input frequency of 20 kHz and sampling frequency at 500 kHz.

In a CMOS based Op-Amp, circuit techniques that are fully compatible with low-voltage submicron CMOS

processes were addressed to solve the DC Gain issues with unity gain frequency, like Switched-Op-Amps

(SO) [11]–[15] and the Op-Amp-reset Switching Technique (ORST) [16][17]. However, SO circuits face a

tradeoff between speed and accuracy due to slow transients, while ORST stages have higher power

consumption and settling issues due to unity gain feedback during the reset phase [17][18].

Low Power Op-Amp Design with Current Compensation Technique [19] is used to implement a single

output two stage CMOS Op-Amp with at 1.8 V supply voltage and it is designed in 0.18μm CMOS

technology having very low power consumption with a high driving capabilities. The Op-Amp had open loop

gain of 73.57db, the Gain Bandwidth Product (GBW) as 1.094 MHz and 4.35μW power consumption at a

Phase Margin of 65.86º.

Another approach for designing of a low power Op-Amp could be done by using Class AB CMOS Fully

Differential technique [20] in which an Op-Amp has been designed in a low-cost 0.18 μm CMOS technology

with 0.8 V single voltage supply using Cadence Spectre with a BSIM3v3.2. The Op-Amp operates in the sub-

threshold operation which results in ultra low-power consumption and enhanced slew-rate. The Phase Margin

and DC open-loop gain of the Op-Amp with a load capacitance of 10 pF are 65º and 51 dB, while the

simulated unity gain frequency is 40 kHz, with a Phase Margin of 65º degrees. The power consumption of

the Operational Amplifier is 1 μW with a slew-rate of 0.12 V/μs [20].

This work comprises of five sections where section I presents introduction. Section II consists of the design

of two stage Operational Amplifier with an analysis on power and stability. The section II also sheds light on

the Integrator design using two stage differential amplifiers. Section III discusses the simulation of Op-Amp

and Integrator based on the various parameters like operating frequency, Gain Margin, Phase Margin, power

and bandwidth. Finally, the conclusions are presented in section IV.

II. TWO STAGE DIFFERENTIAL OP-AMP INTEGRATOR

Due to the continuous scaling of supply voltage and channel length, the Op-Amp design has started offering

the design challenges in terms of speed, power, gain, etc. and their tradeoffs. Gain Margin and Phase Margin

are the measures of stability in closed-loop, dynamic-control systems which indicates the absolute stability

and relative stability of the system [16][17]. The Phase Margin and Gain Margin of a minimum phase system

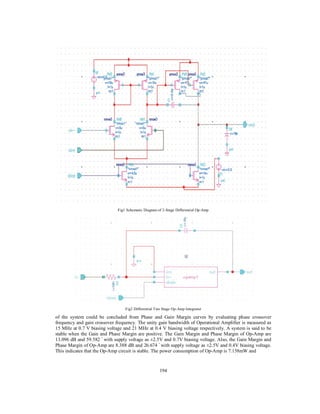

should be positive for an Op-Amp and Integrator to be stable. The schematic of two stage differential Op-

Amp having coupling capacitor and load capacitor of values 2.2pF and 10 pF respectively, is shown in Fig 1.

The Op-Amp Integrator performs the mathematical operation of integration with respect to time. It offers

output voltage proportional to the input voltage over time. The schematic of Integrator comprising of two

stage differential Op-Amp as the lower block, Fig 2. The values of resistor and capacitor used in the

Integrator design are 50kΩ and 10pF respectively.

III. SIMULATION AND RESULT

The design simulation of Op-Amp that comprises of input and output waveform with basic amplification

function is presented here, Fig 1. The transient analysis, DC and AC analysis of operation amplifier are

presented in Fig 3 and Fig 4. It also discusses the stability of Operational Amplifier. This section also

contains the simulations of Integrator with sine wave provided as input to it obtaining a cosine wave as

output verifying the mathematical operation of integration.

The transient analysis of two stage differential Op-Amp is shown in Fig 3 in which a signal of small

magnitude (mV) is amplified by the amplifier. The input voltage of Op-Amp ranges from 50mV to 100mV

which is amplified approximately to 1.85 V. When a sinusoidal wave is applied to the input terminals of the

amplifier, the amplified output waveform of a continuous sinusoidal wave is showing the AC simulations of

Op-Amp as shown in Fig 4.

In the presence of negative feedback to the amplifier, a zero or negative Phase Margin (PM), where the loop

gain exceeds unity guarantees instability. Thus, positive PM is a safety margin that ensures proper operation

of the amplifier circuit for minimum phase systems. The magnitude verses frequency curve of Op-Amp is

shown in Fig 5. The Gain Margin curve depicting the unity gain bandwidth of Op-Amp with a biasing

voltage of 0.7V is shown in Fig6 and the Phase Margin curve of Op-Amp is also shown in Fig7. The stability](https://image.slidesharecdn.com/525-192-198-140325041503-phpapp01/85/525-192-198-2-320.jpg)

![197

Fig9 Output Waveform of Integrator

TABLE III: SIMULATIONS OF INTEGRATOR

S.No Parameters Values

1 Supply voltage ± 2.5 V

2 Bandwidth 15.03MHz

3 Vin+ 50mV to -50mV

4 Vin- 30mV to -30mV

5 Vbais 0.4V

6 Time Period 100μs

7 Frequency 10kHz

8 Power 7.844mW

The power of Op-Amp and Integrator is also evaluated. The unity gain bandwidth of Operational Amplifier is

15 MHz at 0.7 V biasing voltage and 21 MHz at 0.4 V biasing voltage with power consumption of 7.158mW

and 6.998mW, respectively. The power of Op-Amp is 7.158mW at 0.7V biasing voltage and 6.998mW at

0.4V and the power of Integrator circuit is 7.884mW.

REFERENCES

[1] G. Ahn,N. Ozaki, H. Youra, K. Yamamura, K. Hamashita, K. Takasuka, “A 0.6-V 82-dB Delta-Sigma Audio ADC

Using Switched-RC Integrators,” IEEE Journal Of Solid-State Circuits, vol. 40, no. 12, Dec. 2005.

[2] T. Adachi, A. Ishinawa, and K. Takasuka, “A 1.4 V switched capacitor filter,” Proc. IEEE Custom Integrated

Circuits Conf., pp. 821–824, 1990.

[3] Y. Nakagome, H. Tanaka, K. Takeuchi, E. Kume, Y. Watanabe, T.Kaga, Y. Kawamoto, F. Murai, R. Izawa, D.

Hisamoto, T. Kisu, T. Nishida, E. Takeda, and K. Itoh, “An experimental 1.5-V 64-Mb DRAM,” IEEE J. Solid-State

Circuits, vol. 26, no. 4, pp. 465–472, Apr. 1991.

[4] A. Abo and P. Gray, “A 1.5-V 10-bit 14.3 MS/s CMOS pipeline ADC,” IEEE J. Solid-State Circuits, vol. 34, no. 5,

pp. 599–606, May 1999.

[5] J. Crols and M. Steyaert, “Switched-Op-Amp: An approach to realize full CMOS switched-capacitor circuits at very

low power supply voltages,” IEEE J. Solid-State Circuits, vol. 29, no. 8, pp. 936–942, Aug. 1994.

[6] M. Keskin, U. Moon, and G. C. Temes, “A 1-V 10-MHz clock-rate 13-bit CMOS modulator using unity-gain-reset

op amps,” IEEE J. Solid-State Circuits, vol. 37, no. 7, pp. 817–824, Jul. 2002.

[7] D. Chang and U. Moon, “A 1.4-V 10-bit 25-MS/s pipelined ADC using Op-Amp-reset switching technique,” IEEE

J. Solid-State Circuits, vol. 37, no. 8, pp. 1401–1404, Aug. 2003.

[8] A. Gupta, D.K. Mishra, and R. Khatri, “A Two Stage and Three Stage CMOS OP-AMP with Fast Settling, High DC

Gain and Low Power Designed in 180nm Technology,” International Conference on Computer Information Systems

and Industrial Management Applications, 2010.

[9] Kim Min Gyu, Gil-Cho Ahn, Kumar Pavan, Lee Sang-Hyeon, Kim Sang-Ho, Seung-Bin , Kim Jae-Whui, Temes

Gabor C., and Moon Un-Ku, “A 0.9 V 92 dB Double-Sampled Switched-RC Delta-Sigma Audio ADC,” IEEE J.

Solid-Stute Circuits, vol. 43, no. 5, May 2008.

[10] R. Yaguchi, F. Adachi, and T. Waho, “A Low-Power Delta-Sigma Modulator Using Dynamic-Source-Follower

Integrators,” IEEE, 2010.

[11] J. Crols and M. Steyaert, “Switched Op-Amp: An approach to realize full CMOS SC circuits at very low supply

voltages,” IEEE J. Solid-State Circuits, vol. 29, no. 8, pp. 936–942, Aug. 1994.

[12] V. Peluso, P. Vancorenland, A. Marques, M. Steyaert, and W. Sansen, “A 900-mV low-power A/D converter with

77-dB dynamic range,” IEEE J. Solid-State Circuits, vol. 33, no. 12, pp. 1887–1897, Dec. 1998.

[13] A. Baschirotto and R. Castello, “A 1-V 1.8-MHz CMOS switched Op-Amp SC filter with rail-to-rail output swing,”

IEEE J. Solid-State Circuits, vol. 32, pp. 1979–1986, Dec. 1997.](https://image.slidesharecdn.com/525-192-198-140325041503-phpapp01/85/525-192-198-6-320.jpg)

![198

[14] M. Waltari and K. Halonen, “1-V 9-bit pipelined switched-Op-Amp,” IEEE J. Solid-State Circuits, vol. 36, no. 1,

pp. 129–134, Jan. 2001.

[15] B. Vaz, J. Goes, and N. Paulino, “A 1.5-V 10-b 50 MS/s time-interleaved switched-Op-Amp pipeline CMOS ADC

with high energy efficiency,” Dig. Symp. VLSI Circuits, pp. 432–435, Jun. 2004.

[16] M. Keskin, U. Moon, and G. Temes, “A 1-V 10-MHz clock-rate 13-bit CMOS delta-sigma modulator using unity-

gain-reset Op-Amps,” IEEE J. Solid- State Circuits, vol. 37, no. 7, pp. 817–823, Jul. 2002.

[17] D. Chang, G. Ahn, and U. Moon, “A 0.9 V 9 mW 1 MSPS digitally calibrated ADC with 75 dB SFDR,” Dig. Symp.

VLSI Circuits, pp. 67–70, Jun. 2003.

[18] D. Chang and U. Moon, “A 1.4-V 10-bit 25 MSPS pipelined ADC using Op-Amp-reset switching technique,” IEEE

J. Solid-State Circuits, vol. 38, no. 8, pp. 1401–1404, Aug. 2003.

[19] P. Sheetal1, N. Tripathi, “Low Power Op-Amp Design with Current Compensation Technique,” International

Journal of Advanced Research in Computer and Communication Engineering, vol. 2, issue 9, Sept. 2013.

[20] M. R. V. Bernal, S. Celma, N. Medrano, and B. Calvo, “An Ultralow-Power Low-Voltage Class-AB Fully

Differential Op-Amp for Long-Life Autonomous Portable Equipment,” IEEE Transactions On Circuits And

Systems, vol. 59, no. 10, Oct. 2012.

ABOUT THE AUTHORS

1

Anu, completed her B.Tech in Electronics and Communication Engineering from Ganga Institute of Technology and

Management, Kablana in 2012. She is now pursuing her Master of Technology (M.Tech) in VLSI Design at ITM

University, Gurgaon. Her interest includes Digital Design, ASIC Design, VLSI Testing and Verification.

2

Amit Kumar, received the B.E. (Hons.) degree in Electronics and Communication Engineering from C.I.T.M. Faridabad

in 2010 and the M.Tech. degree in VLSI Design from N.I.T. Kurukshetra in 2012. He joined ITM University, Gurgaon,

(Haryana) India as Asst. Professor in the Department of Electrical, Electronics & Communication Engineering during

July-December 2013. His areas of interest include VLSI domain and in particular Analog IC Design, Operational

Amplifers and Mixed signal systems.

3

Neeraj Kr. Shukla, (IETE, IE, IACSIT, IAENG, CSI, ISTE, VSI-India), an Associate Professor in the Department of

Electrical, Electronics & Communication Engineering, and Project Manager – VLSI Design at ITM University, Gurgaon,

(Haryana) India. He received his PhD from UK Technical University, Dehradun in Low-Power SRAM Design and

M.Tech. (Electronics Engineering) and B.Tech. (Electronics & Telecommunication Engineering) Degrees from the J.K.

Institute of Applied Physics & Technology, University of Allahabad, Allahabad (Uttar Pradesh) India in the year of 1998

and 2000, respectively. He has more than 50 Publications in the Journals and Conferences of National and International

repute. His main research interests are in Low-Power Digital VLSI Design and its Multimedia Applications, Digital

Hardware Design, Open Source EDA, Scripting and their role in VLSI Design, and RTL Design.](https://image.slidesharecdn.com/525-192-198-140325041503-phpapp01/85/525-192-198-7-320.jpg)