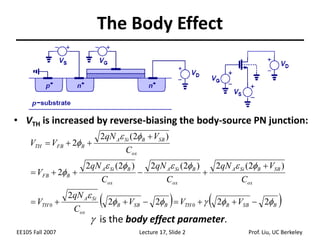

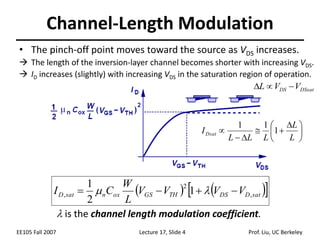

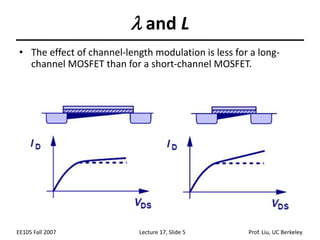

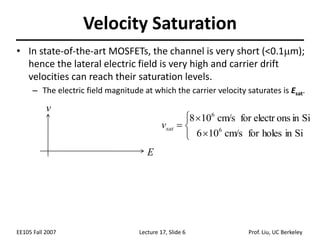

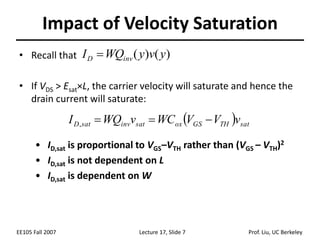

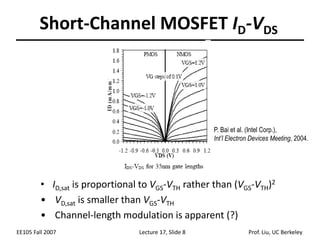

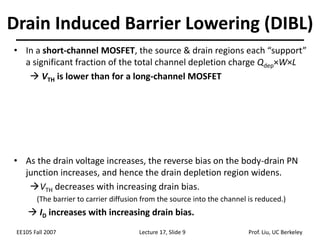

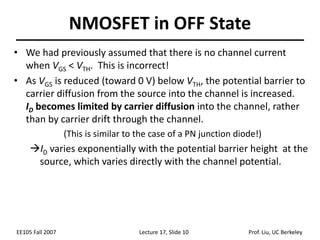

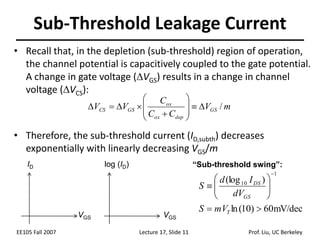

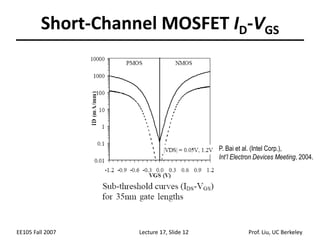

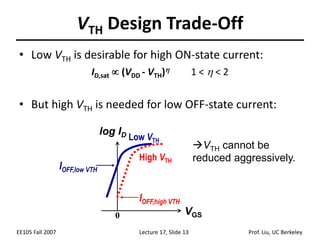

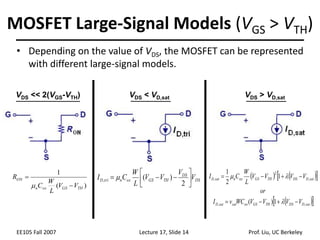

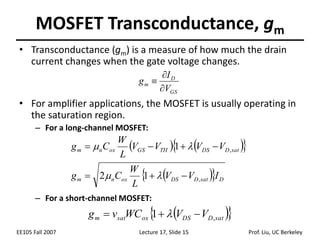

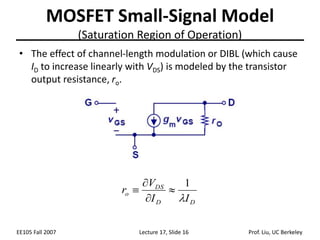

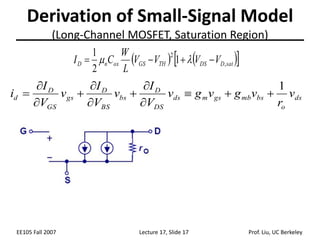

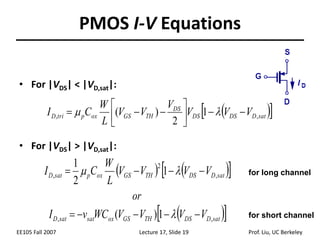

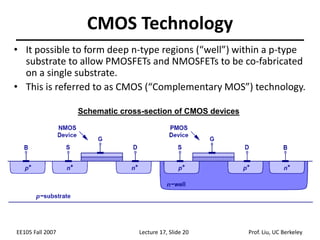

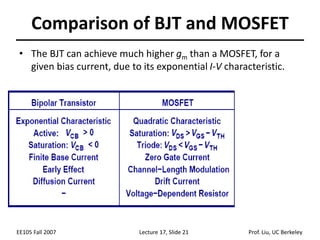

This document summarizes key concepts from Lecture 17 of the EE105 Fall 2007 course at UC Berkeley taught by Prof. Liu. It discusses the body effect, channel-length modulation, and velocity saturation in NMOSFETs operating in the ON state. It also covers NMOSFET operation in the OFF state due to subthreshold leakage. MOSFET models including the impact of short-channel effects are presented. The document concludes by discussing PMOSFET operation and CMOS technology.