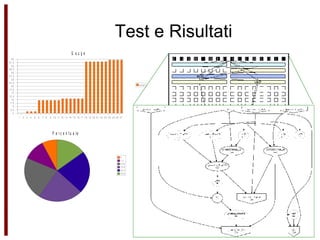

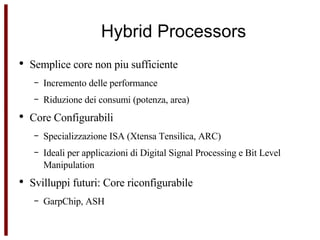

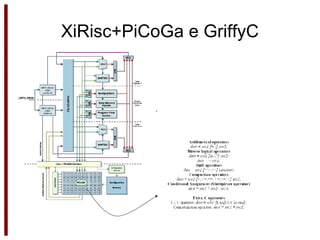

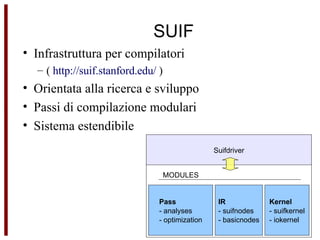

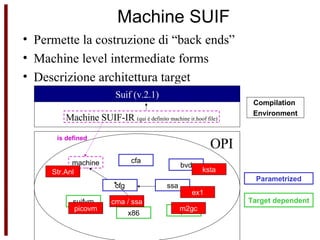

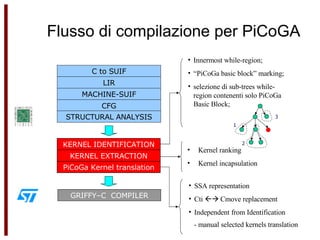

The document discusses parallel compilation techniques for reconfigurable architectures. It describes a hybrid processor called XiRisc+PiCoGa and GriffyC that has a configurable RISC core and reconfigurable PiCoGa component. It outlines the compilation flow from C to GriffyC code that can be executed on the XiRisc+PiCoGa architecture, including various analyses and optimizations performed during compilation.

![GriffyC L1 : sub a,a,2 rol b,b,a add d,d,a add c,b,d add i,i,1 bnz c,L1 sub a,a,2 add d,d,a rol b,b,a add c,b,d add i,i,1 A D I B L1 : sub a,2 rol b,a add d,a add c,b,d add i,i,1 bnz c,L1 PGAop a,b,d,i [..] for(;c!=0;i++)[ a=a-2; b=b<<a; d=d+a; c=b+d; ] [..] [..] PD_0=pga_allocate(myPGAop); [..] for(;c!=0;i++)[ pgadirect1(PD_0, a,i,b,d); ] [..] pga_deallocate(myPGAop); [..]](https://image.slidesharecdn.com/3d-dresd-lorenzo-pavesi3601/85/3D-DRESD-Lorenzo-Pavesi-6-320.jpg)

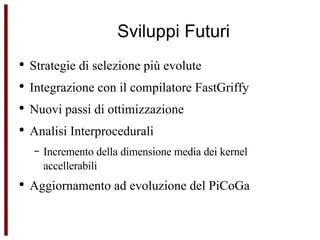

![Generazione del GriffyC ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ C SUIF SUIF (LIR) Dismantling delle strutture di controllo FileSetBlock FileBlock procedure procedure procedure FileBlock procedure procedure Machine SUIF CFG](https://image.slidesharecdn.com/3d-dresd-lorenzo-pavesi3601/85/3D-DRESD-Lorenzo-Pavesi-10-320.jpg)

![Generazione del GriffyC picovm Control Tree ANNOTED Mach – SUIF ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ PICOHEADER ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ FileSetBlock FileBlock procedure procedure procedure FileBlock procedure procedure kernel Ottimizzazioni sul tipo di selezione ottimizzazioni sul body del kernel Selezione 2 3 Ranking & Estrazione SSA M2GC ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ ...... ........ ......#ifndef PICOHEADER__provaTmp1 #define PICOHEADER__provaTmp1 #pragma fpga _provaTmp1 0x00 0 0 { /* Virtual register declarations */ void * _vr0; double _vr1; float _vr2; _vr4 = (float (*)[1])part_amplitude; _vr5 = (float *)_vr4; _vr6 = (float *)((char *)_vr5 + _vr3); _vr7 = *_vr6; _vr2 = (float)_vr7; _vr1 = (double)_vr2; printf(_vr0, i, _vr1); } #pragma end #endif /*PICOHEADER__provaTmp1*/ Structural Analysis 1 X](https://image.slidesharecdn.com/3d-dresd-lorenzo-pavesi3601/85/3D-DRESD-Lorenzo-Pavesi-11-320.jpg)