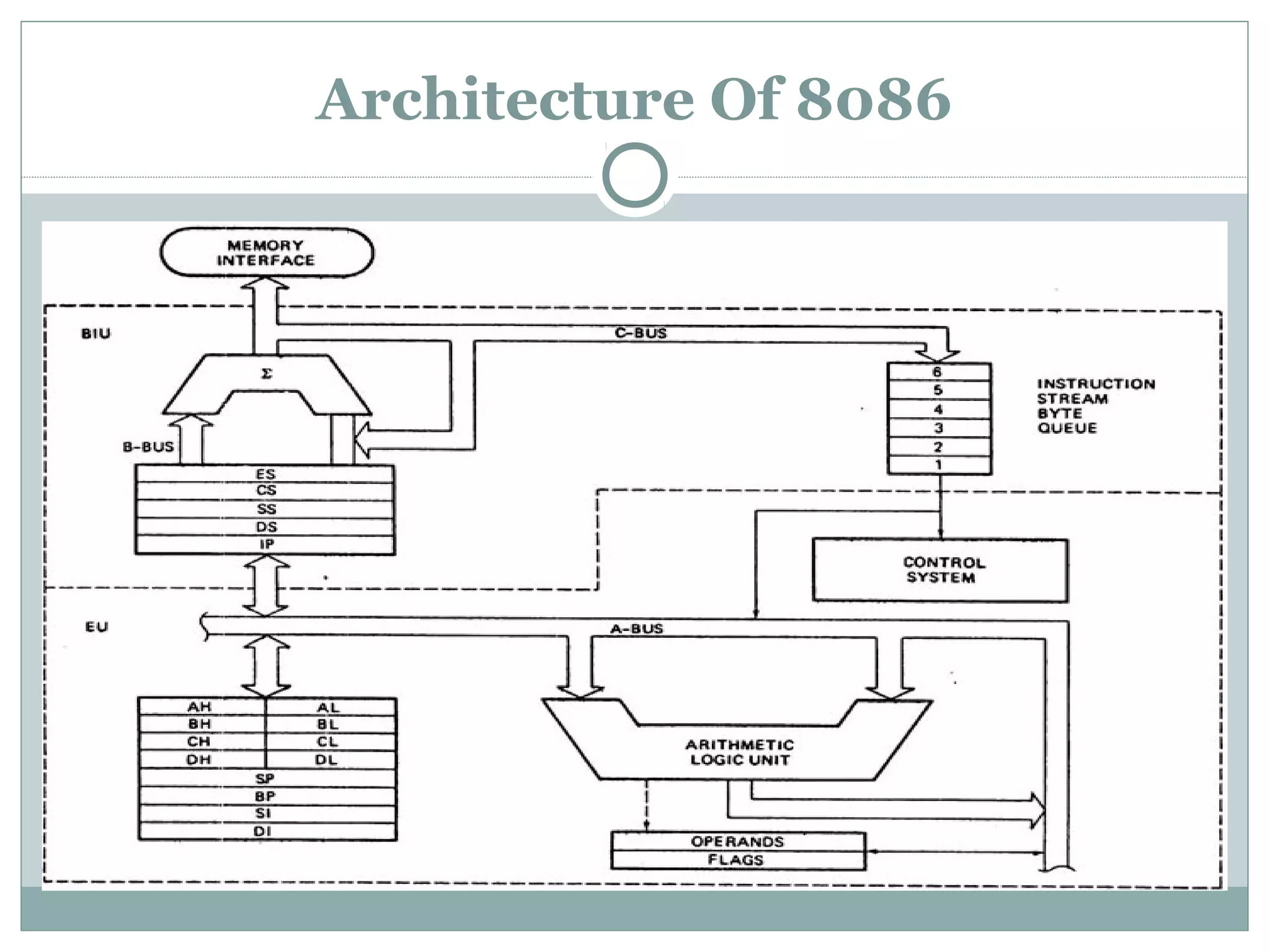

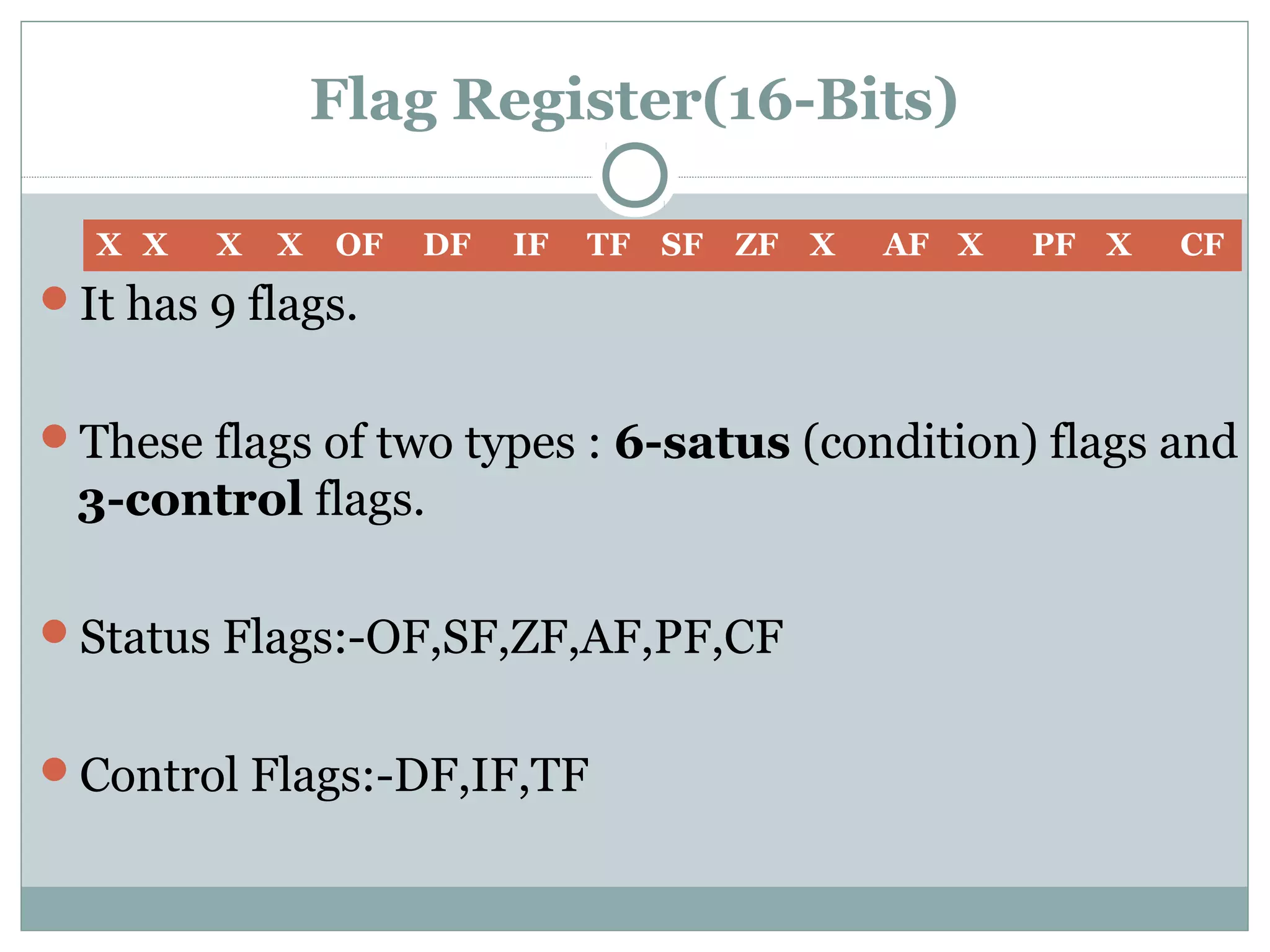

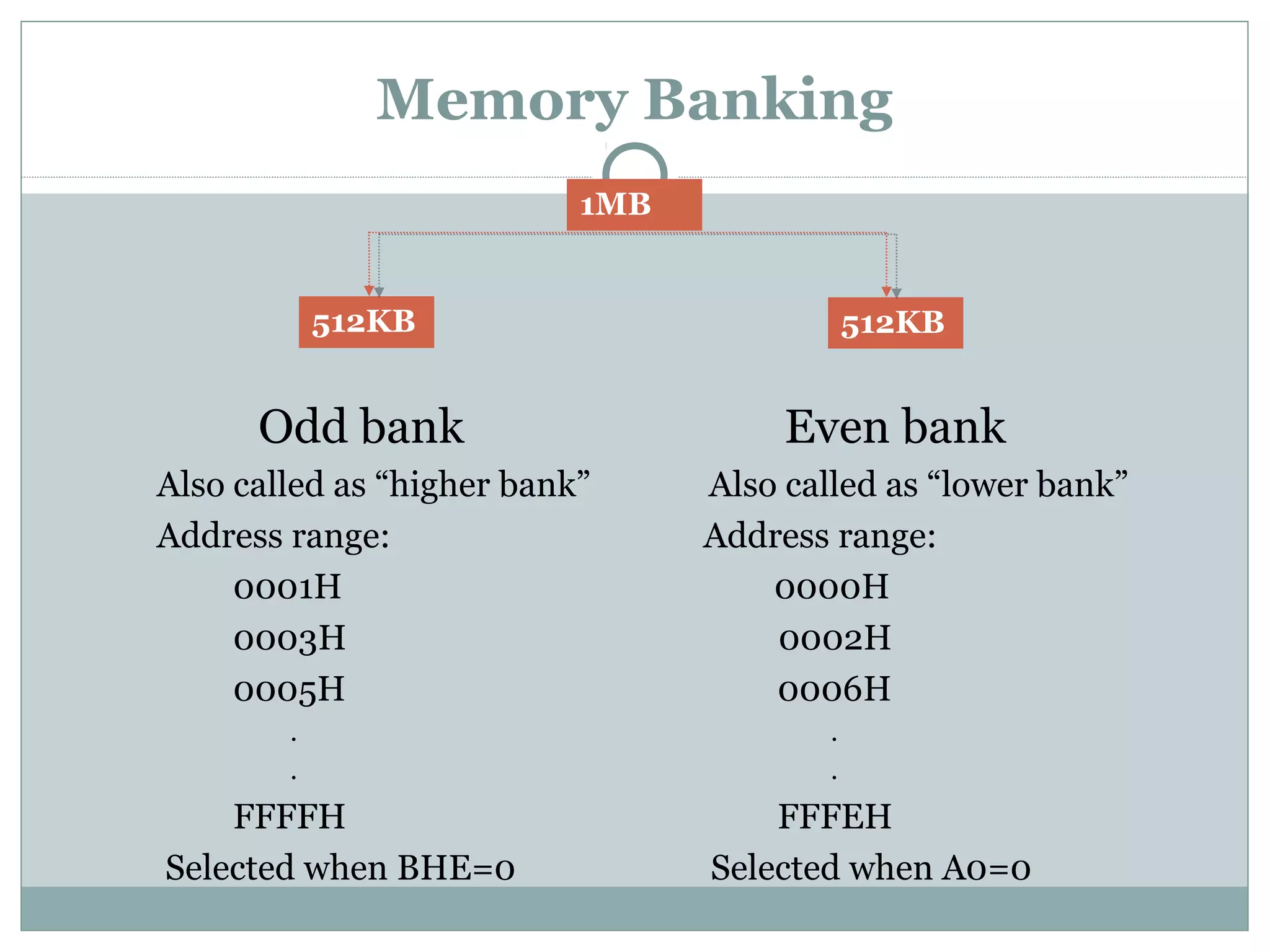

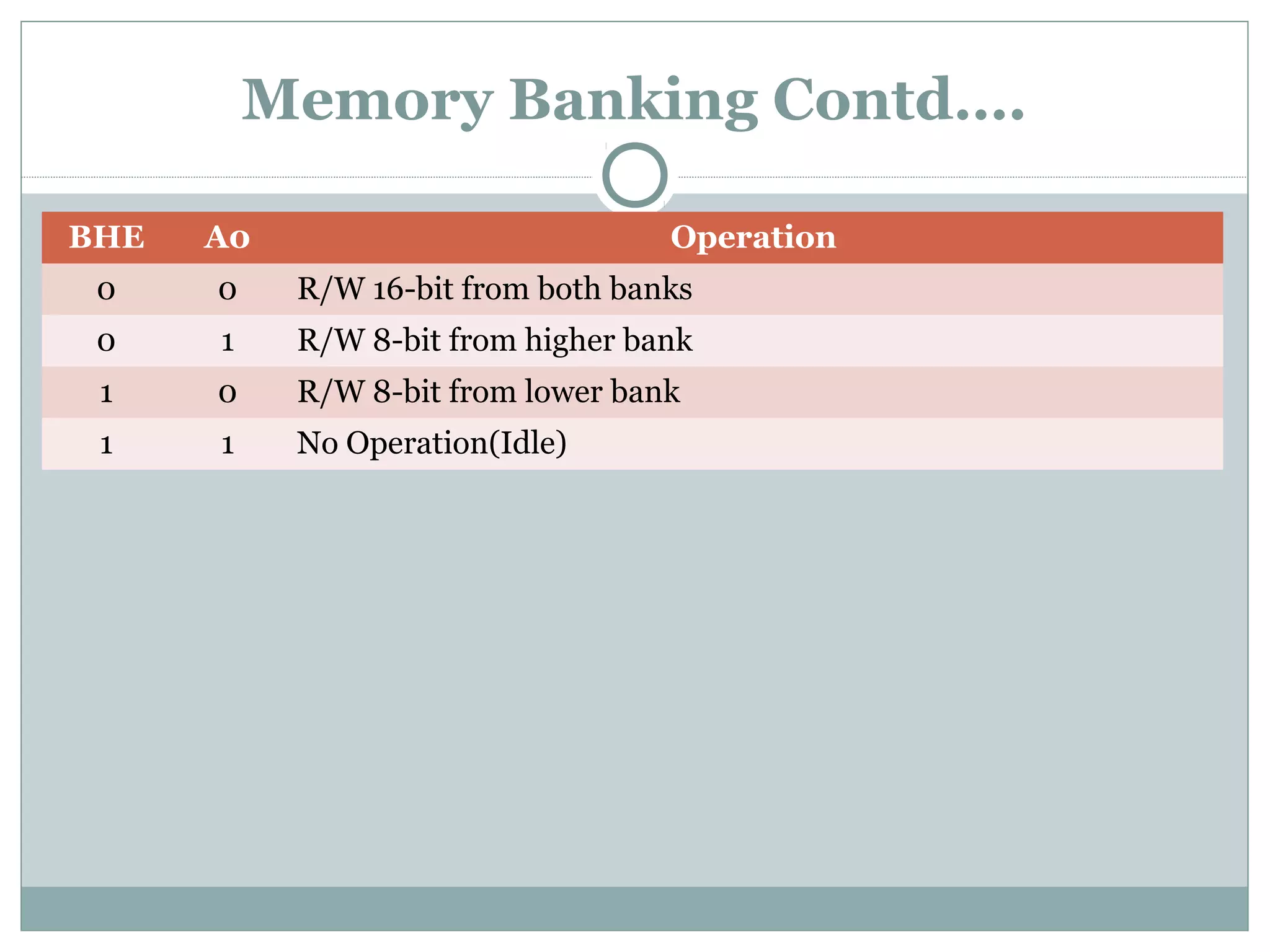

The document discusses the architecture and features of the 8086 microprocessor. It describes the various components of the 8086 including the Bus Interface Unit (BIU) which handles communication with external memory and I/O devices, the segment registers, instruction pointer, address generation circuit, and execution unit. It also covers the flag register, memory segmentation using segments and offsets, and memory banking using the BHE and A0 pins.