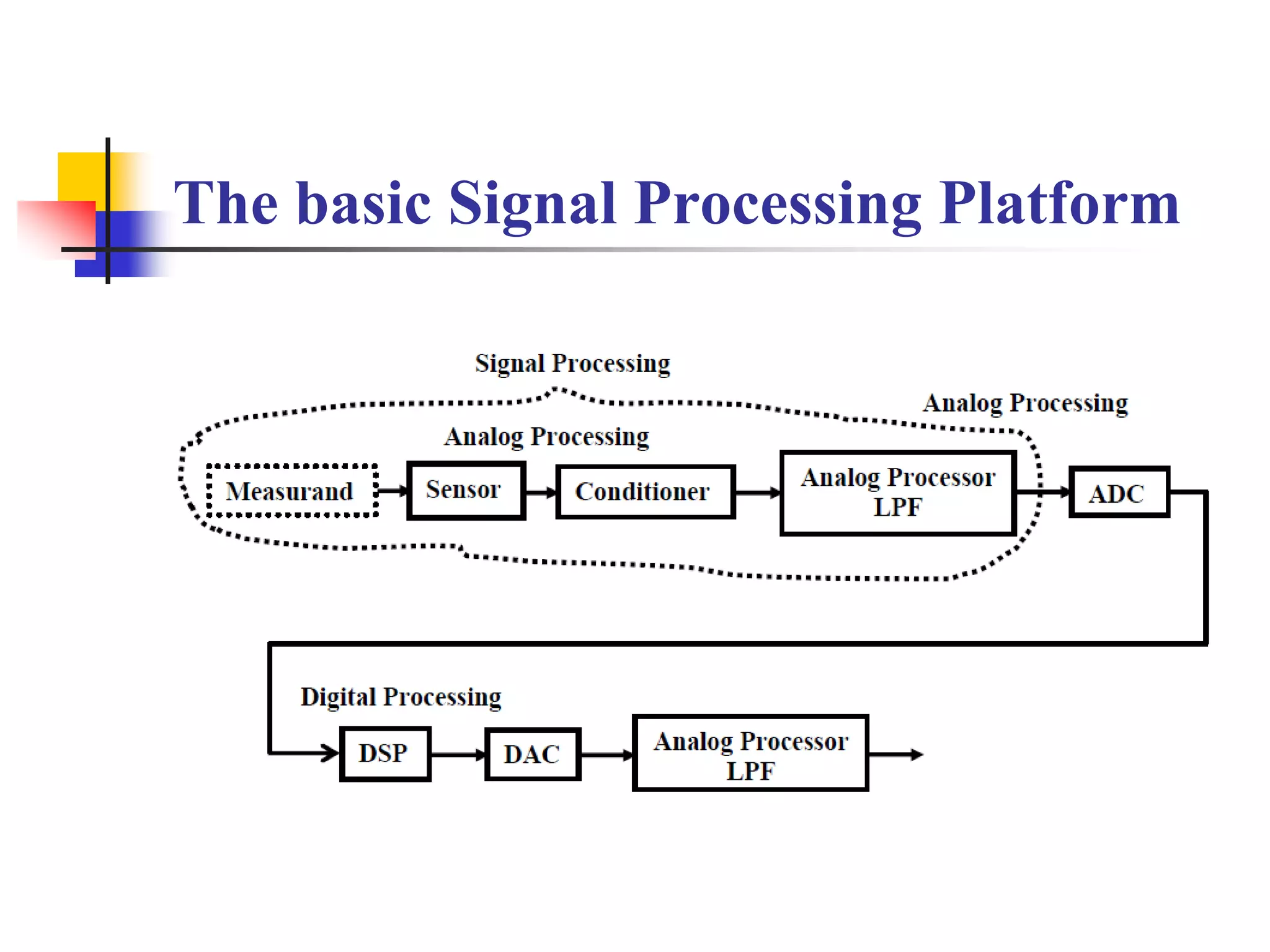

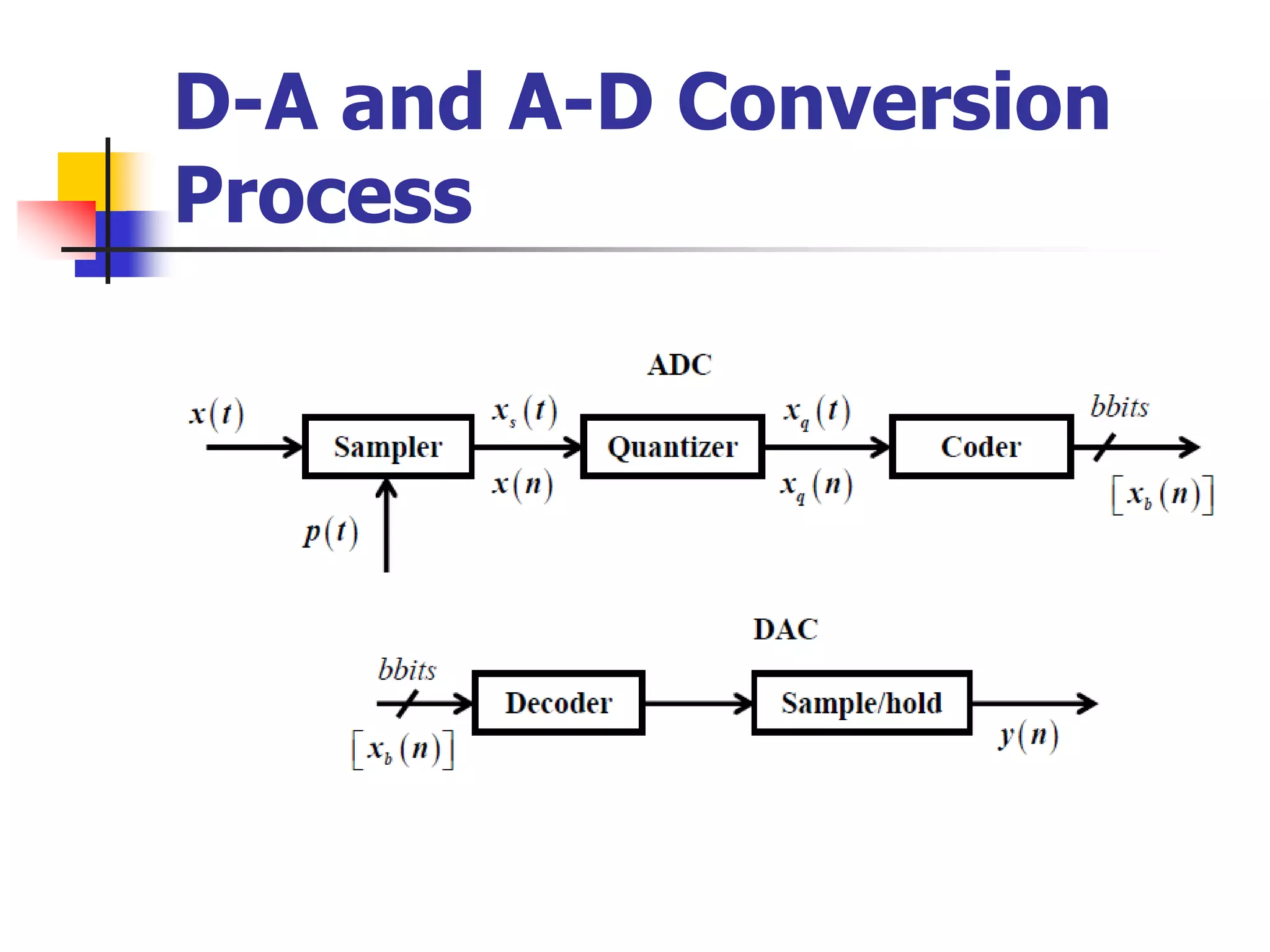

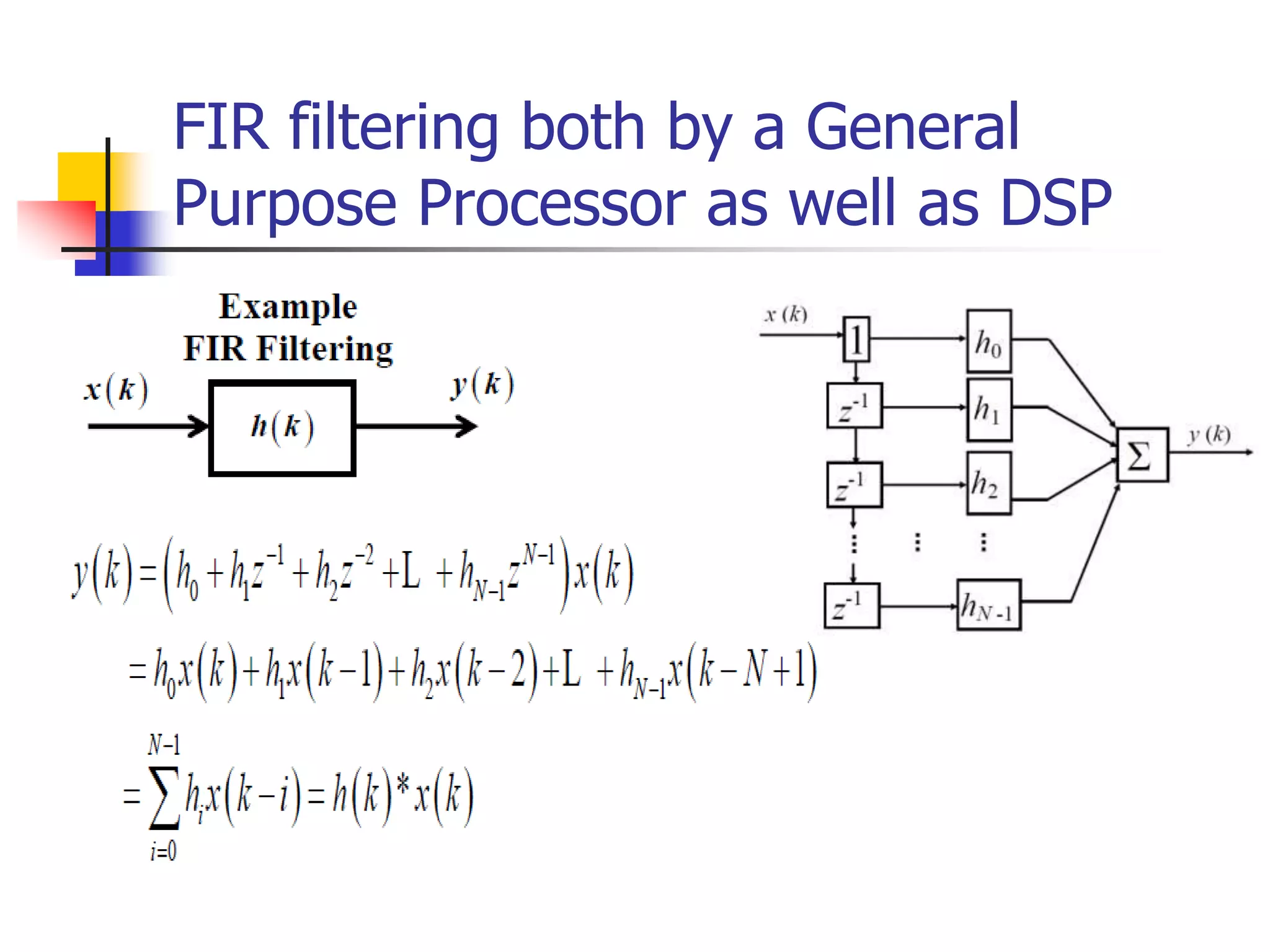

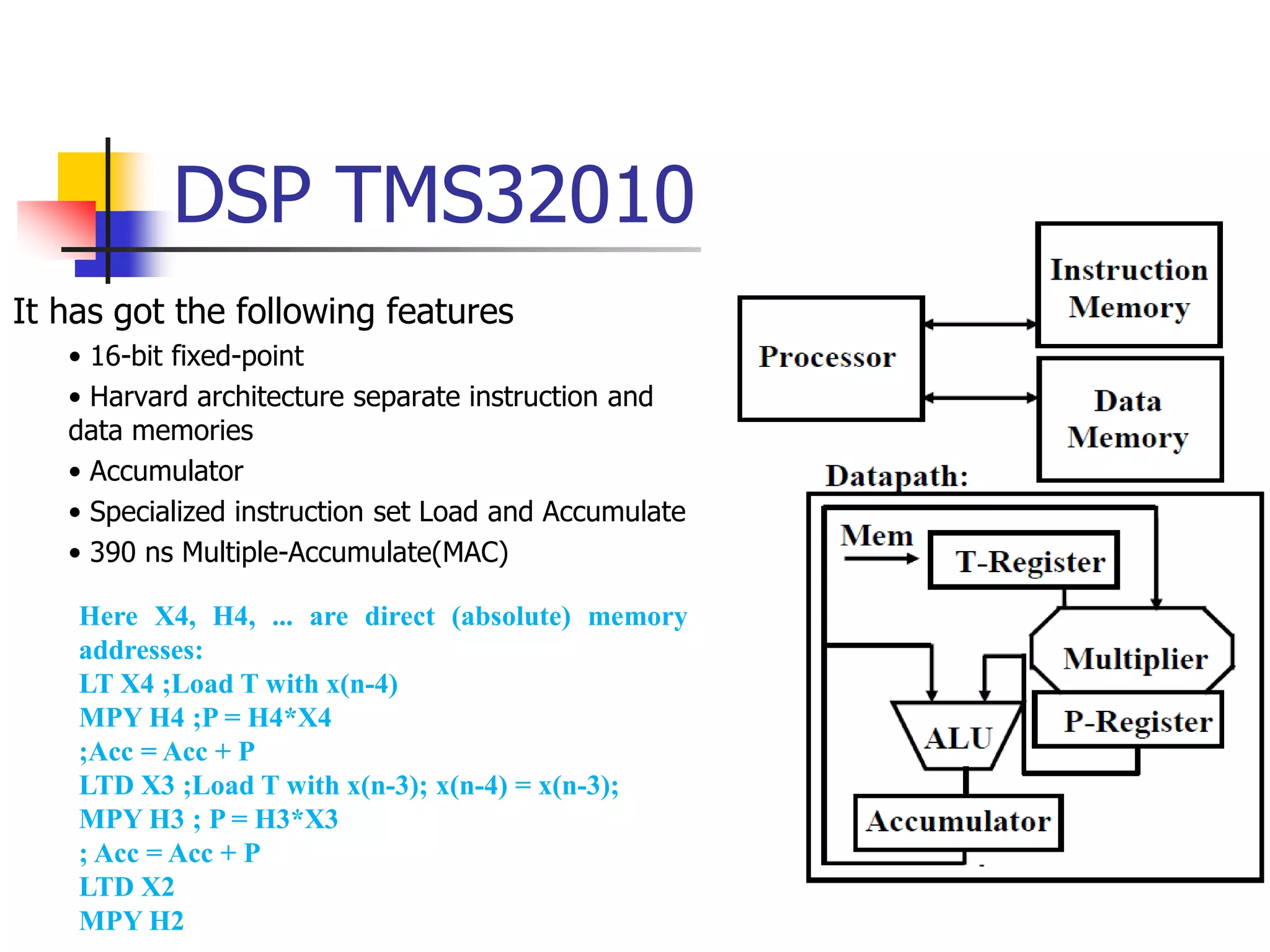

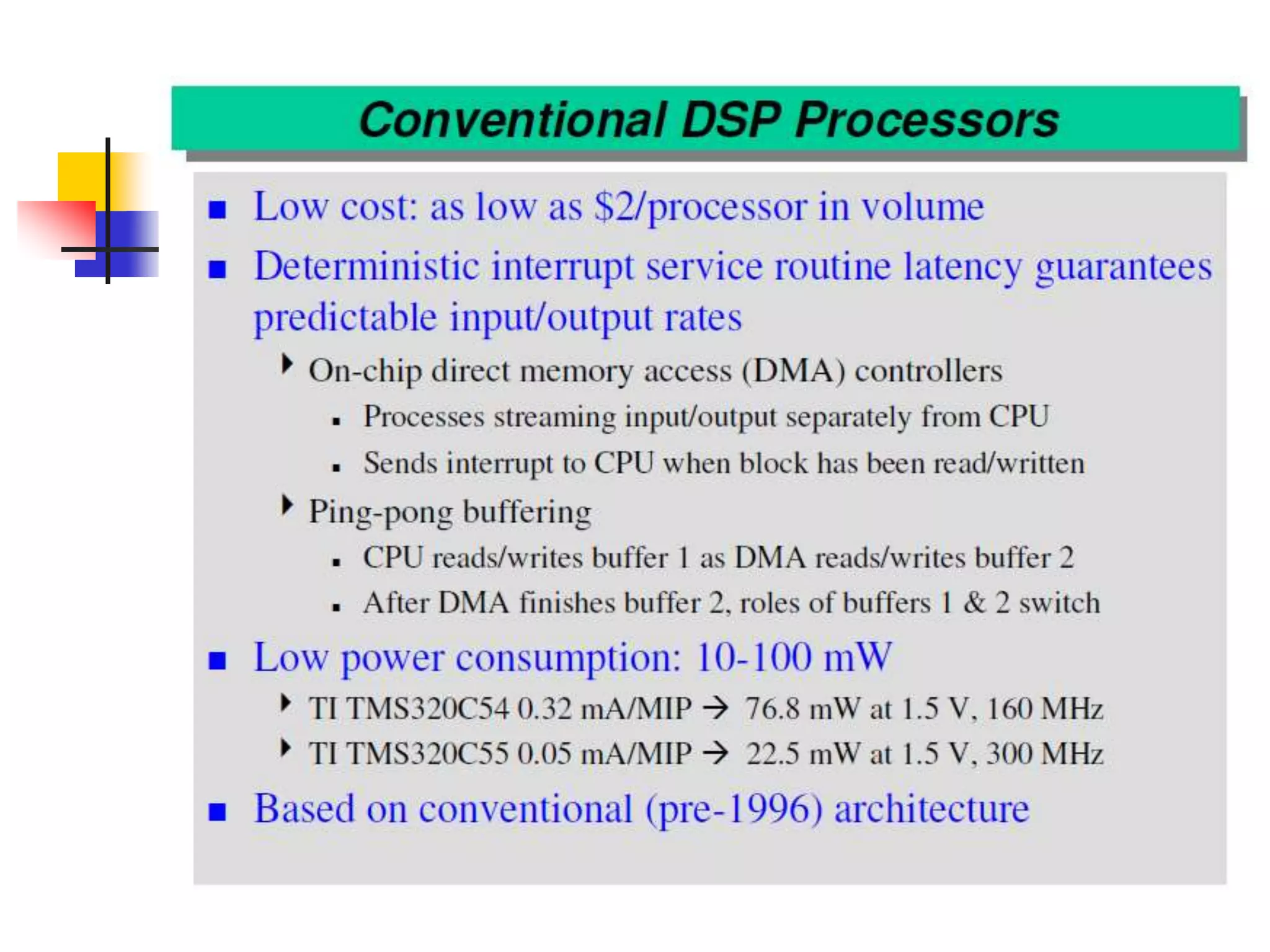

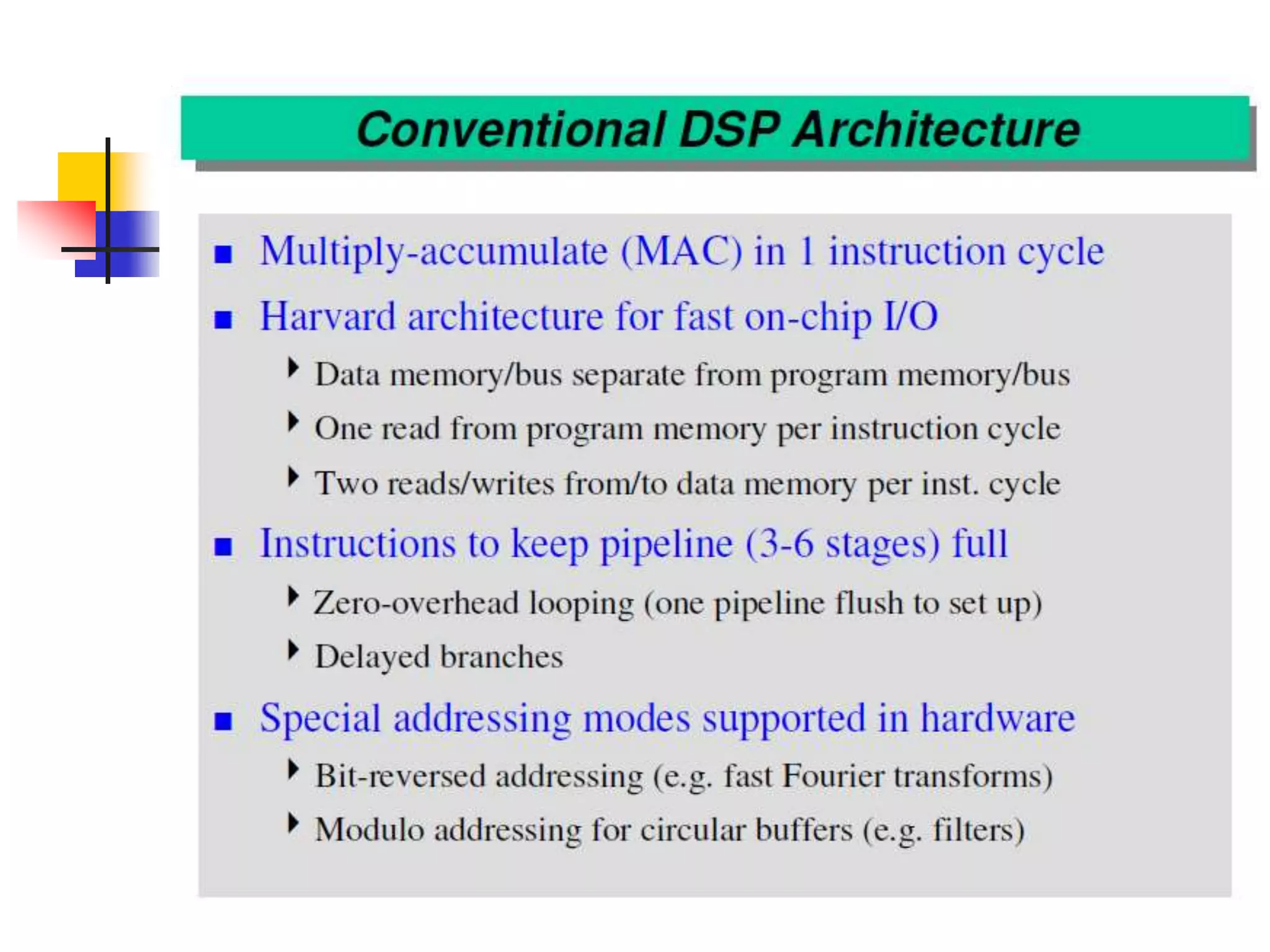

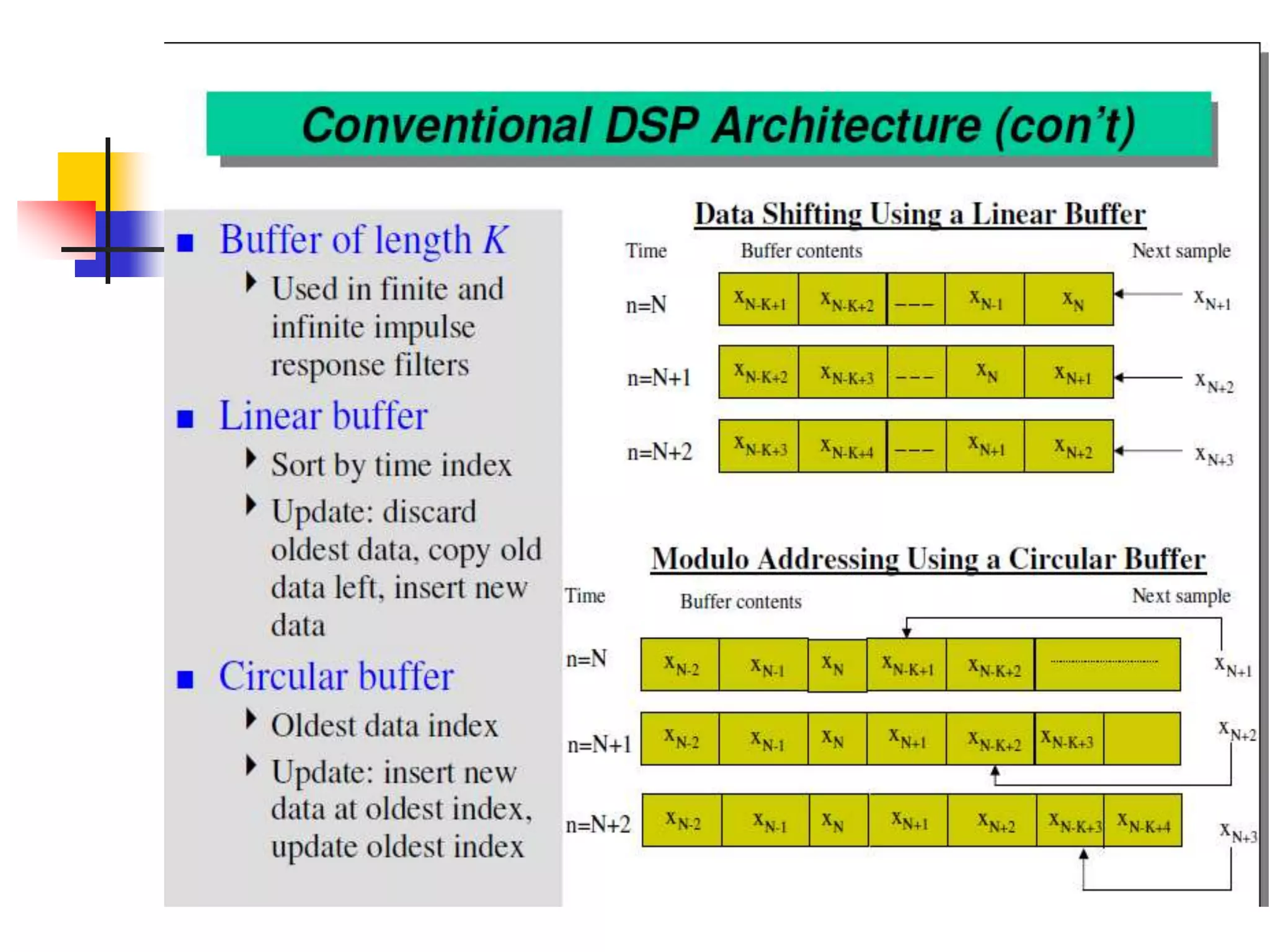

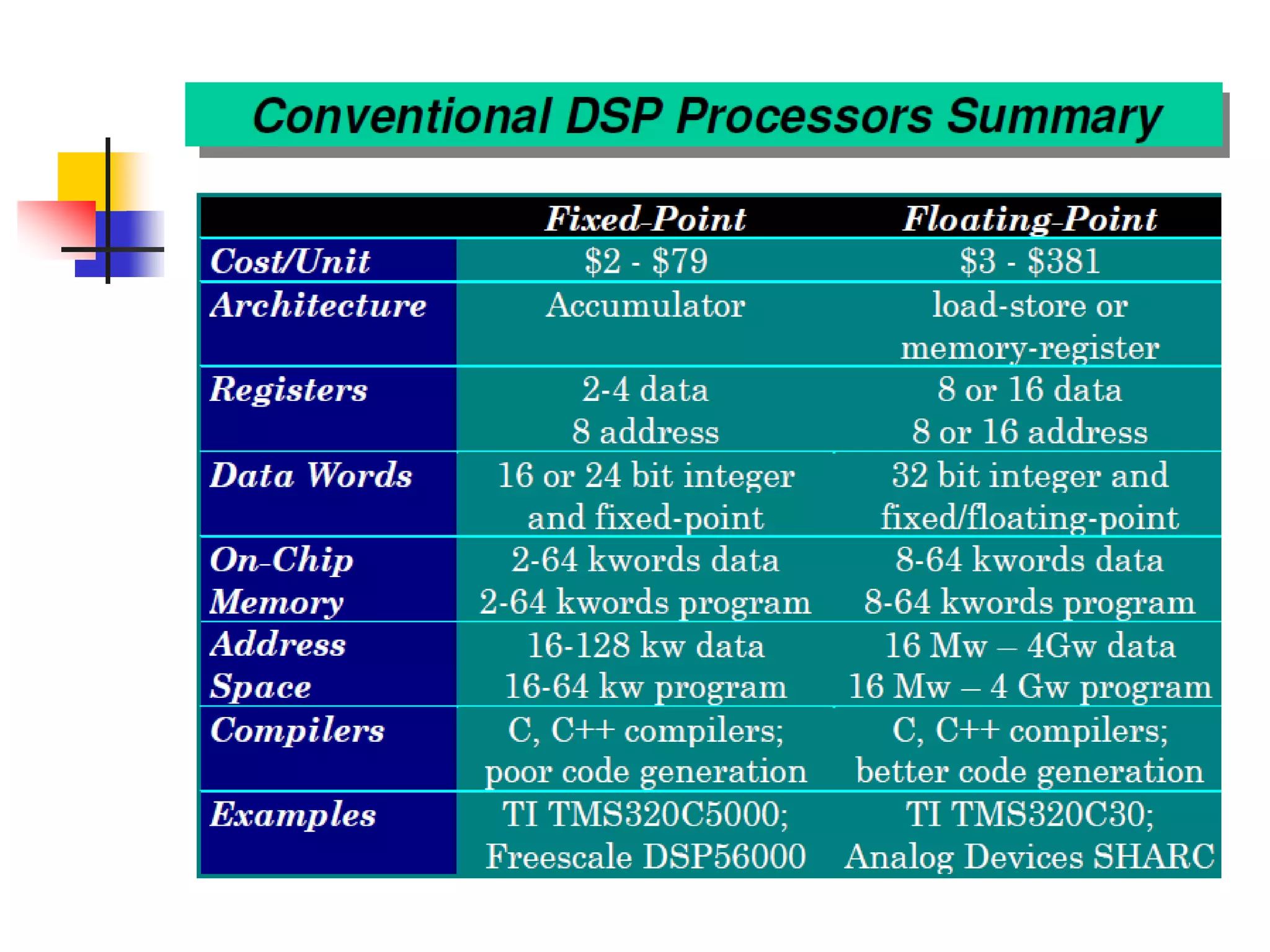

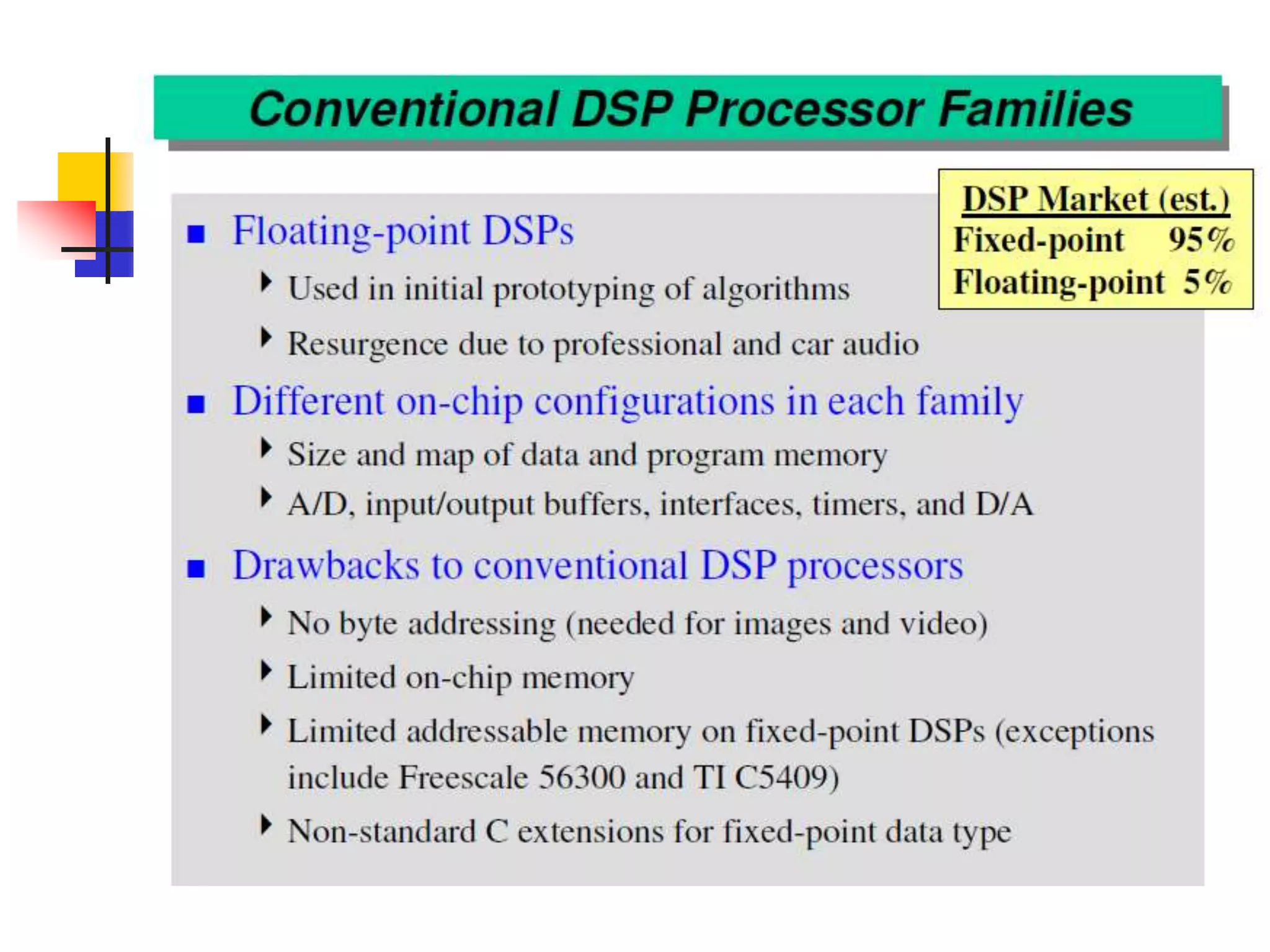

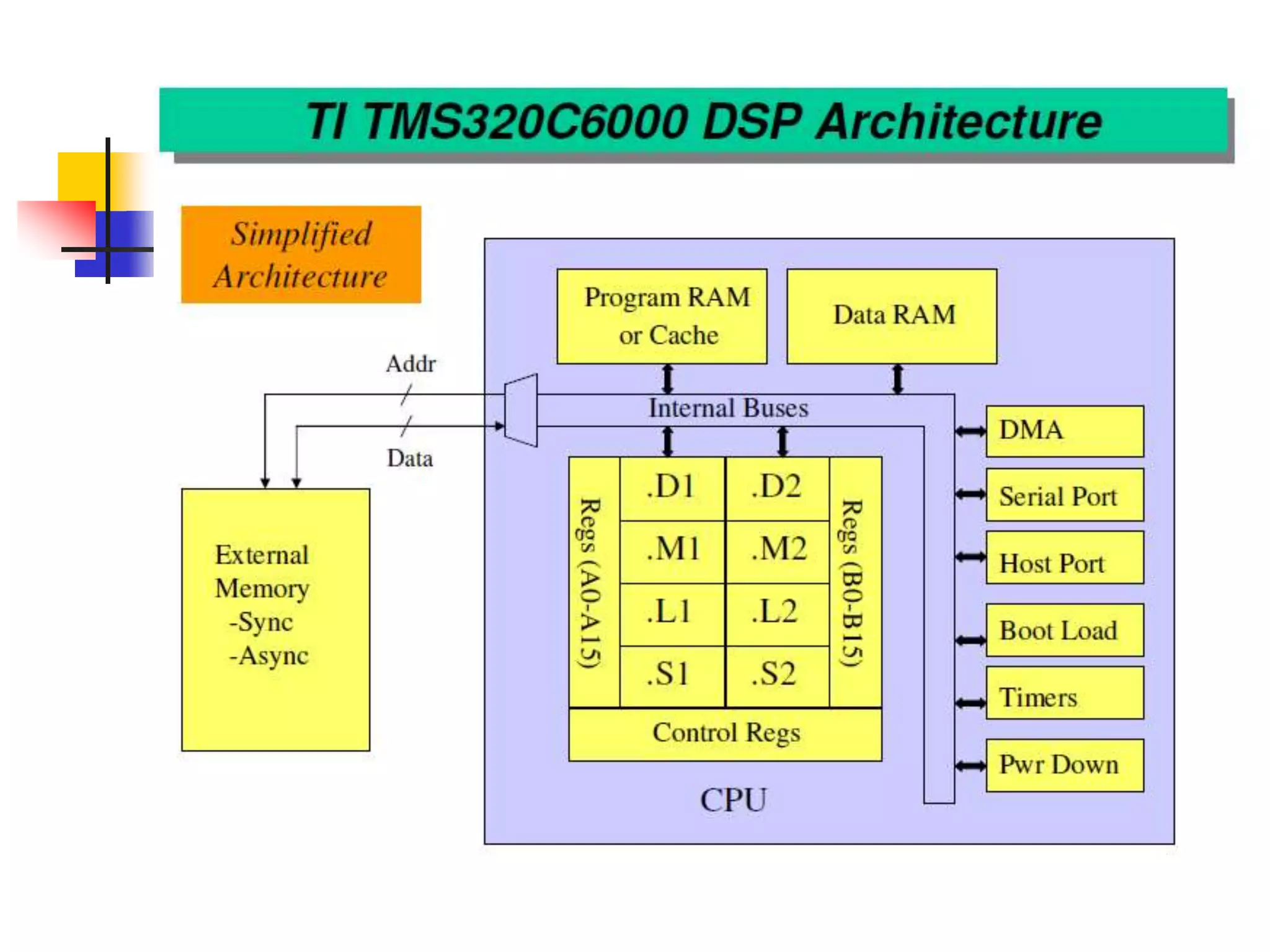

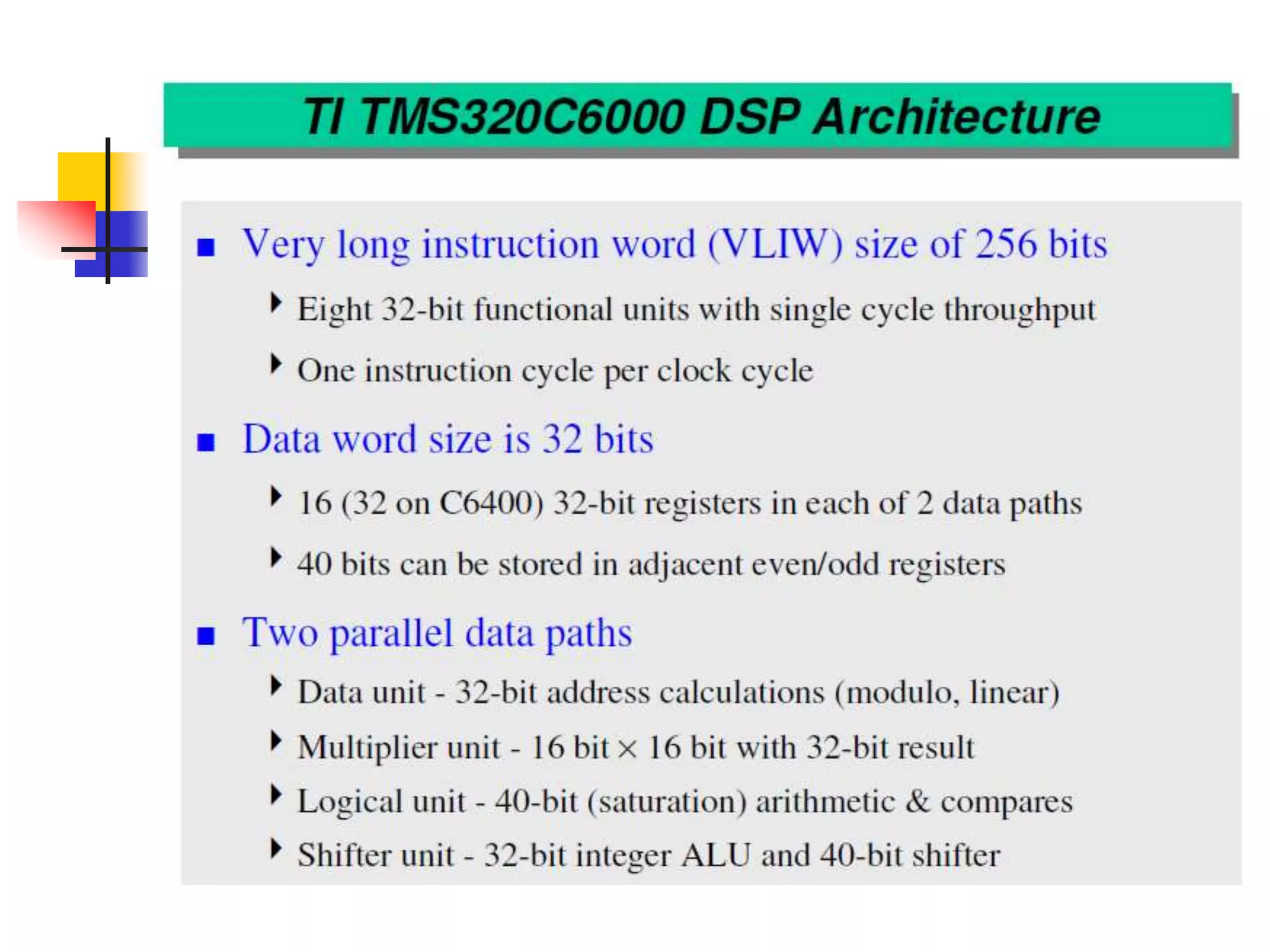

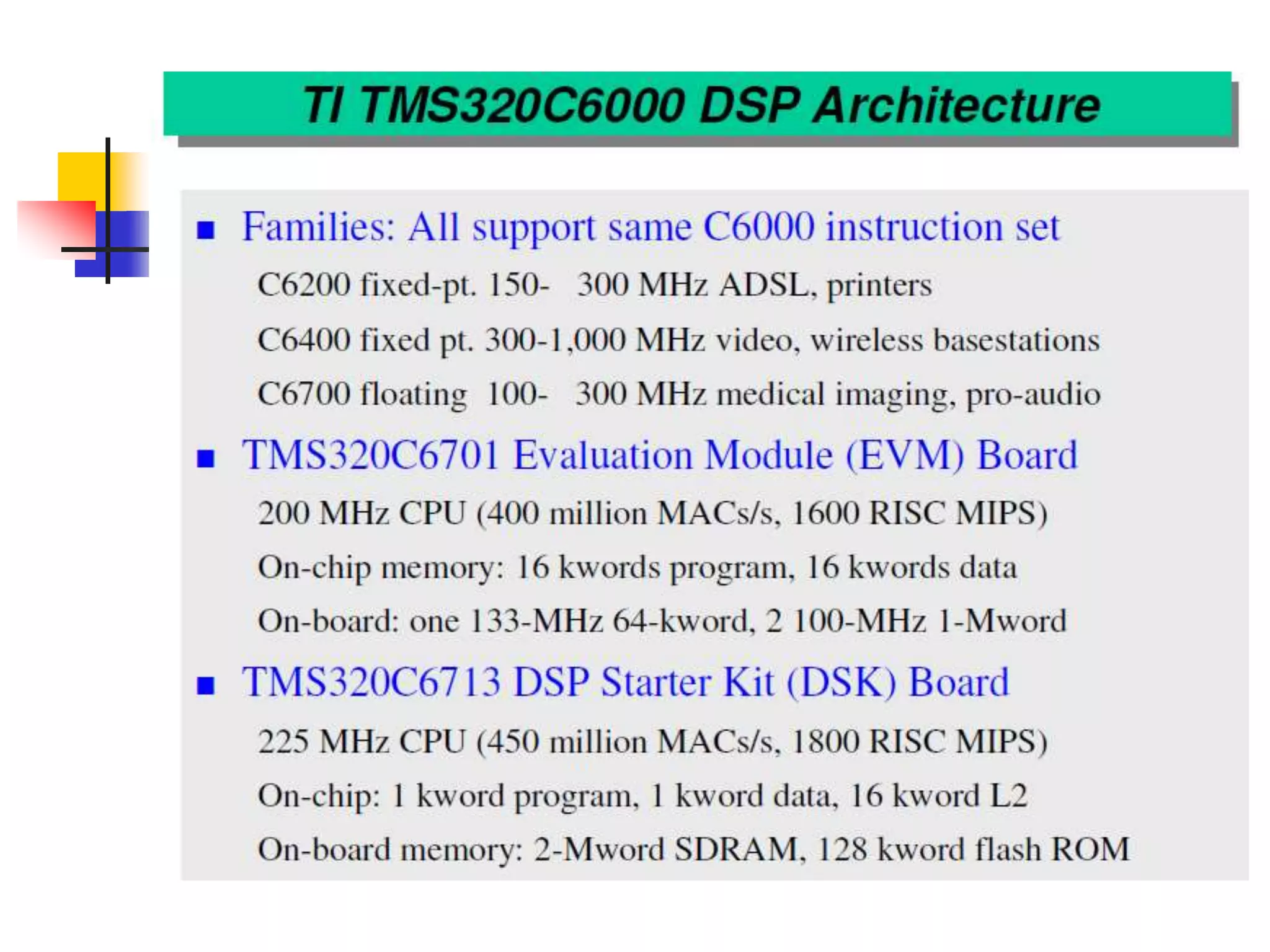

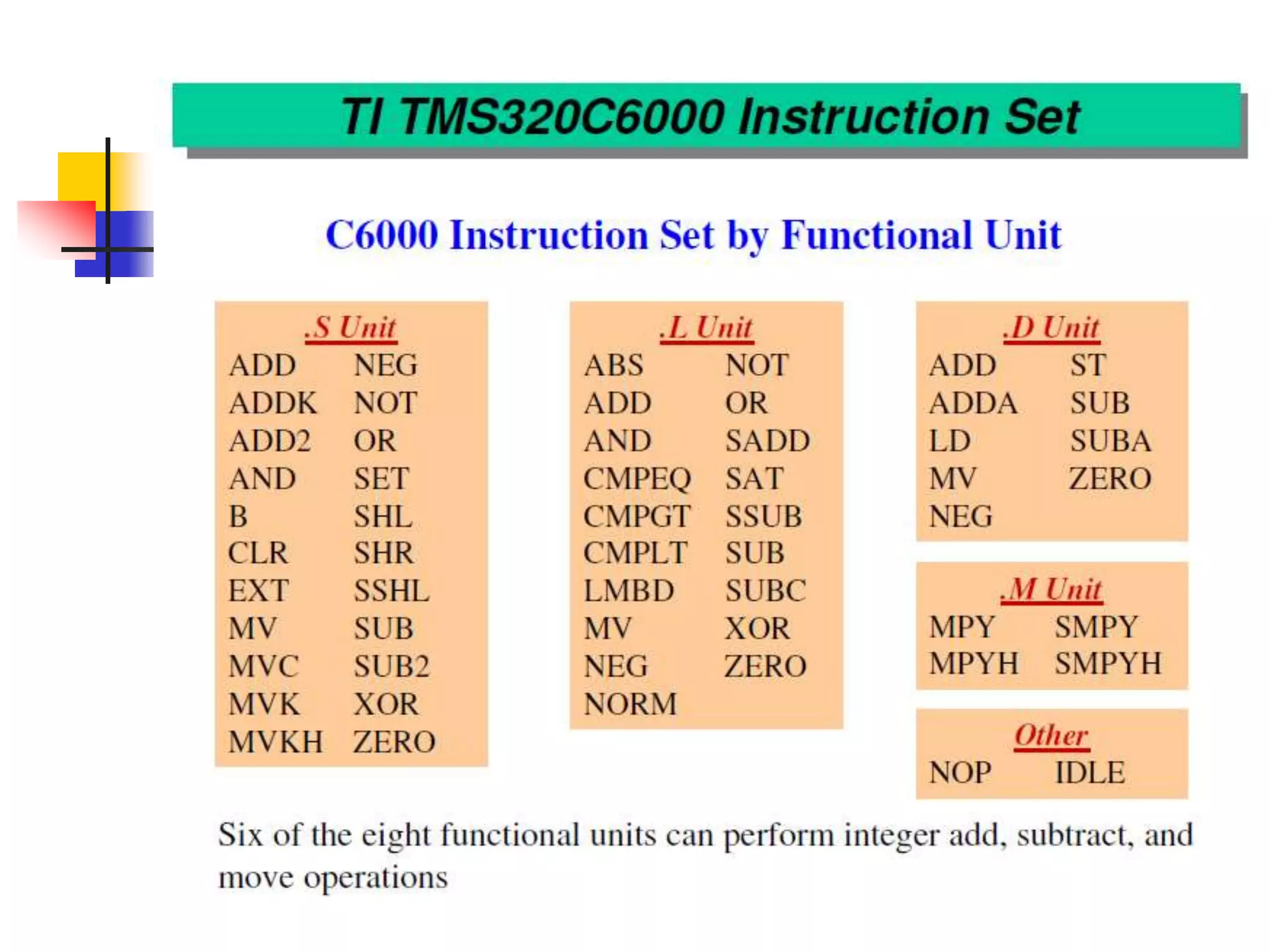

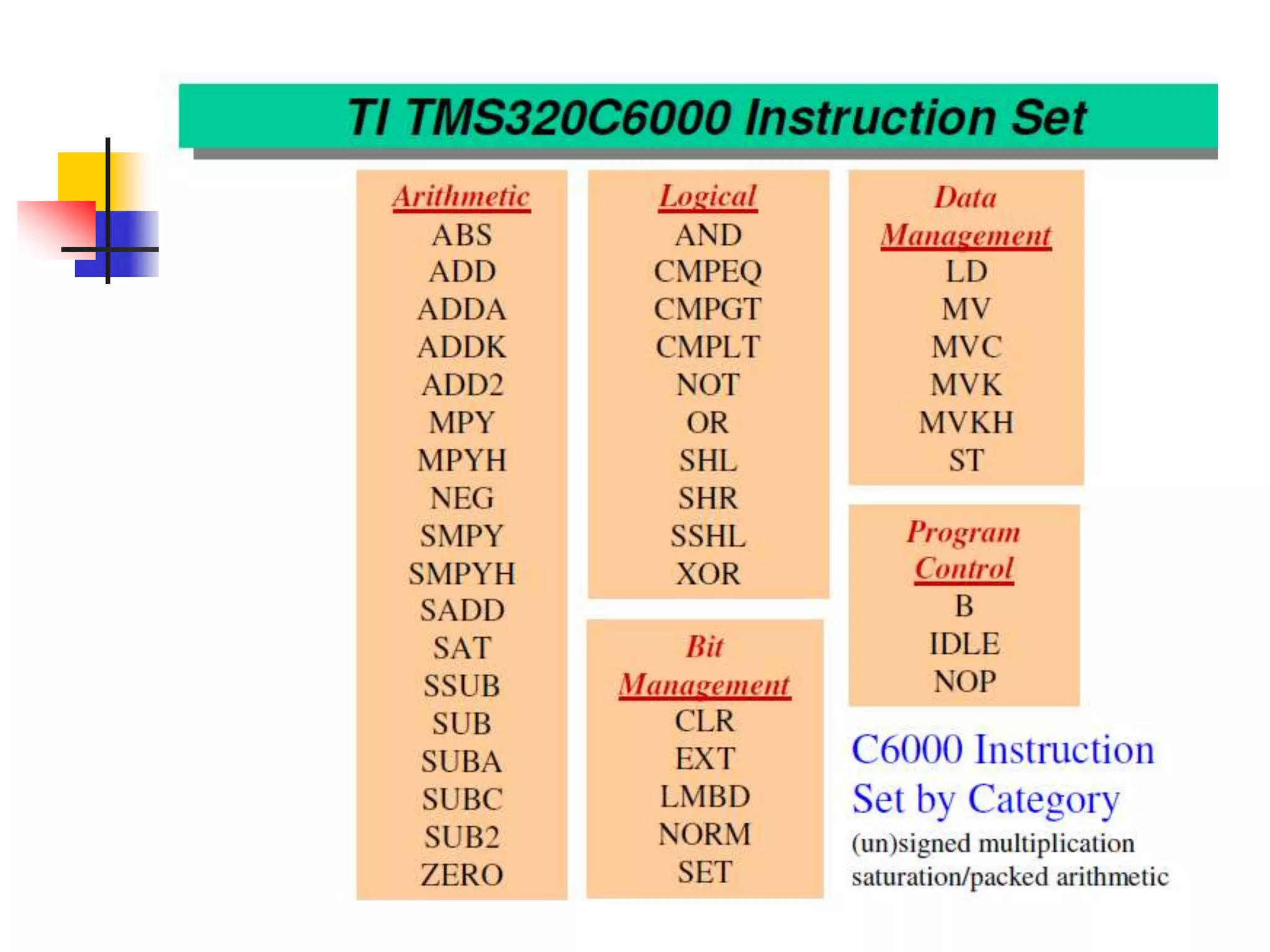

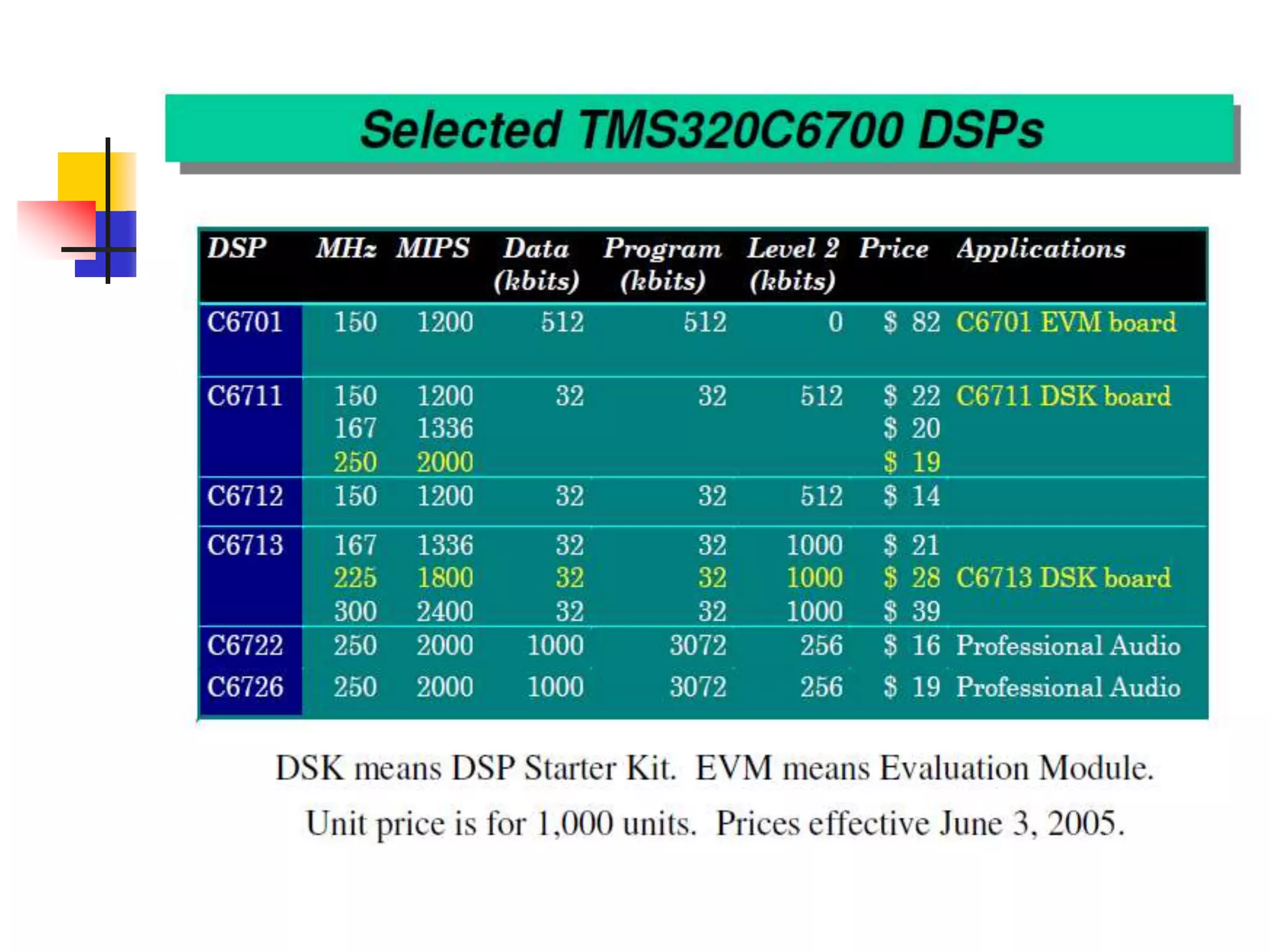

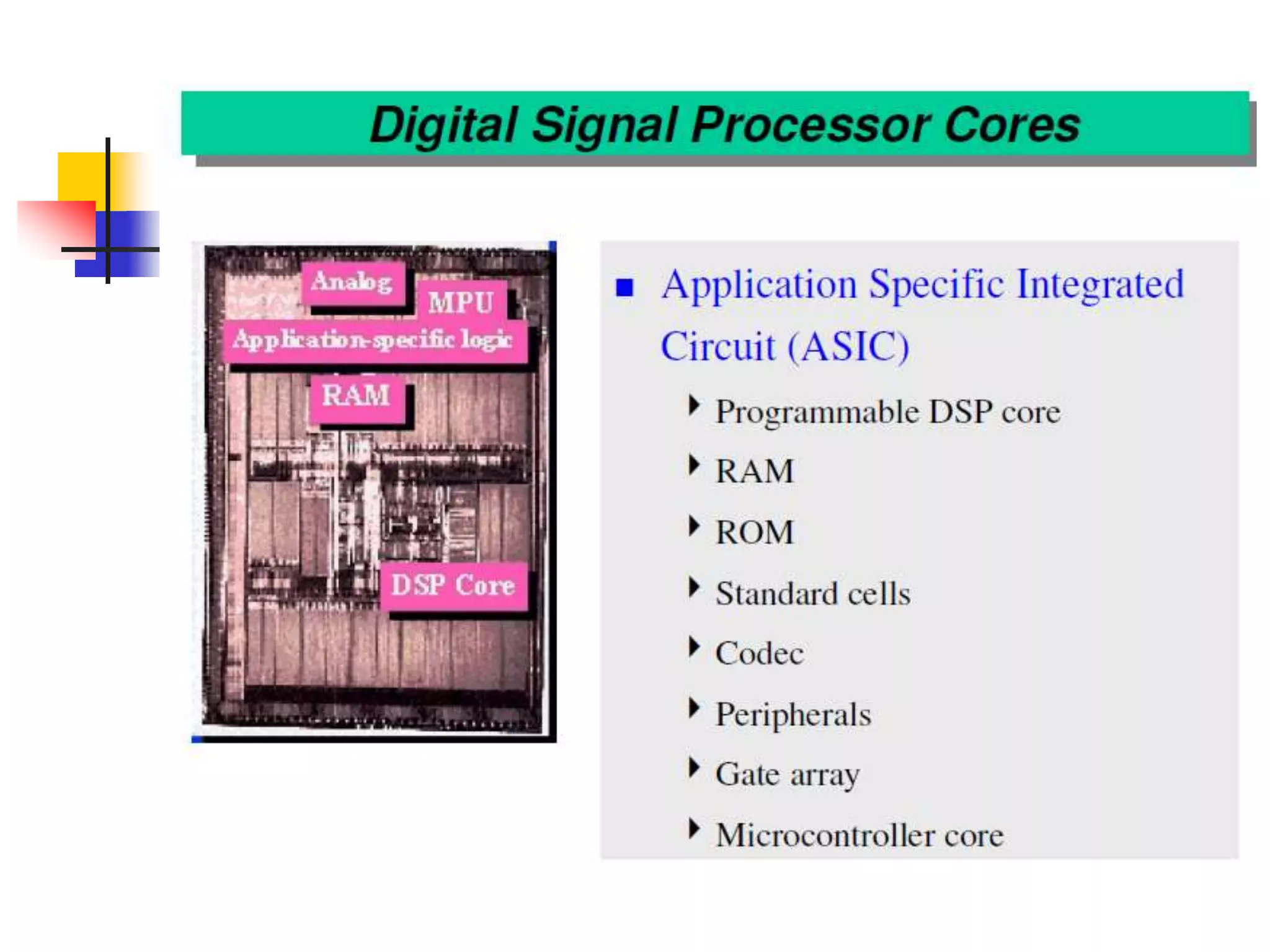

This document discusses digital signal processors and customizable processors. It begins by describing digital signal processors, noting they are used for digital signal processing tasks like filtering, estimation, and data manipulation in real time. It then discusses customizable processors and the benefits of customization, as well as using microprocessor cores in system-on-chip designs. The rest of the document provides details on digital signal processing, including digital to analog conversion, applications of DSP like finite impulse response filtering using general purpose and digital signal processors, and features of the TMS32010 digital signal processor.