Modified architecture of MAC using VLsI technology in verilog 2nd review.pptx

•Download as PPTX, PDF•

0 likes•12 views

Review presentation

Report

Share

Report

Share

Recommended

Recommended

The advents in this technological era have resulted into enormous pool of information. This information is

stored at multiple places globally, in multiple formats. This article highlights a methodology for extracting

the video lectures delivered by experts in the domain of Computer Science by using Generalized Gamma

Mixture Model. The feature extraction is based on the DCT transformations. In order to propose the model,

the data set is pooled from the YouTube video lectures in the domain of Computer Science. The outputs

generated are evaluated using Precision and Recall.An Intelligent Approach for Effective Retrieval of Content from Large Data Se...

An Intelligent Approach for Effective Retrieval of Content from Large Data Se...IJCSIS Research Publications

Duplicate and Accumulate (MAC) is one of the central practices utilized absolutely in signal-controlling

and different applications. The multiplier is the major piece of Digital Signal Processors (DSPs). Its cutoff spins around power, LUT use, and surrender pick the presence of a DSP. In like way, there is a need to sort out the drive and give up fit multiplier. In this paper, a 16-digit MAC unit is proposed to utilize an 8-cycle Vedic multiplier and pass on a save snake. A relationship with the current 8-cycle Vedic multiplier utilizing Square-Root (SQR) Carryselect snake (CSLA) is introduced. It is isolated and a standard pack multiplier. The whole technique is done in Verilog HDL. Blend and redirections were finished utilizing Xilinx InDesign Suite 14.5. The proposed game plan

accomplishes fundamental improvement in region and suspension. In like manner, an abatement in power around 9.5% is refined.An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics

An Efficient Design of 16 Bit MAC Unit using Vedic MathematicsBOHR International Journal of Intelligent Instrumentation and Computing

More Related Content

Similar to Modified architecture of MAC using VLsI technology in verilog 2nd review.pptx

The advents in this technological era have resulted into enormous pool of information. This information is

stored at multiple places globally, in multiple formats. This article highlights a methodology for extracting

the video lectures delivered by experts in the domain of Computer Science by using Generalized Gamma

Mixture Model. The feature extraction is based on the DCT transformations. In order to propose the model,

the data set is pooled from the YouTube video lectures in the domain of Computer Science. The outputs

generated are evaluated using Precision and Recall.An Intelligent Approach for Effective Retrieval of Content from Large Data Se...

An Intelligent Approach for Effective Retrieval of Content from Large Data Se...IJCSIS Research Publications

Duplicate and Accumulate (MAC) is one of the central practices utilized absolutely in signal-controlling

and different applications. The multiplier is the major piece of Digital Signal Processors (DSPs). Its cutoff spins around power, LUT use, and surrender pick the presence of a DSP. In like way, there is a need to sort out the drive and give up fit multiplier. In this paper, a 16-digit MAC unit is proposed to utilize an 8-cycle Vedic multiplier and pass on a save snake. A relationship with the current 8-cycle Vedic multiplier utilizing Square-Root (SQR) Carryselect snake (CSLA) is introduced. It is isolated and a standard pack multiplier. The whole technique is done in Verilog HDL. Blend and redirections were finished utilizing Xilinx InDesign Suite 14.5. The proposed game plan

accomplishes fundamental improvement in region and suspension. In like manner, an abatement in power around 9.5% is refined.An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics

An Efficient Design of 16 Bit MAC Unit using Vedic MathematicsBOHR International Journal of Intelligent Instrumentation and Computing

Similar to Modified architecture of MAC using VLsI technology in verilog 2nd review.pptx (20)

A Time-Area-Power Efficient High Speed Vedic Mathematics Multiplier using Com...

A Time-Area-Power Efficient High Speed Vedic Mathematics Multiplier using Com...

LOAD BALANCED CLUSTERING WITH MIMO UPLOADING TECHNIQUE FOR MOBILE DATA GATHER...

LOAD BALANCED CLUSTERING WITH MIMO UPLOADING TECHNIQUE FOR MOBILE DATA GATHER...

Digital Twin-based Software-defined UAV Networks Using Queuing Model

Digital Twin-based Software-defined UAV Networks Using Queuing Model

A Review of Different Methods for Booth Multiplier

A Review of Different Methods for Booth Multiplier

Binary Division Algorithms based on Vedic Mathematics: A Review

Binary Division Algorithms based on Vedic Mathematics: A Review

Regular clocking scheme based design of cost-efficient comparator in QCA

Regular clocking scheme based design of cost-efficient comparator in QCA

Design and testing of systolic array multiplier using fault injecting schemes

Design and testing of systolic array multiplier using fault injecting schemes

An Intelligent Approach for Effective Retrieval of Content from Large Data Se...

An Intelligent Approach for Effective Retrieval of Content from Large Data Se...

An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics

An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics

A Novel Efficient VLSI Architecture Modified 16-B SQRT Carry Select Adder

A Novel Efficient VLSI Architecture Modified 16-B SQRT Carry Select Adder

IRJET- Design of 16 Bit Low Power Vedic Architecture using CSA & UTS

IRJET- Design of 16 Bit Low Power Vedic Architecture using CSA & UTS

Design of a Novel Multiplier and Accumulator using Modified Booth Algorithm w...

Design of a Novel Multiplier and Accumulator using Modified Booth Algorithm w...

Recently uploaded

Differences between analog and digital communicationanalog-vs-digital-communication (concept of analog and digital).pptx

analog-vs-digital-communication (concept of analog and digital).pptxKarpagam Institute of Teechnology

Recently uploaded (20)

Introduction to Arduino Programming: Features of Arduino

Introduction to Arduino Programming: Features of Arduino

The battle for RAG, explore the pros and cons of using KnowledgeGraphs and Ve...

The battle for RAG, explore the pros and cons of using KnowledgeGraphs and Ve...

Intelligent Agents, A discovery on How A Rational Agent Acts

Intelligent Agents, A discovery on How A Rational Agent Acts

Electrostatic field in a coaxial transmission line

Electrostatic field in a coaxial transmission line

Fabrication Of Automatic Star Delta Starter Using Relay And GSM Module By Utk...

Fabrication Of Automatic Star Delta Starter Using Relay And GSM Module By Utk...

Seismic Hazard Assessment Software in Python by Prof. Dr. Costas Sachpazis

Seismic Hazard Assessment Software in Python by Prof. Dr. Costas Sachpazis

Involute of a circle,Square, pentagon,HexagonInvolute_Engineering Drawing.pdf

Involute of a circle,Square, pentagon,HexagonInvolute_Engineering Drawing.pdf

Instruct Nirmaana 24-Smart and Lean Construction Through Technology.pdf

Instruct Nirmaana 24-Smart and Lean Construction Through Technology.pdf

analog-vs-digital-communication (concept of analog and digital).pptx

analog-vs-digital-communication (concept of analog and digital).pptx

Research Methodolgy & Intellectual Property Rights Series 1

Research Methodolgy & Intellectual Property Rights Series 1

Introduction to Artificial Intelligence and History of AI

Introduction to Artificial Intelligence and History of AI

Modified architecture of MAC using VLsI technology in verilog 2nd review.pptx

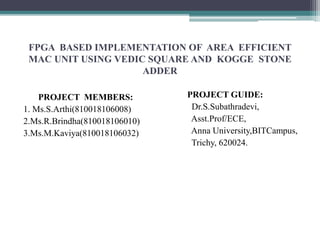

- 1. FPGA BASED IMPLEMENTATION OF AREA EFFICIENT MAC UNIT USING VEDIC SQUARE AND KOGGE STONE ADDER PROJECT MEMBERS: 1. Ms.S.Arthi(810018106008) 2.Ms.R.Brindha(810018106010) 3.Ms.M.Kaviya(810018106032) PROJECT GUIDE: Dr.S.Subathradevi, Asst.Prof/ECE, Anna University,BITCampus, Trichy, 620024.

- 2. OBJECTIVE The aim of this project is to design a MAC unit circuit which consumes lower area by using vedic square and kogge stone adder.

- 3. In this project work we propose a new architecture for an efficient MAC (Multiplier Accumulator Unit) unit with low area consumption which includes vedic square as an alternate component in the MAC unit. Here, we use vedic square based on the principle of duplex property of Urdhva Tiryagbhya sutra. One MAC unit is implemented by vedic multiplier and kogge stone adder. Another MAC unit is implemented by vedic multiplier and kogge stone adder. Here we comparing these two MAC units. Hence, speed is increased and area is decreased by means of decreased toggling of gates in vedic square. The overall performance of MAC unit is determined by three parameters, namely speed, power and area. The proposed architecture of high speed and low area consumption MAC unit will contribute immensely to the future DSP systems. ABSTRACT

- 4. 4 BIT VEDIC MULTIPLIER

- 5. 4 BIT VEDIC SQUARE

- 6. 4 BIT KOGGE STONE ADDER

- 7. MAC UNIT (using vedic multiplier and kogge stone adder) output

- 8. MAC UNIT (using vedic square and kogge stone adder)

- 9. WORK PLAN MODULES ON FIRST REVIEW ON SECOND REVIEW ON THIRD REVIEW MODULE 1 VEDIC MULTIPLIER (BITS:4,8) VEDIC MULTIPLIER (BITS:16) VEDIC MULTIPLIER (BITS:32) MODULE 2 KOGGE STONE ADDER (BITS:8,16) KOGGE STONE ADDER (BITS:32) KOGGE STONE ADDER (BITS:64) MODULE 3 MAC UNIT (USING VEDIC MUL AND KSA) MAC UNIT (USING VEDIC MUL AND KSA) MAC UNIT (USING VEDIC MUL AND KSA) MODULE 4 VEDIC SQUARE (BITS: 4,8) VEDIC SQUARE (BITS: 16) VEDIC SQUARE (BITS: 32) MODULE 5 KOGGE STONE ADDER (BITS :8,16) KOGGE STONE ADDER (BITS :32) KOGGE STONE ADDER (BITS : 64) MODULE 6 MAC UNIT (USING VEDIC SQUARE AND KSA) MAC UNIT (USING VEDIC SQUARE AND KSA) MAC UNIT (USING VEDIC SQUARE AND KSA)

- 10. COMPLETED MODULE VEDIC MULTIPLIER AND KOGGE STONE ADDER Half adder - synthesized and simulated. Full adder- synthesized and simulated. 4-bit vedic multiplier and kogge stone adder- synthesized and simulated. Mac unit using vedic multiplier and kogge stone adder- synthesized and simulated. 8-bit vedic multiplier and kogge stone adder- synthesized and simulated. Mac unit using vedic multiplier and kogge stone adder- synthesized and simulated. 16-bit vedic multiplier and kogge stone adder- synthesized and simulated. Mac unit using vedic multiplier and kogge stone adder- synthesized and simulated. 32-bit vedic multiplier and kogge stone adder- synthesized and simulated. Mac unit using vedic multiplier and kogge stone adder- synthesized and simulated.

- 11. COMPLETED MODULE VEDIC SQUARE AND KOGGE STONE ADDER Half adder - synthesized and simulated. Full adder- synthesized and simulated. 4-bit vedic square and kogge stone adder- synthesized and simulated. Mac unit using vedic square and kogge stone adder- synthesized and simulated. 8-bit vedic square and kogge stone adder- synthesized and simulated. Mac unit using vedic square and kogge stone adder- synthesized and simulated. 16-bit vedic square and kogge stone adder- synthesized and simulated. Mac unit using vedic square and kogge stone adder- synthesized and simulated. 32-bit vedic square and kogge stone adder- synthesized and simulated. Mac unit using vedic square and kogge stone adder- synthesized and simulated.

- 12. MAC UNIT 4 BIT 8 BIT slices LUT’s Delay in ns slices LUT’s Delay in ns Vedic multiplier 20/4656 36/9312 14.079 107/4656 193/9312 25.713 Kogge stone adder 8/4656 14/9312 12.540 20/4656 36/9312 19.909 MAC UNIT (vedic mul & kogge stone adder) 35/4656 61/9312 149/4656 266/9312 Vedic square 3/4656 6/9312 6.422 21/4656 36/9312 14.183 Kogge stone adder 8/4656 14/9312 12.540 20/4656 36/9312 19.909 MAC UNIT (vedic squ & kogge stone adder) 14/4656 26/9312 49/4656 92/9312

- 13. MAC UNIT 16 bit 32 bit slices LUT’s Delay in ns slices LUT’s Delay in ns vedic multiplier 441/4656 771/9312 45.984 1869/4 656 3259/931 2 82.077 kogge stone adder 47/4656 87/9312 23.035 98/465 6 179/9312 23.134 MAC unit (vedic mul & ksa) 517/4656 920/9312 2043/4 656 3601/931 2 Vedic square 70/4656 122/9312 24.394 244/46 56 424/9312 44.396 Kogge stone adder 47/4656 87/9312 23.035 98/465 6 179/9312 23.134 MAC unit (vedic square & ksa) 152/4656 281/9312 416/46 56 759/9312

- 14. TOOLS USED 1) Xilinx is a software tool used. 2) HDL Verilog code is used.

- 15. REFERENCES [1] Gitika Bhatia, Karanbir Singh Bhatia, “An Efficient MAC Unit Low Area Consumption” International Conference on Advances in Recent Technologies in Communication and Computing, 2015, pp. 186-355 [2] D. C. Chen, L. M. Guerra, E. H. Ng, M. Potkonjak, D. P. Schultz, and J. M. Rabaey, “An integrated system for rapid prototyping of high performance algorithm specific data paths,” International Conference on Application Specific Array Processors, Aug 1992, pp. 134-148 [3] Aminul Islam, M.W. Akram, S.D. Pable, Mohd. Hasan, "Design and Analysis of Robust Dual Threshold CMOS Full Adder Circuit in 32nm Technology”, International Conference on Advances in Recent Technologies in Communication and Computing, 2010, pp. 418-420 [4] Deepa Sinha, Tripti Sharma, K.G.Sharma, Prof B.P Singh, “Design and Analysis of low Power 1-bit Full Adder Cell”, International Conference on Electronics Computer Technology (ICECT), Vol. 2, 2011, pp. 303-305

- 16. [5] Nabihah Ahmad, Rezaul Hasan, “A new Design of XOR-XNOR gates for Low Power application”, International Conference on Electronic Devices, Systems and Applications (ICEDSA), 2011, pp. 45-49 [6] R.Uma, “4-Bit Fast Adder Design: Topology and Layout with Self-Resetting Logic for Low Power VLSI Circuits”, International Journal of Advanced Engineering Sciences and Technology, Vol No. 7, Issue No. 2, 2011, pp. 29-37 [7] David J. Willingham and izzet Kale, “A Ternary Adiabatic Logic (TAL) Implementation of a Four-Trit Full-Adder, NORCHIP, 2011, pp. 1-4 [8] Padma Devi, Ashima Girdher and Balwinder Singh, “Improved Carry Select Adder with Reduced Area and Low Power Consumption”, International Journal of Computer Application, Vol 3. Issue.4, June 2010, pp. 14-18 .