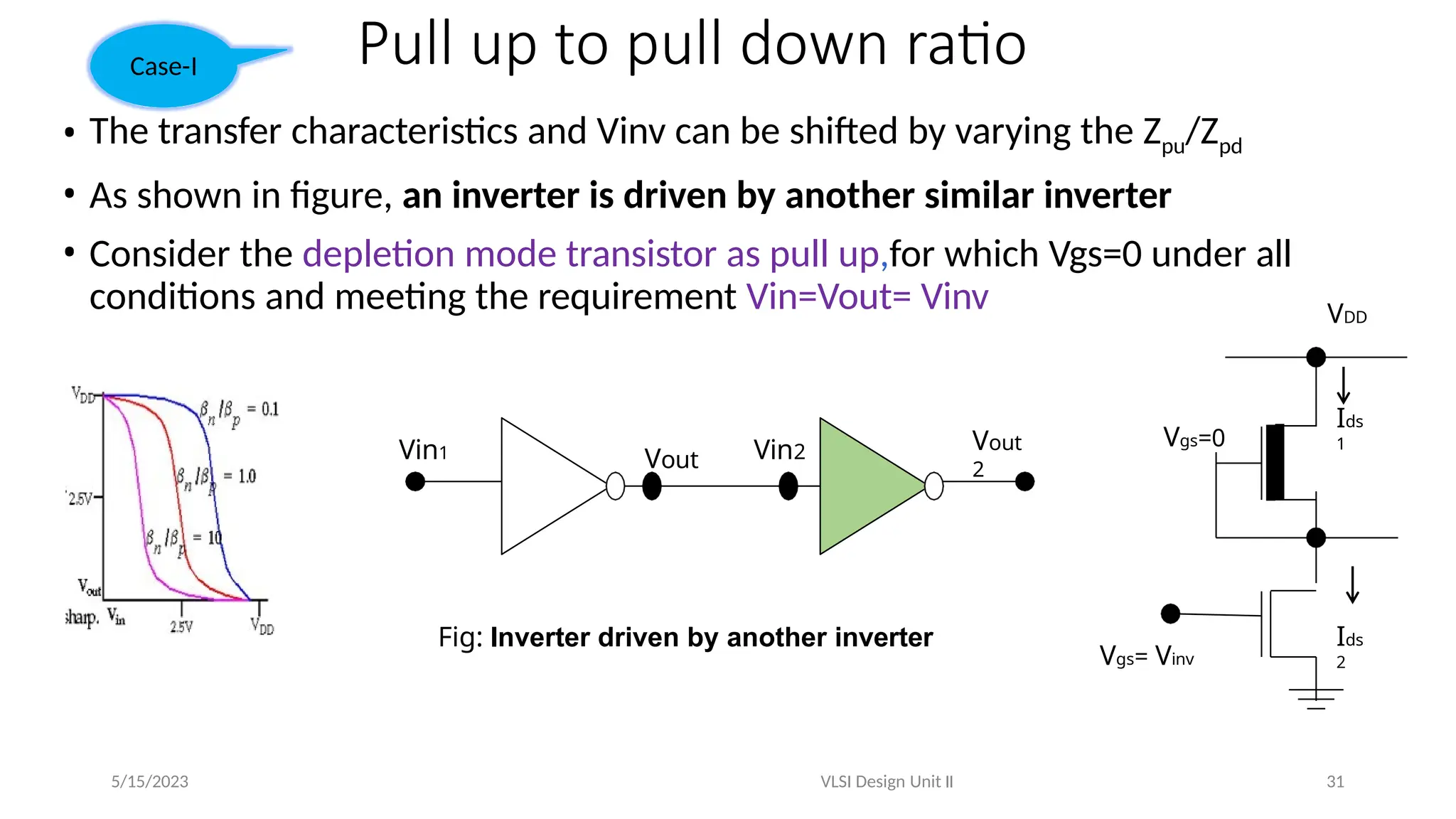

The document outlines the basic electrical properties and principles of MOS transistors, including essential parameters like threshold voltage, transconductance, and drain current characteristics in different operational modes (cut-off, non-saturation, and saturation). It also details the implementation of NMOS and CMOS inverters, along with pass transistor logic and their performance in switching applications. Additionally, the document discusses the pull-up and pull-down ratios in inverter configurations influenced by various circuit components and parameters.

![Summary of normal conduction characteristics:

Cut-off : accumulation, Ids is essentially zero.

Non-saturated : weak inversion, Ids dependent on both Vgs and Vds .

Saturated : strong inversion, Ids is ideally independent of Vds.

Region NMOS

Non-saturation/

Triode

VDS < VDS(sat)

I k' W

(V V )V

1

V 2

TN DS

2

DS

R

VDS

DSon

I

D

Saturation/

Pinch-off

VDS > VDS(sat)

k '

W 2

ID n

[VGS VTN ] 2

L

Transition between triode

and pinch-off

VDS(sat) = VGS - VTN

7](https://image.slidesharecdn.com/elecricalproperties-250103095209-66bcb9f6/75/Elecrical-Propertiesddfafafafafafafav-pptx-3-2048.jpg)