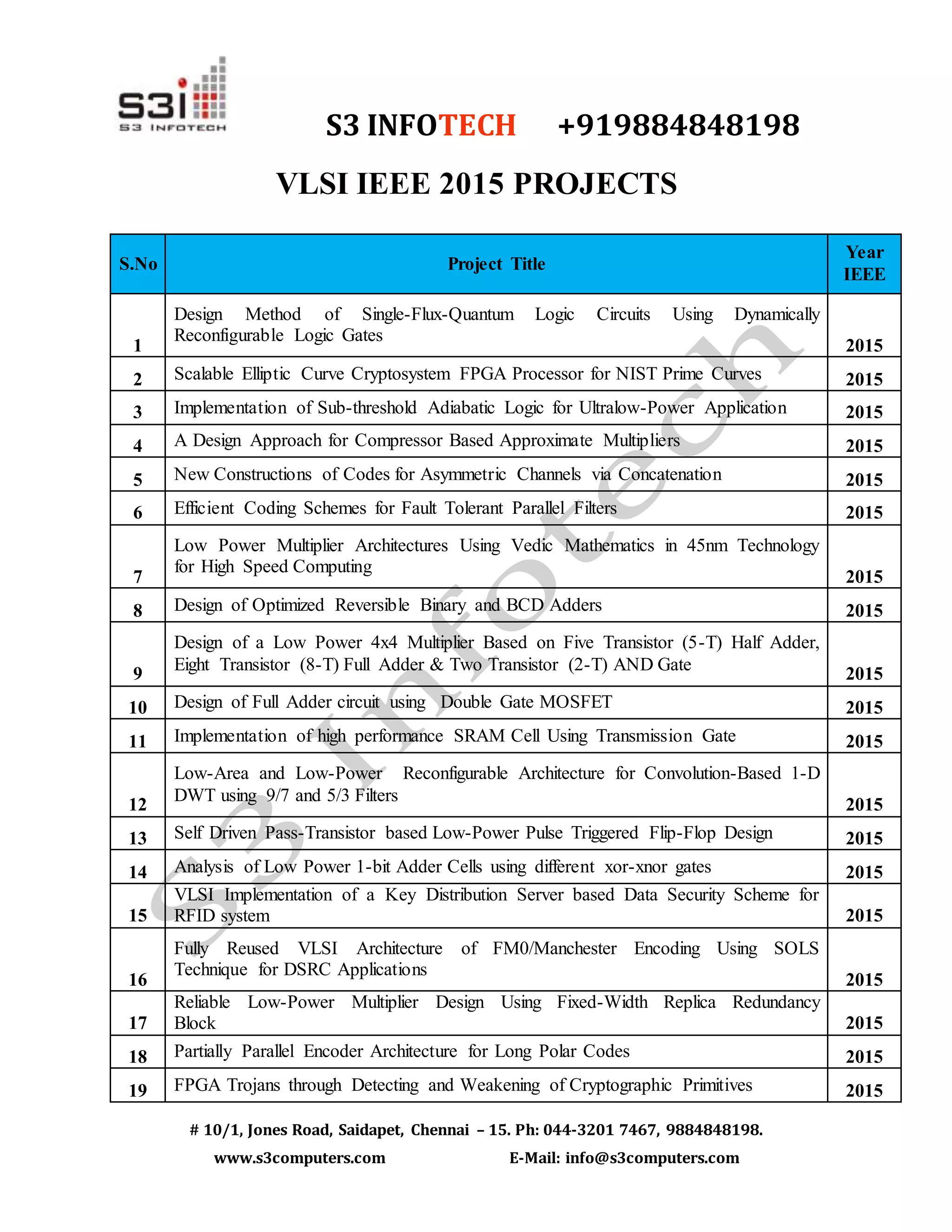

This document contains details of VLSI projects completed in 2015 and 2014. It lists 23 projects completed in 2015 related to topics like logic circuit design using single-flux-quantum, elliptic curve cryptosystem processors, approximate multipliers, reversible adders, and low power SRAM cells. It also lists 12 projects completed in 2014 on topics such as carry-select adders, shift registers, neural networks, barrel shifters, multipliers, and reversible circuitry for computations. The document appears to be listing details of student or research projects conducted by S3 Infotech in the areas of very-large-scale integration (VLSI) design and implementation.