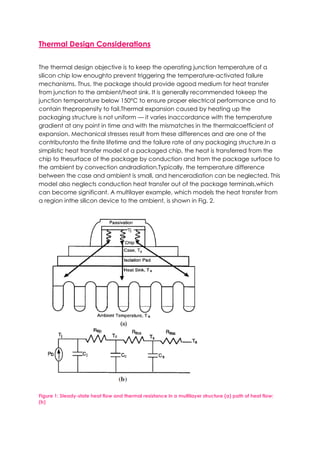

This document discusses various packaging considerations and types for VLSI devices. It covers key design parameters like number of terminals, electrical, thermal, and reliability considerations. It then describes various package types including through hole packages, surface mount packages, flip chip packages, chip size packages, multi-chip modules, and 3D packaging. The goal of packaging is to protect the chip, provide electrical connections, and dissipate heat while meeting requirements for performance, cost, reliability, and manufacturability.