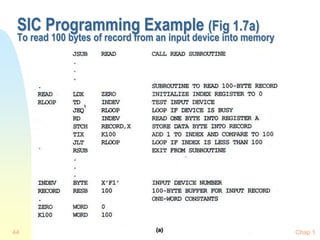

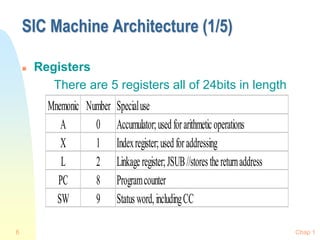

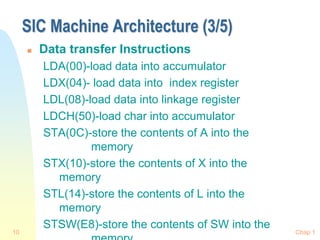

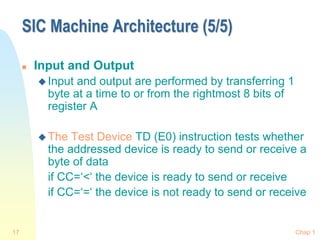

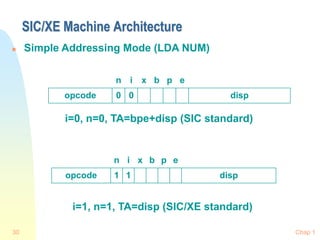

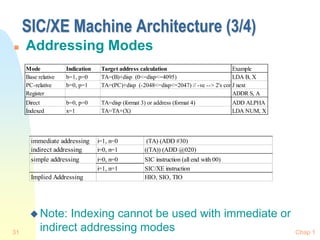

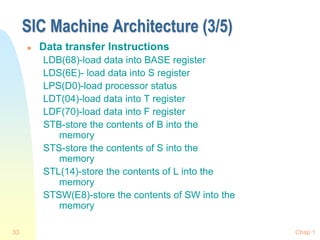

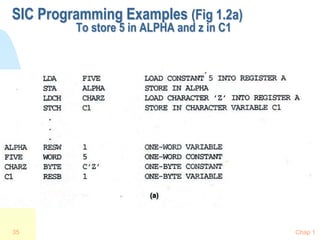

This document describes the architecture of the Simplified Instructional Computer (SIC) and its extended version SIC/XE. It outlines the key components of each machine including memory size and organization, registers, instruction formats, addressing modes, and instruction sets. Examples of assembly language instructions are provided for both SIC and SIC/XE to illustrate how specific tasks like data transfer, arithmetic operations, and input/output can be programmed.

![Chap 1

41

SIC Programming Example (Fig 1.5a)

GAMMA[I]=ALPHA[I]+BETA[I]

I=0 to 100](https://image.slidesharecdn.com/systemsoftware-230327085842-693130eb/85/system-software-ppt-41-320.jpg)