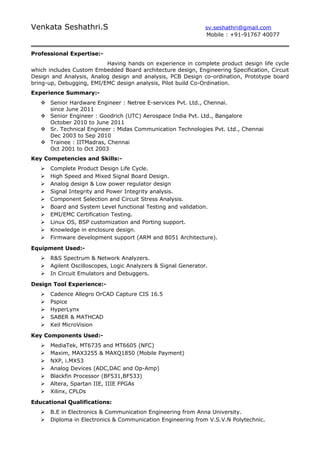

Venkata Seshathri is a senior hardware engineer with over 13 years of experience in product design, embedded systems, and testing. He has expertise in circuit design, PCB design, analog and mixed-signal design, and EMI/EMC testing. Some of his projects include designing smart POS systems for retail applications, performing component stress analysis for aerospace power systems, and developing testing equipment for wireless communication modules. He is proficient in various design tools and has worked with processors like NXP i.MX53, Blackfin, and MediaTek.