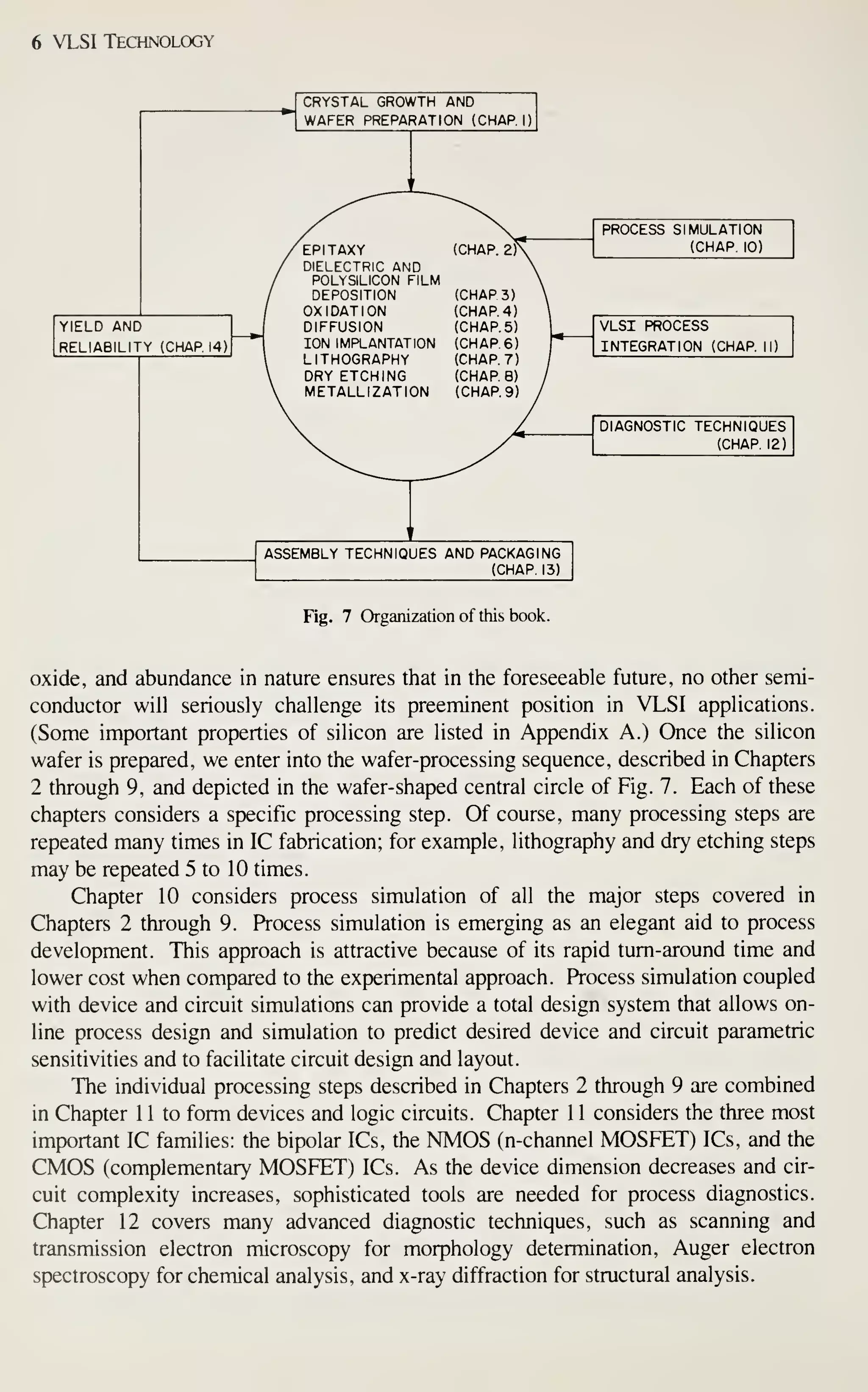

This document provides an introduction to the McGraw-Hill book "VLSI Technology" which describes the theoretical and practical aspects of very-large-scale integration (VLSI). The book covers all major steps in VLSI circuit fabrication from crystal growth to reliability testing. Each chapter focuses on one aspect of the VLSI process, providing an introduction, the underlying science, requirements for steps, and tradeoffs. The book is intended as a textbook for senior undergraduates or graduate students in electrical engineering or applied physics.

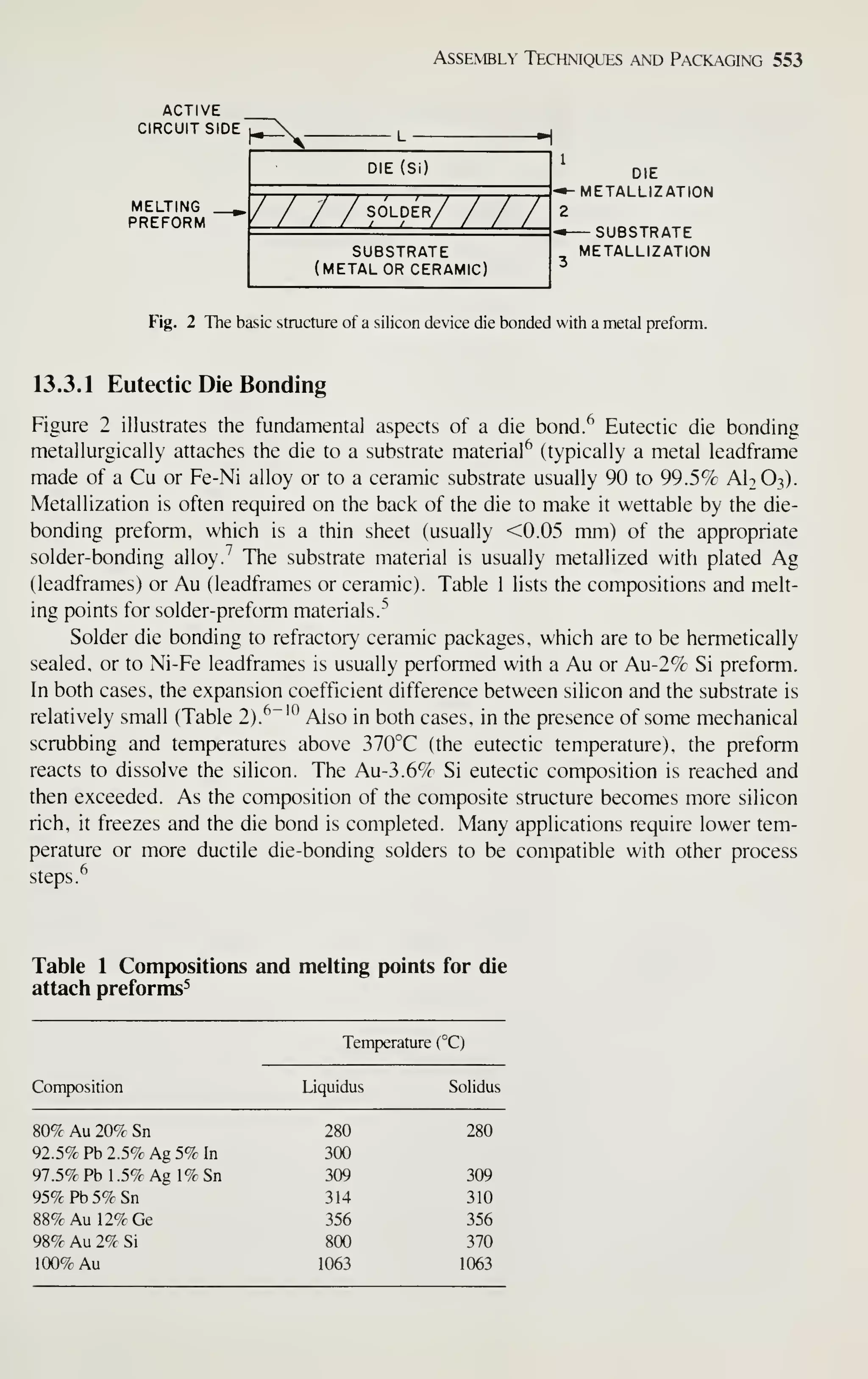

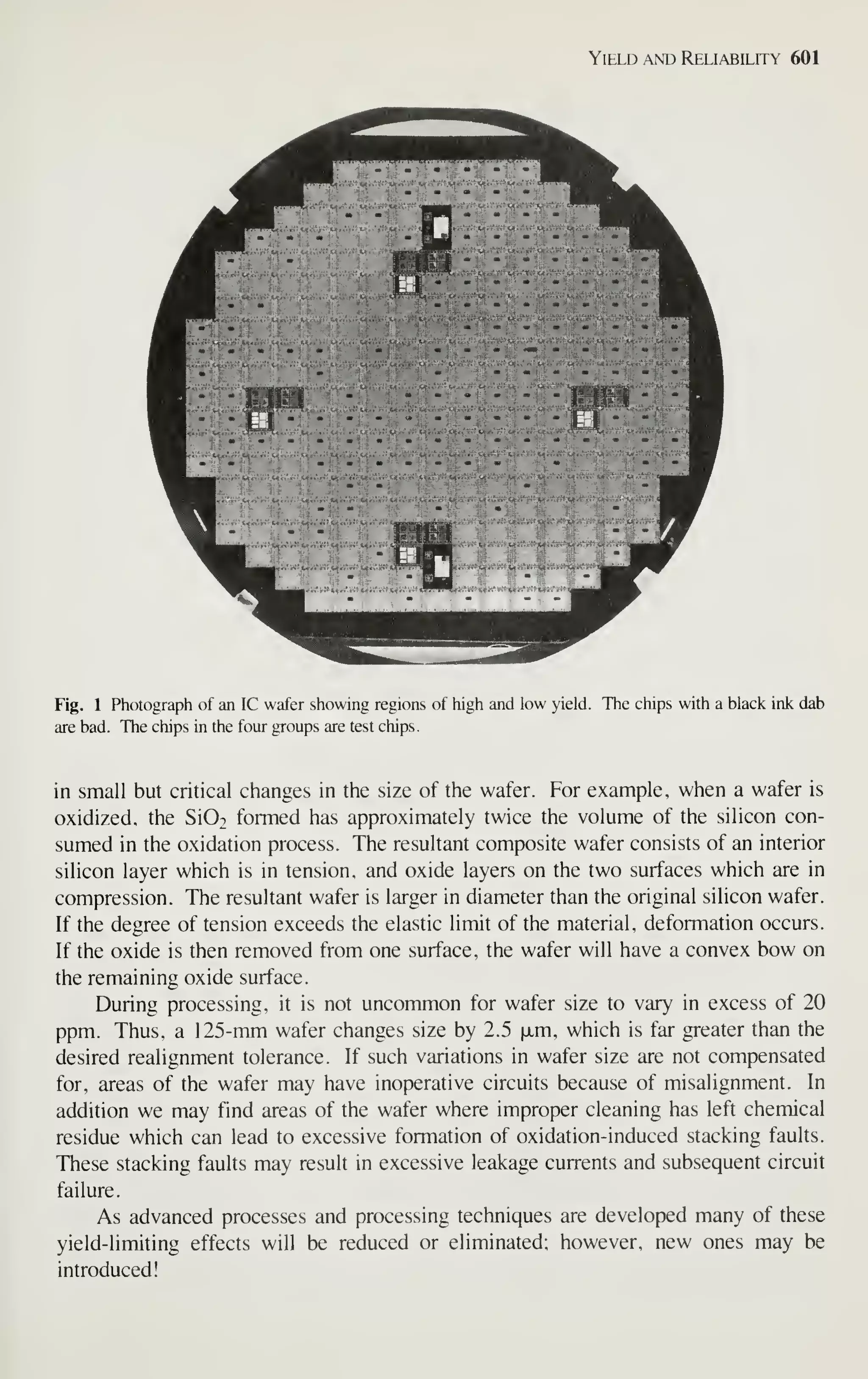

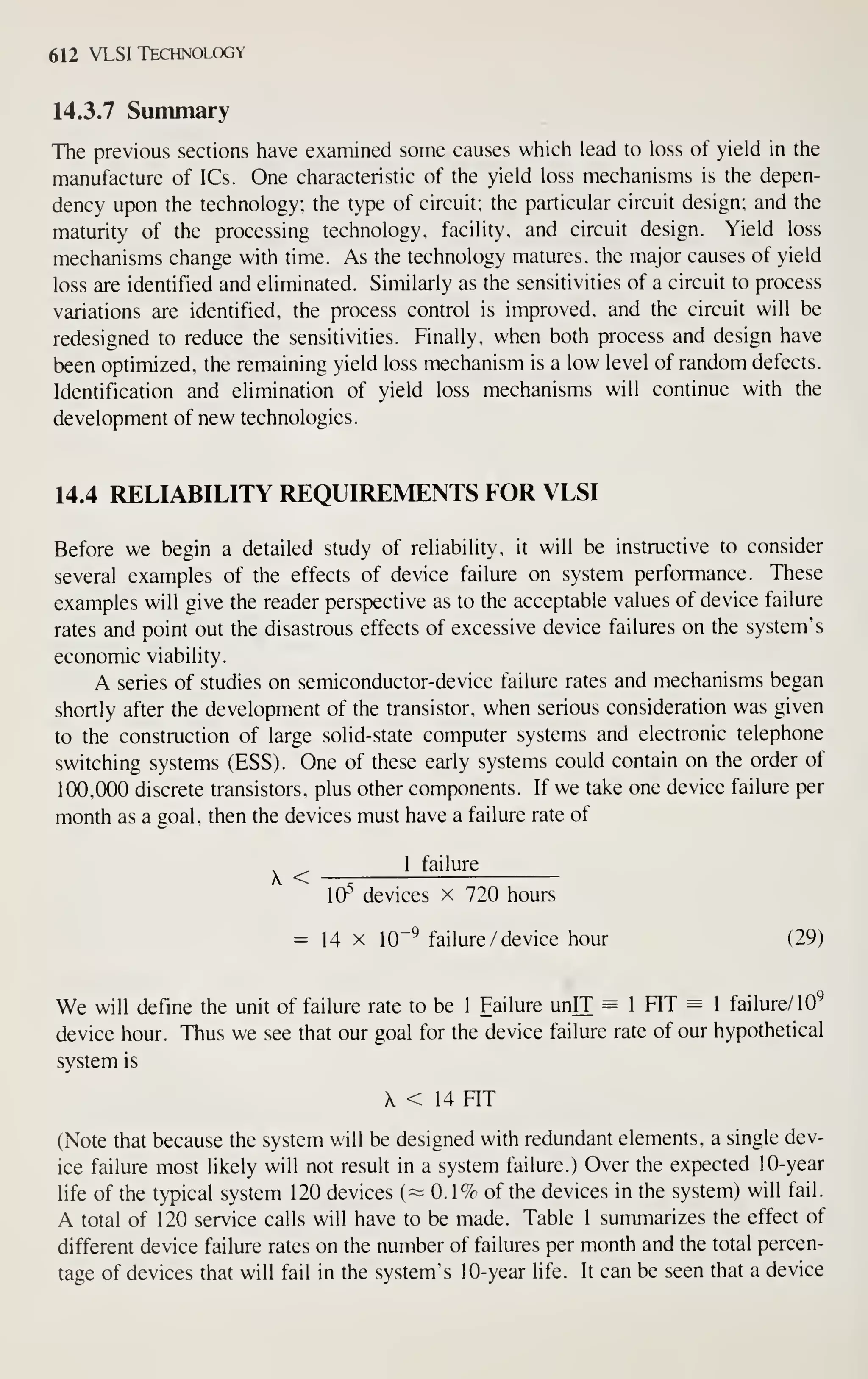

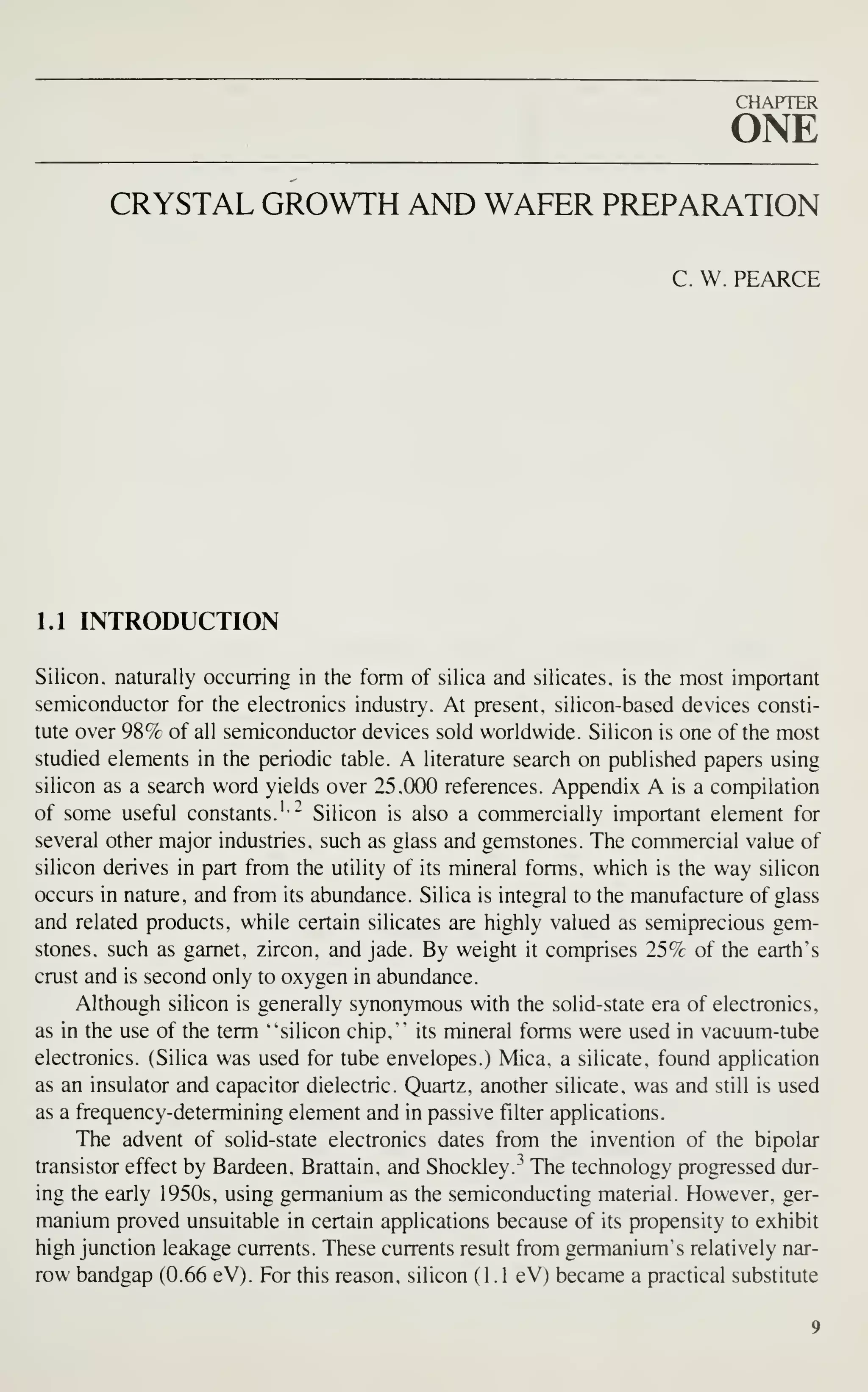

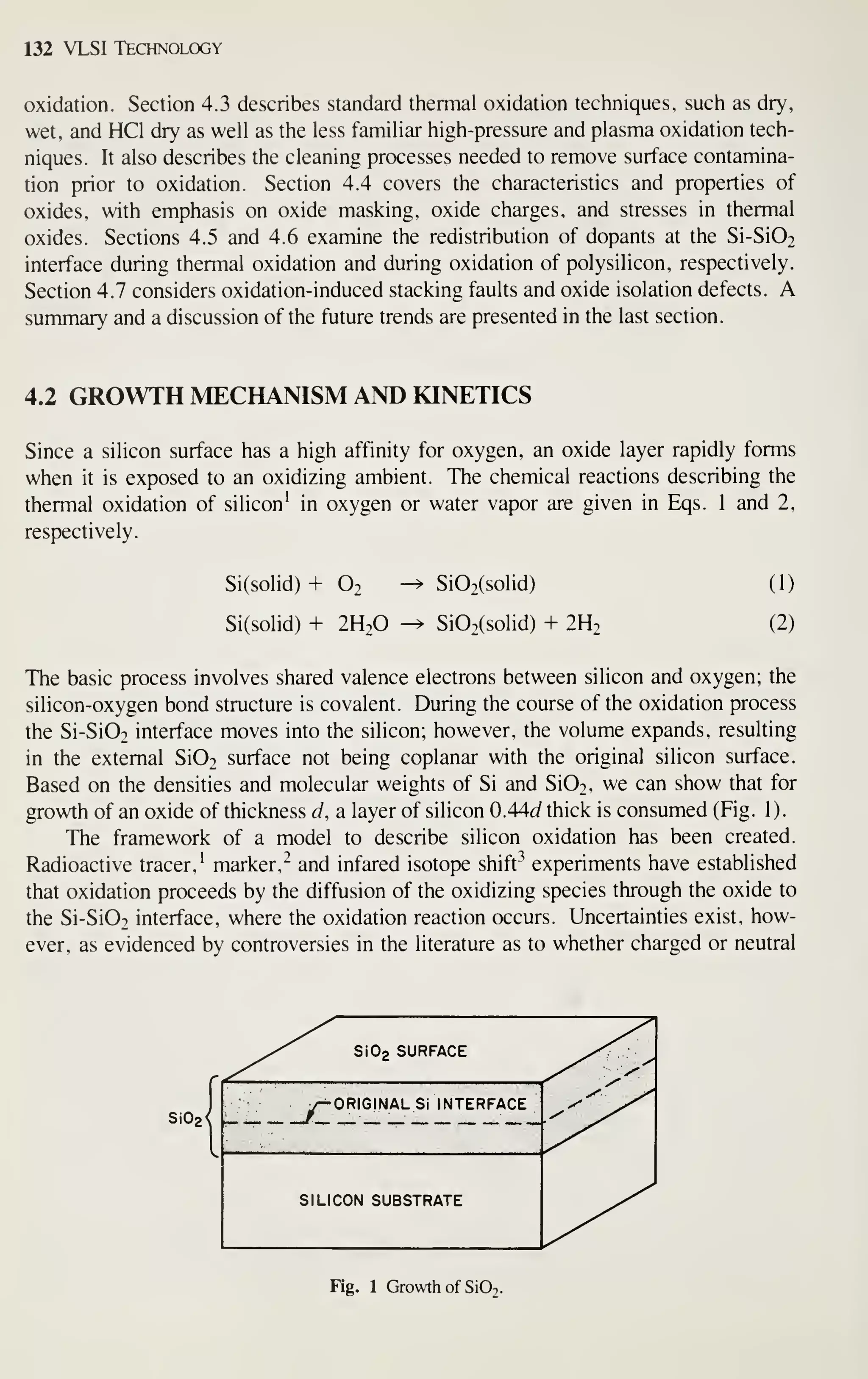

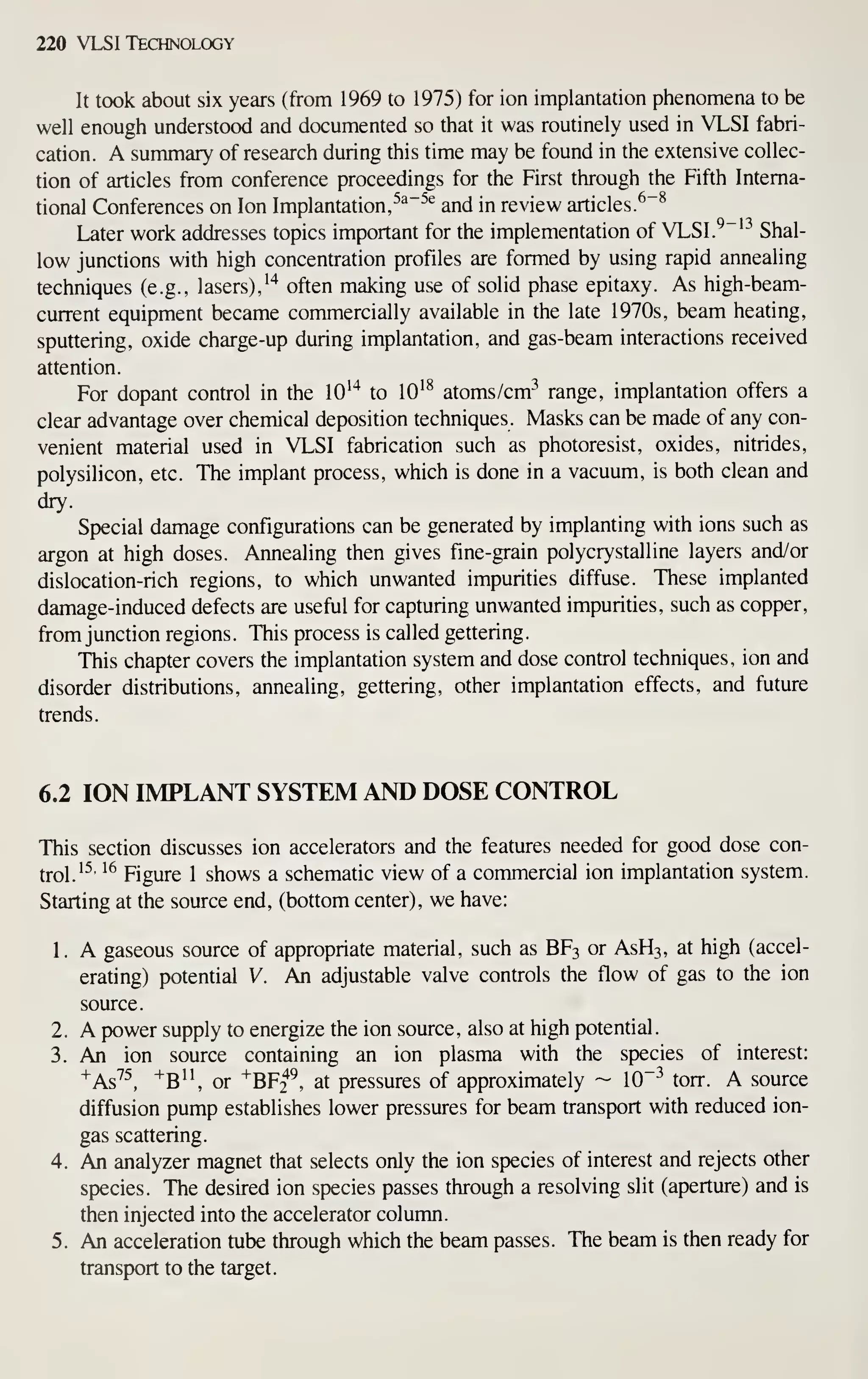

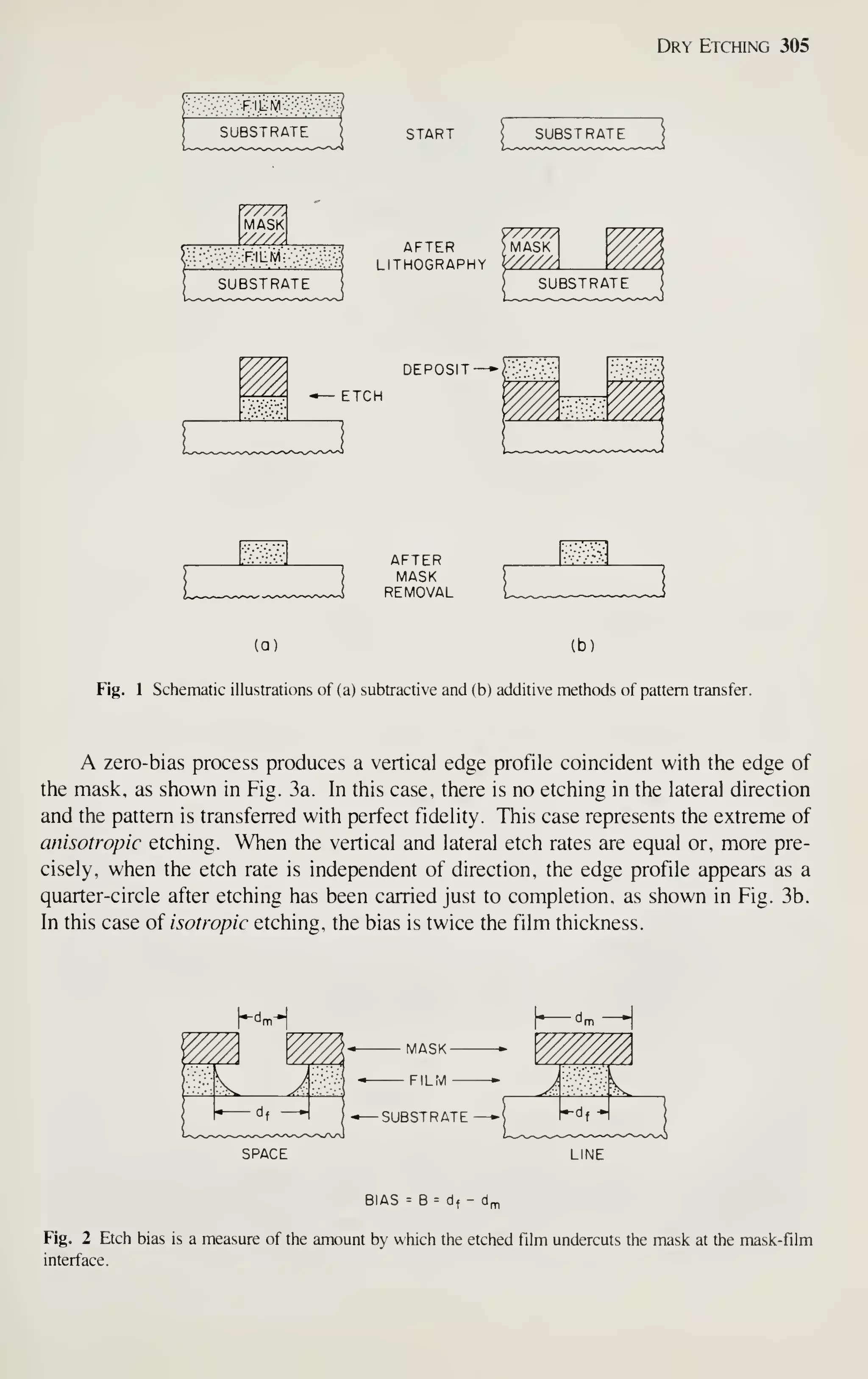

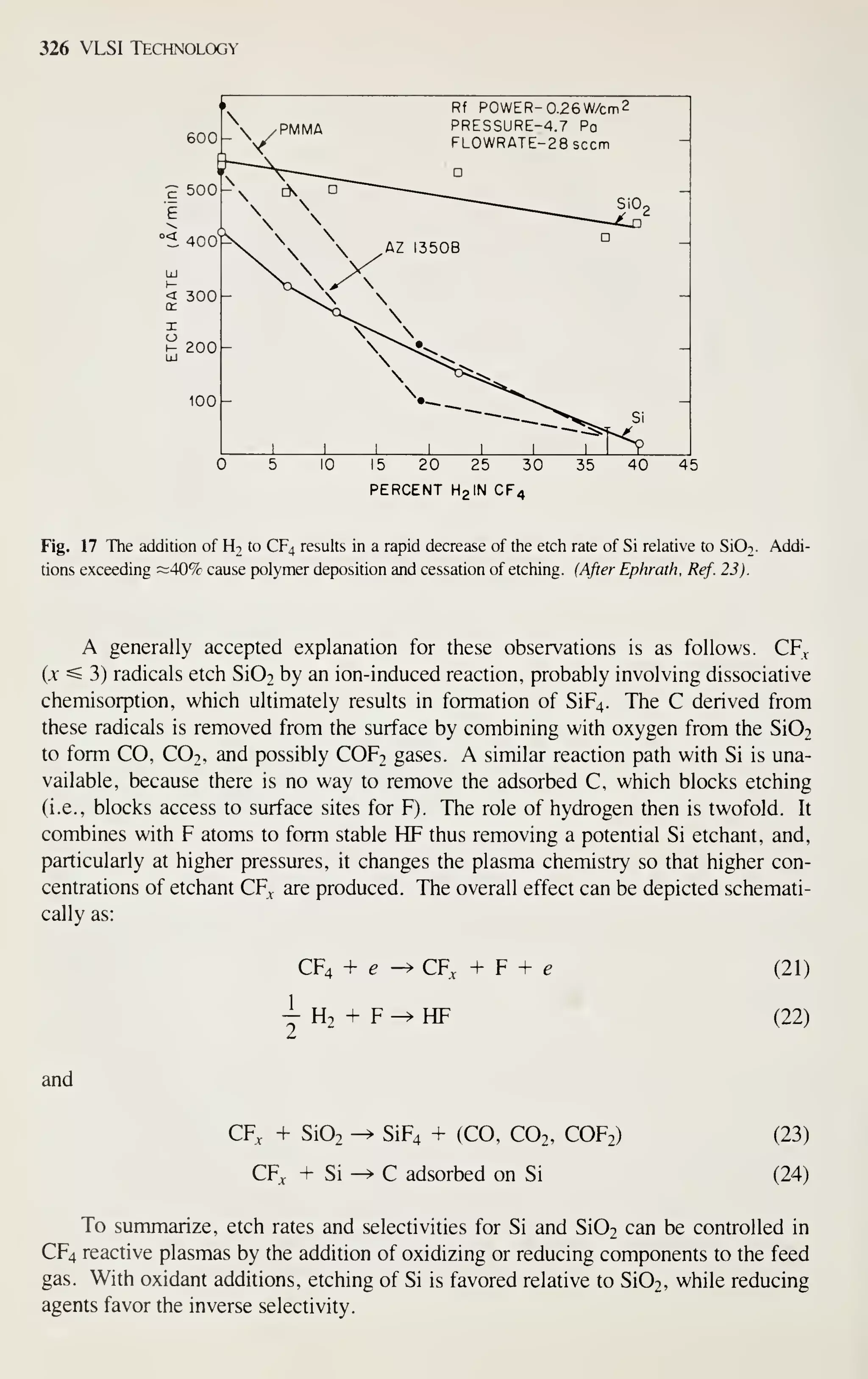

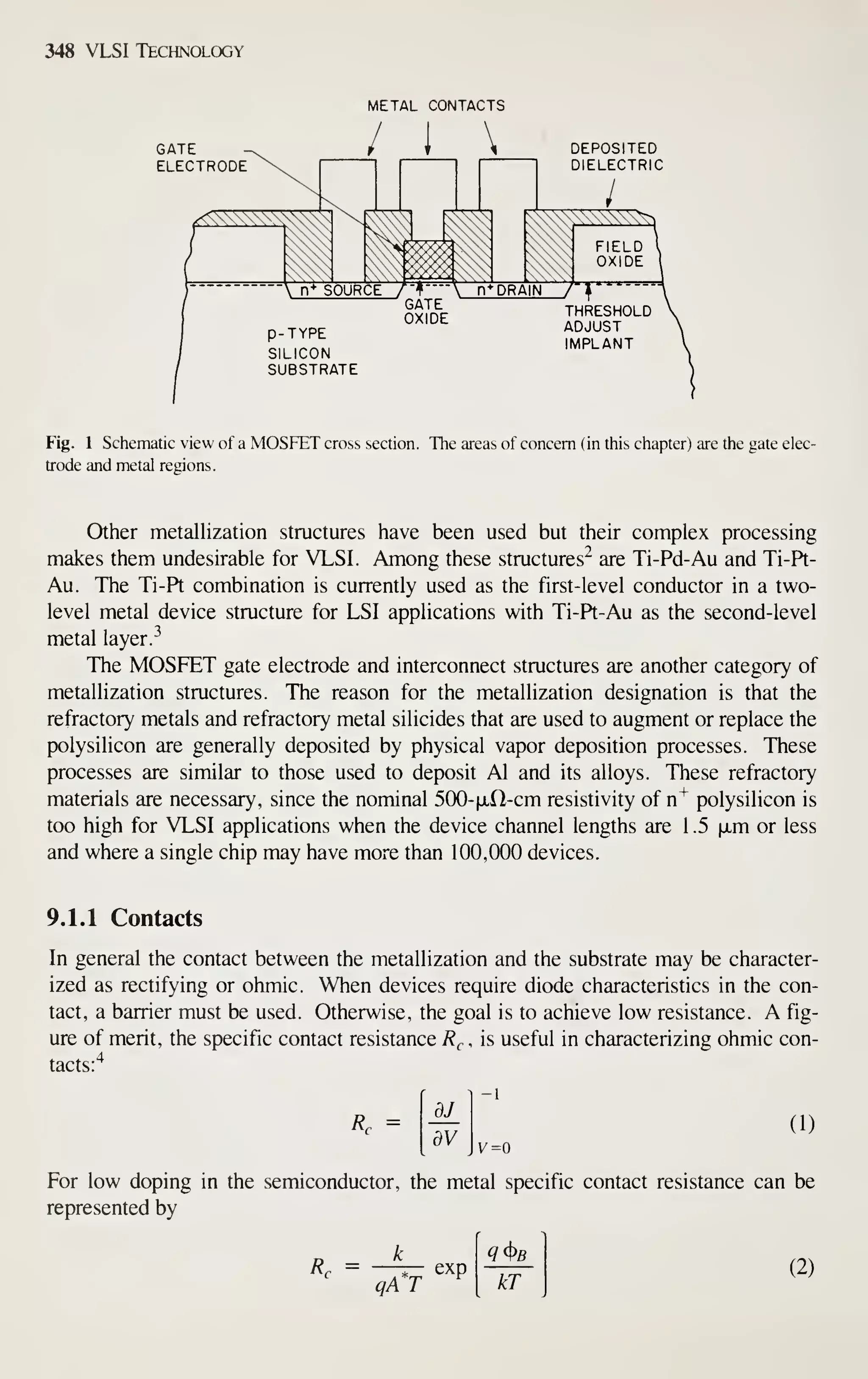

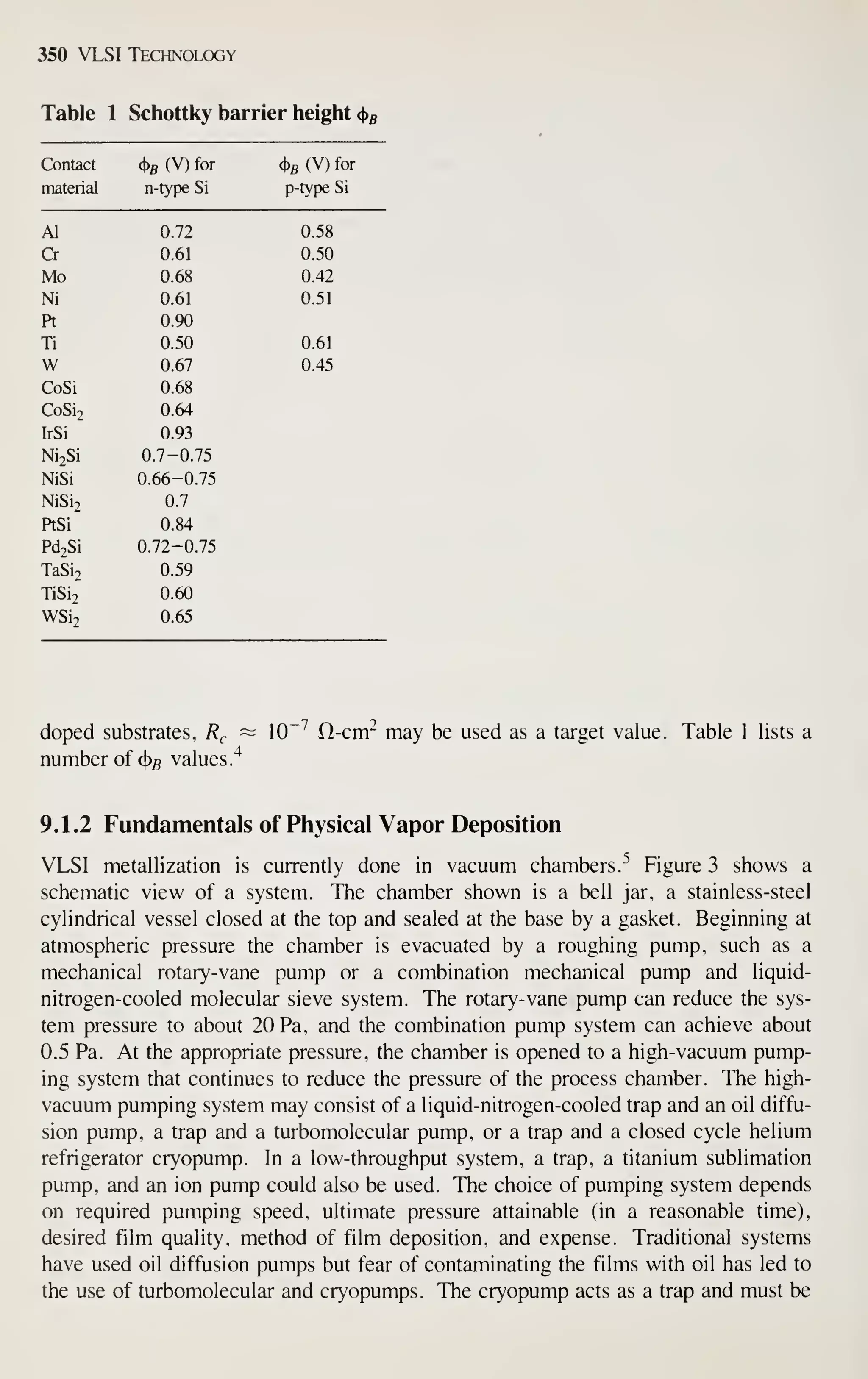

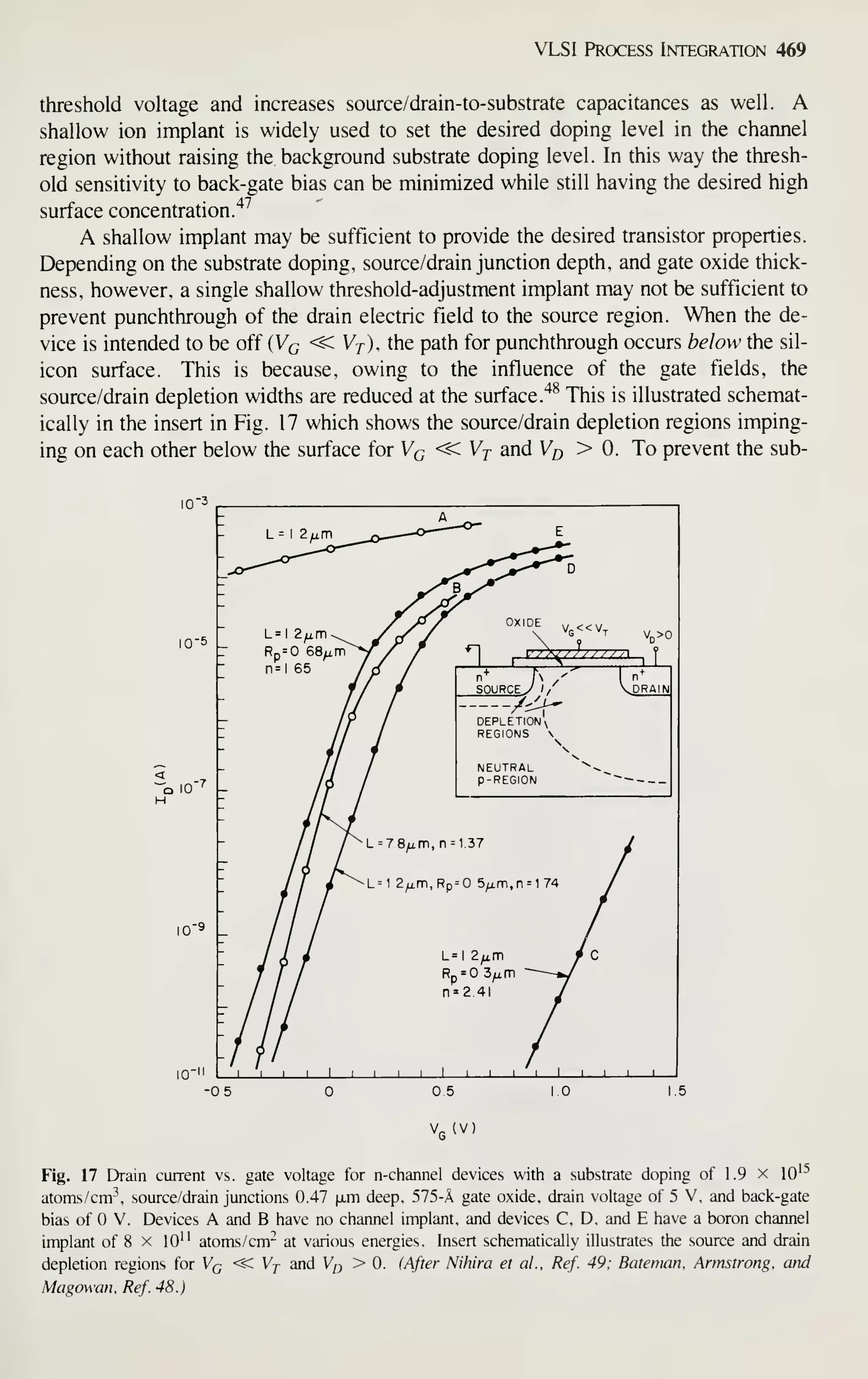

![INTRODUCTION

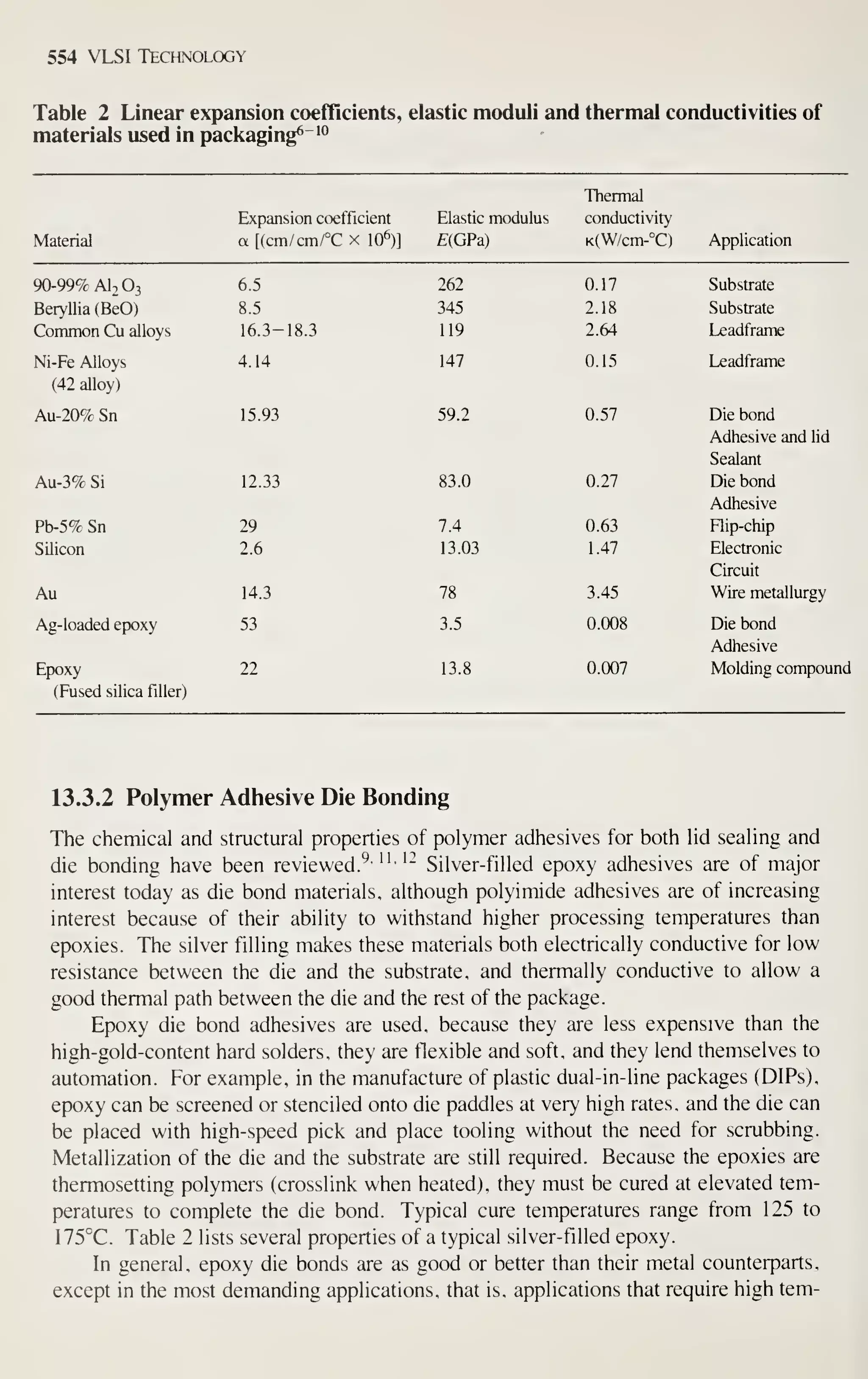

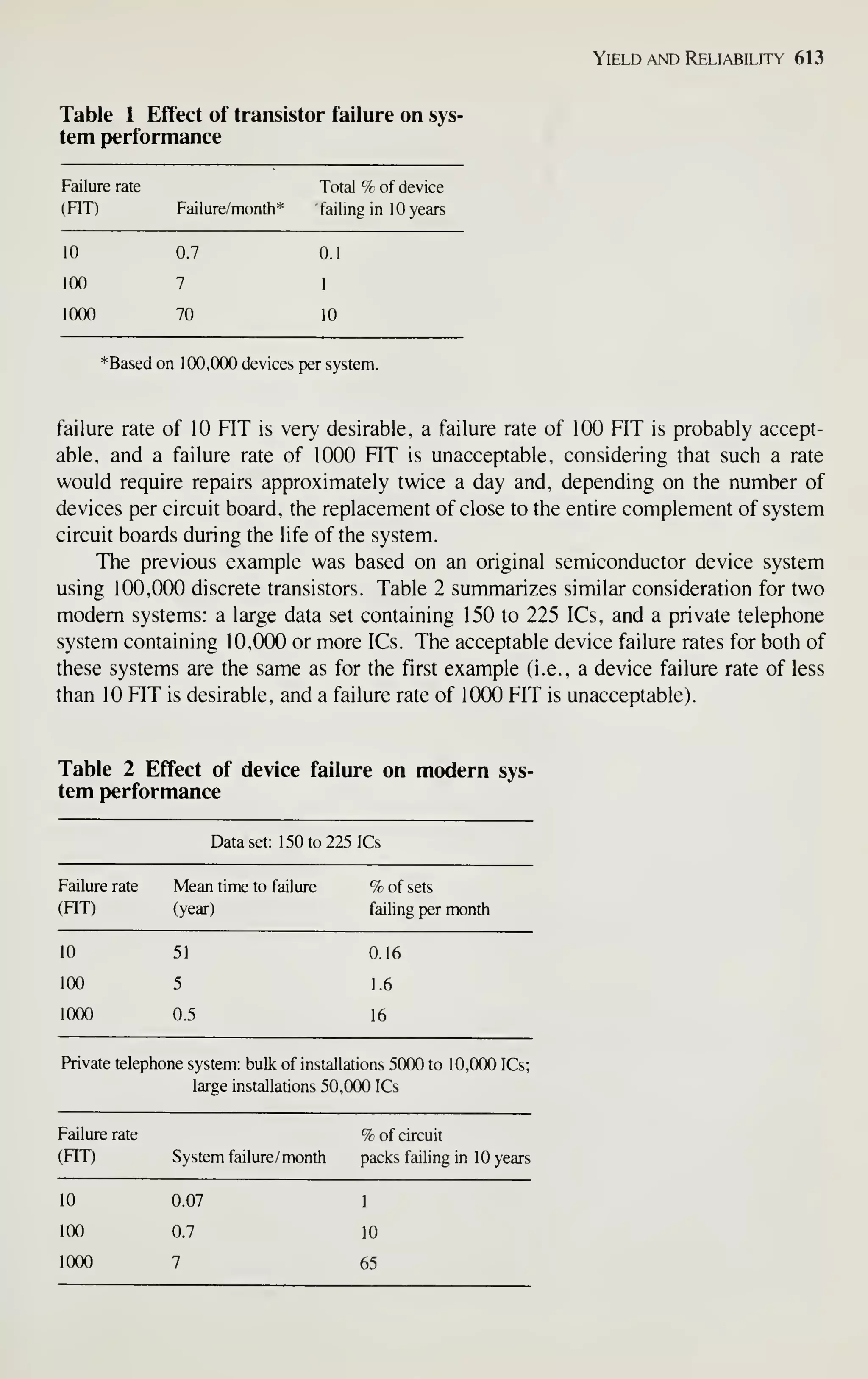

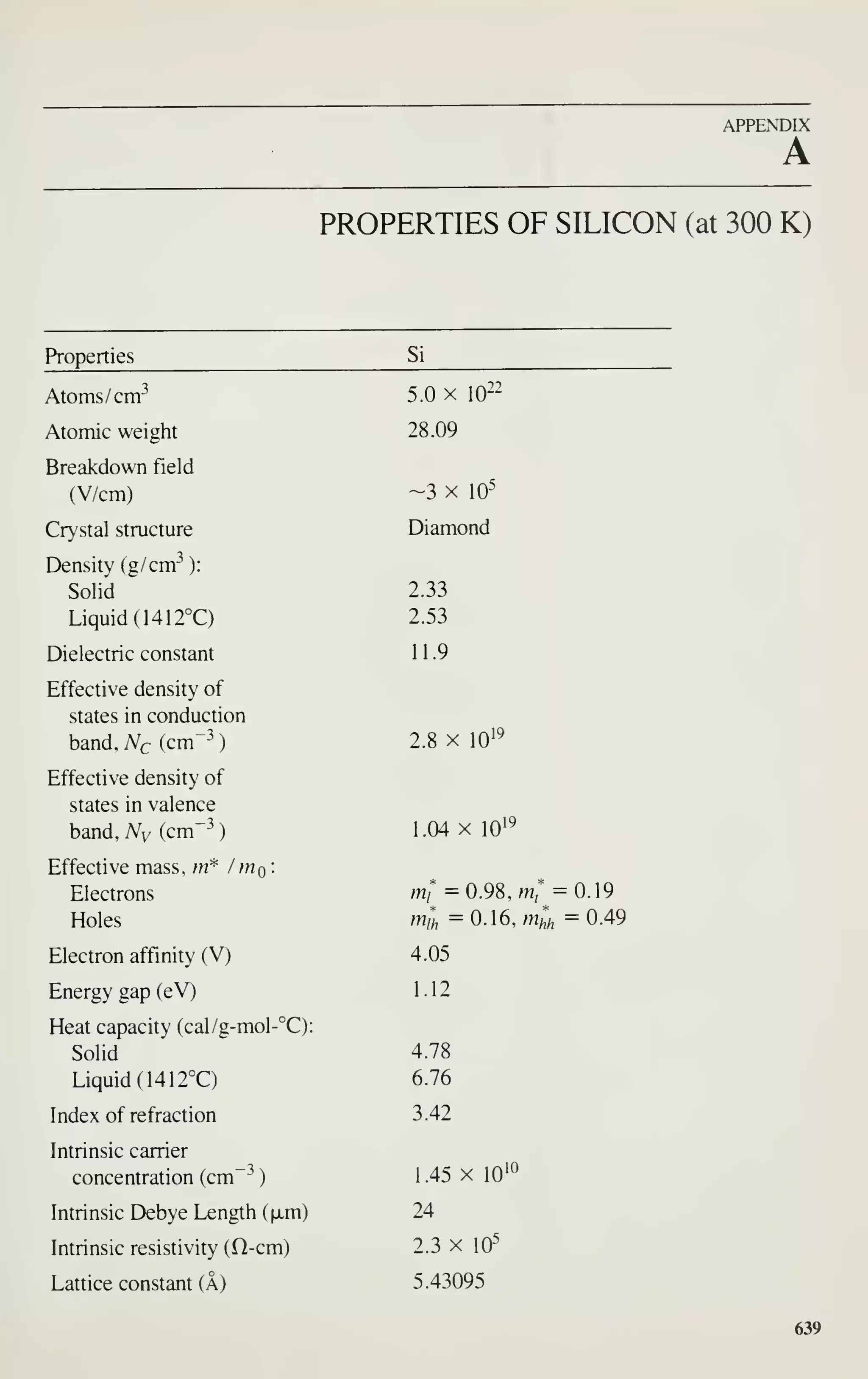

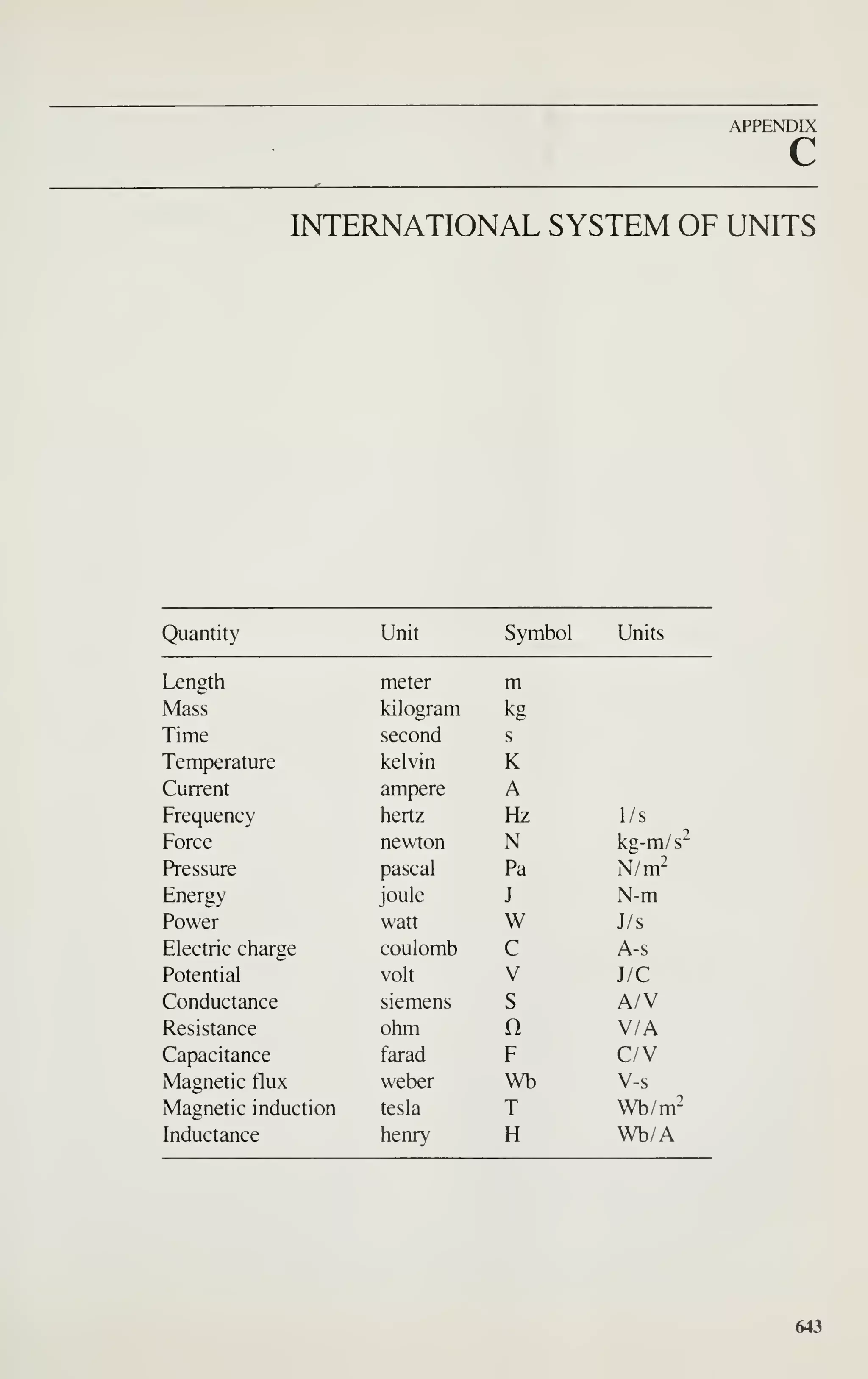

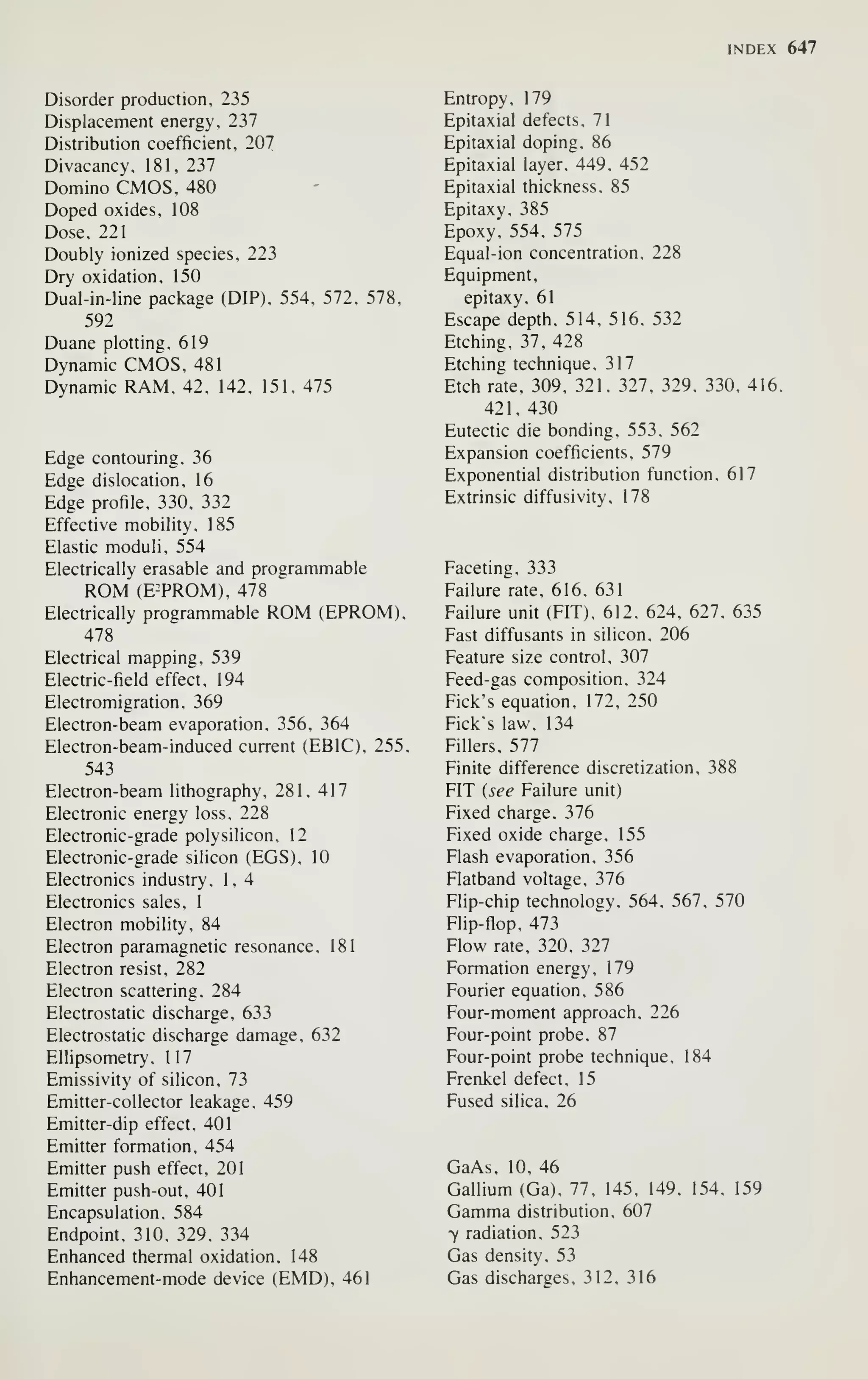

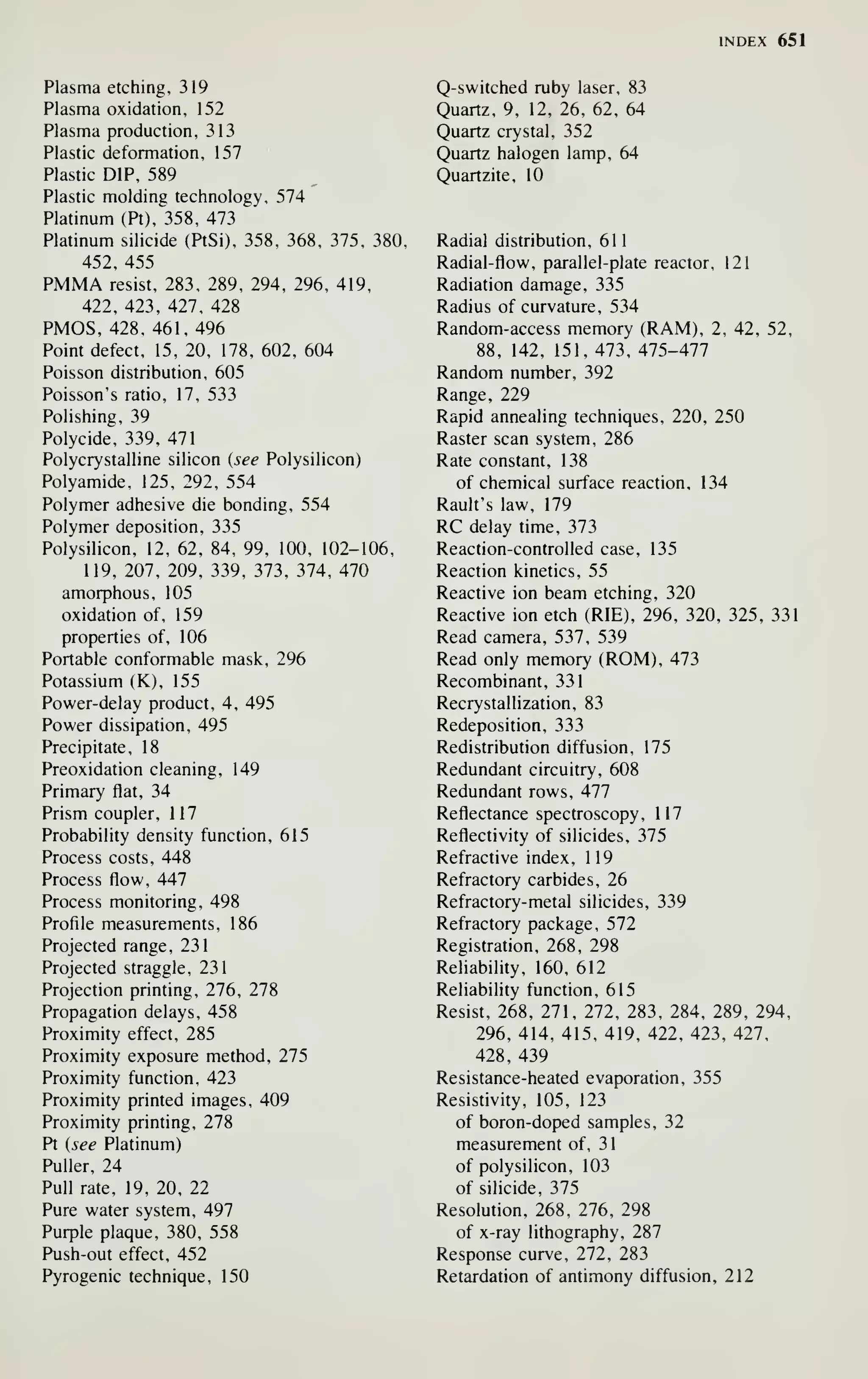

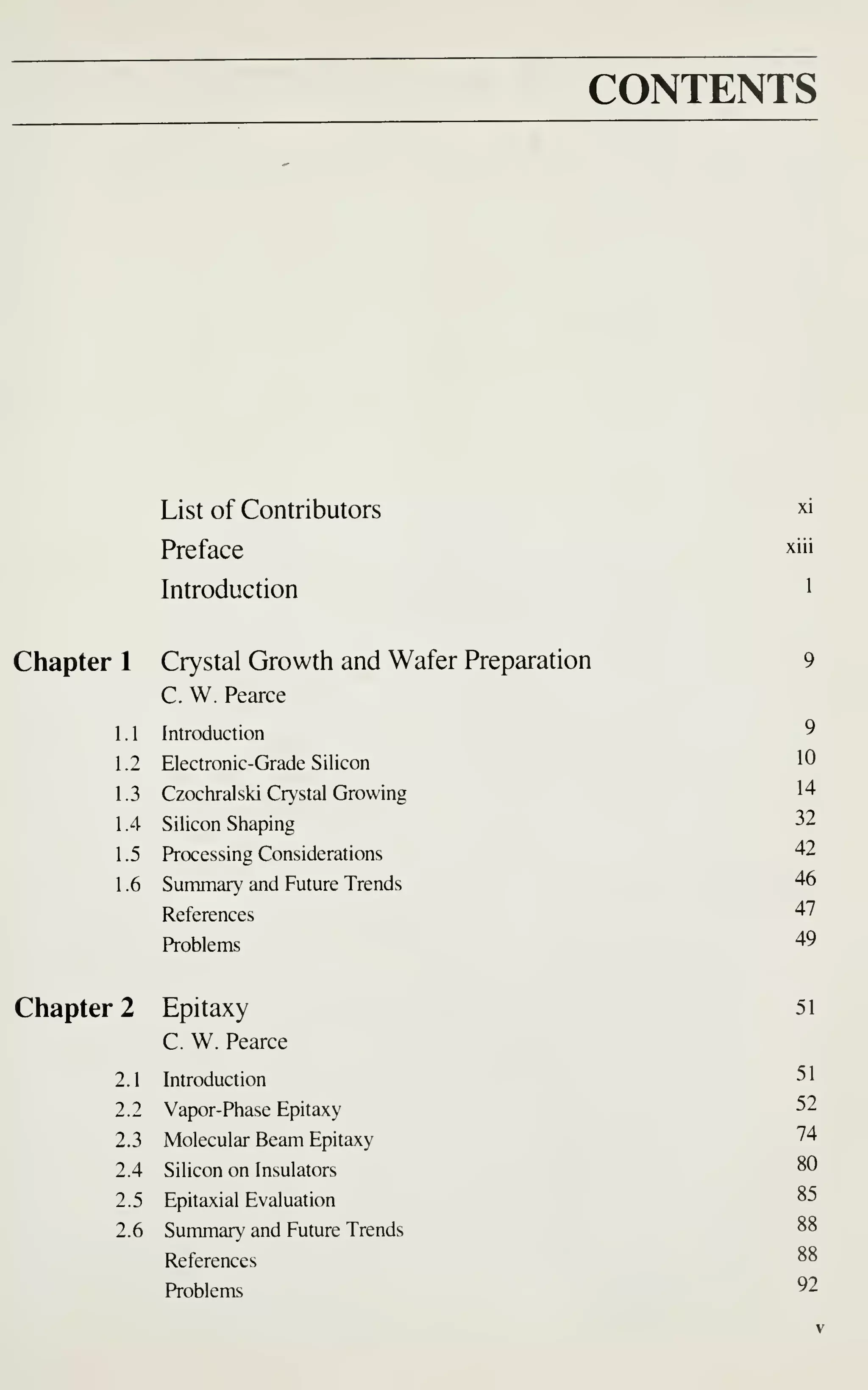

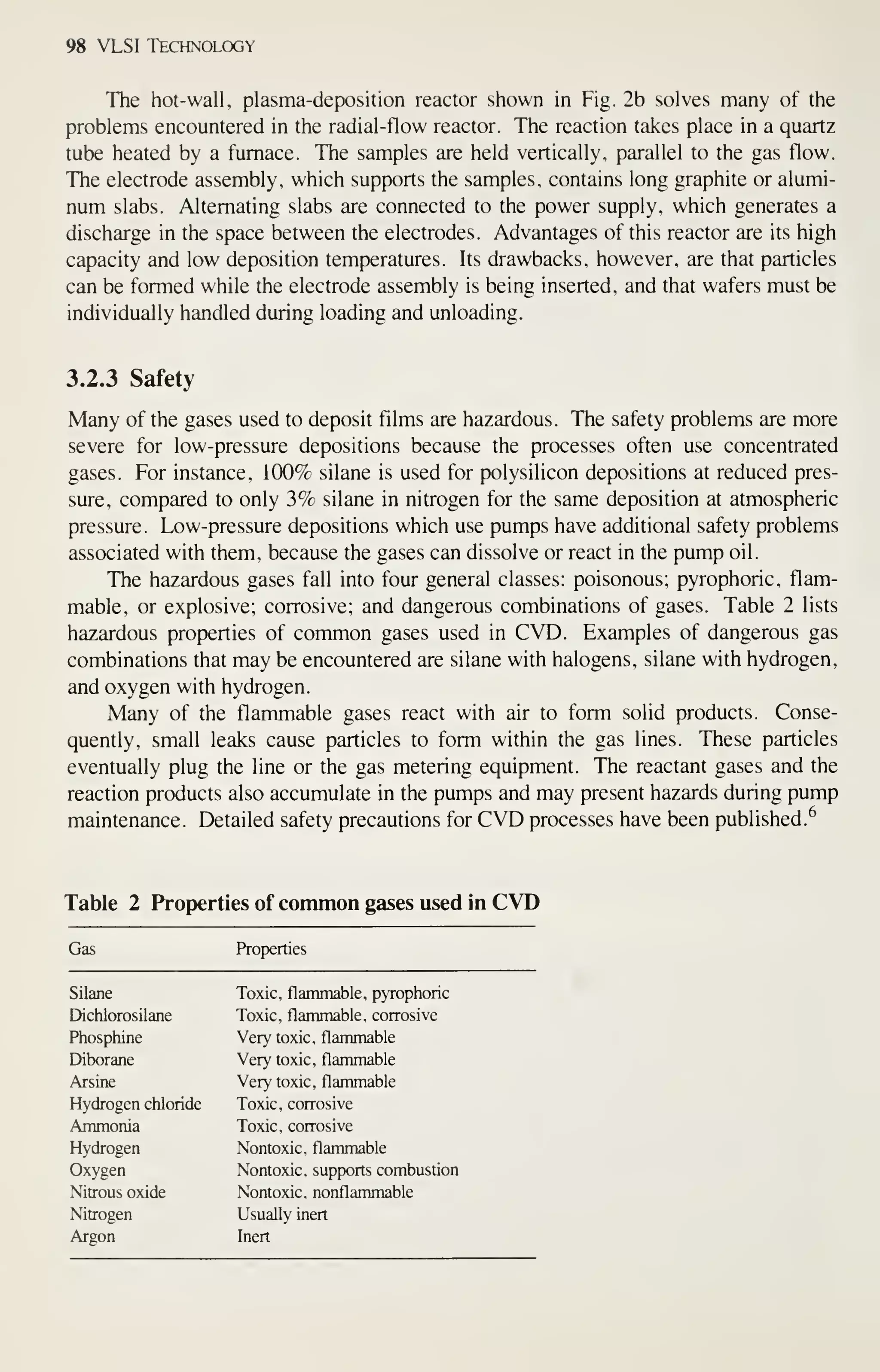

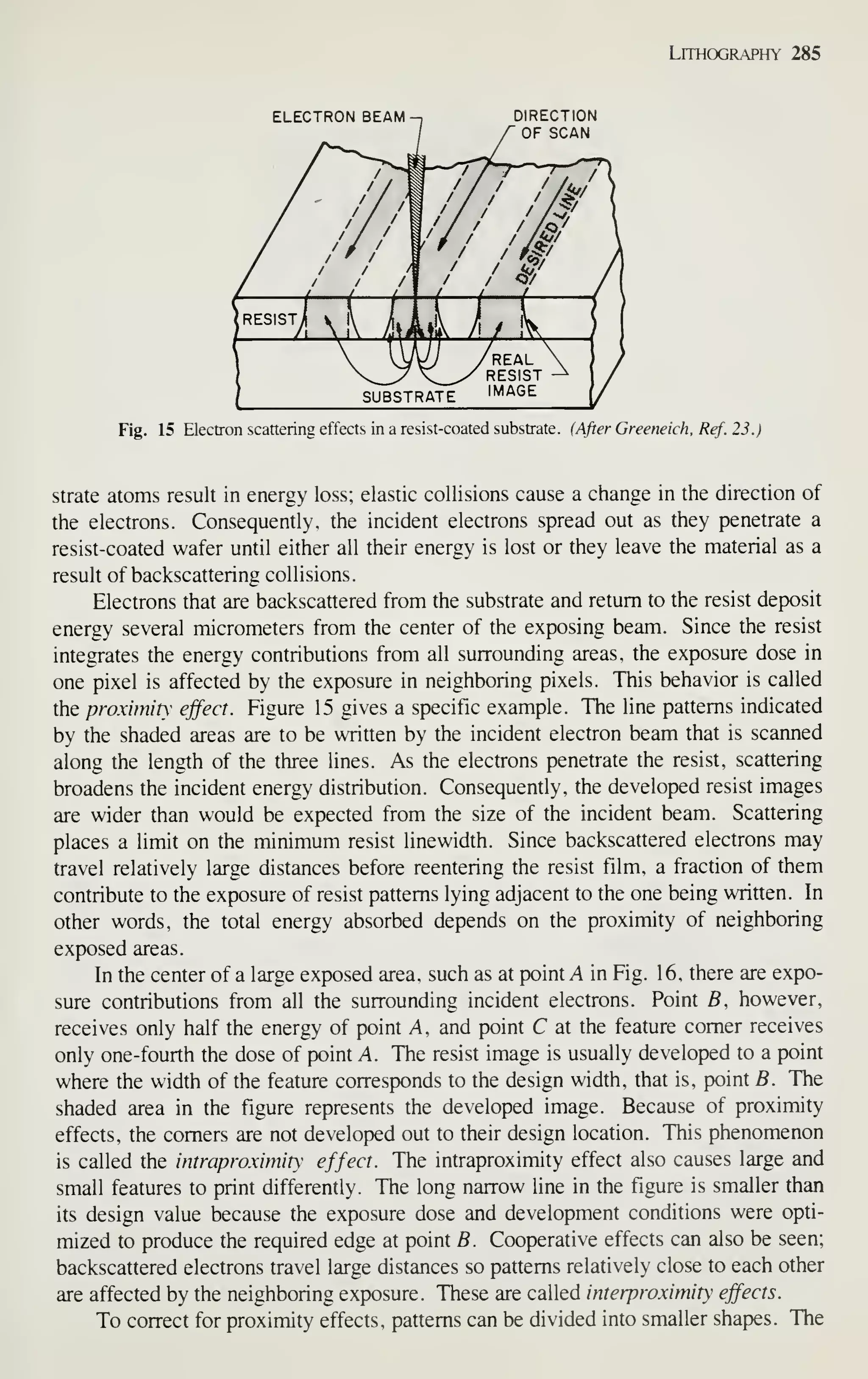

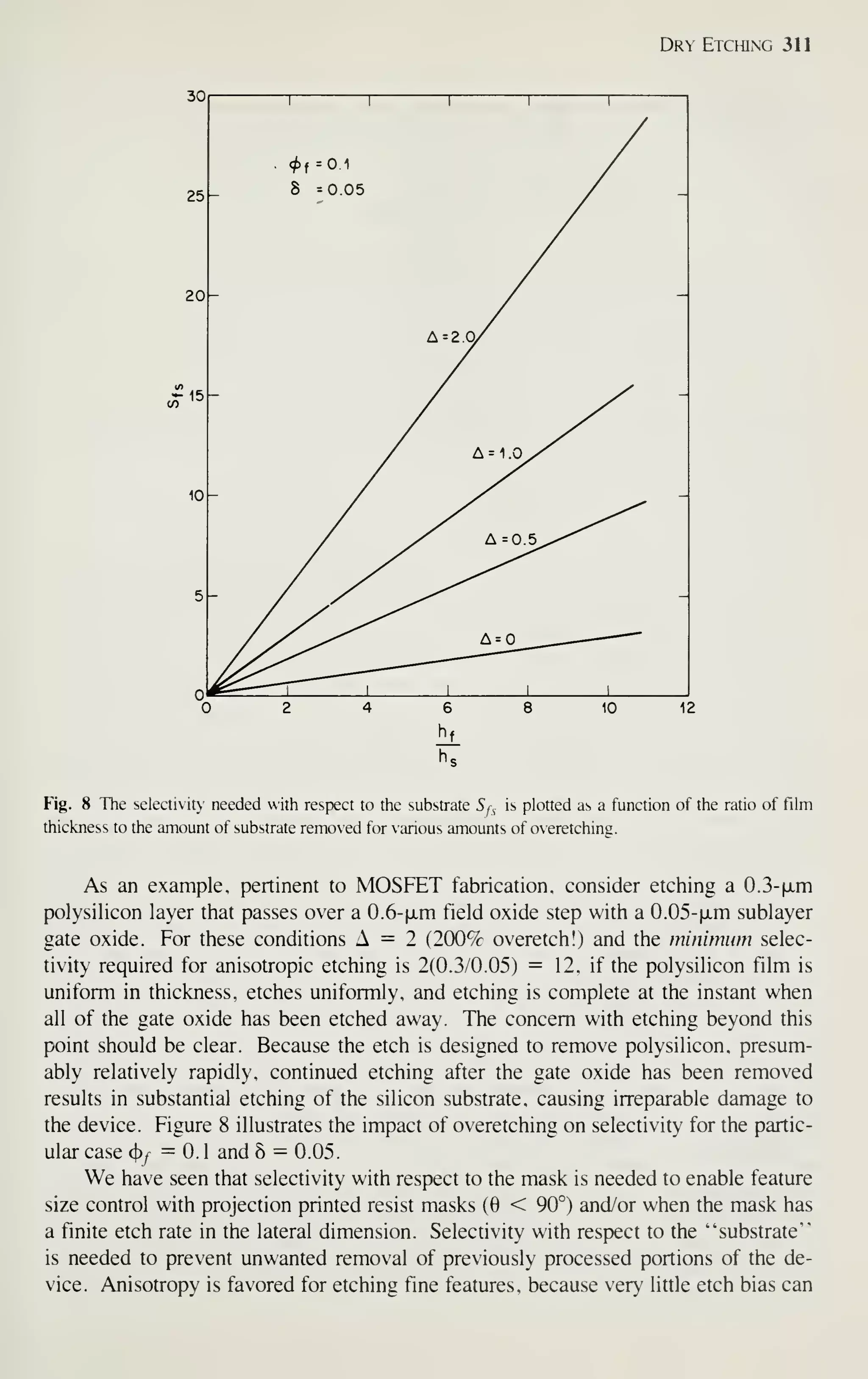

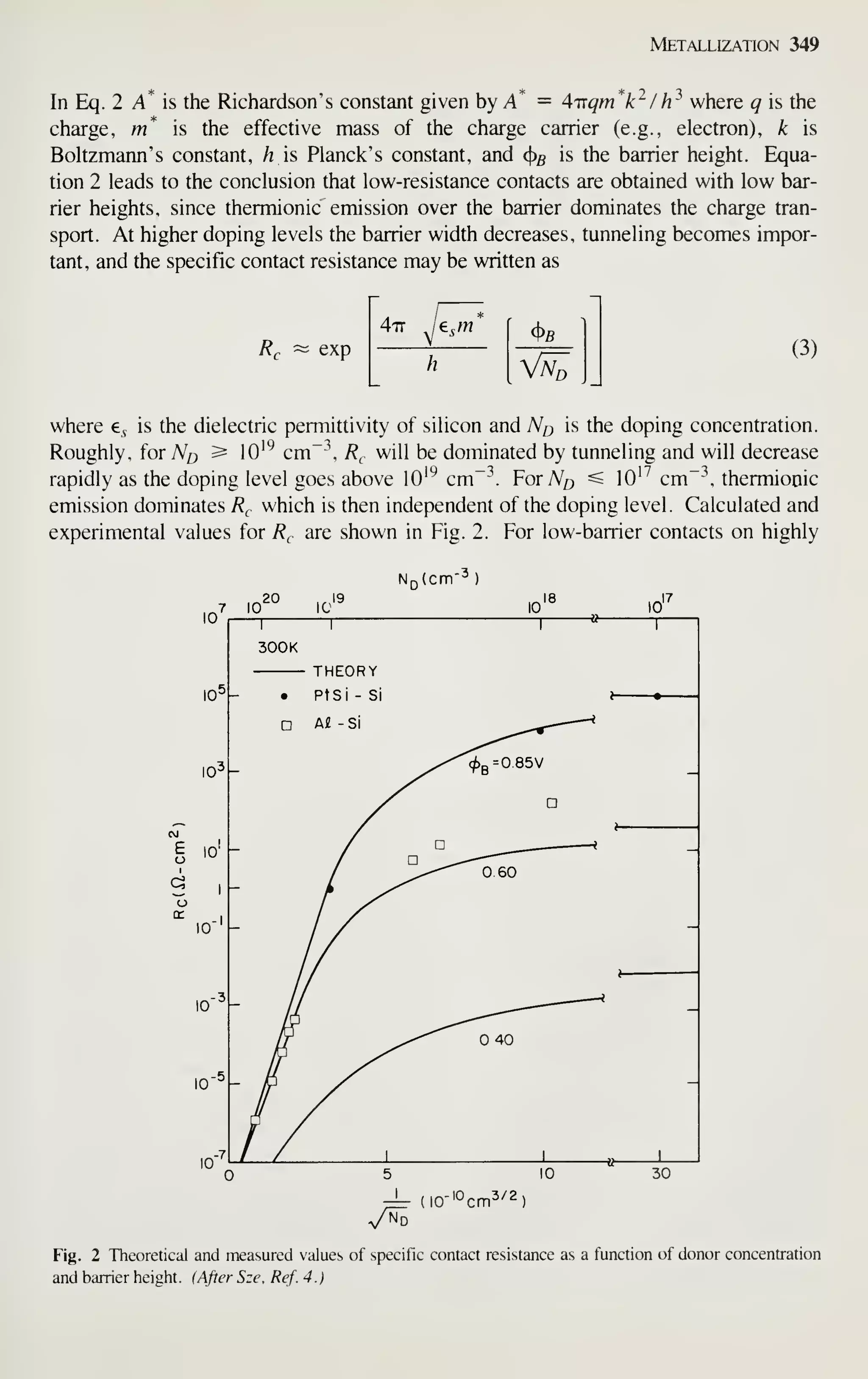

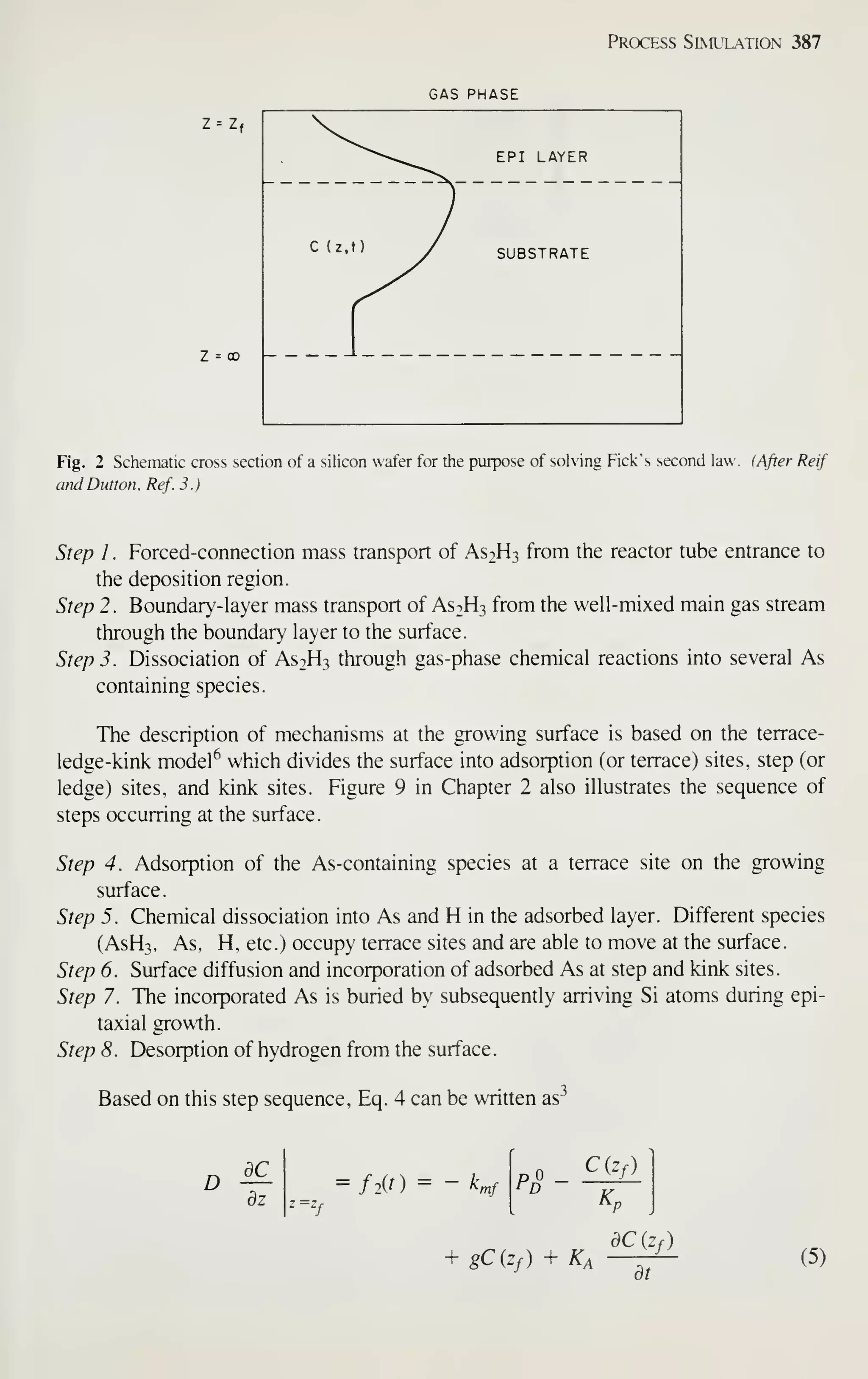

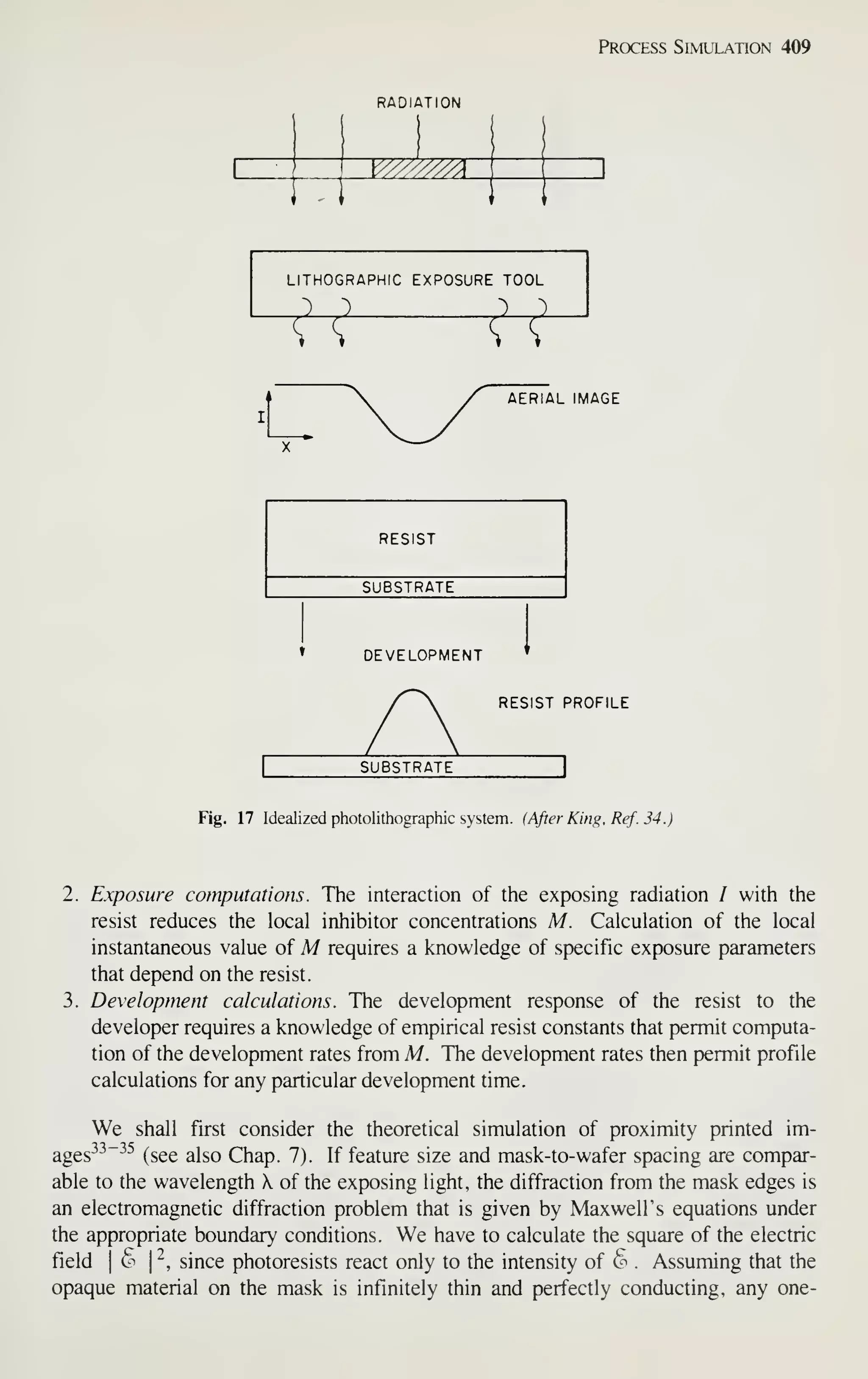

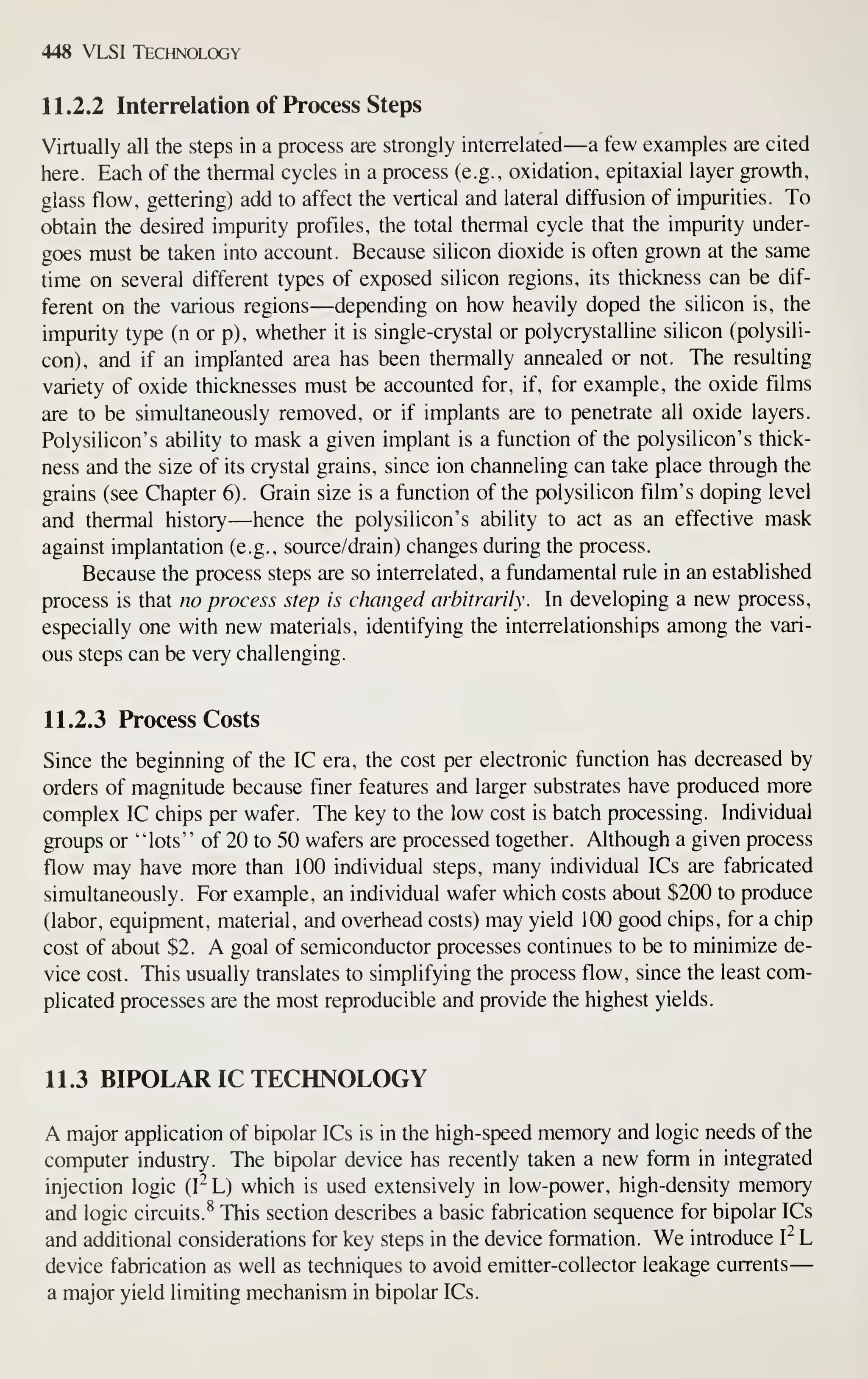

GROWTH OF THE INDUSTRY

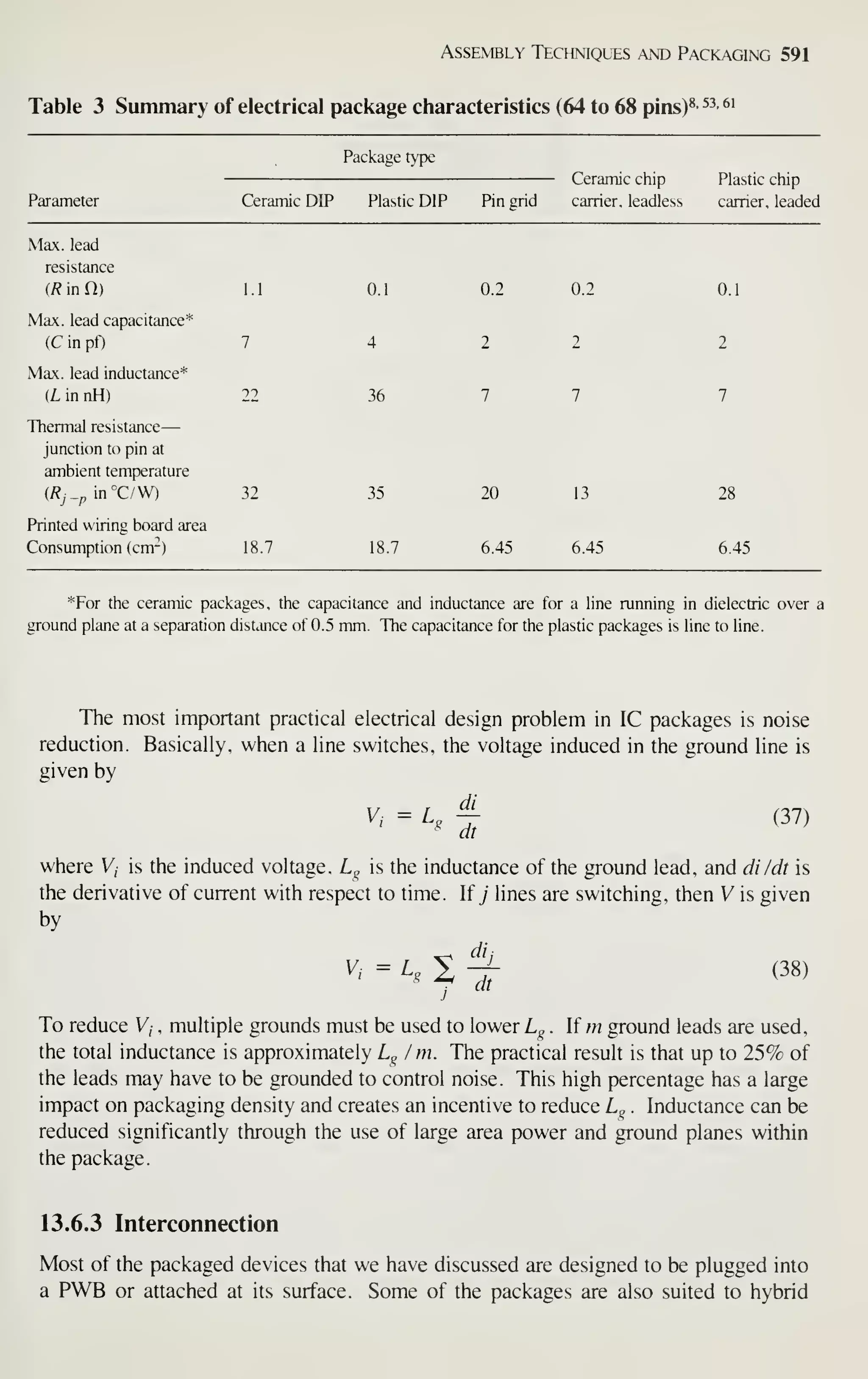

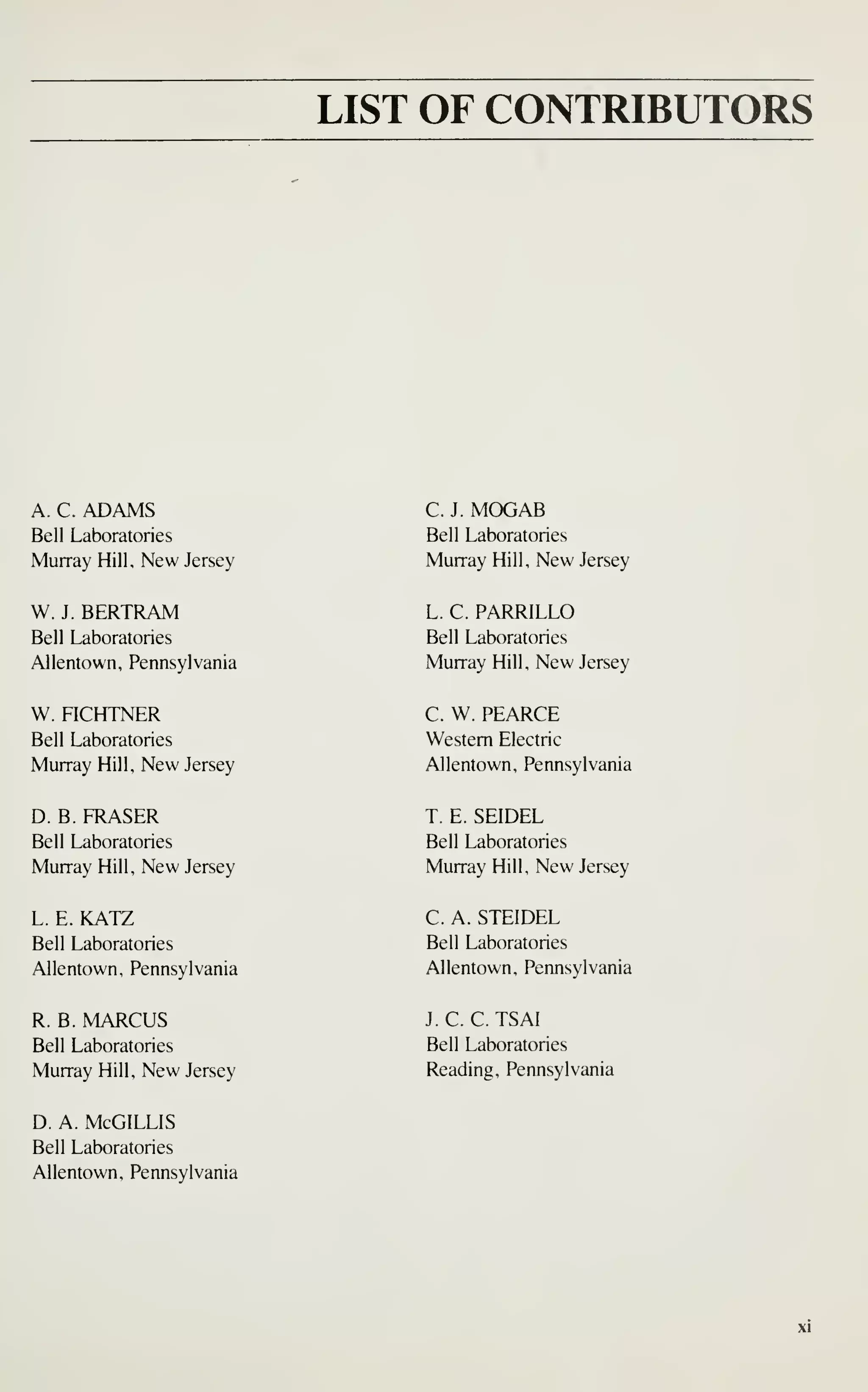

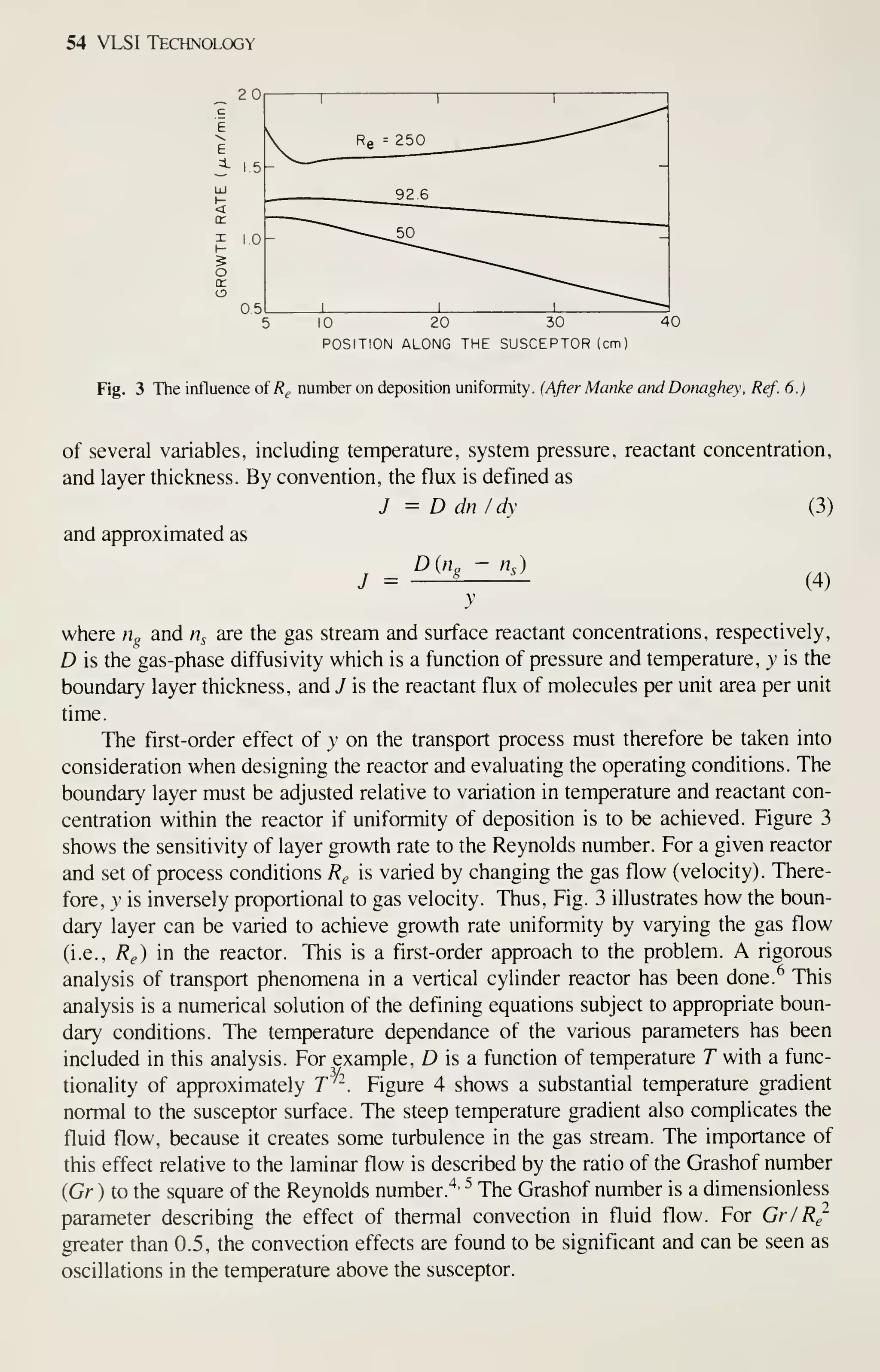

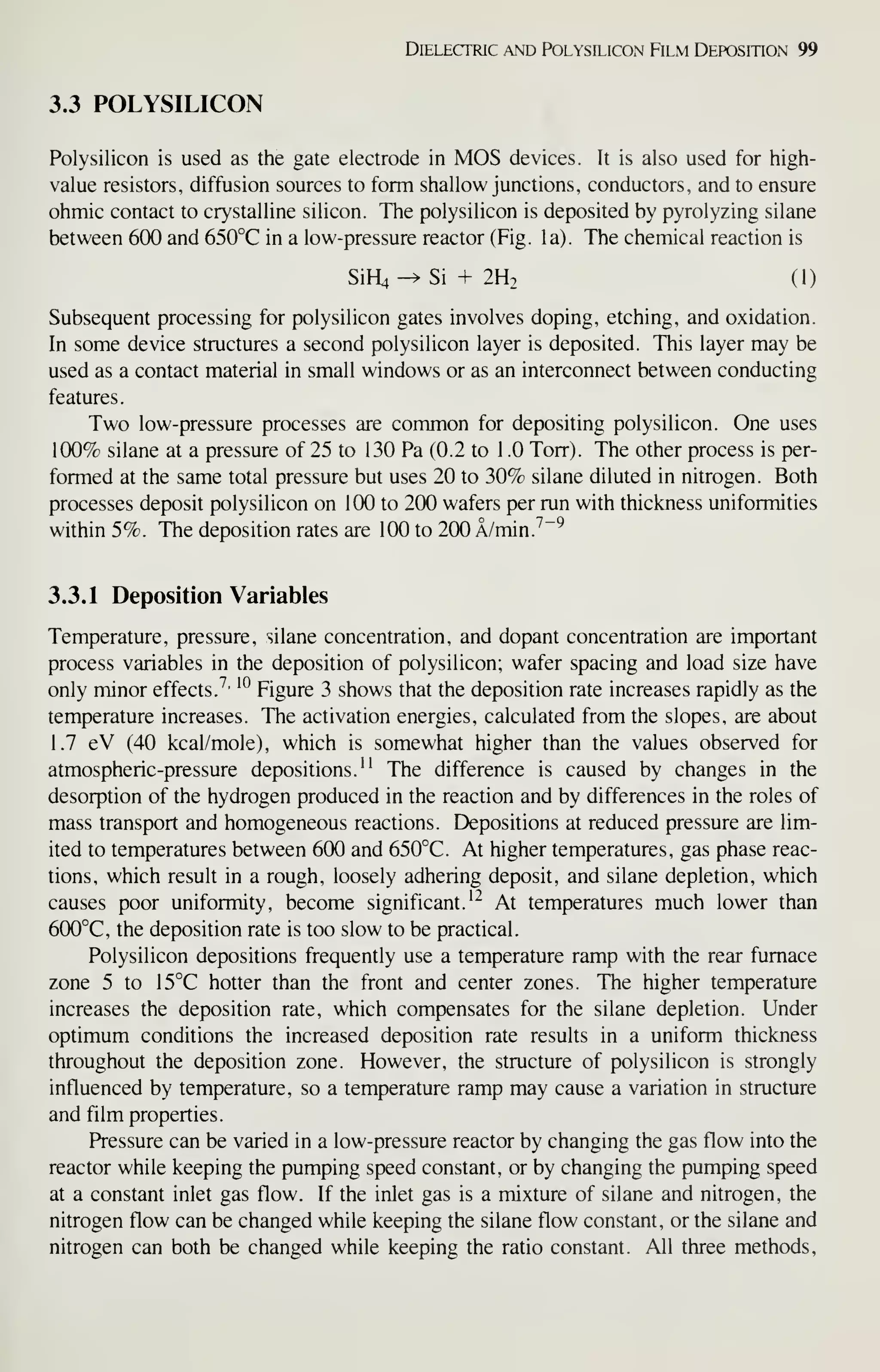

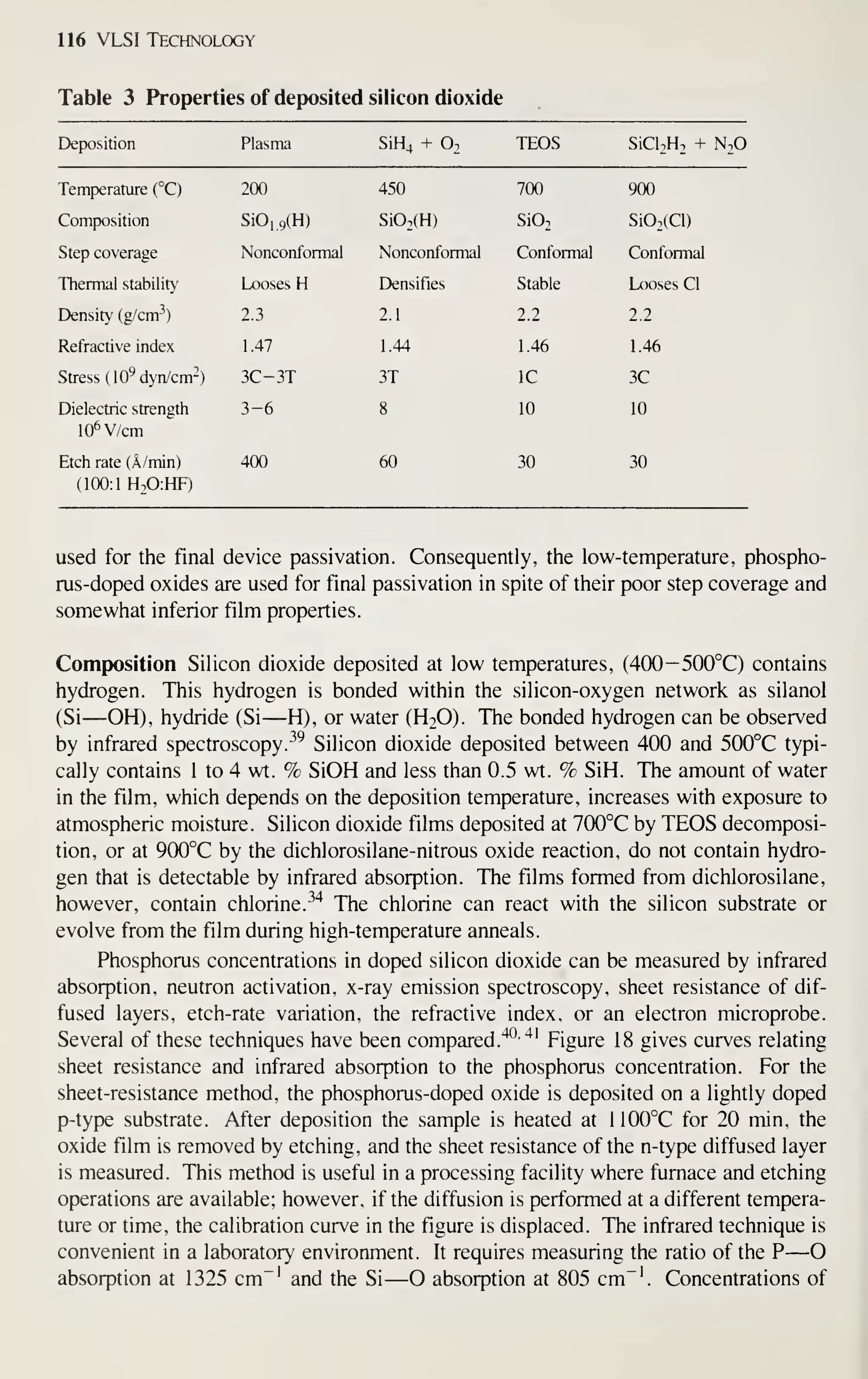

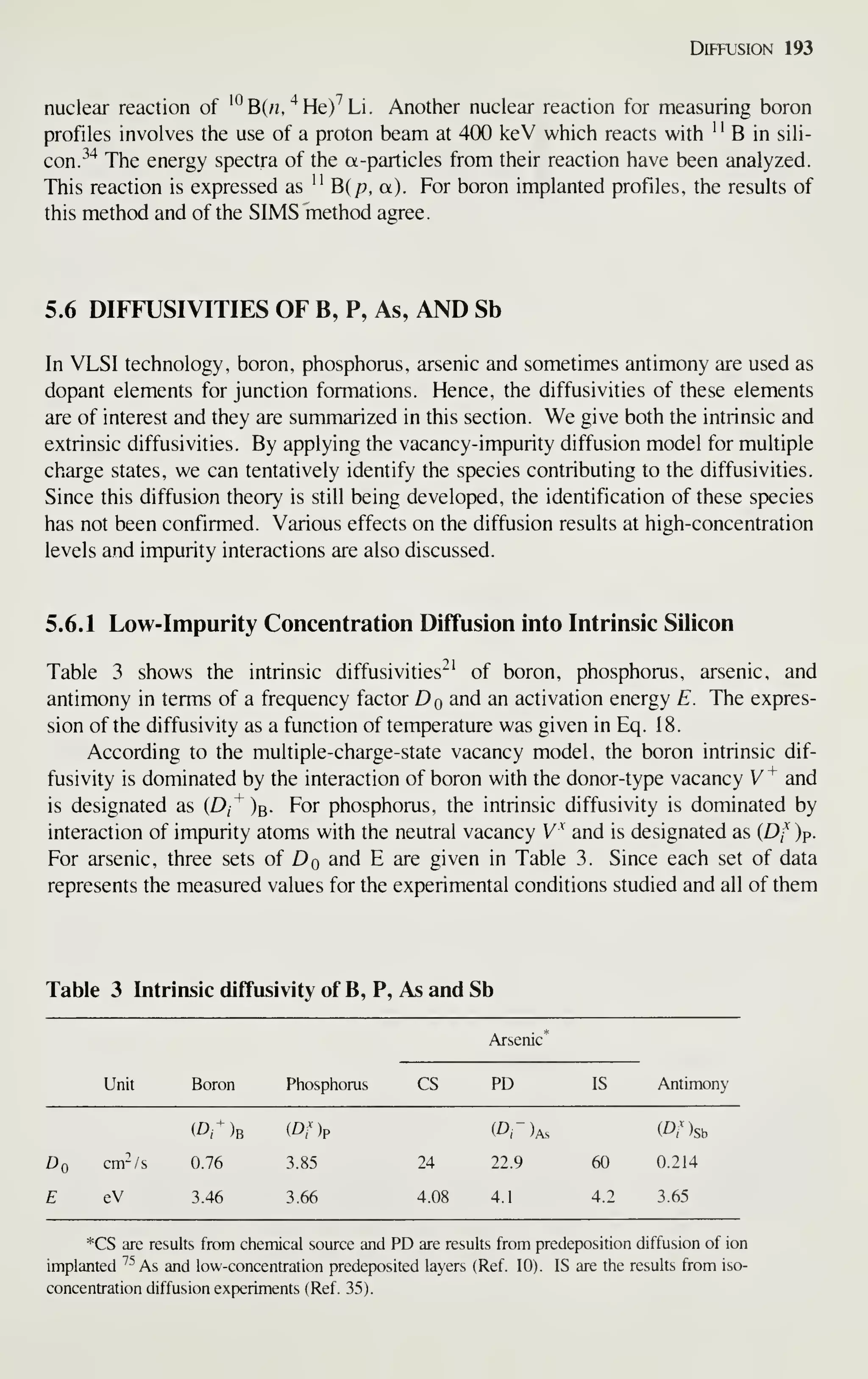

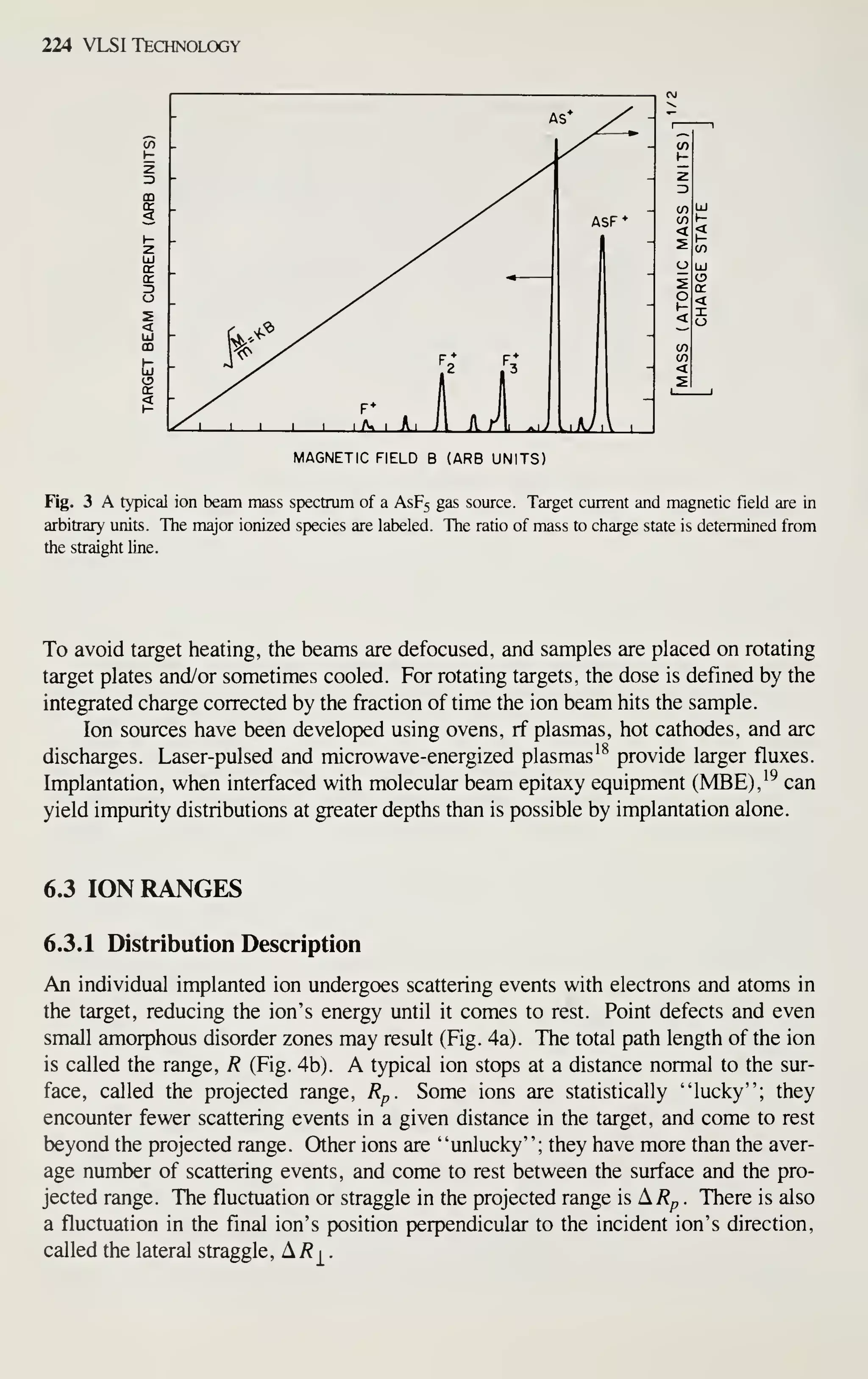

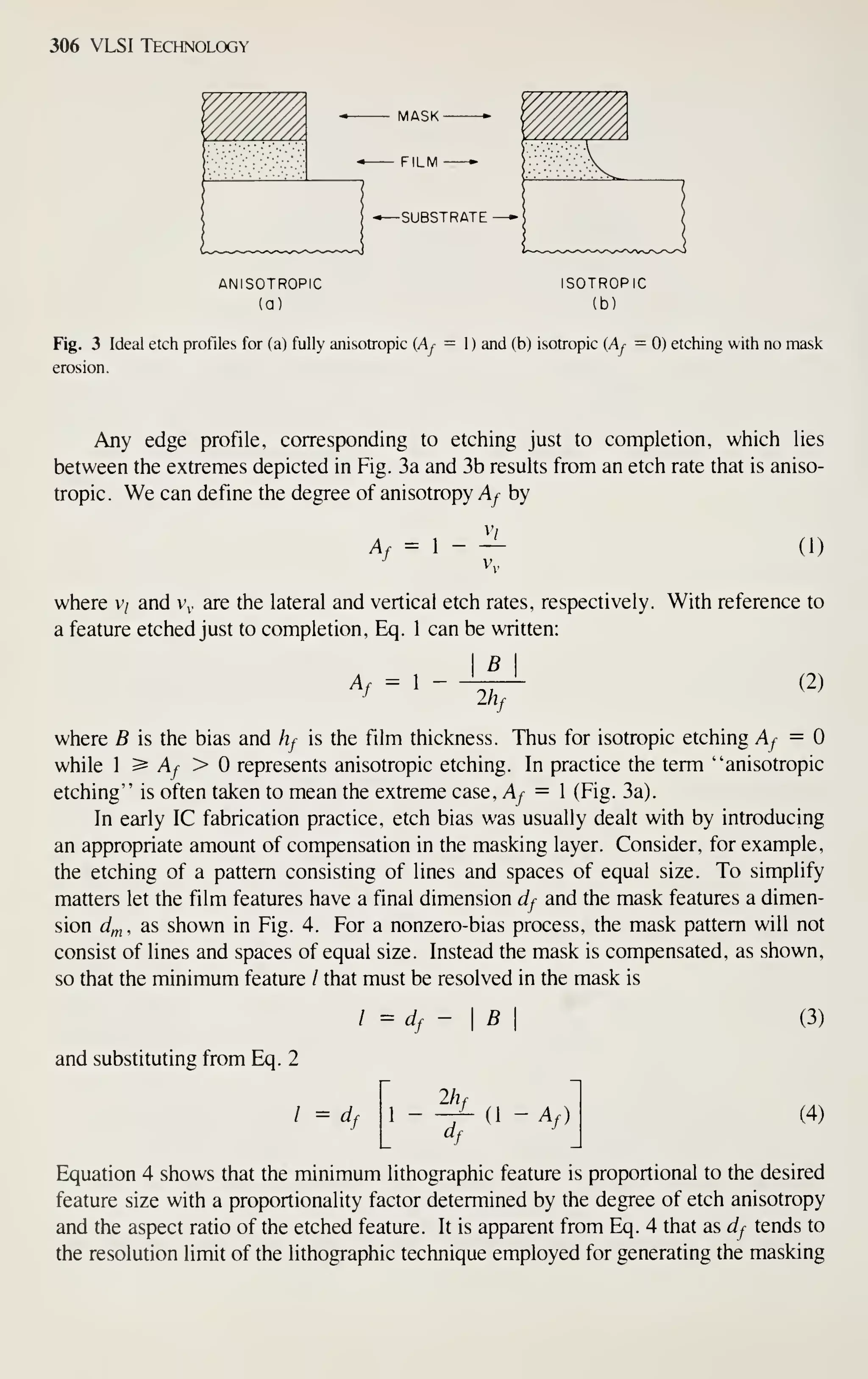

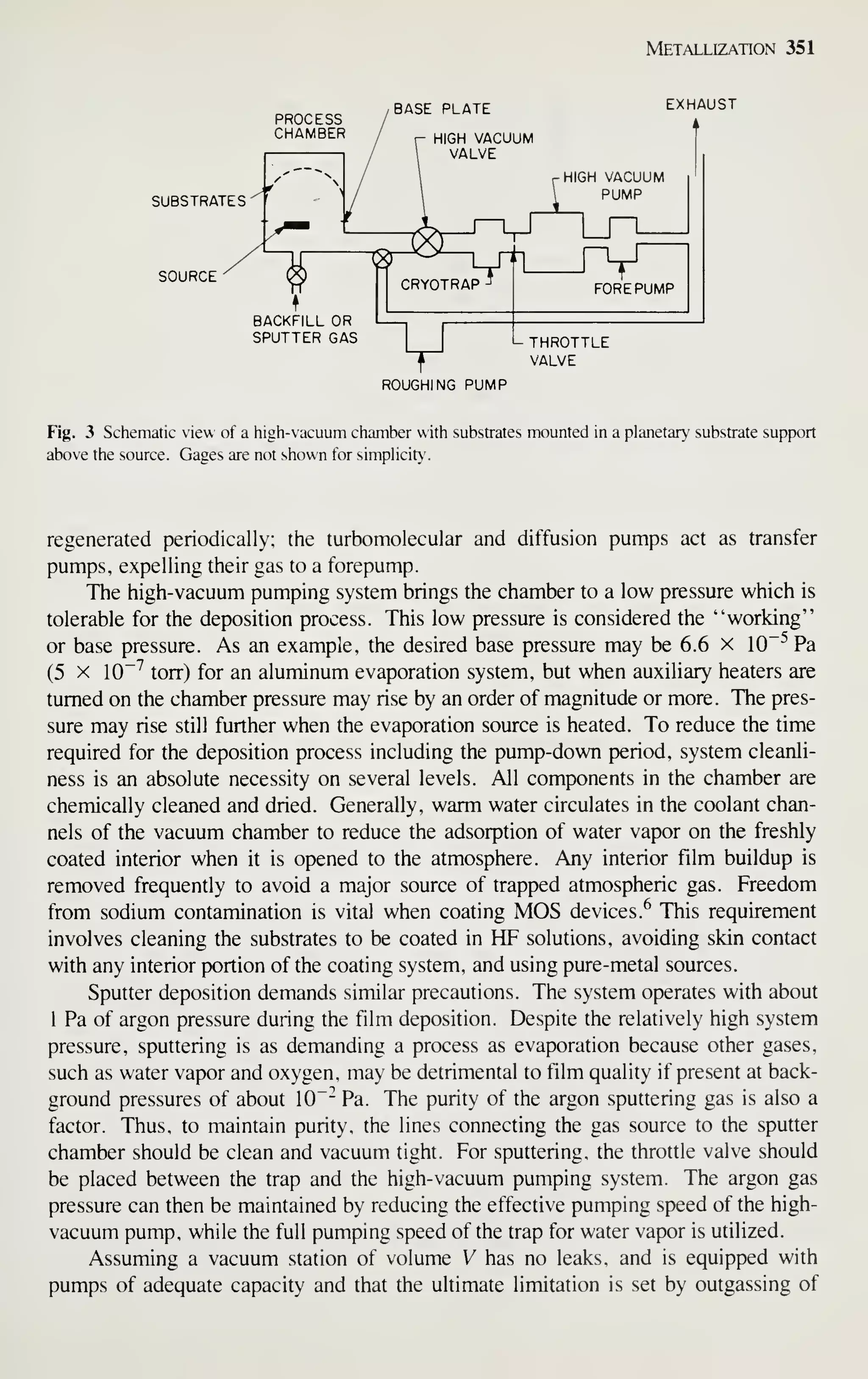

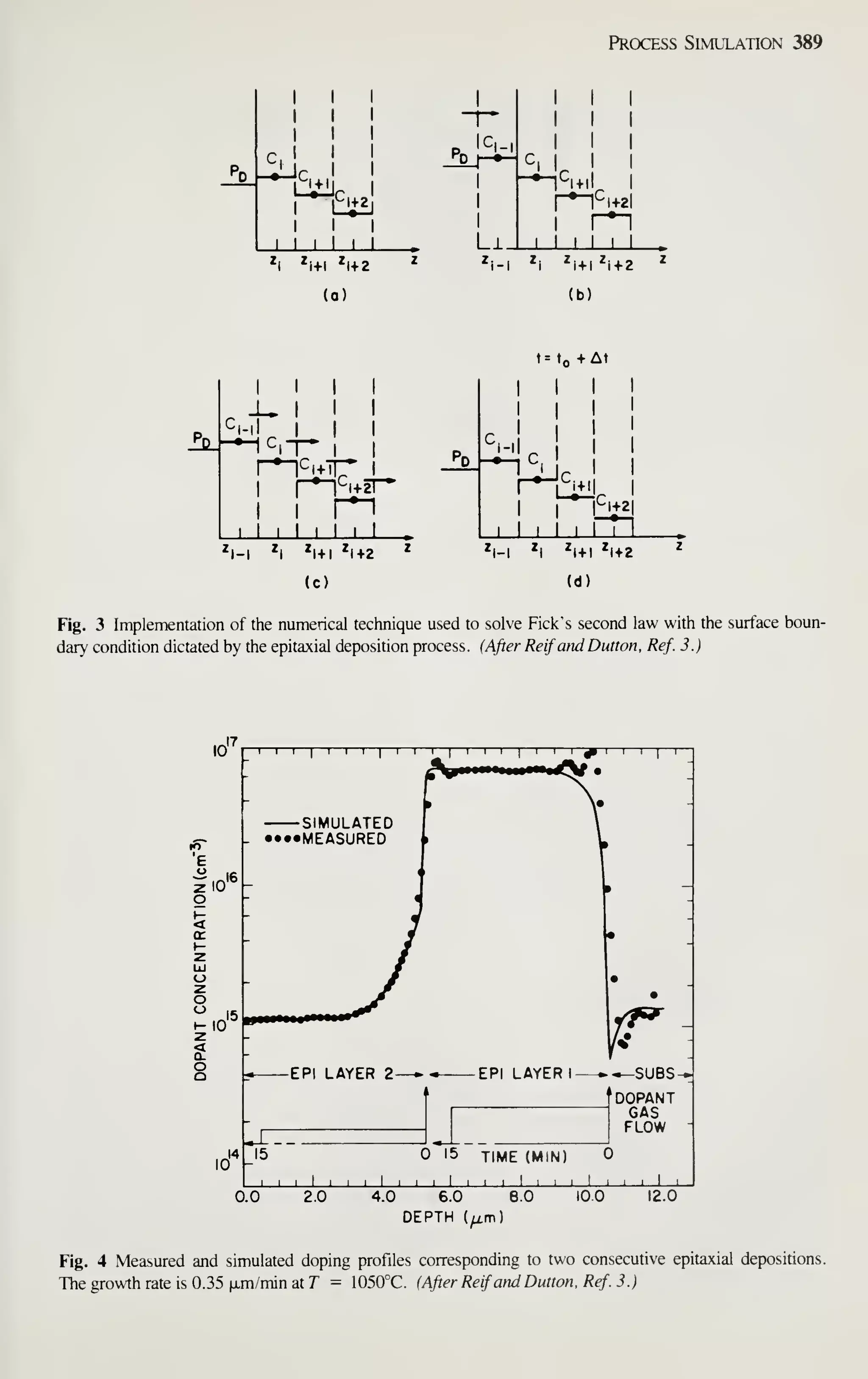

The electronics industry in the United States has grown rapidly in recent years, with

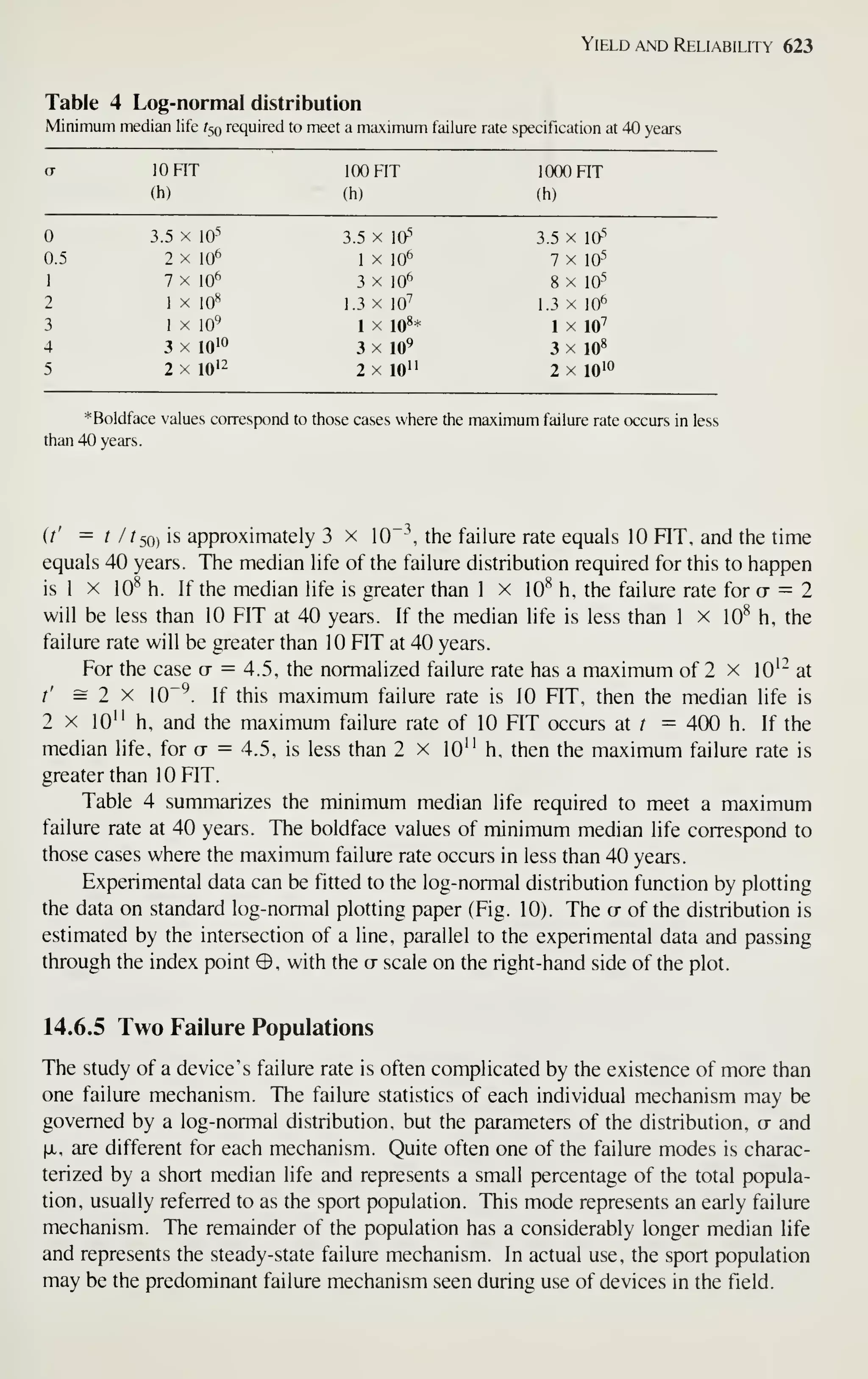

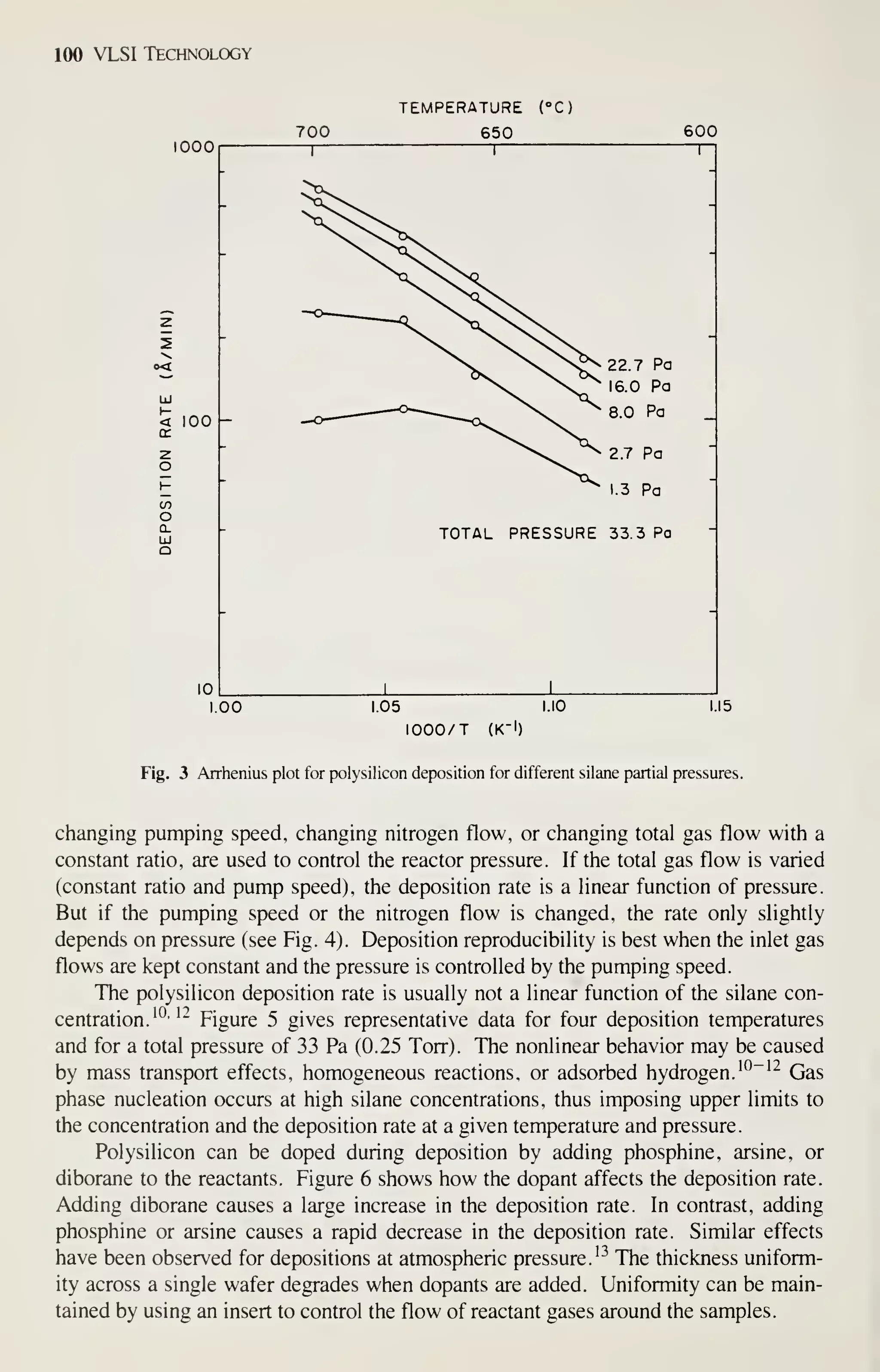

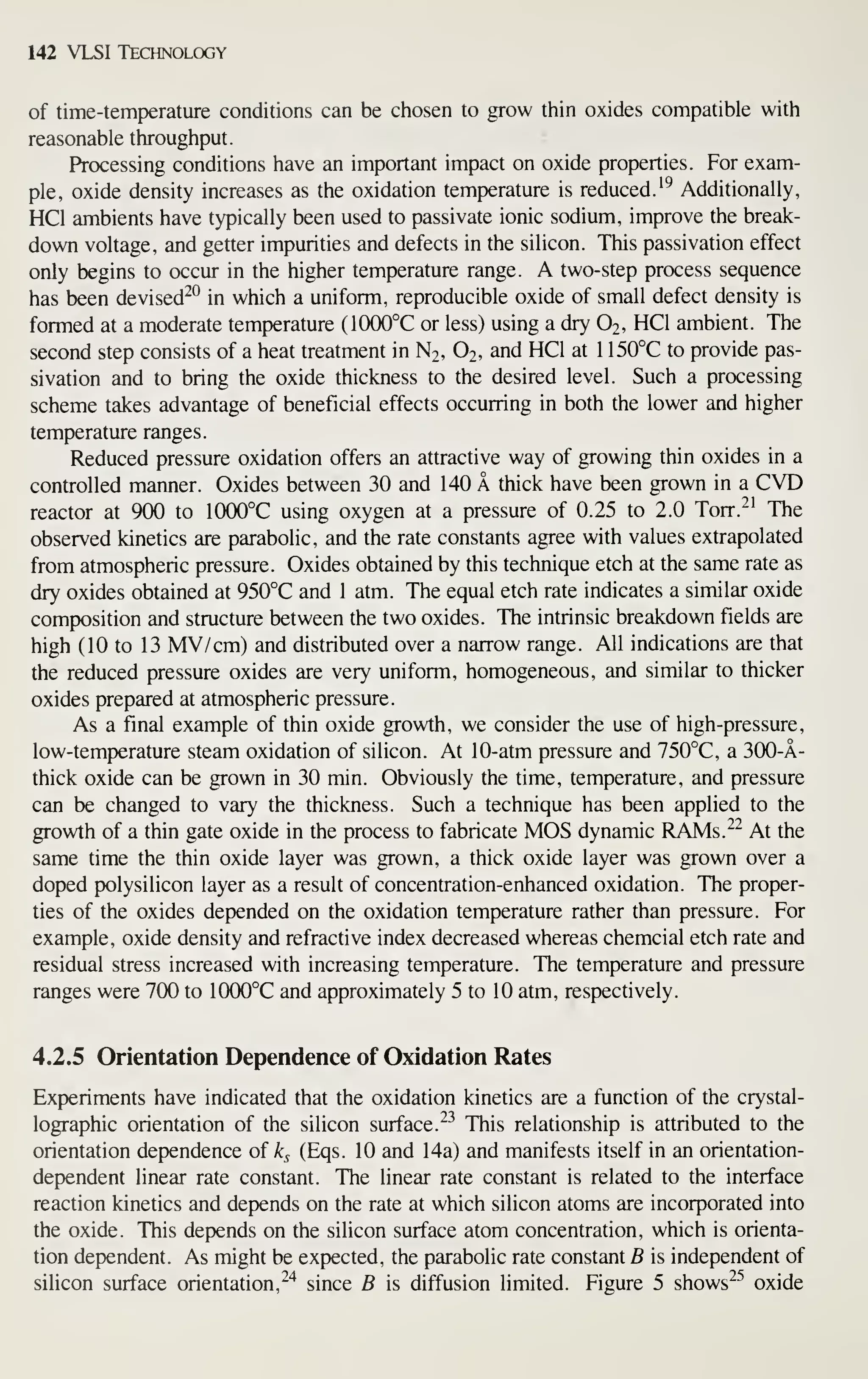

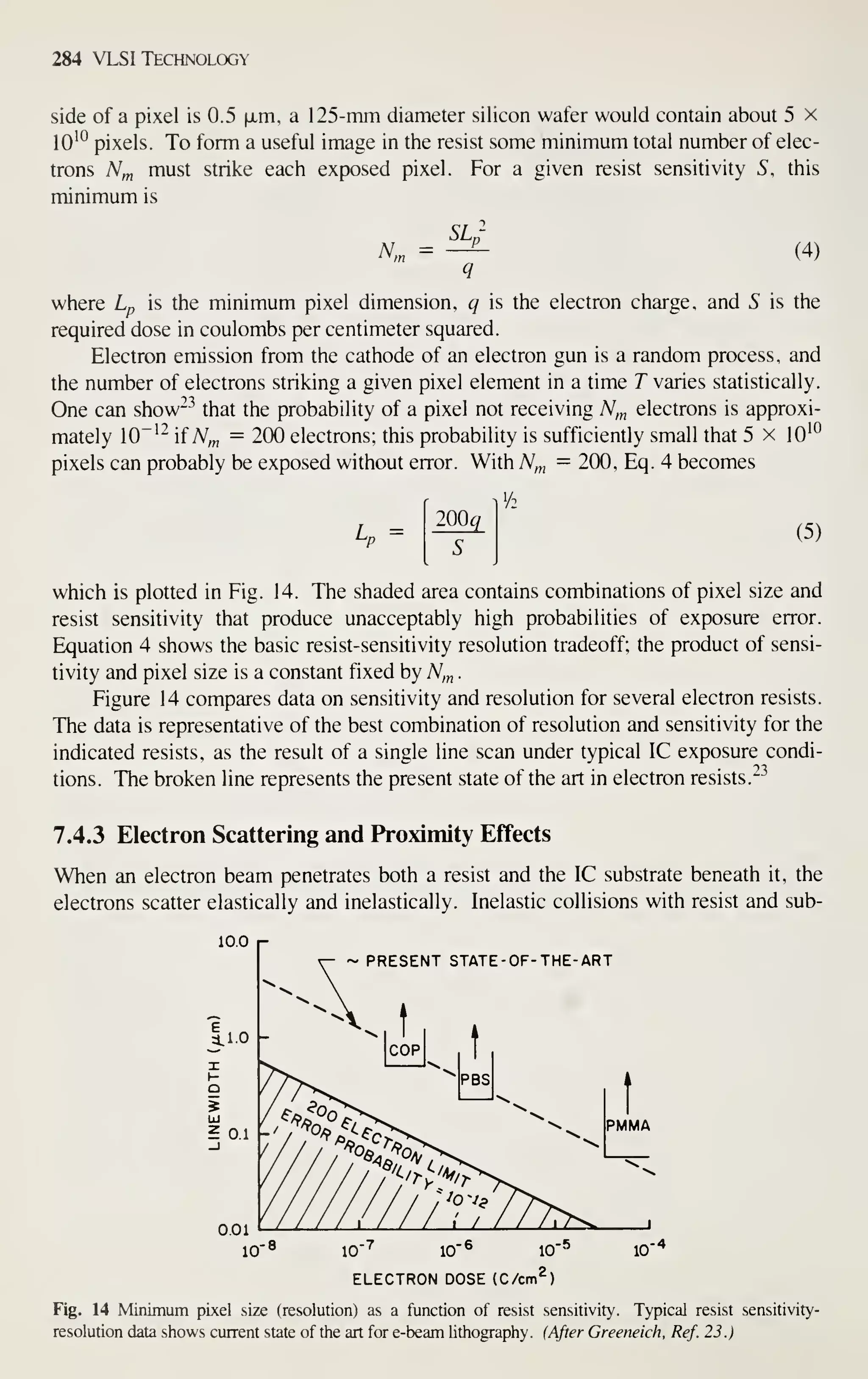

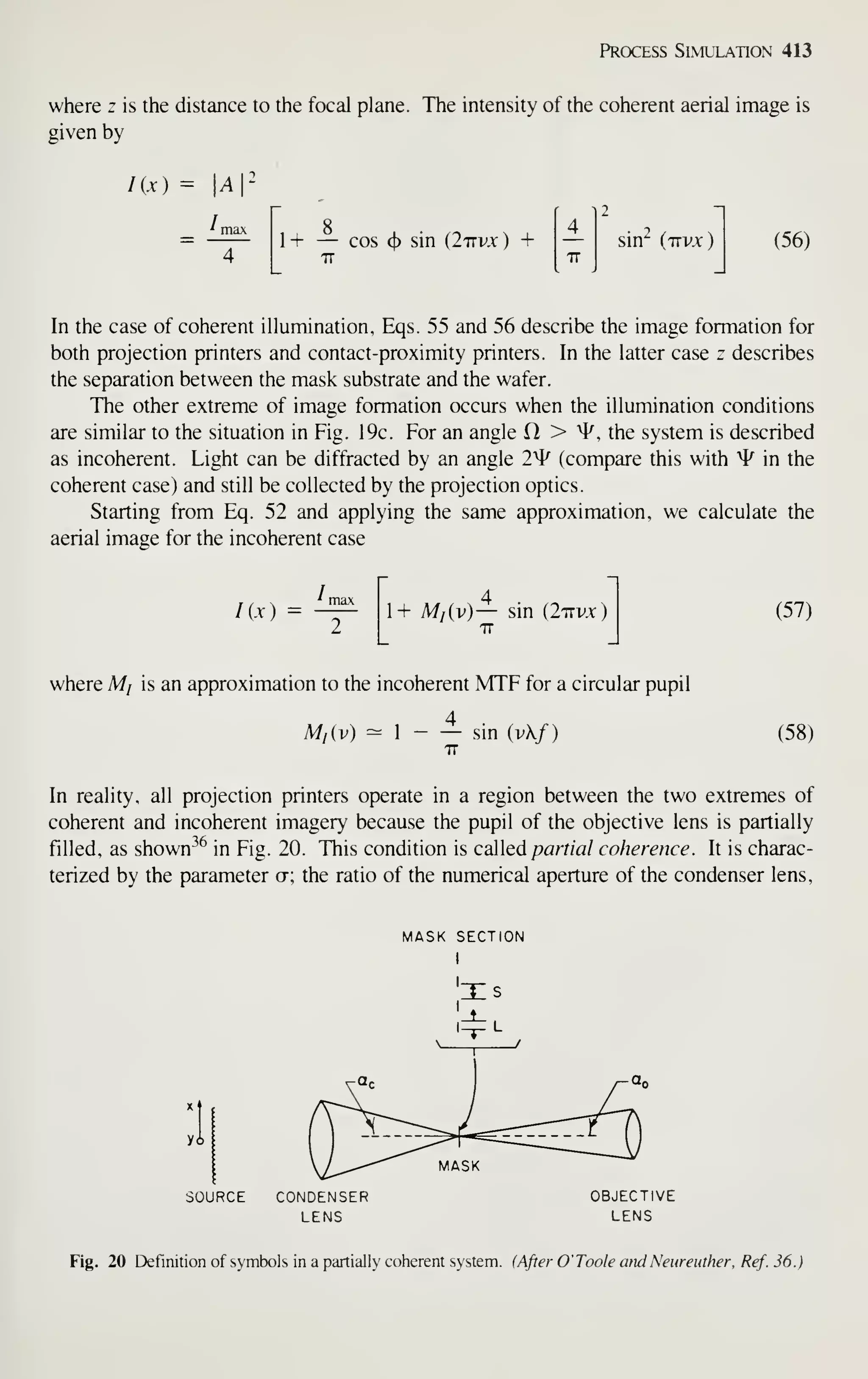

factory sales increasing by a factor of 10 since the early 1960s. [See Fig. 1, curve

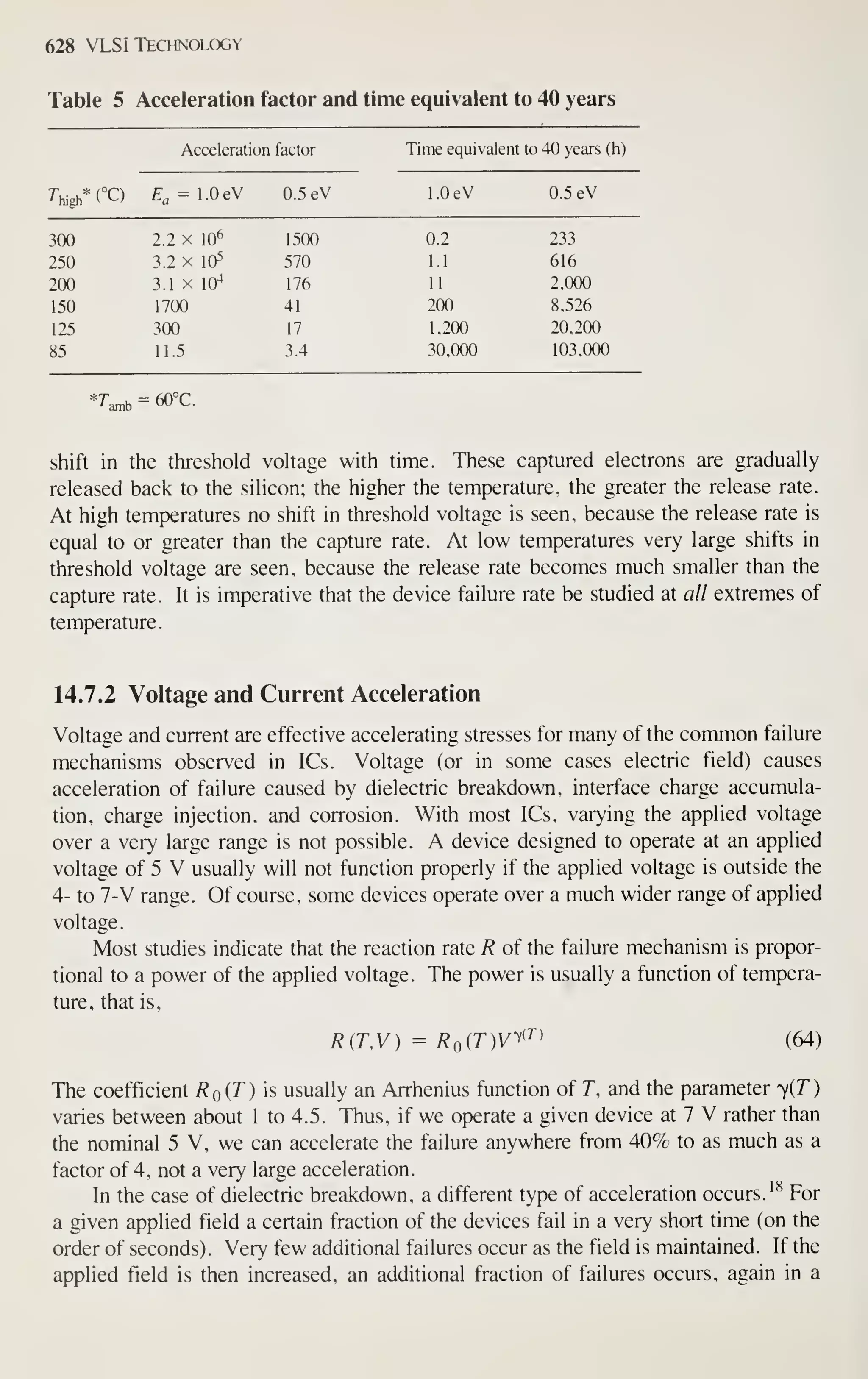

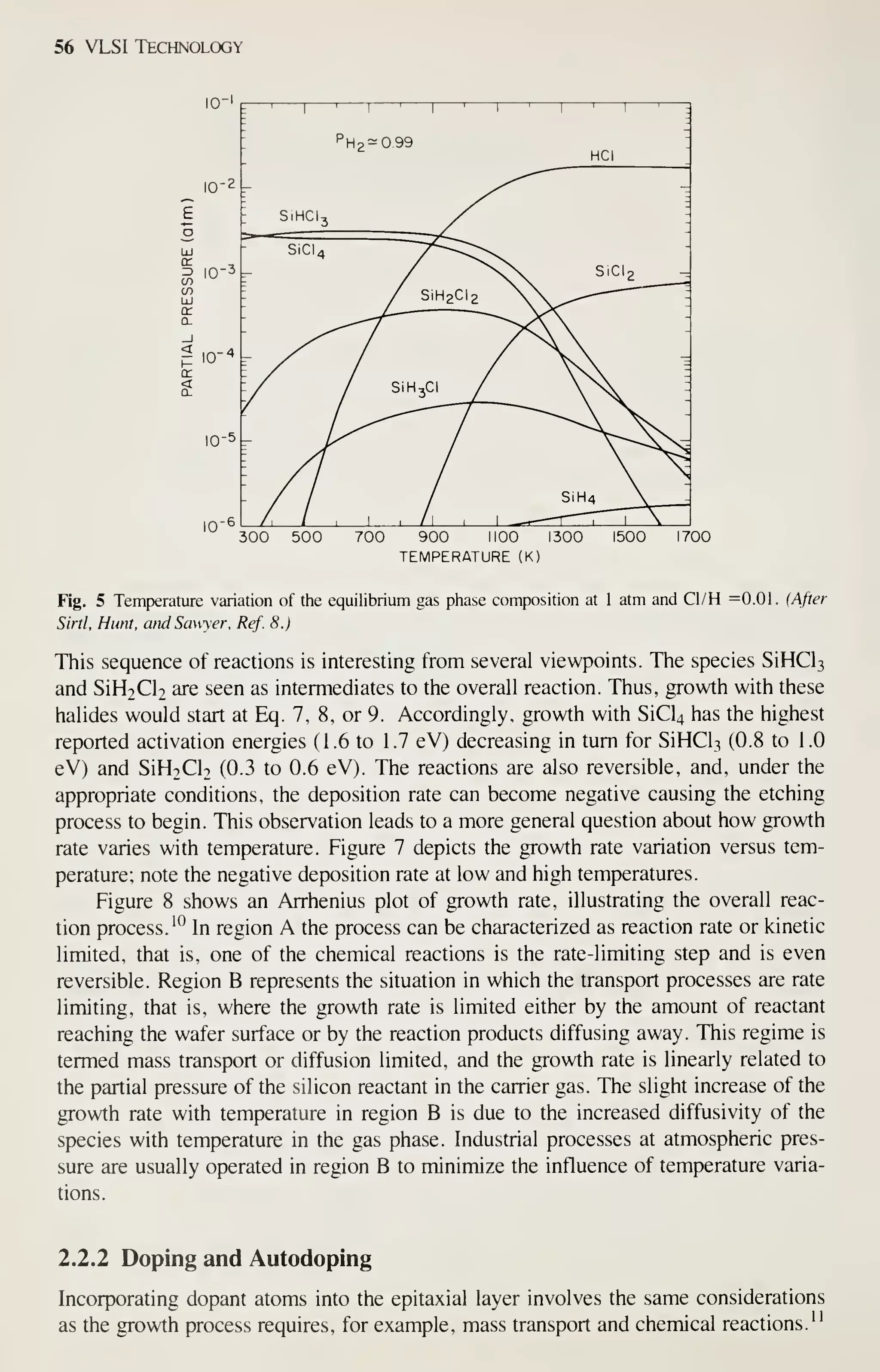

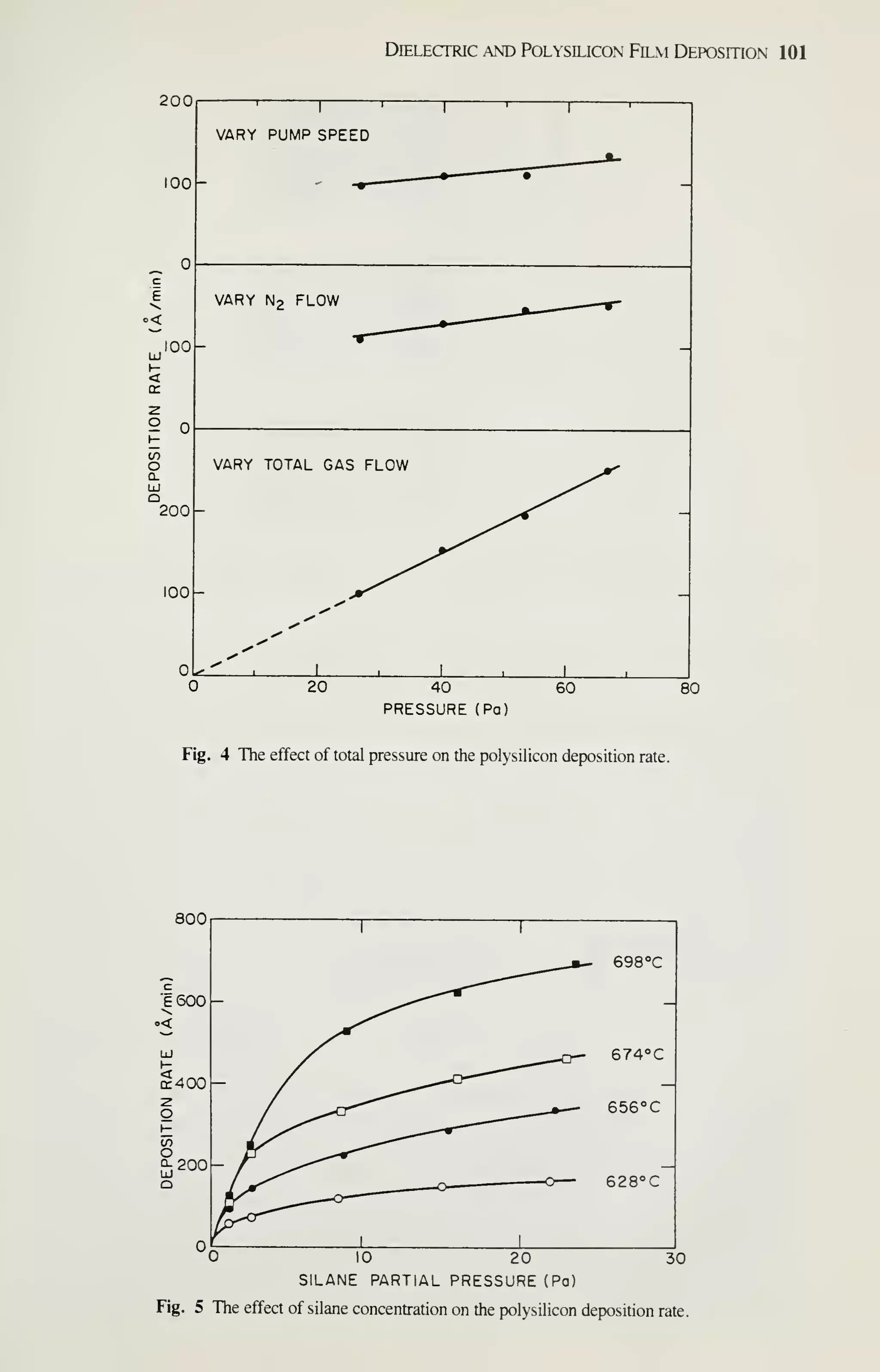

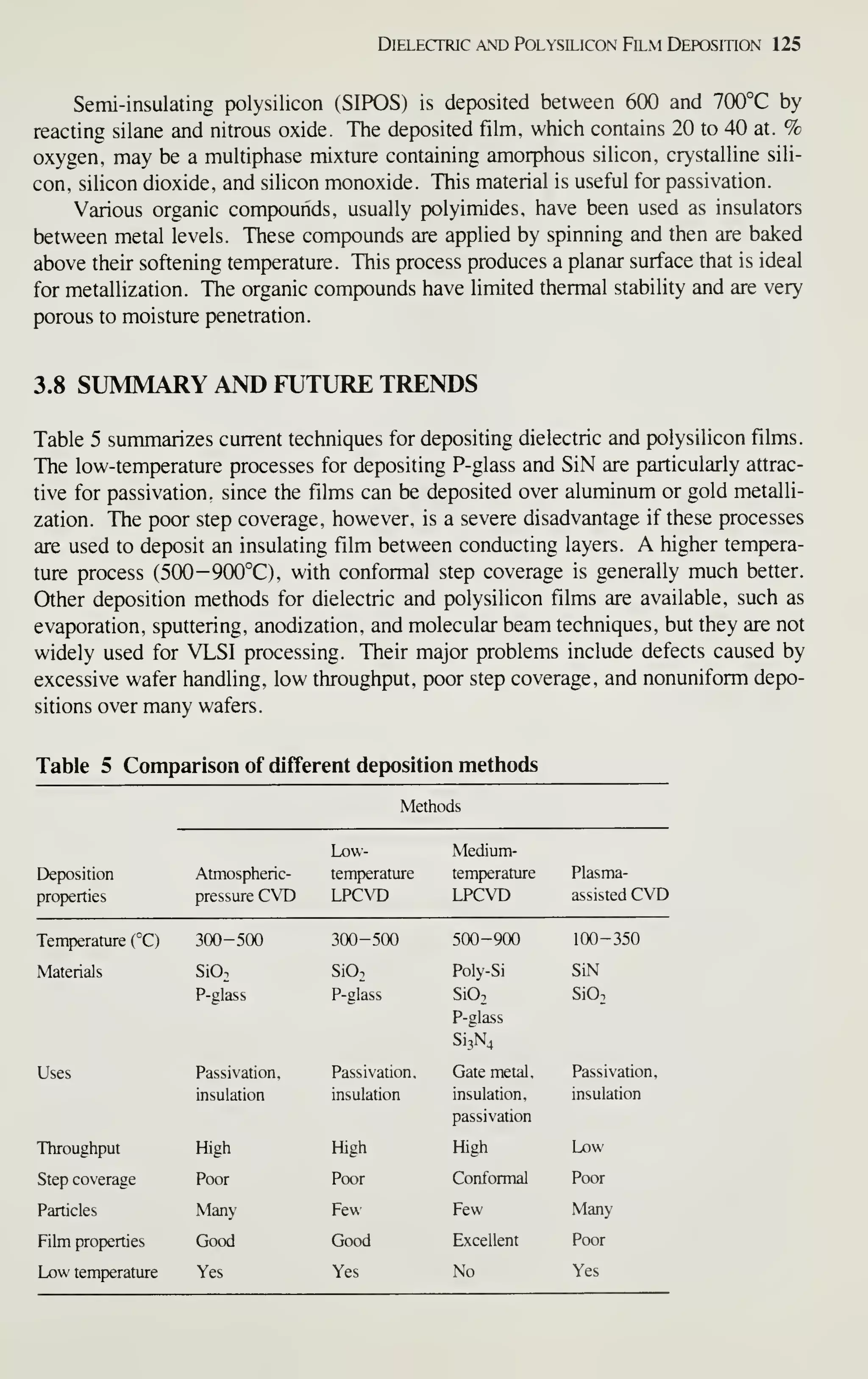

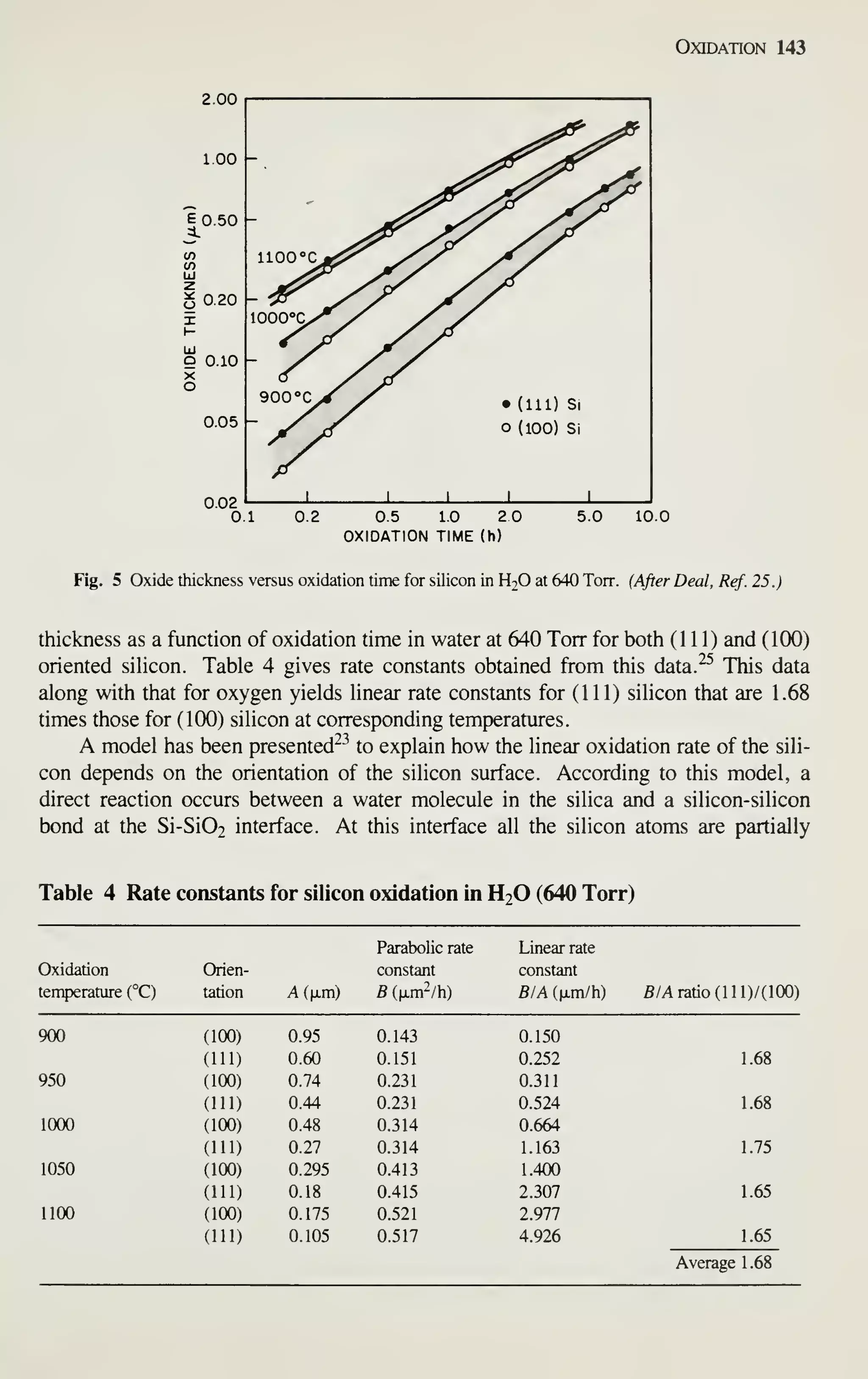

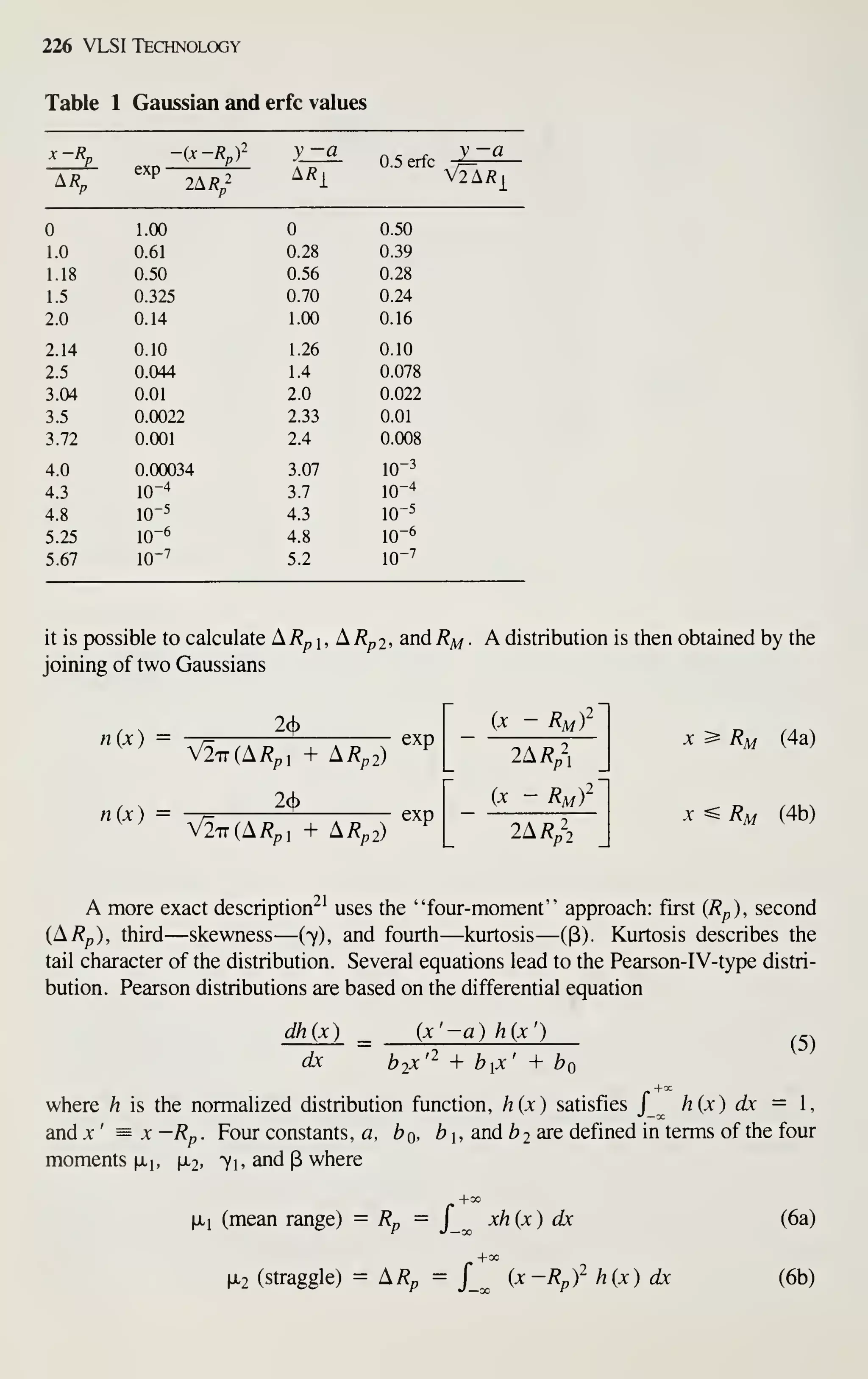

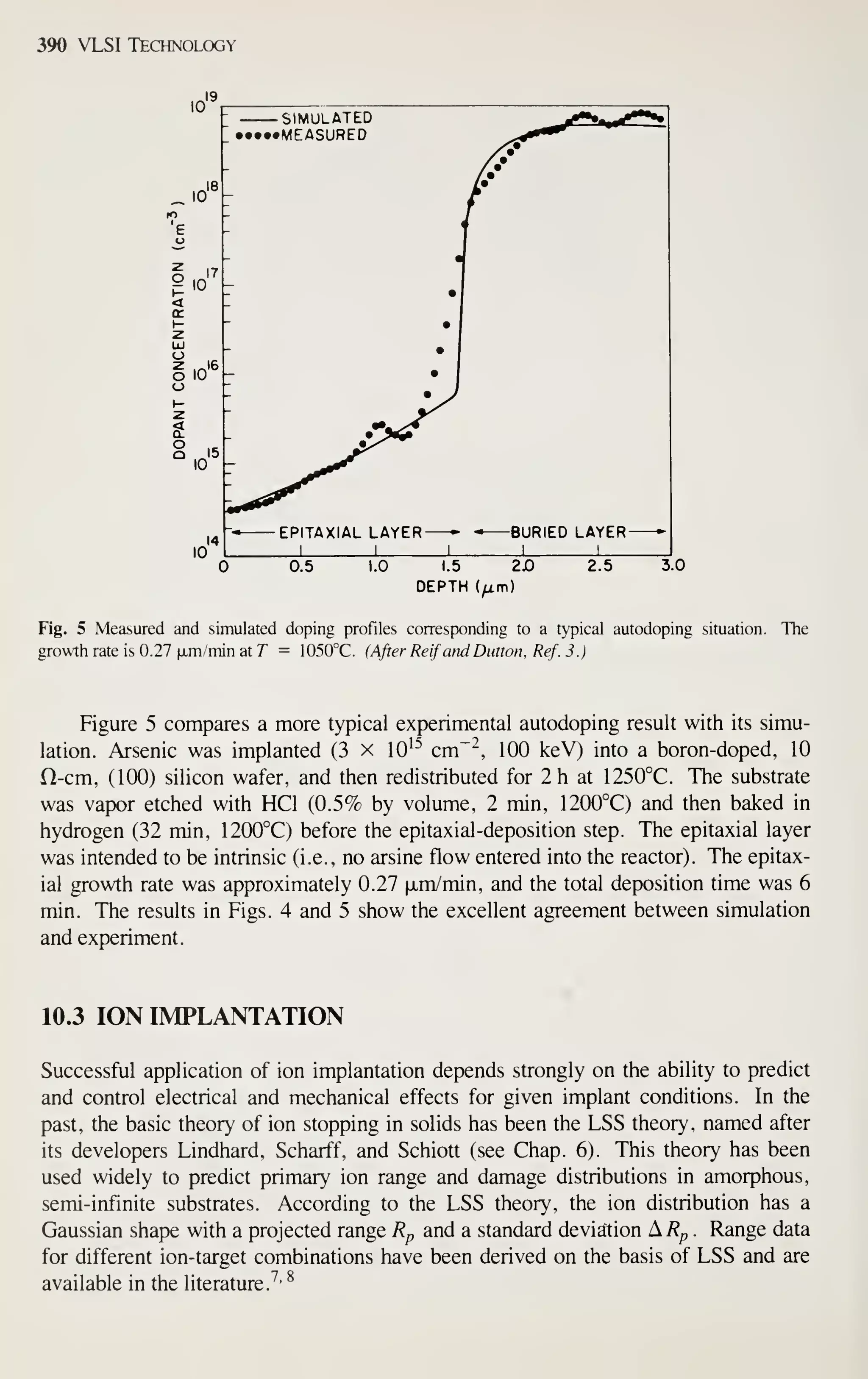

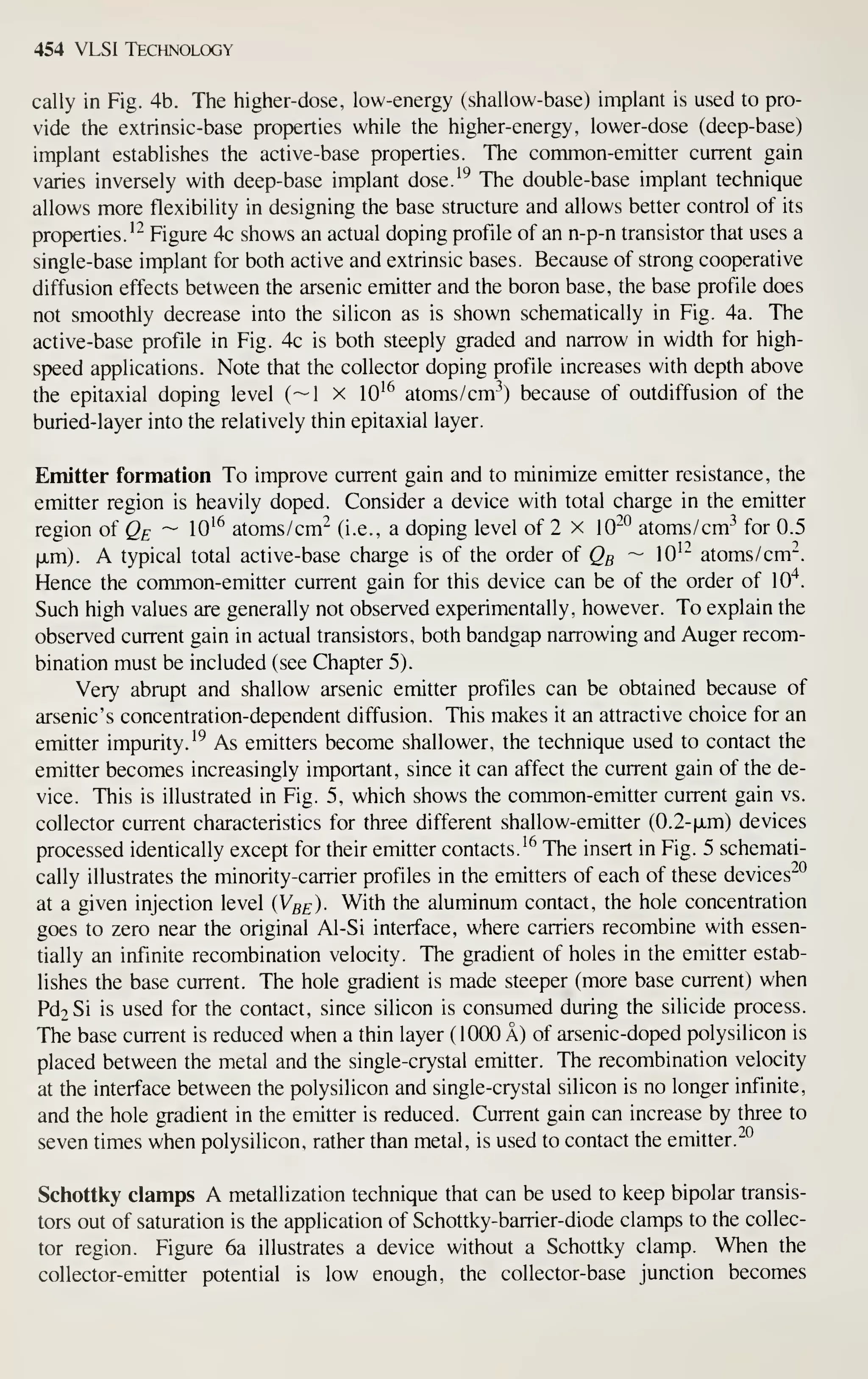

(a).''^] Electronics sales, which were $114 billion in 1981, are projected to increase

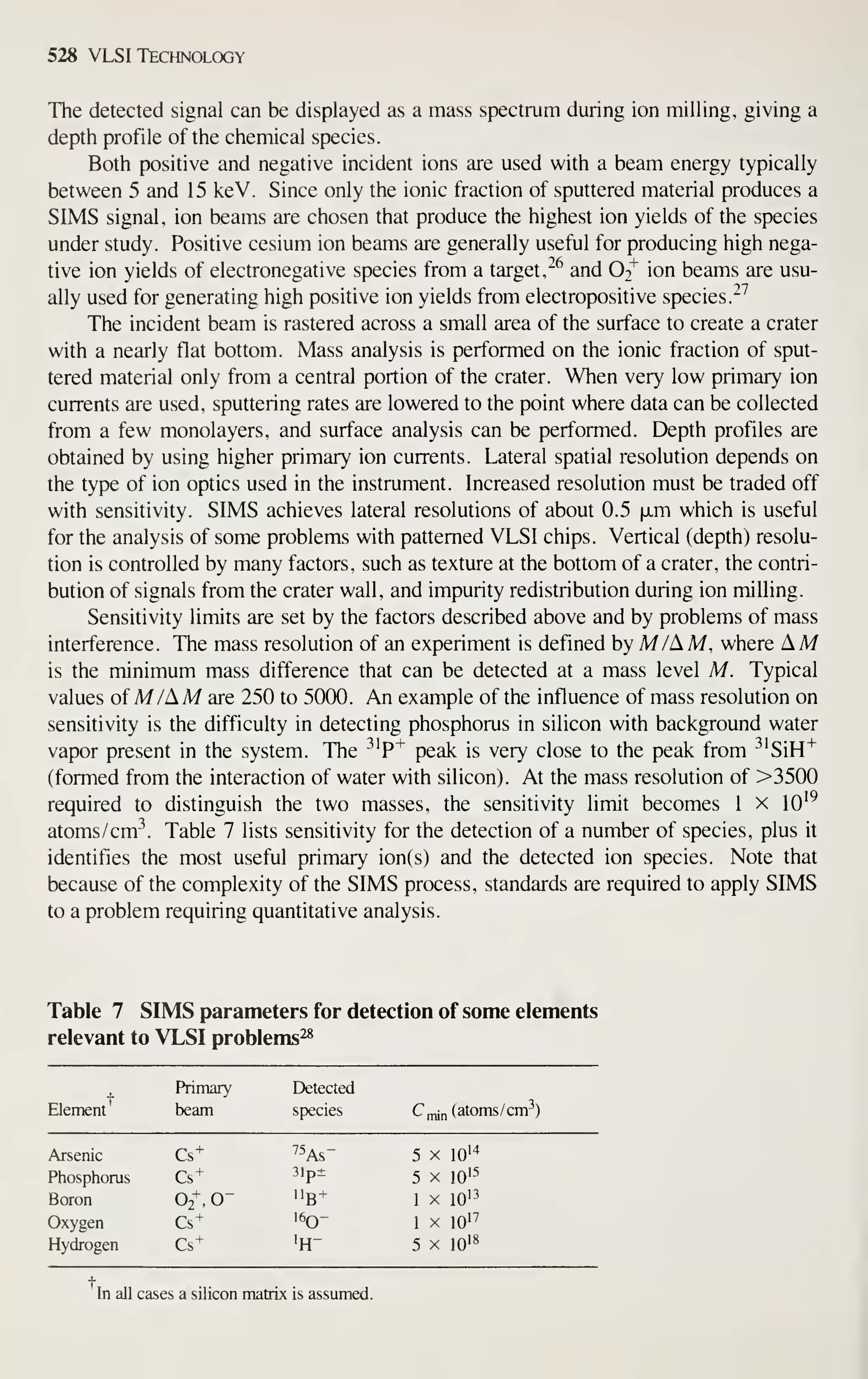

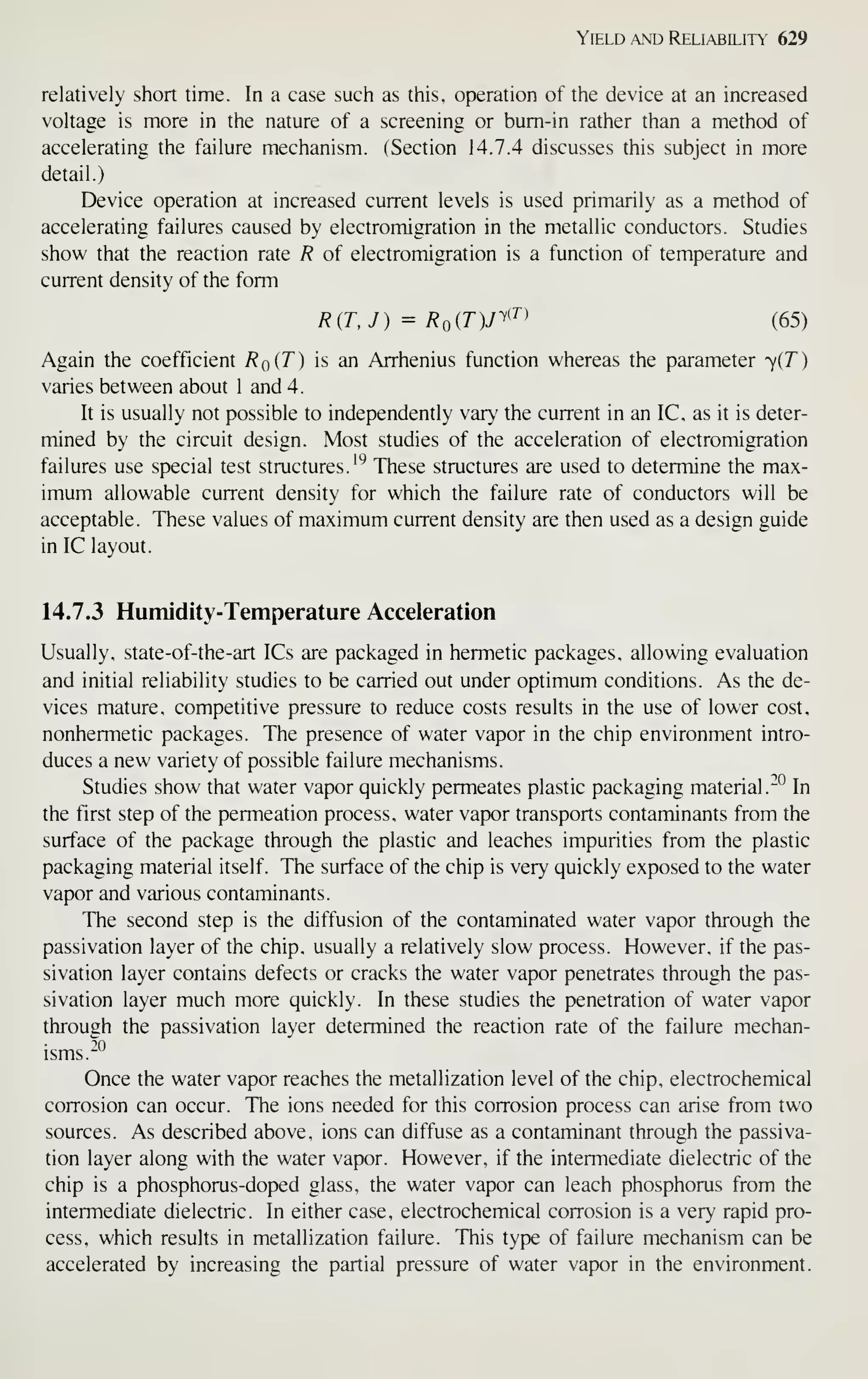

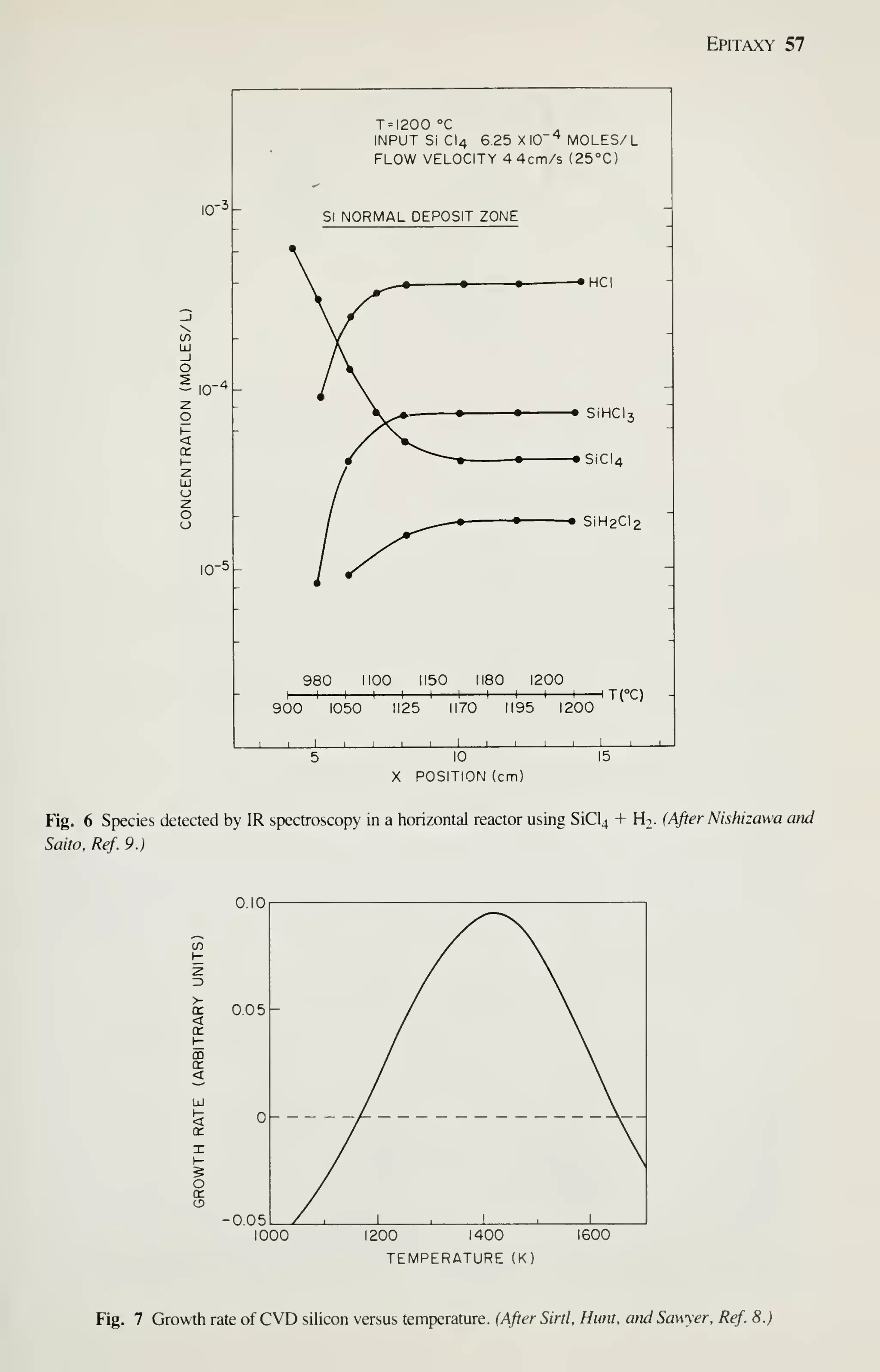

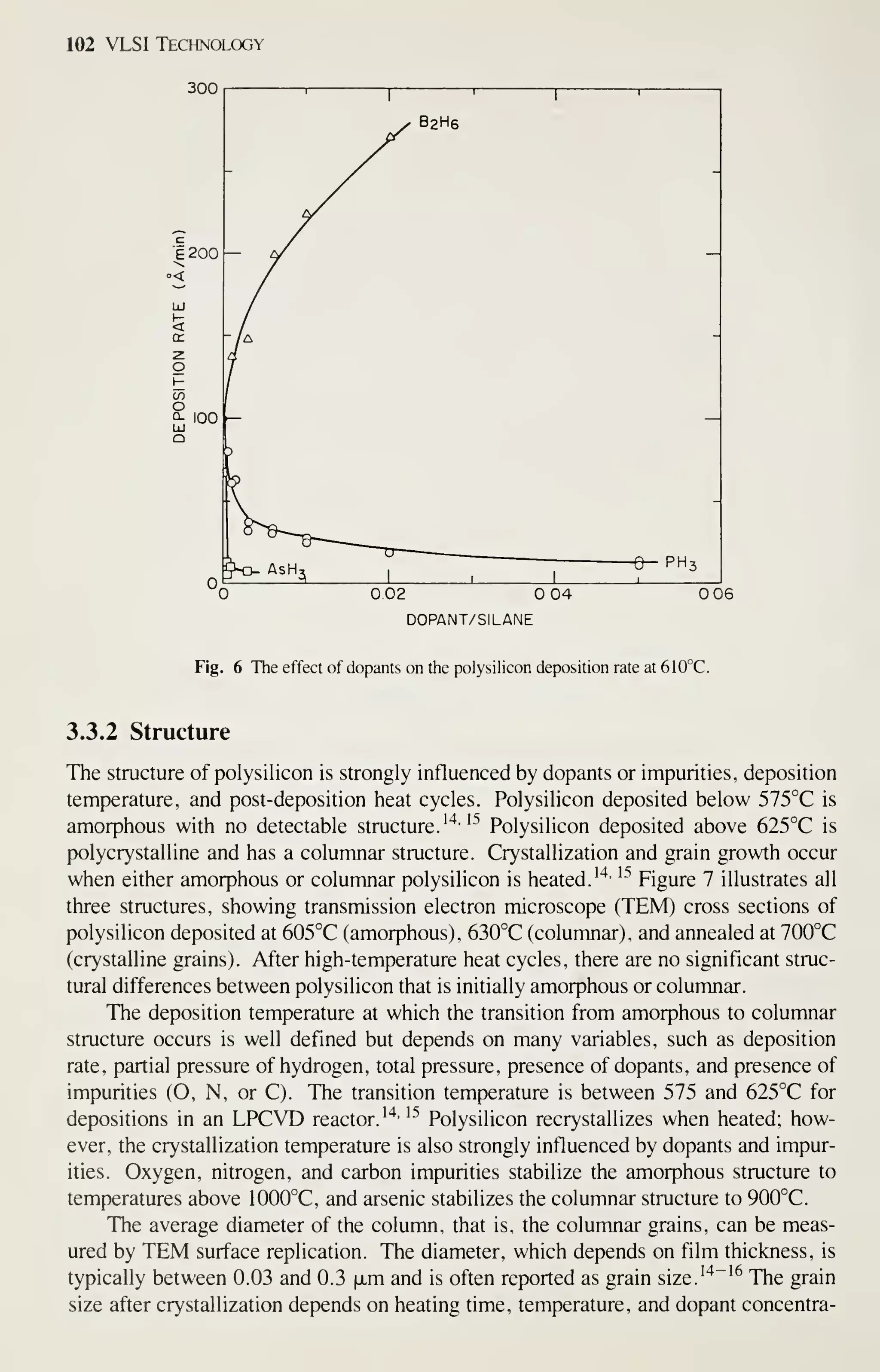

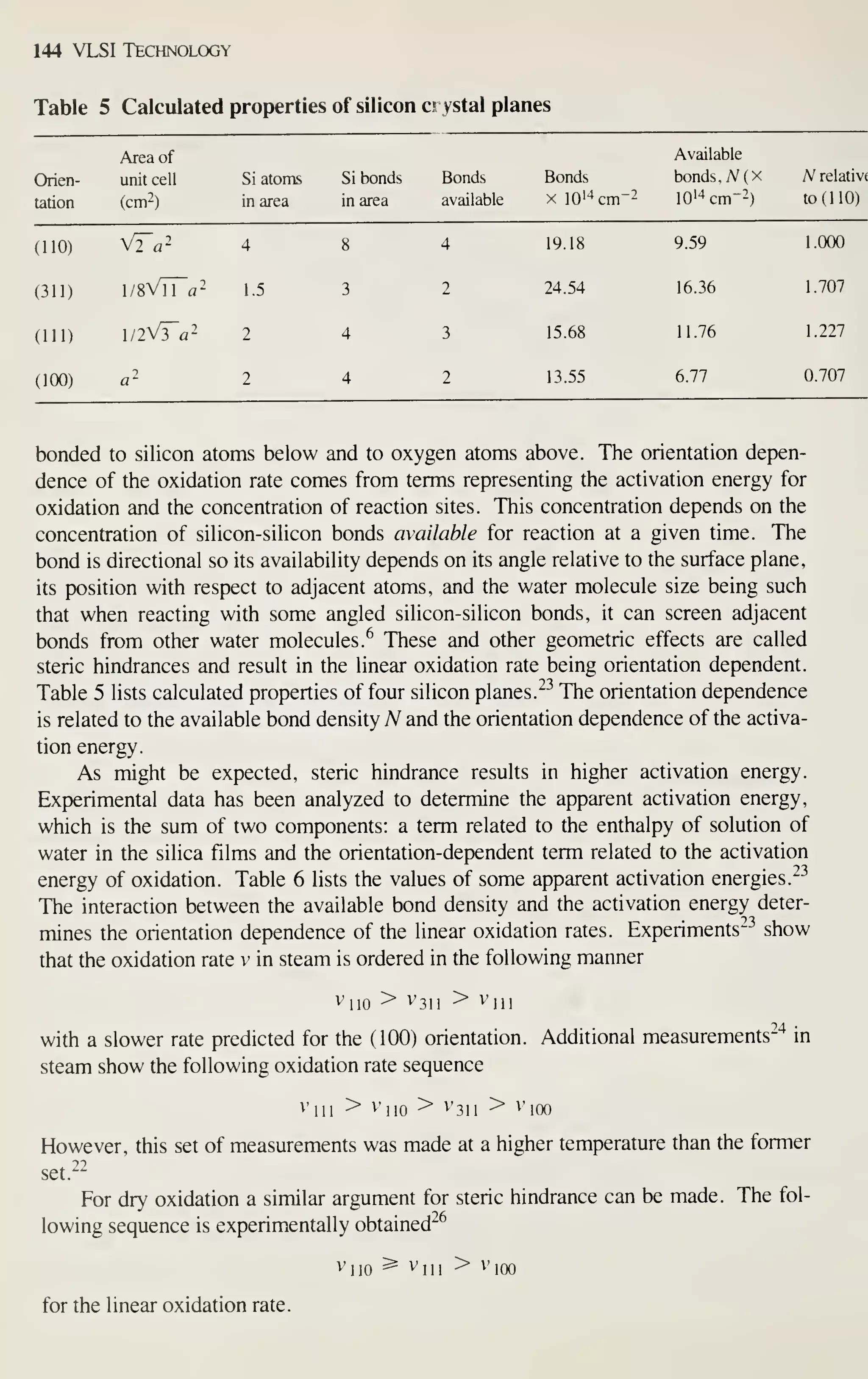

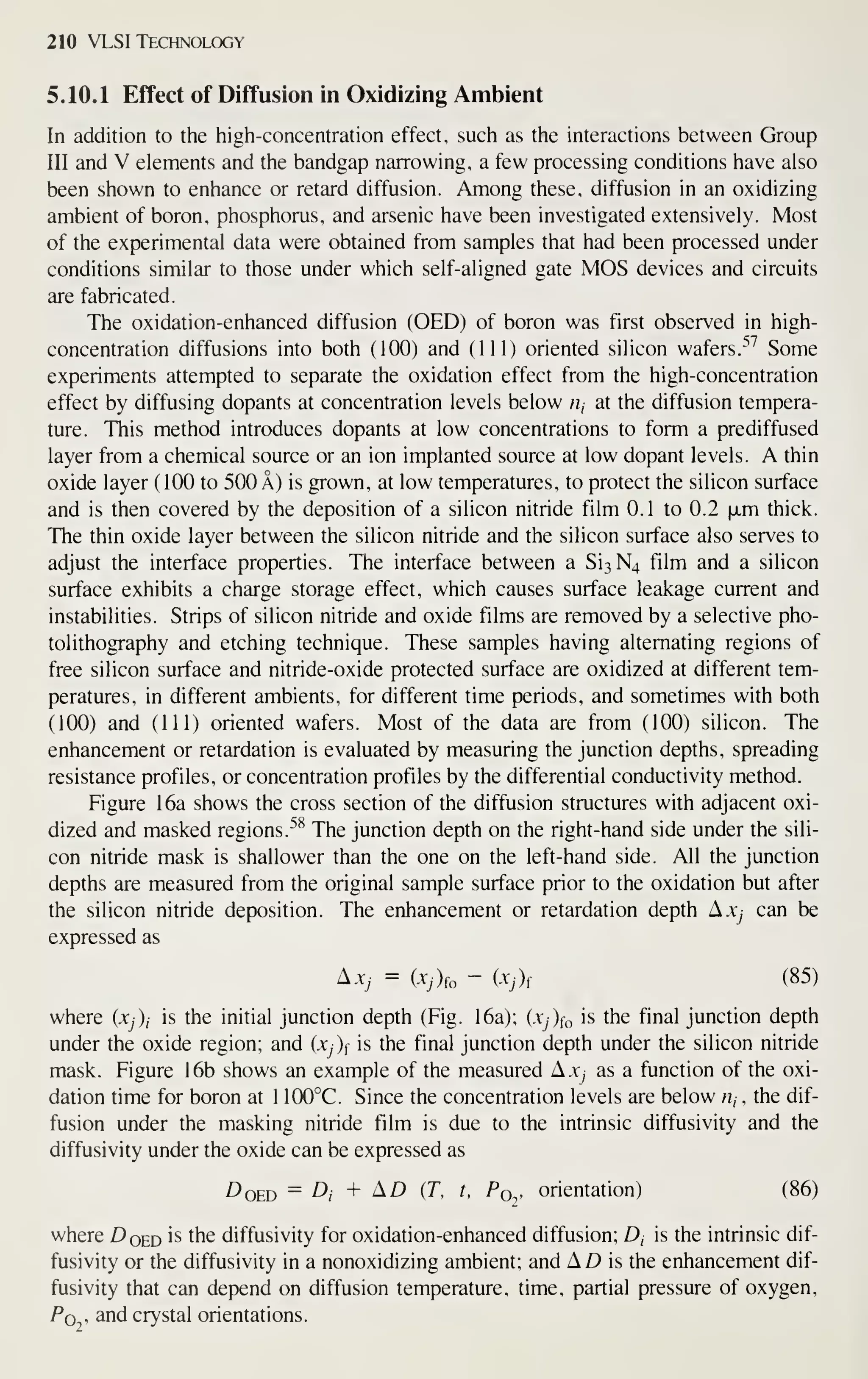

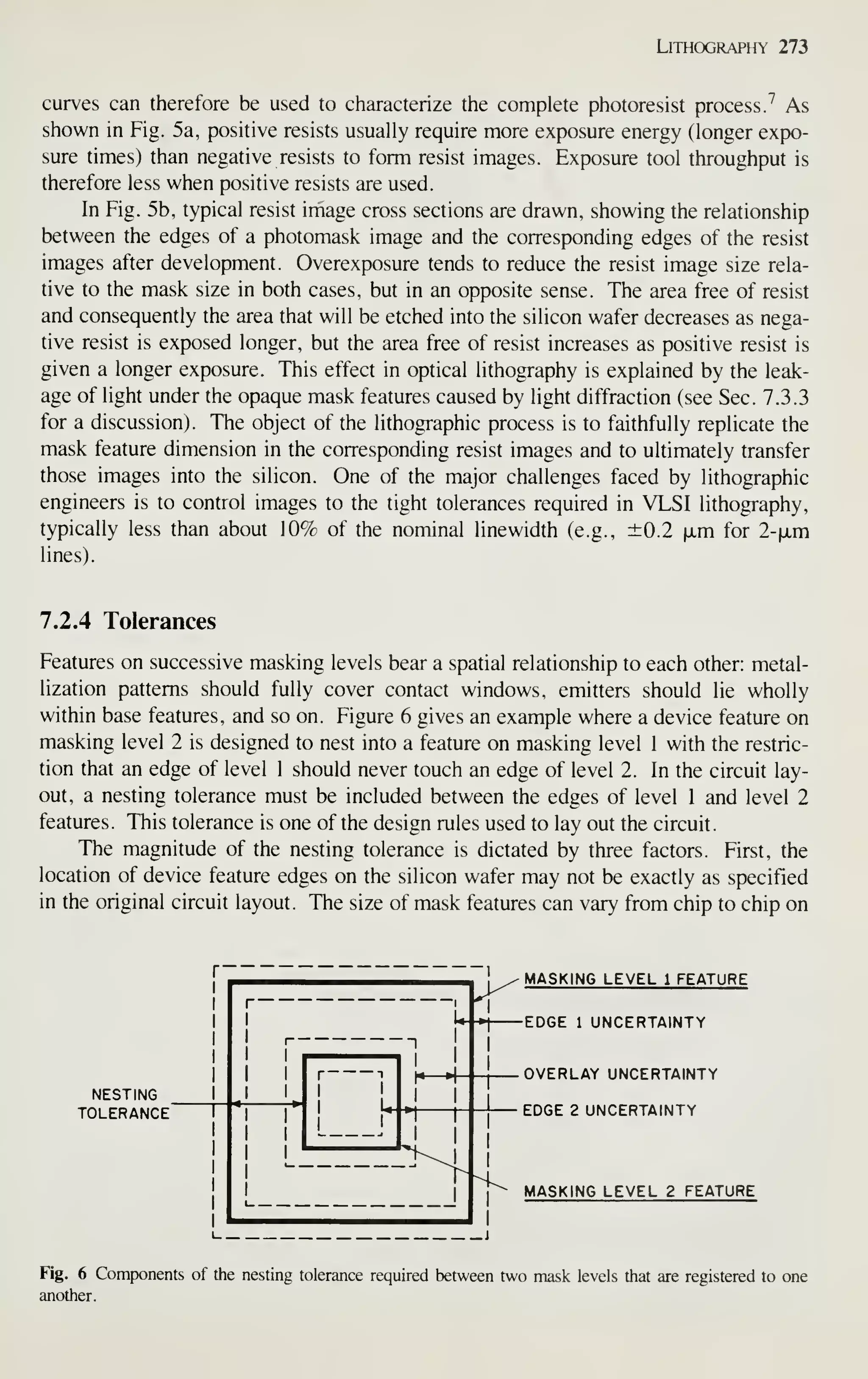

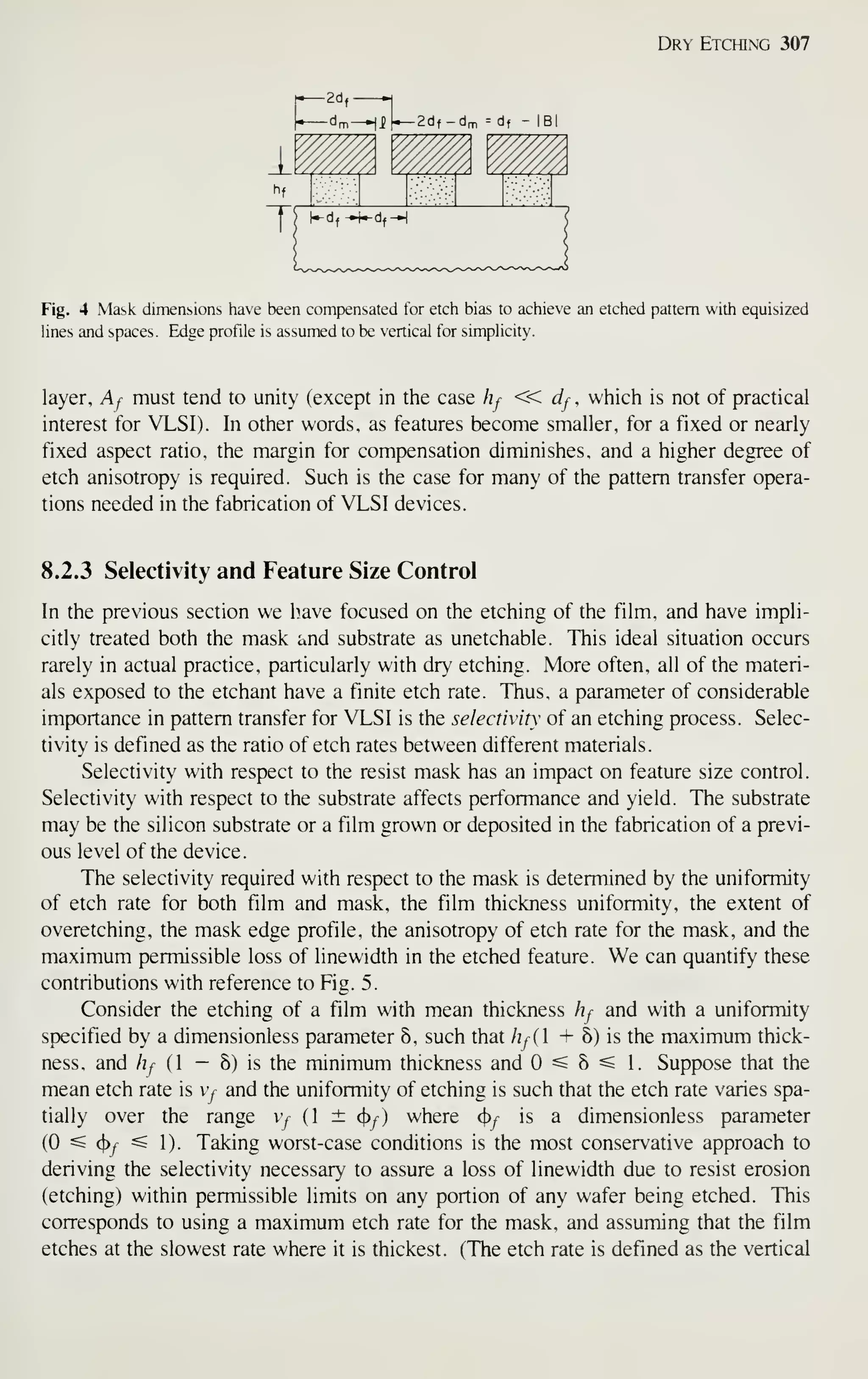

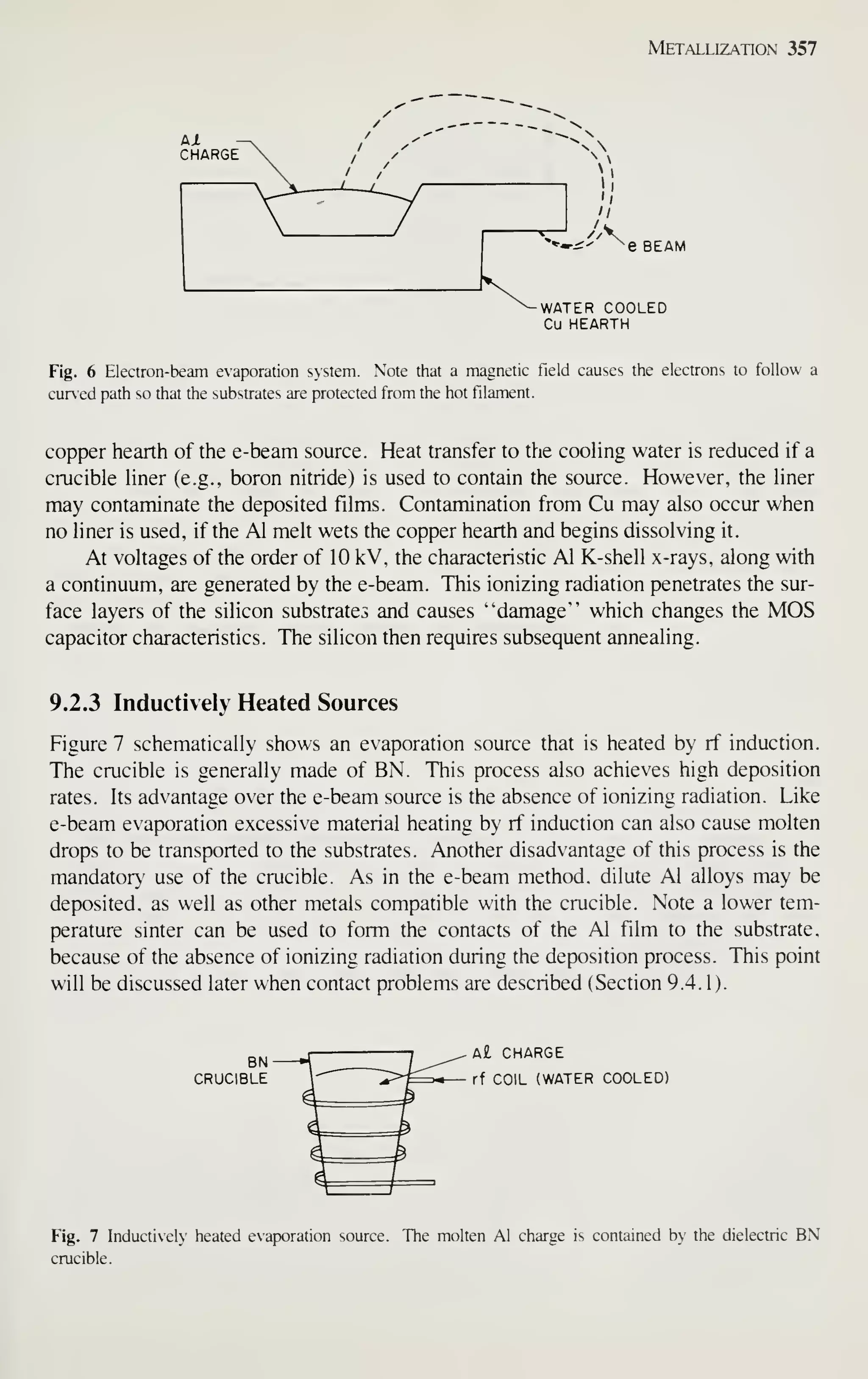

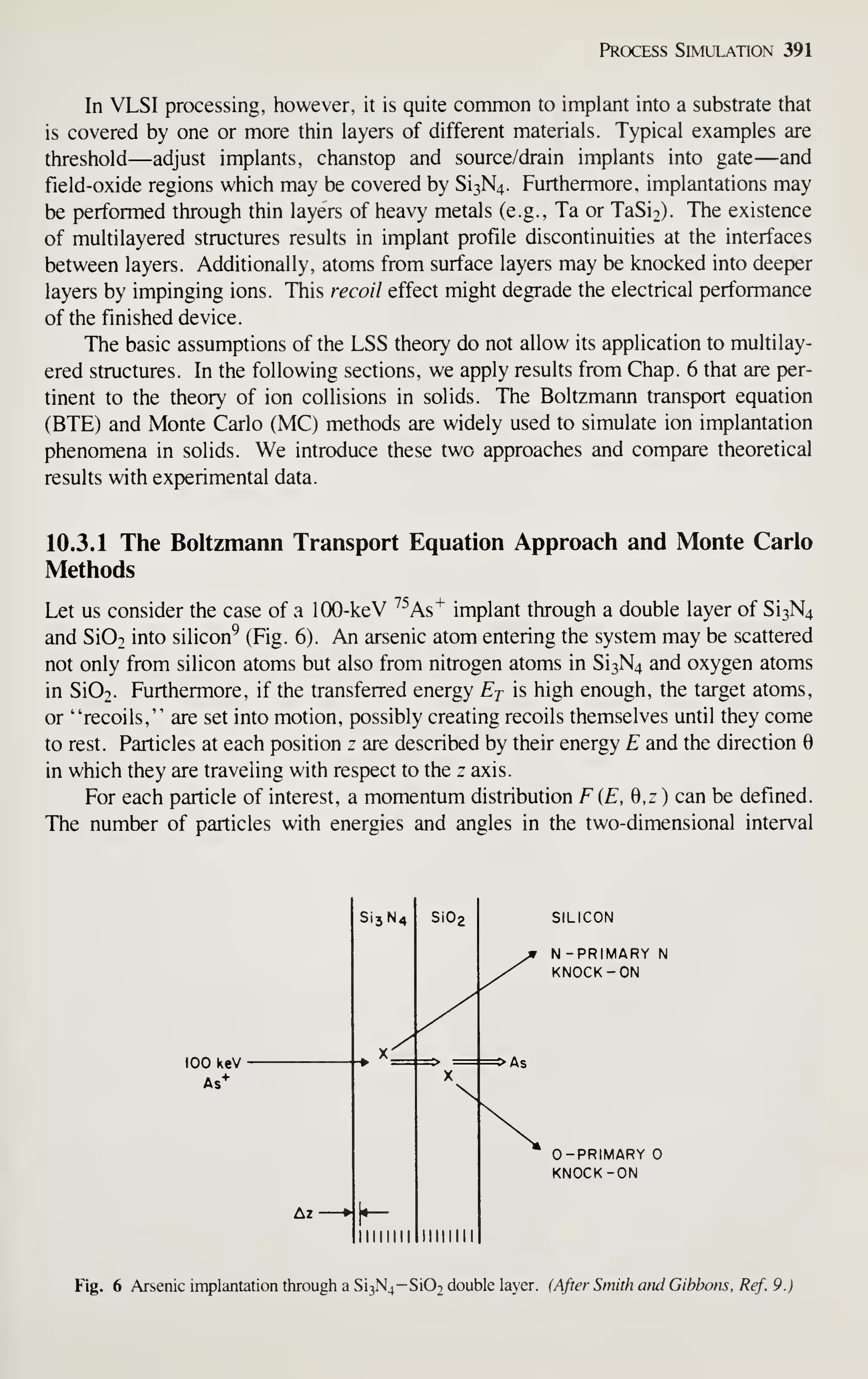

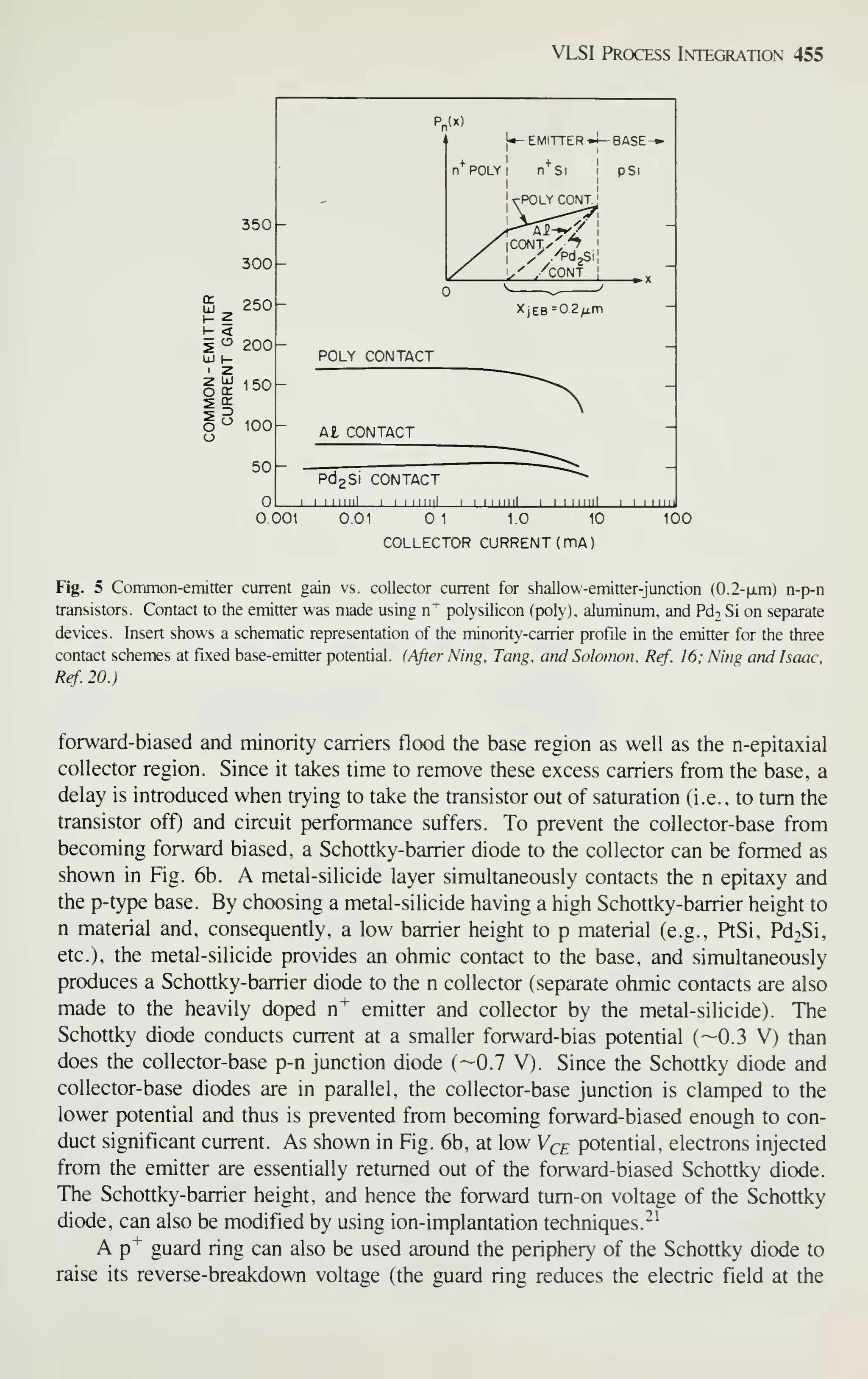

at an average annual rate of 15% and finally reach $400 billion by 1990. The

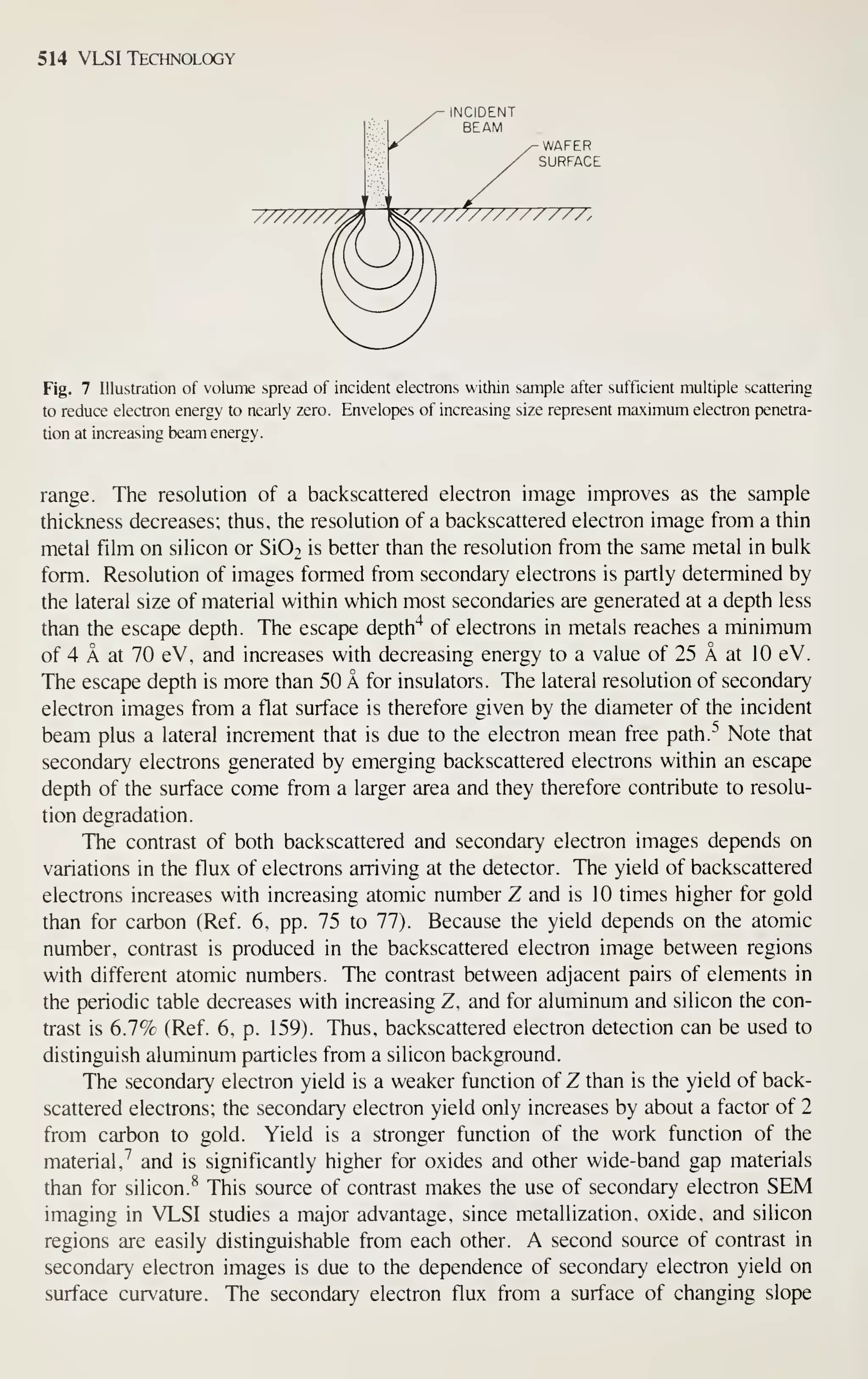

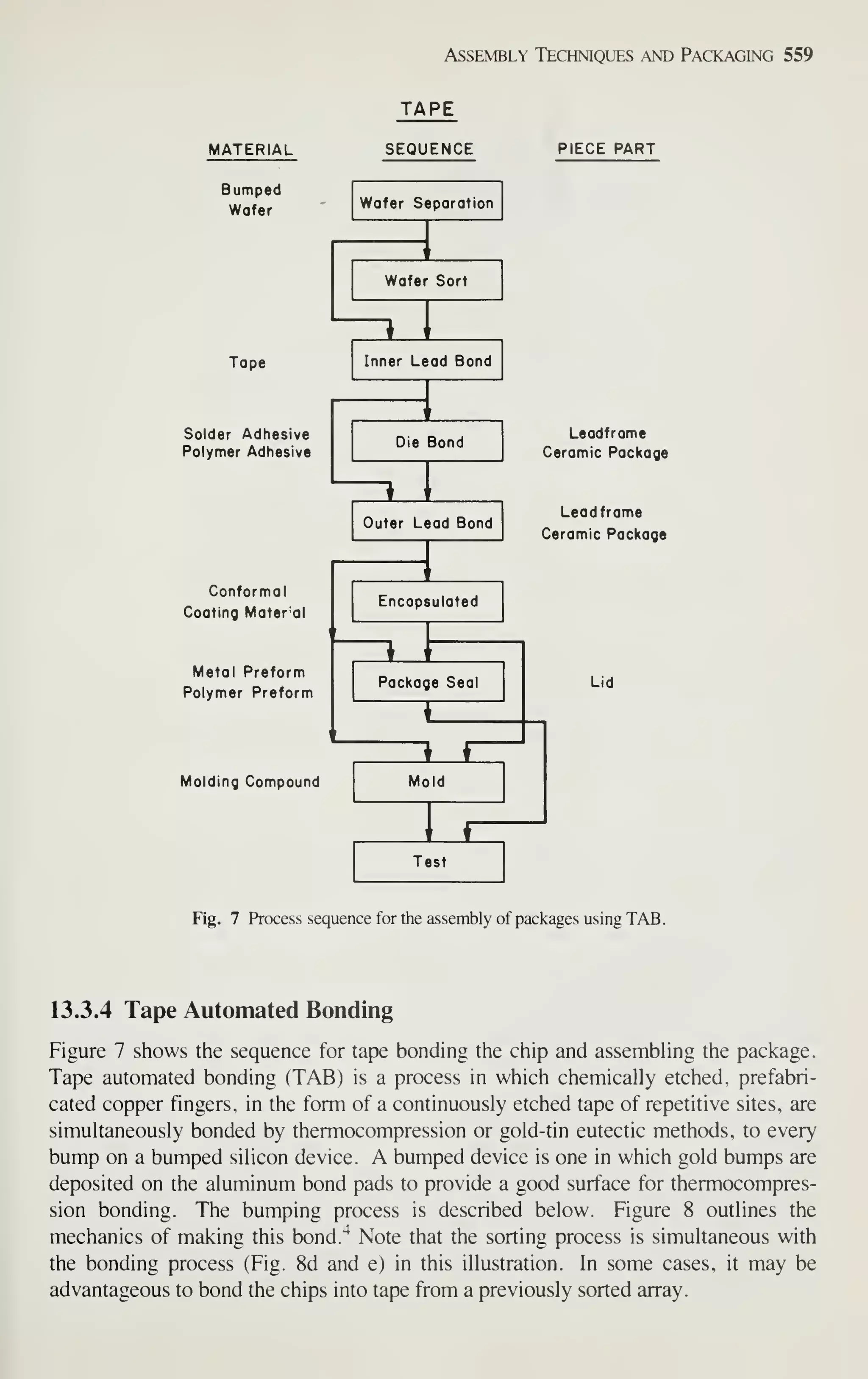

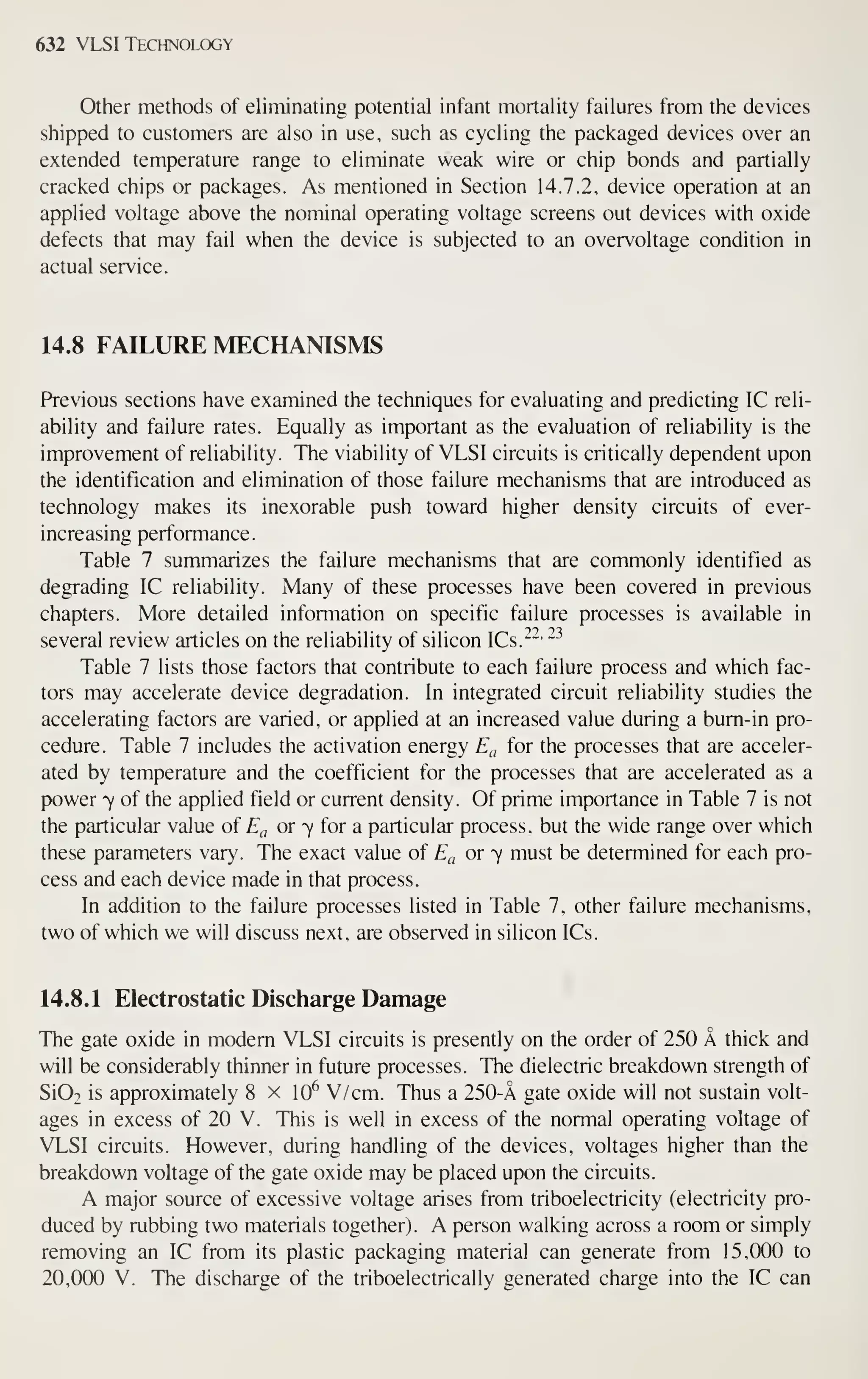

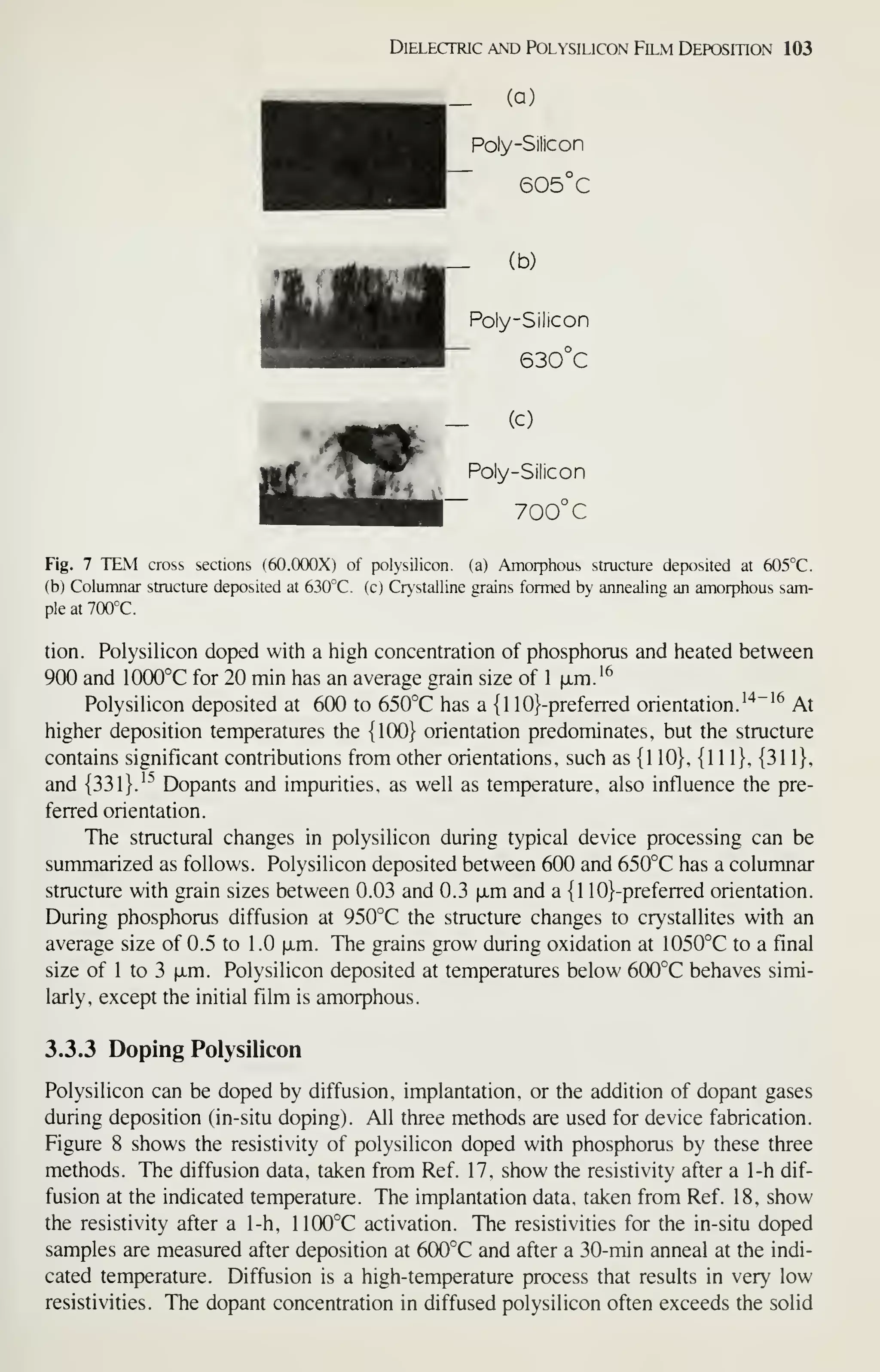

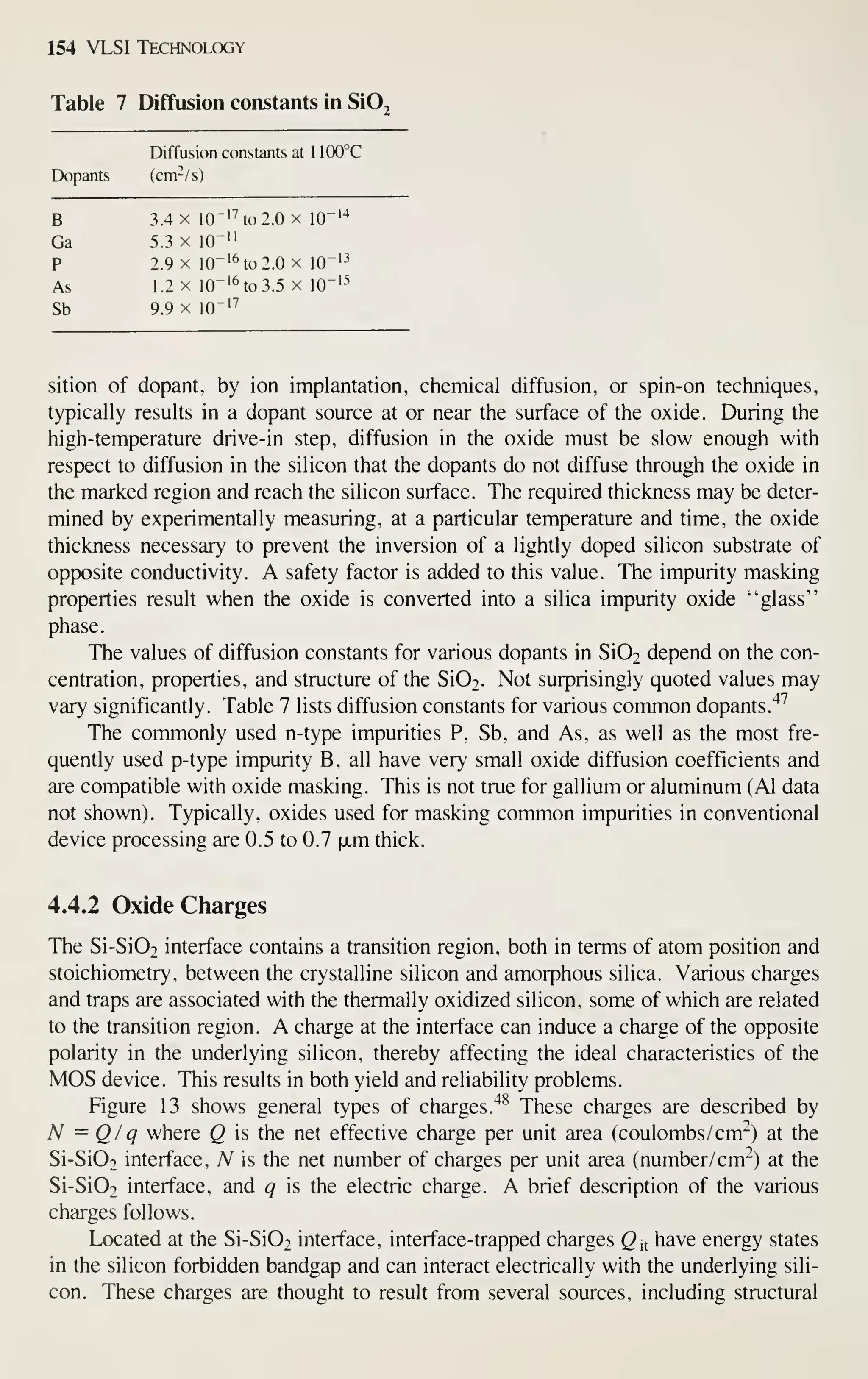

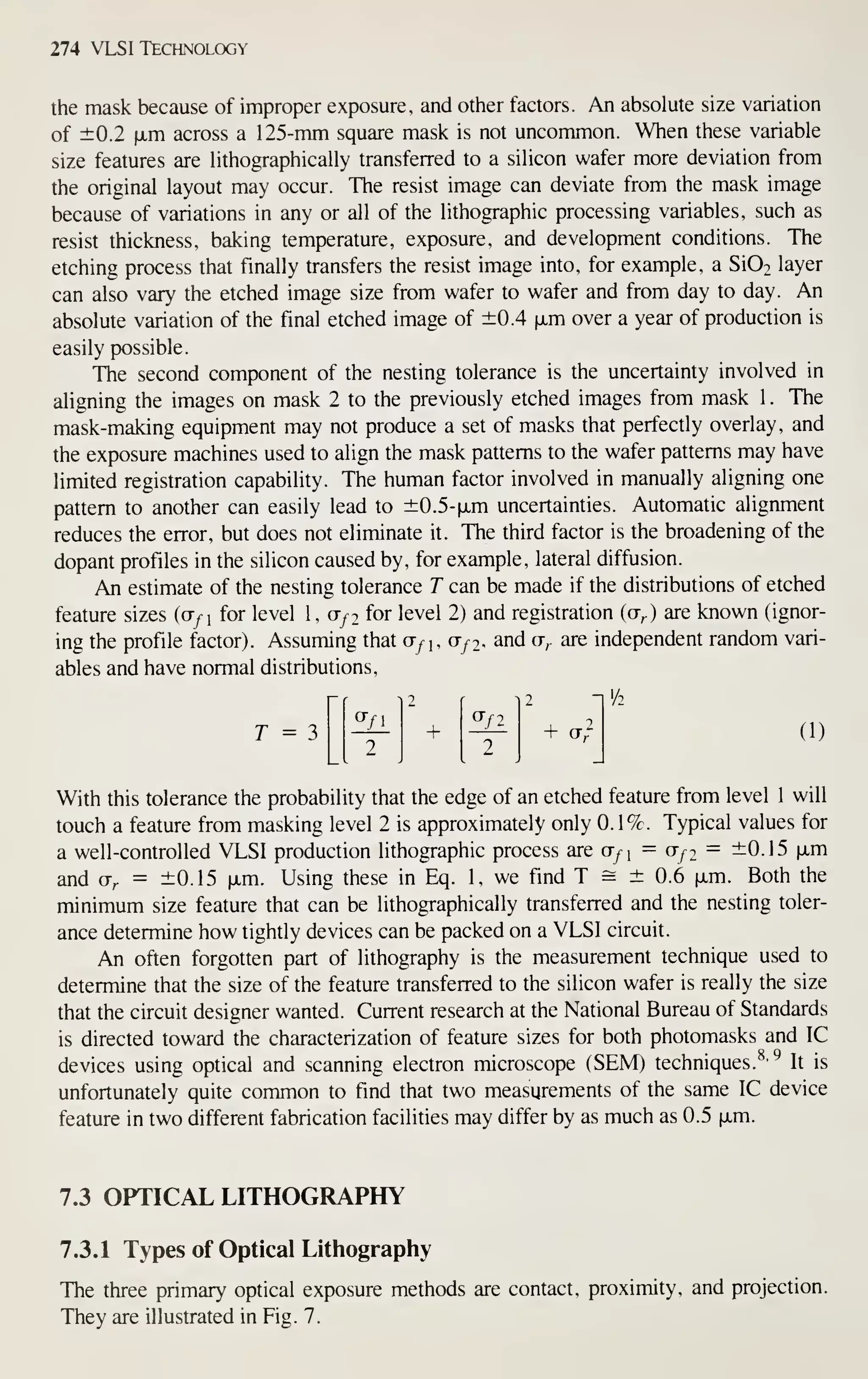

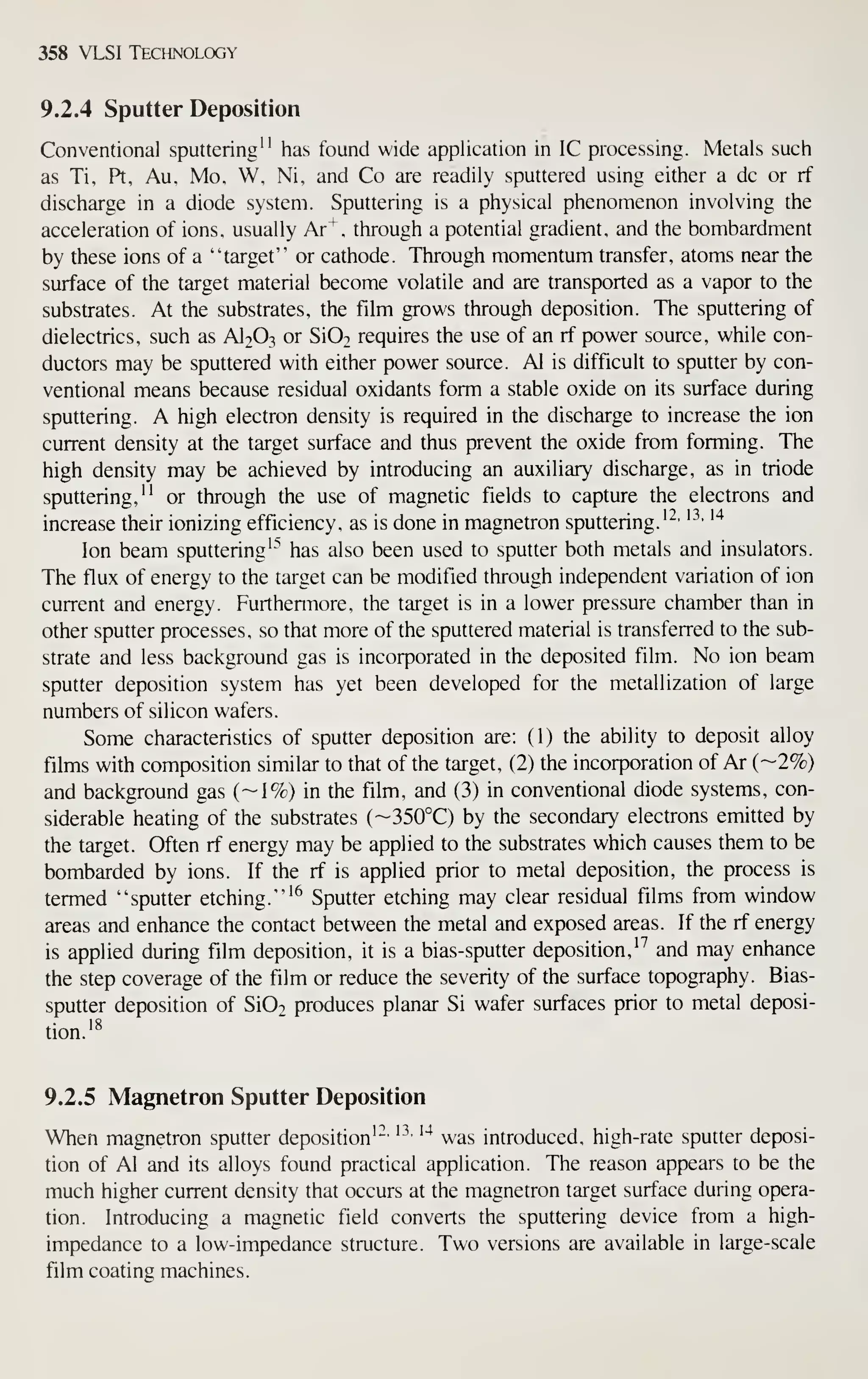

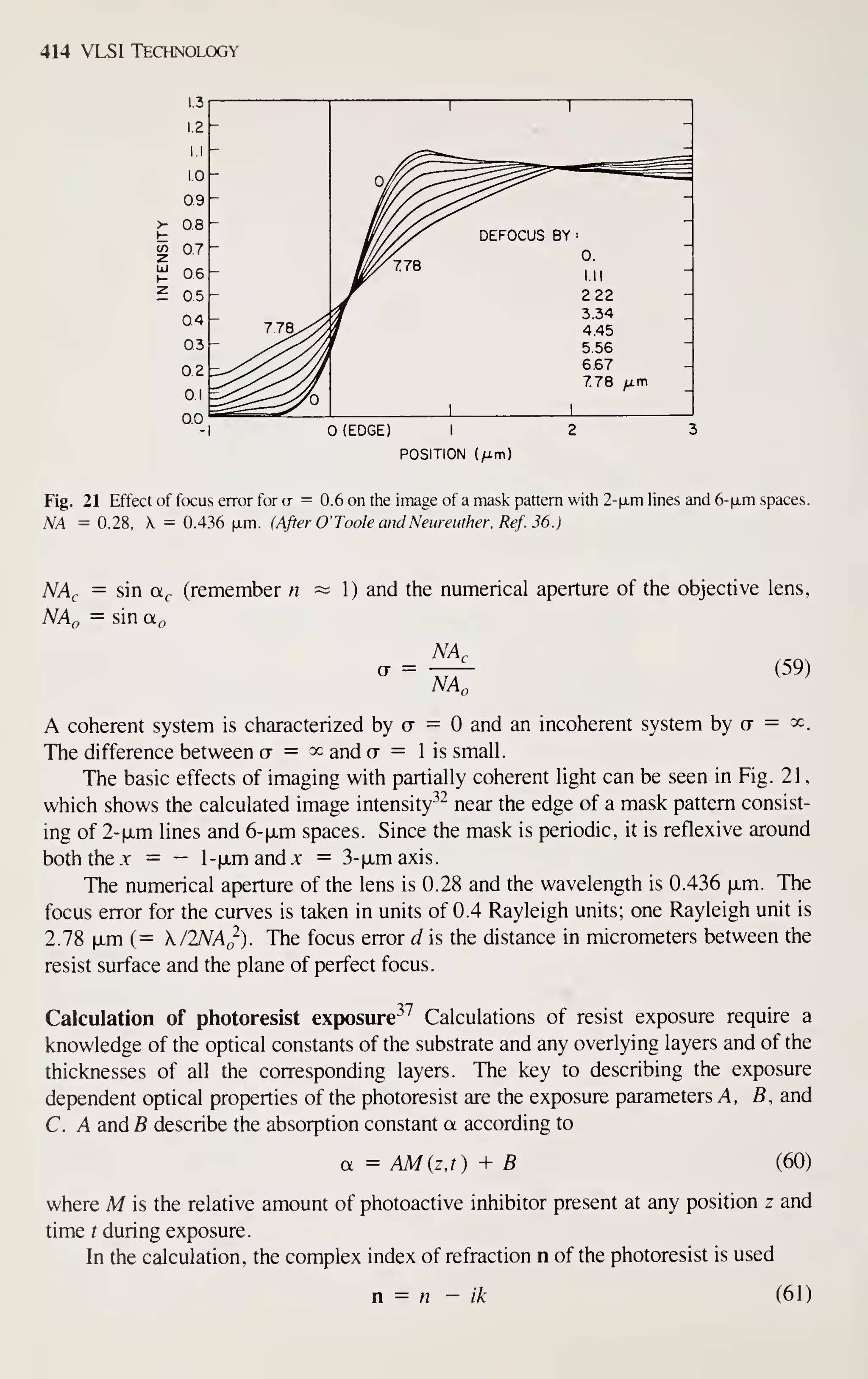

integrated circuit (IC) market has increased at an even higher rate than electronic sales

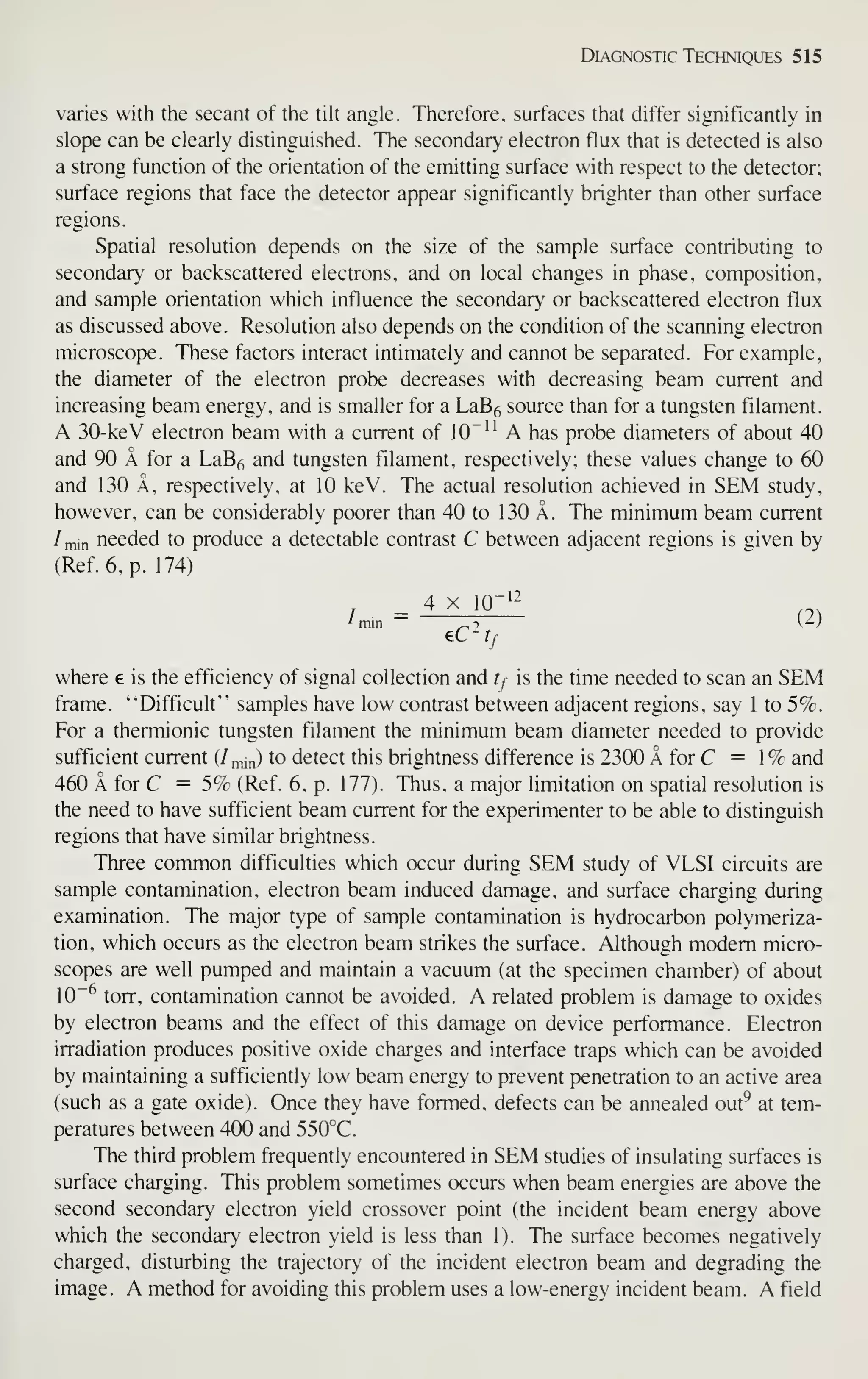

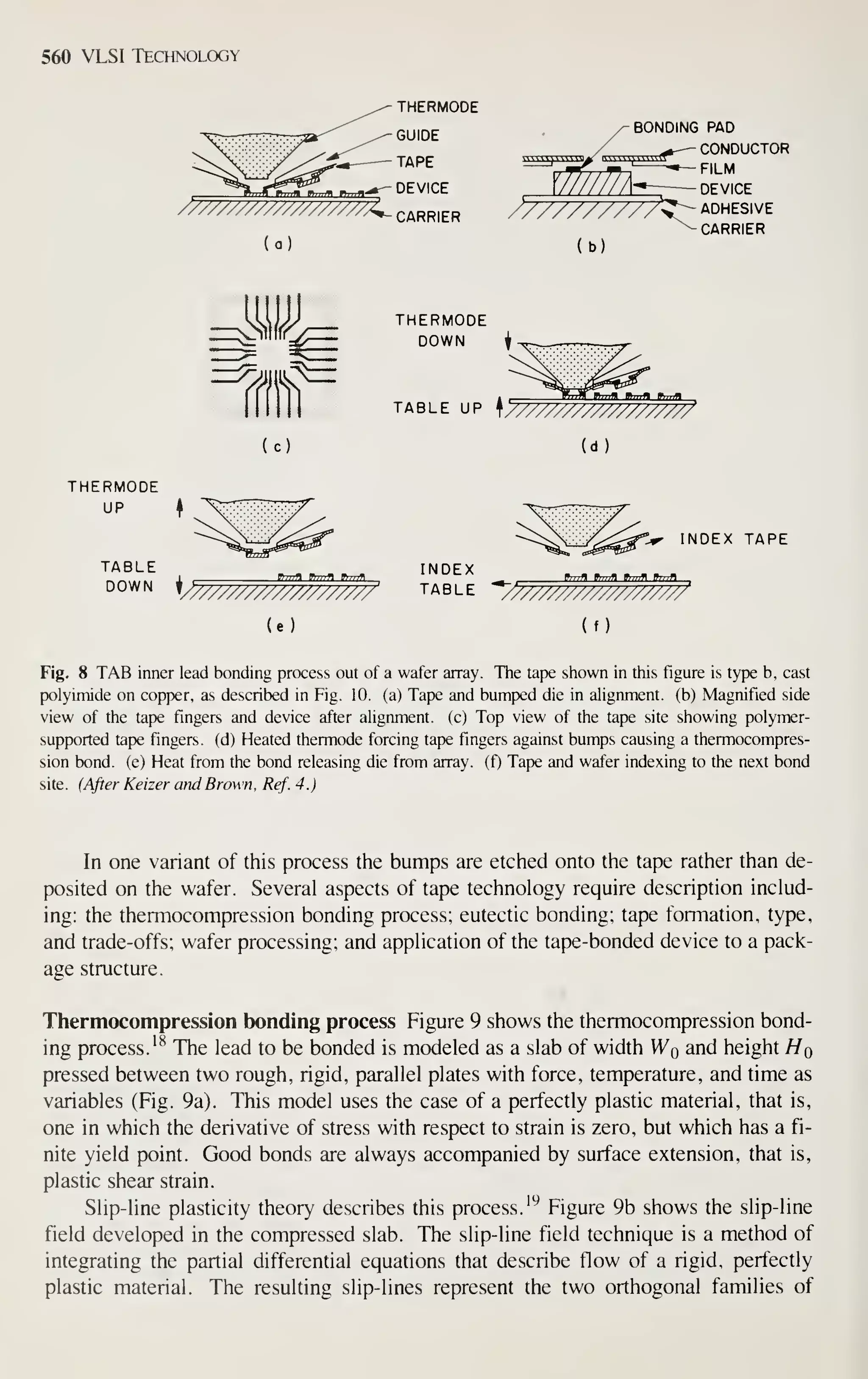

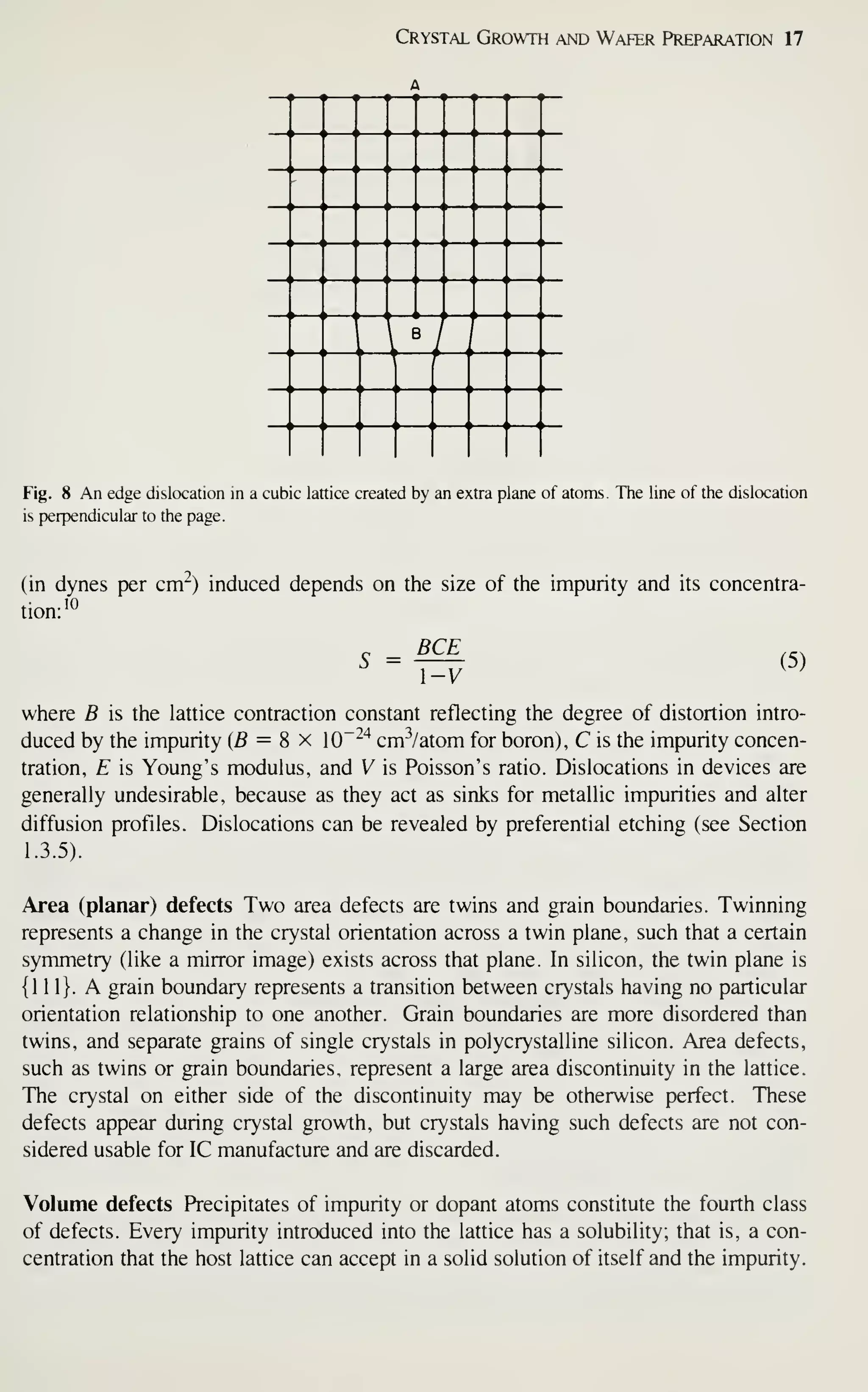

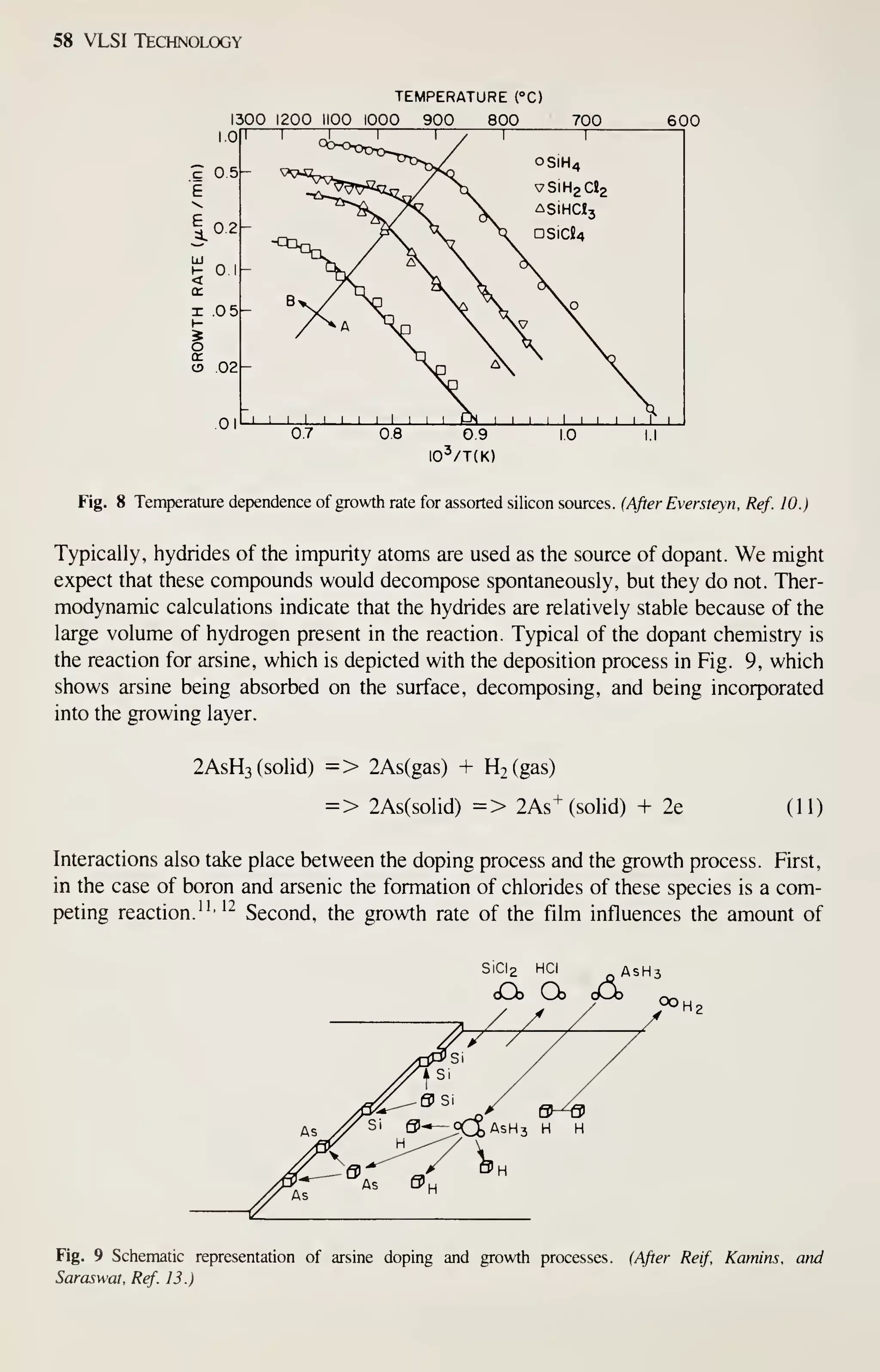

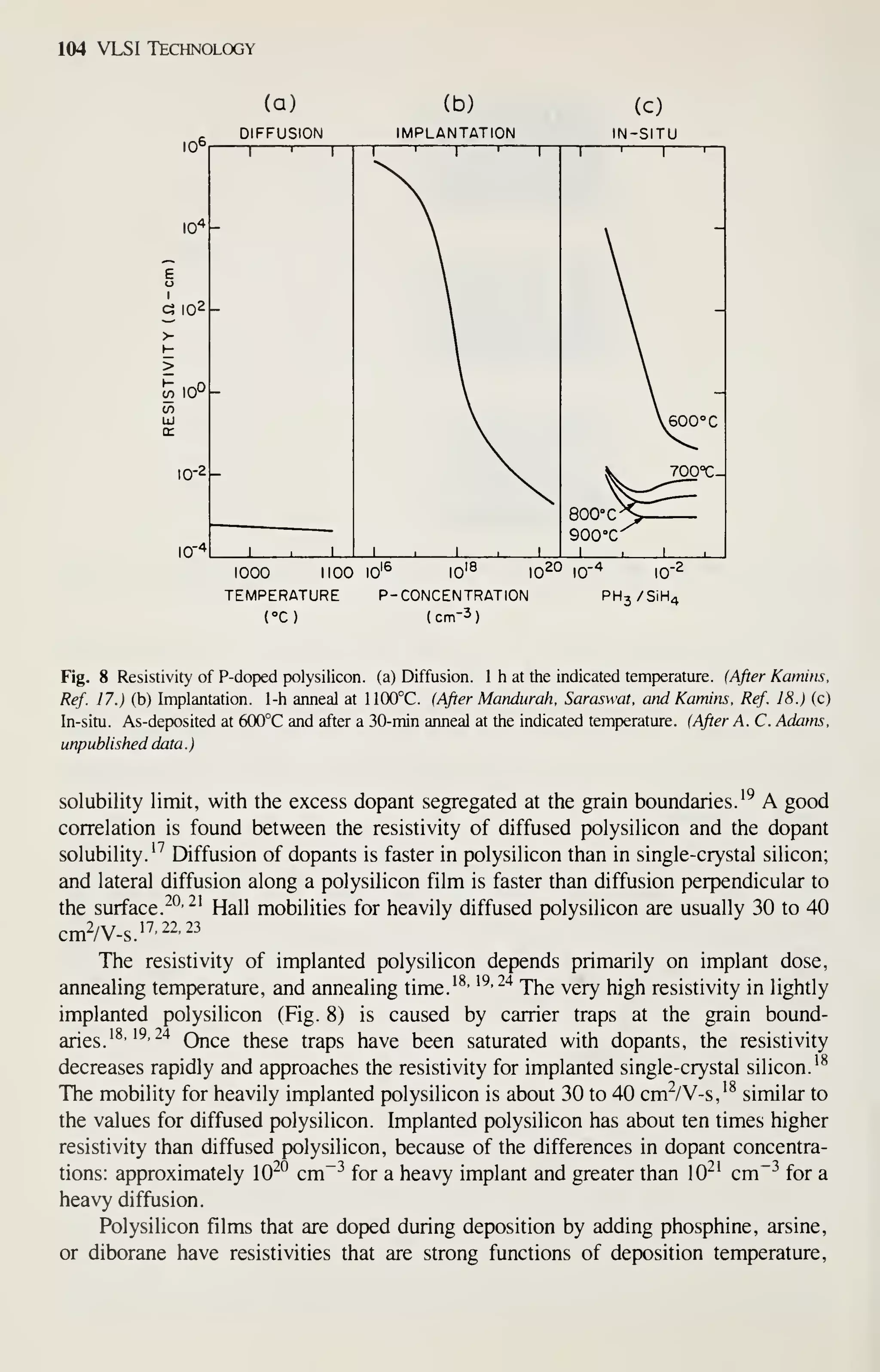

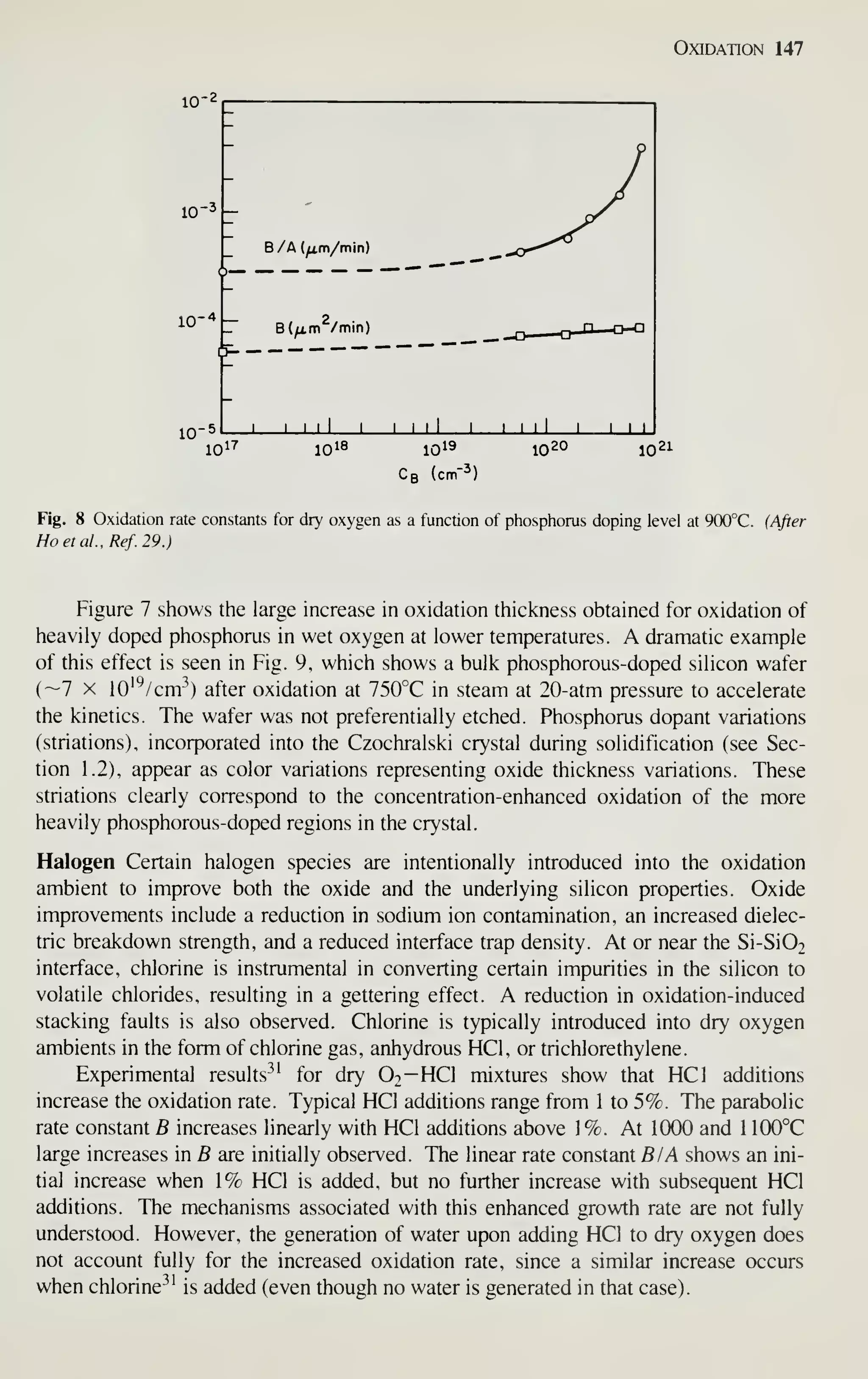

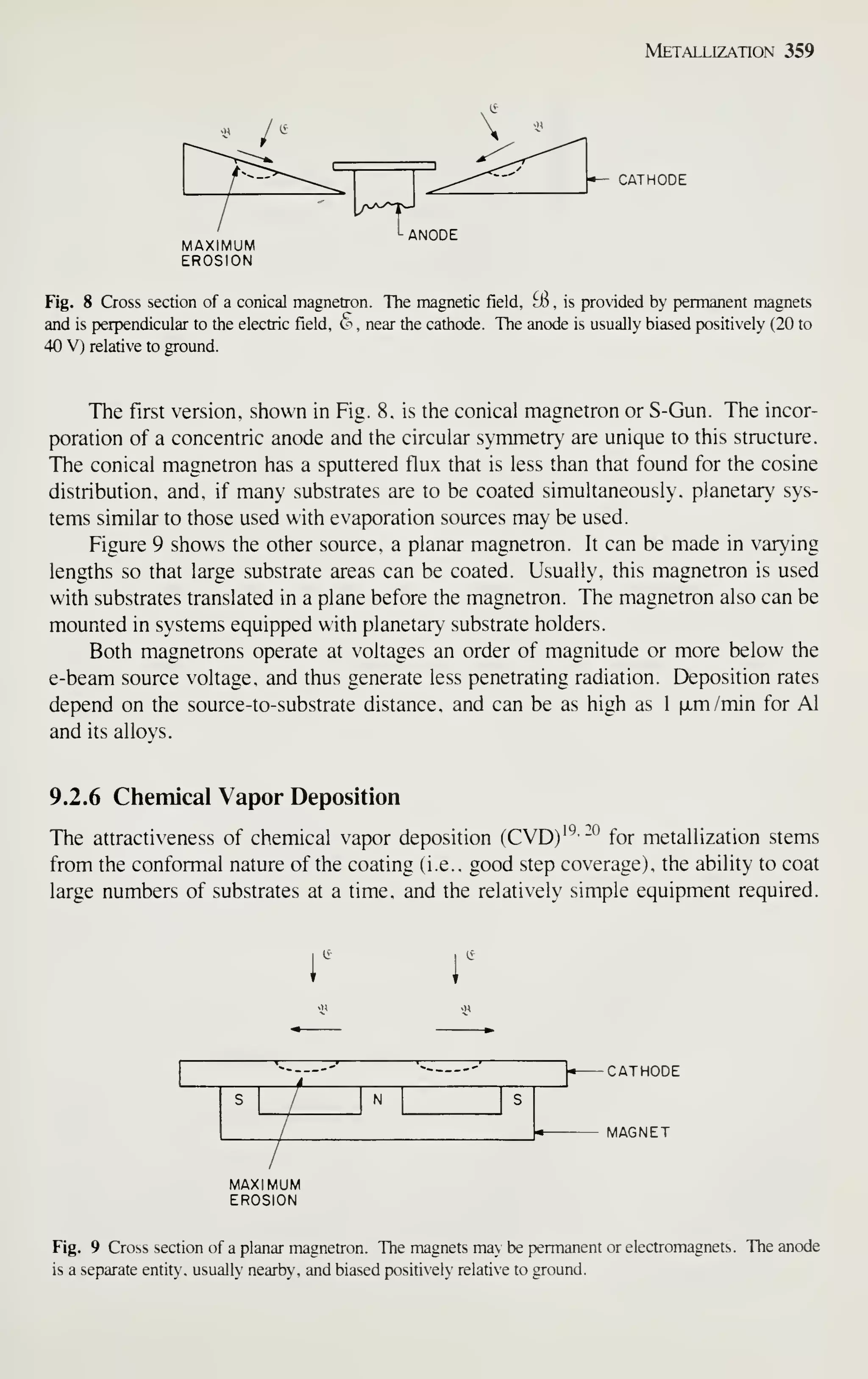

[see Fig. 1, curve (b)]. IC sales in the United States were $6.6 billion in 1981 and are

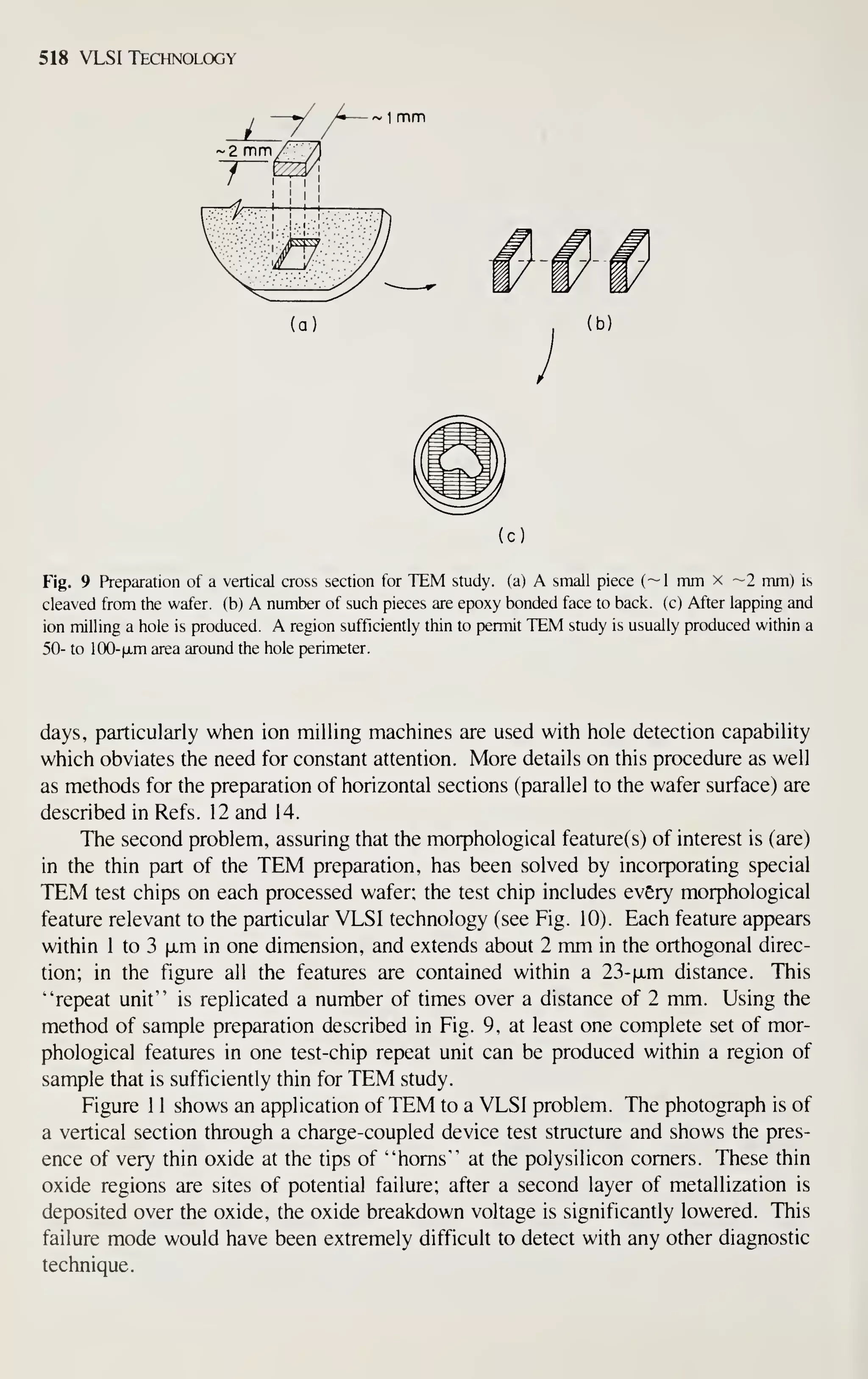

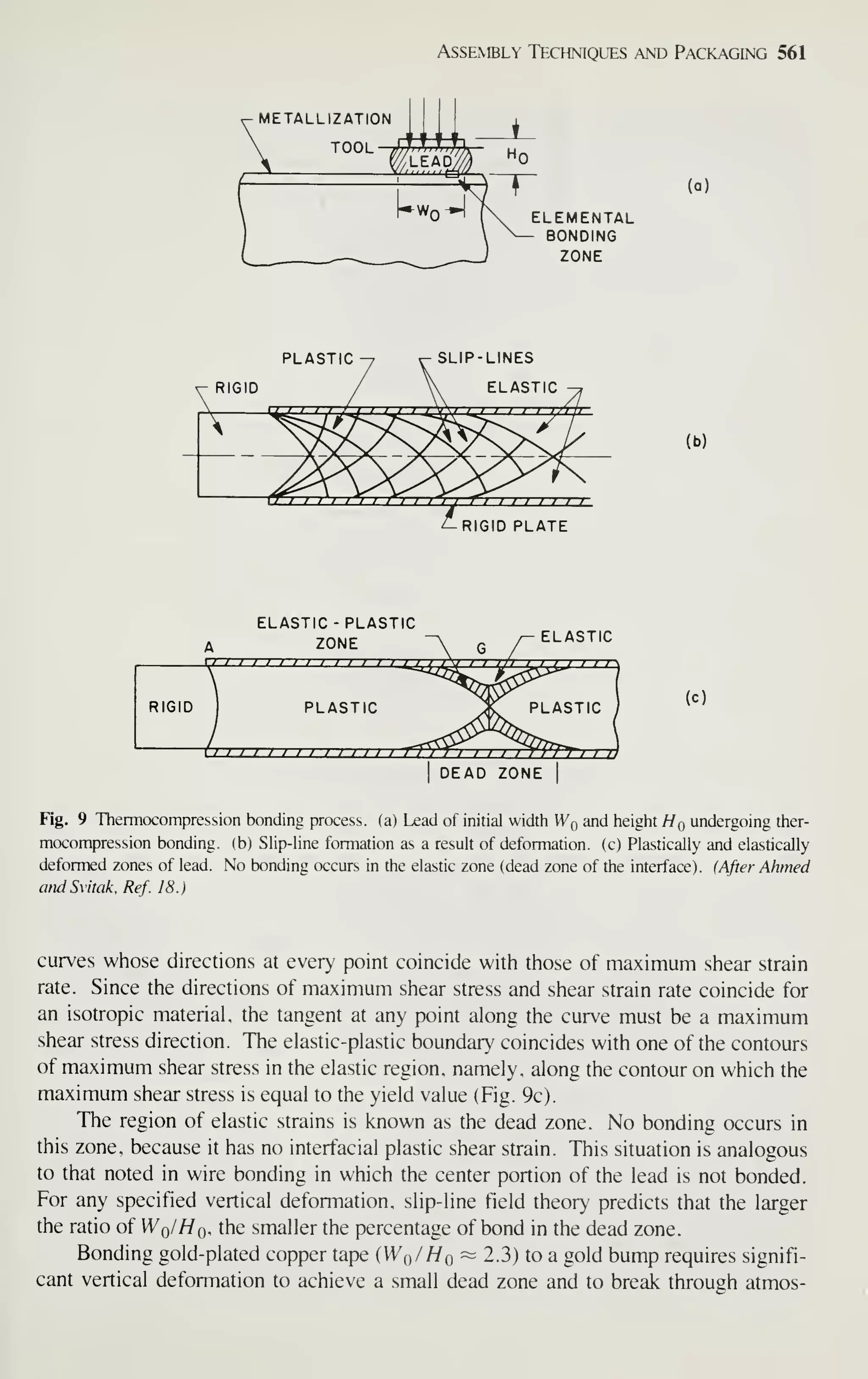

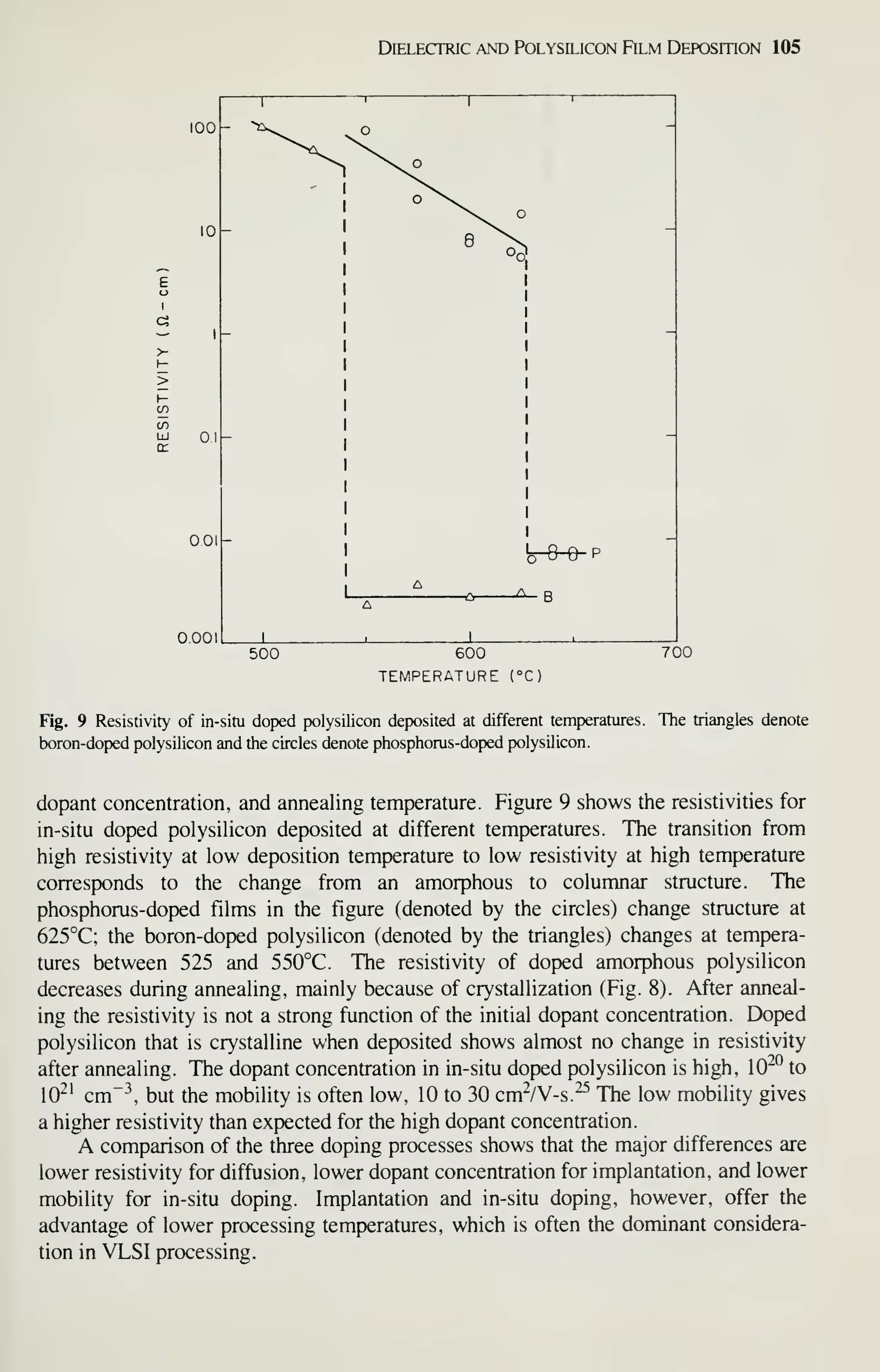

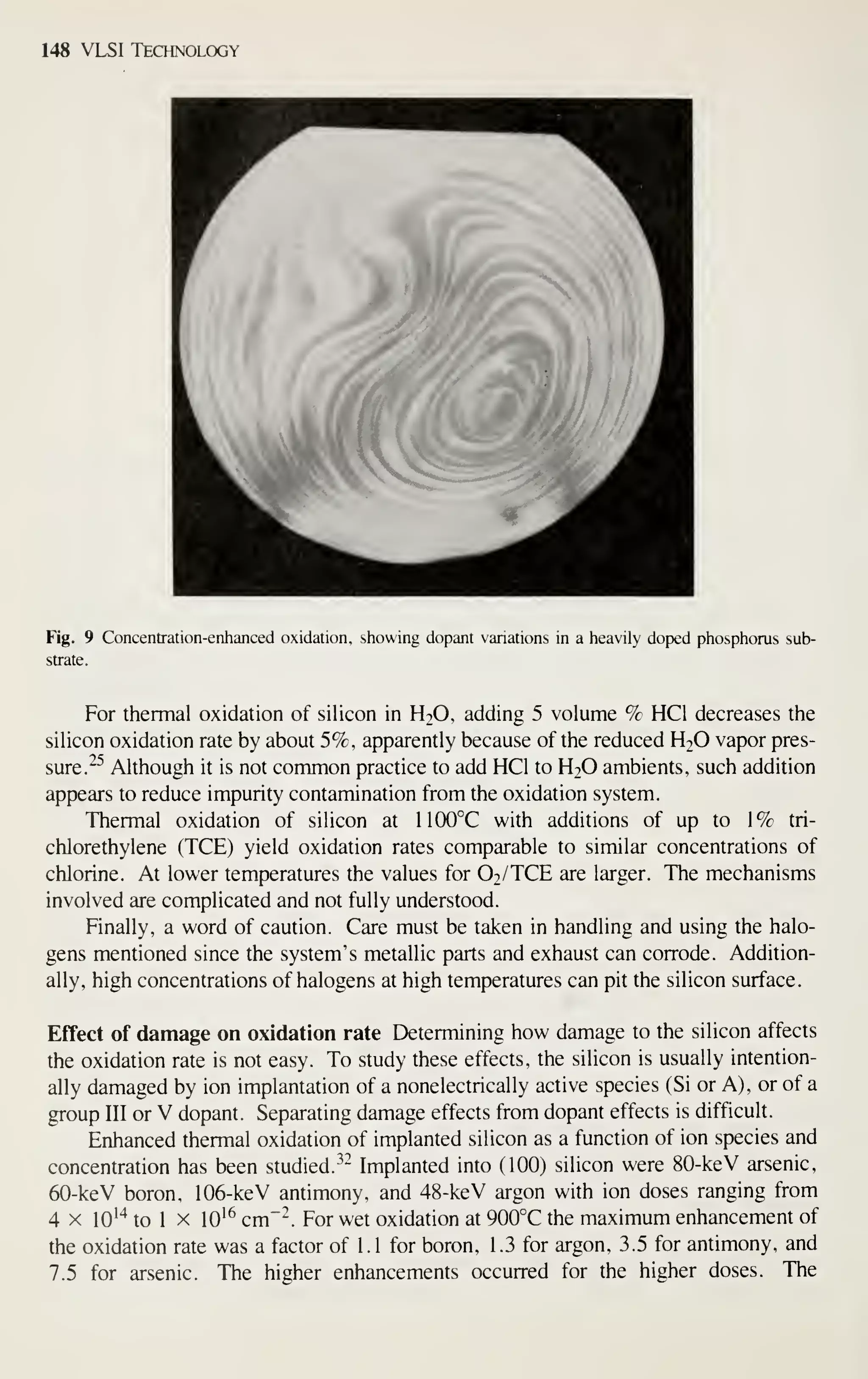

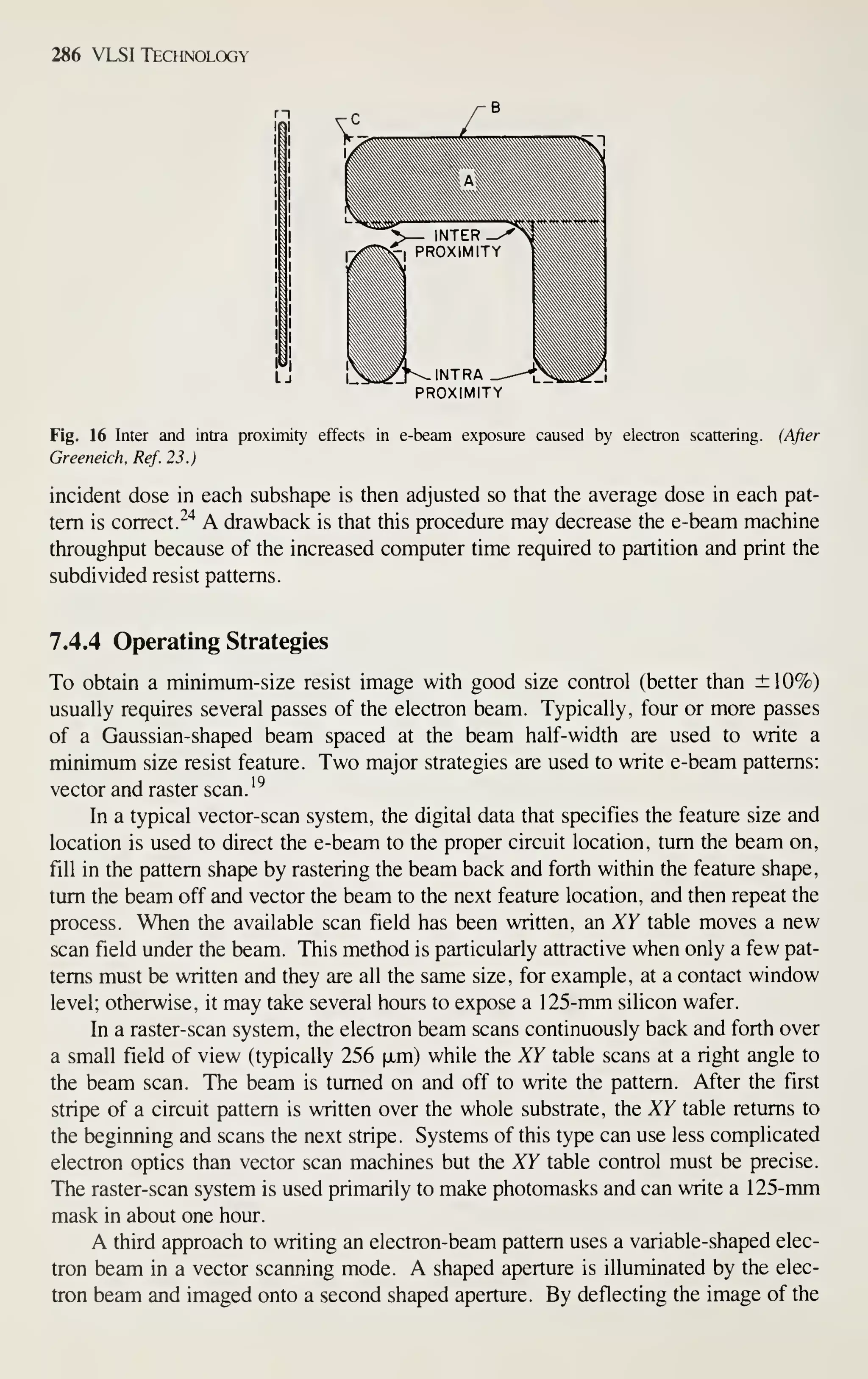

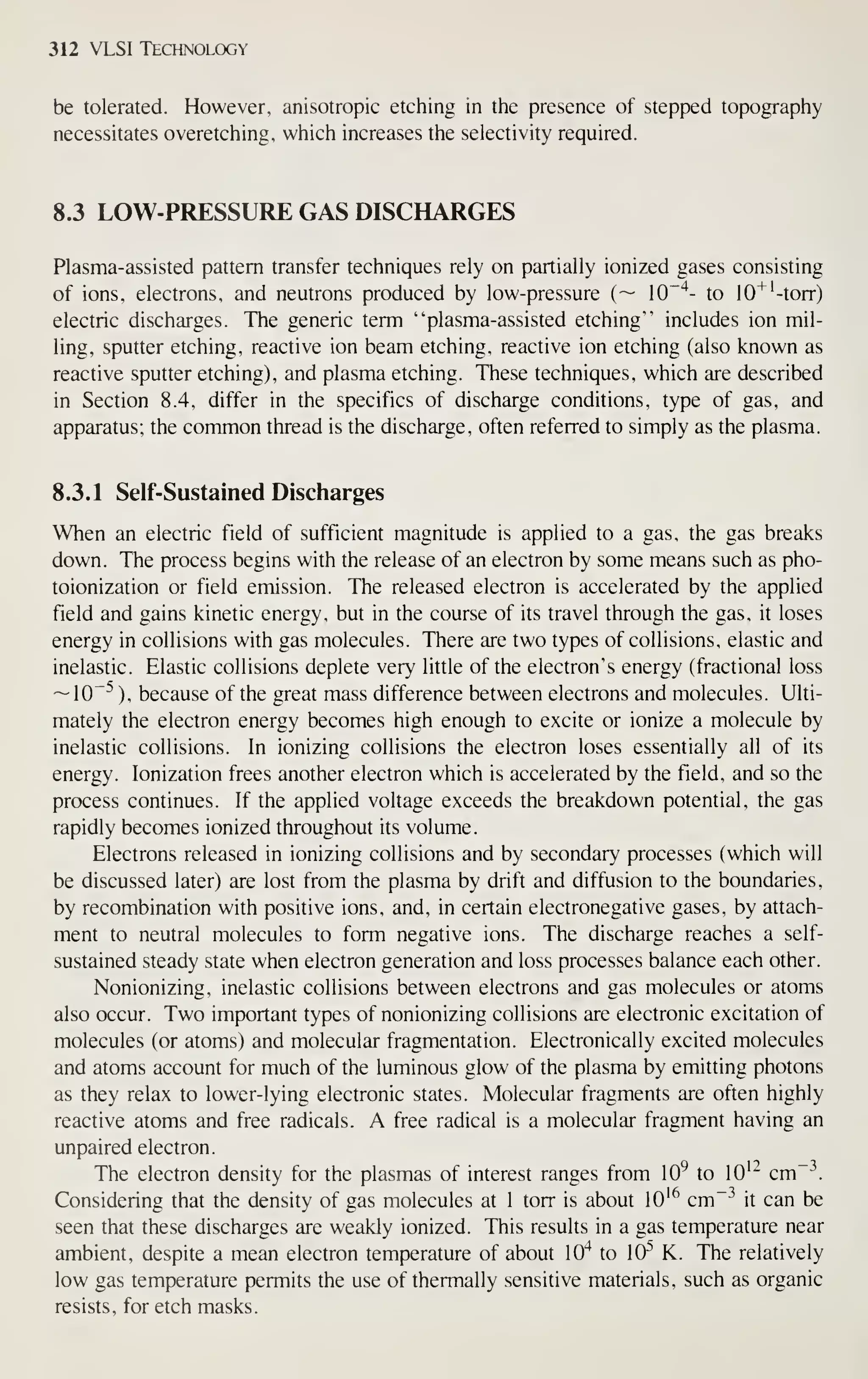

expected to grow by 25% annually, reaching $50 billion by 1990. The main

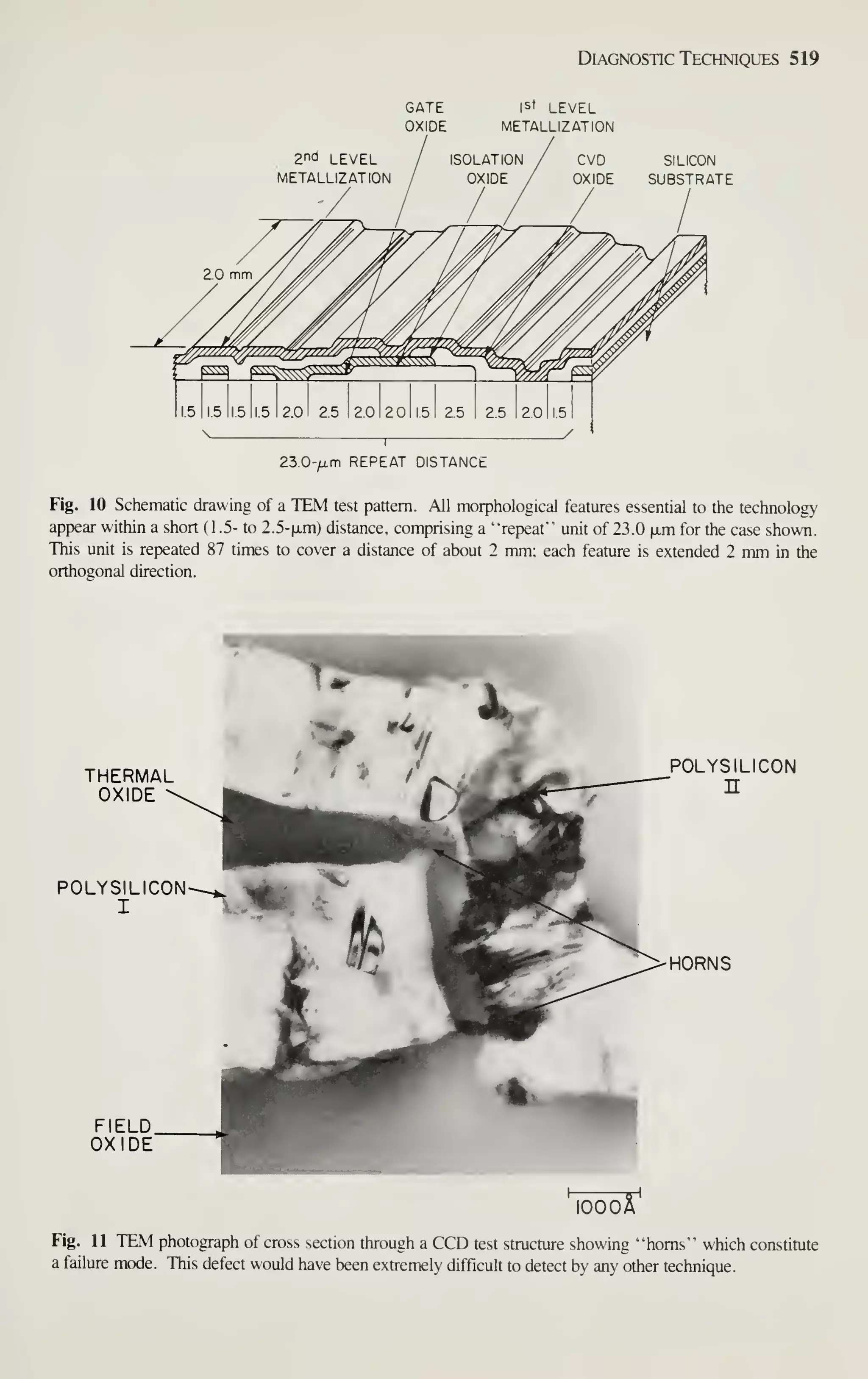

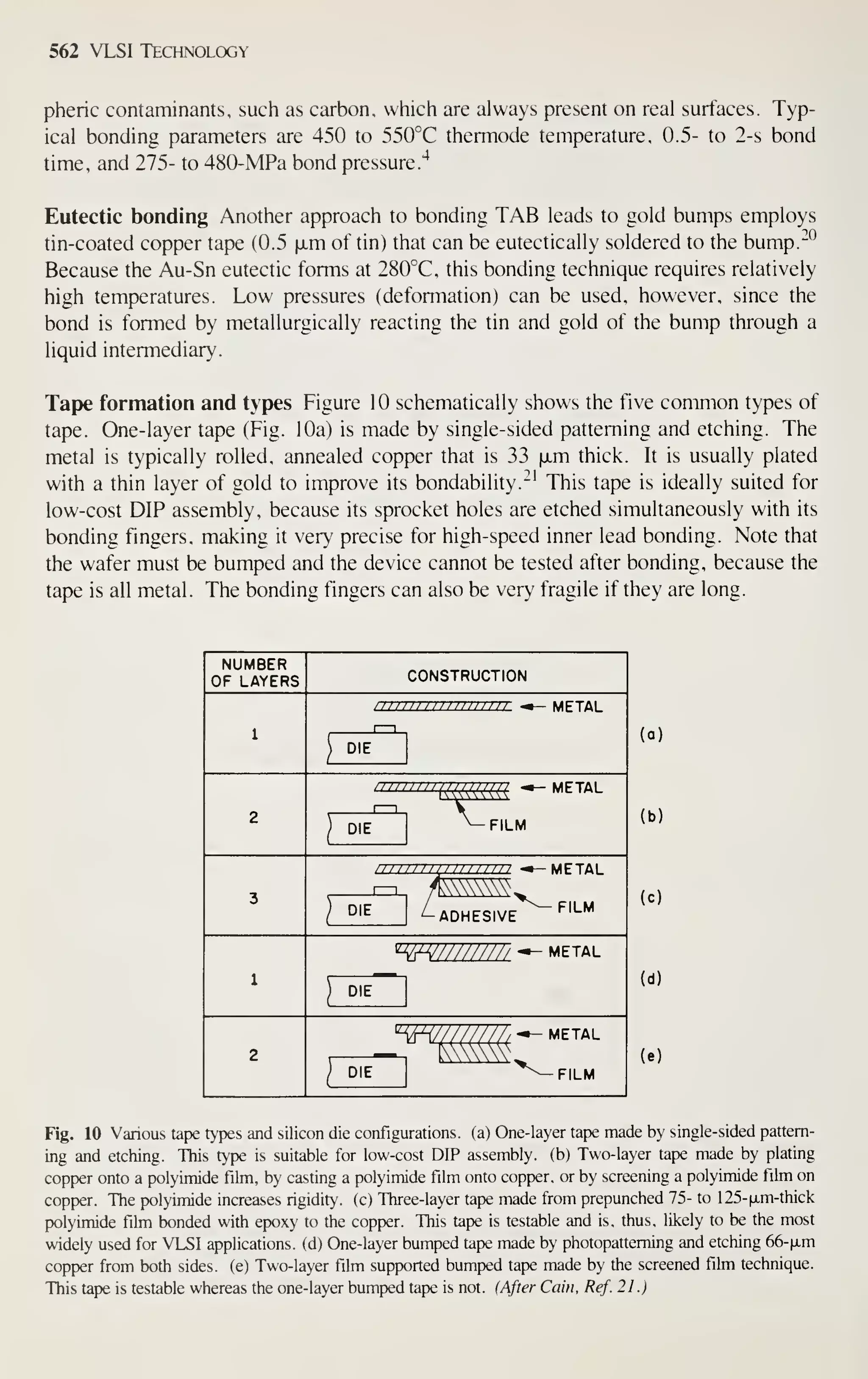

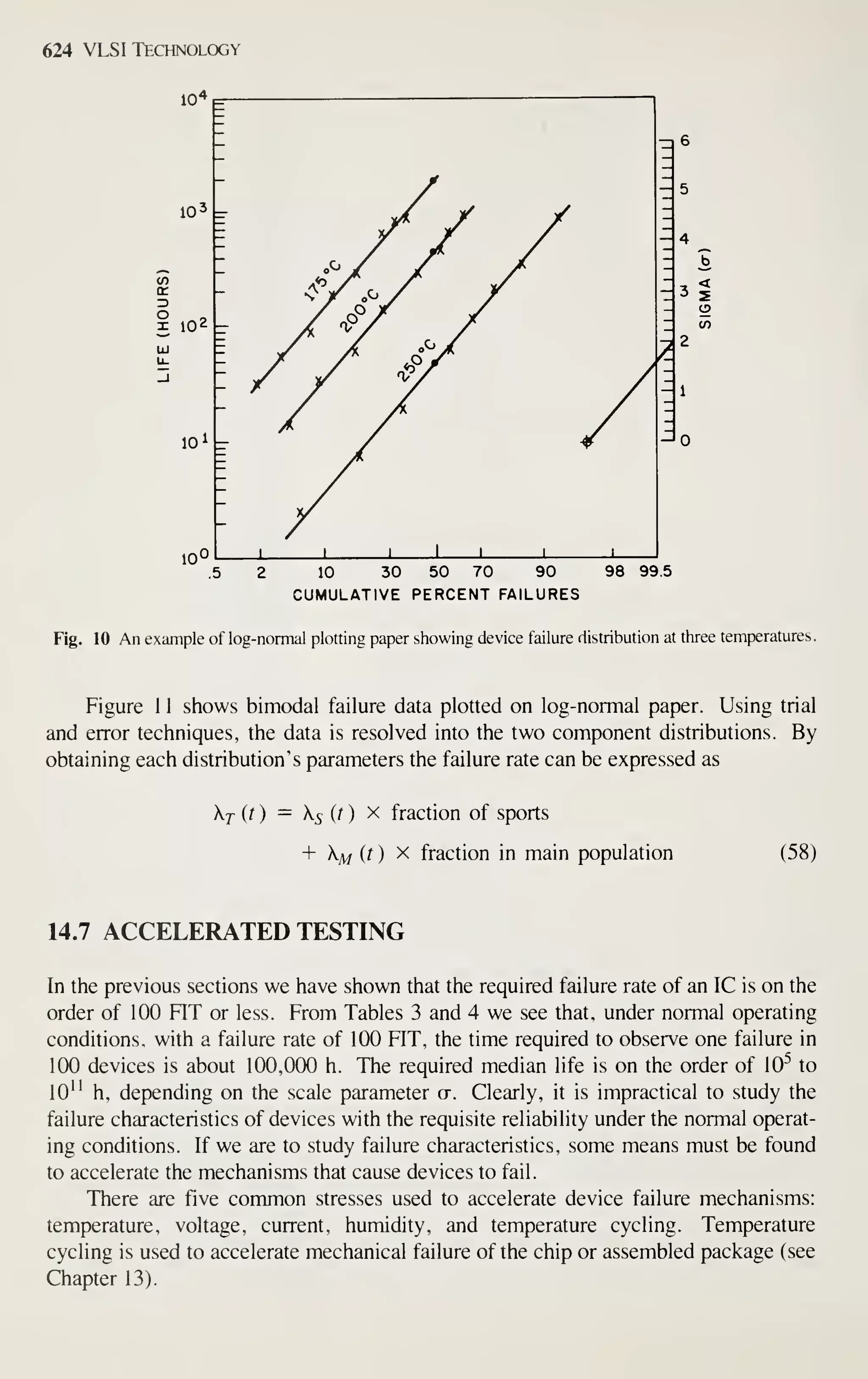

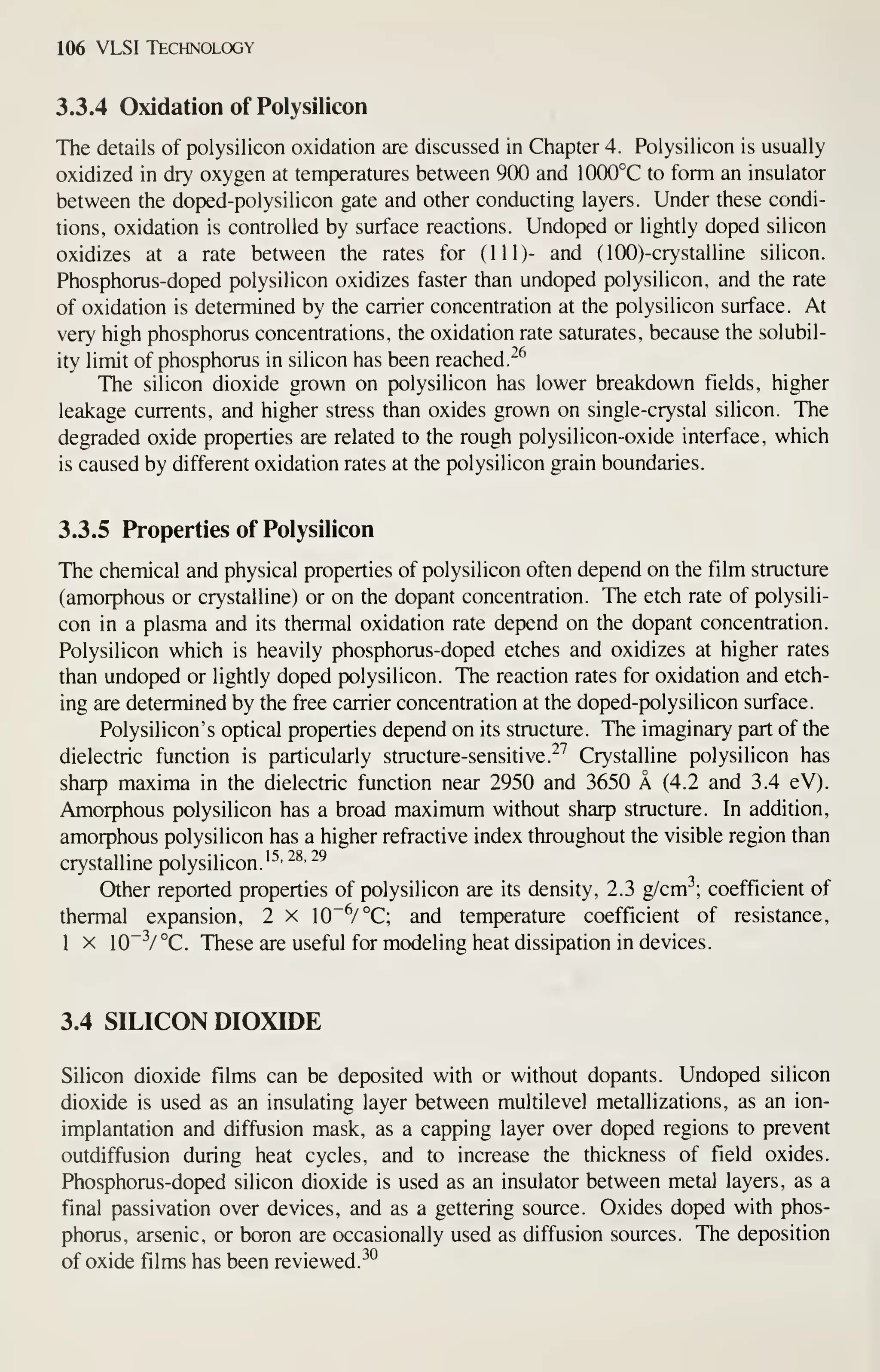

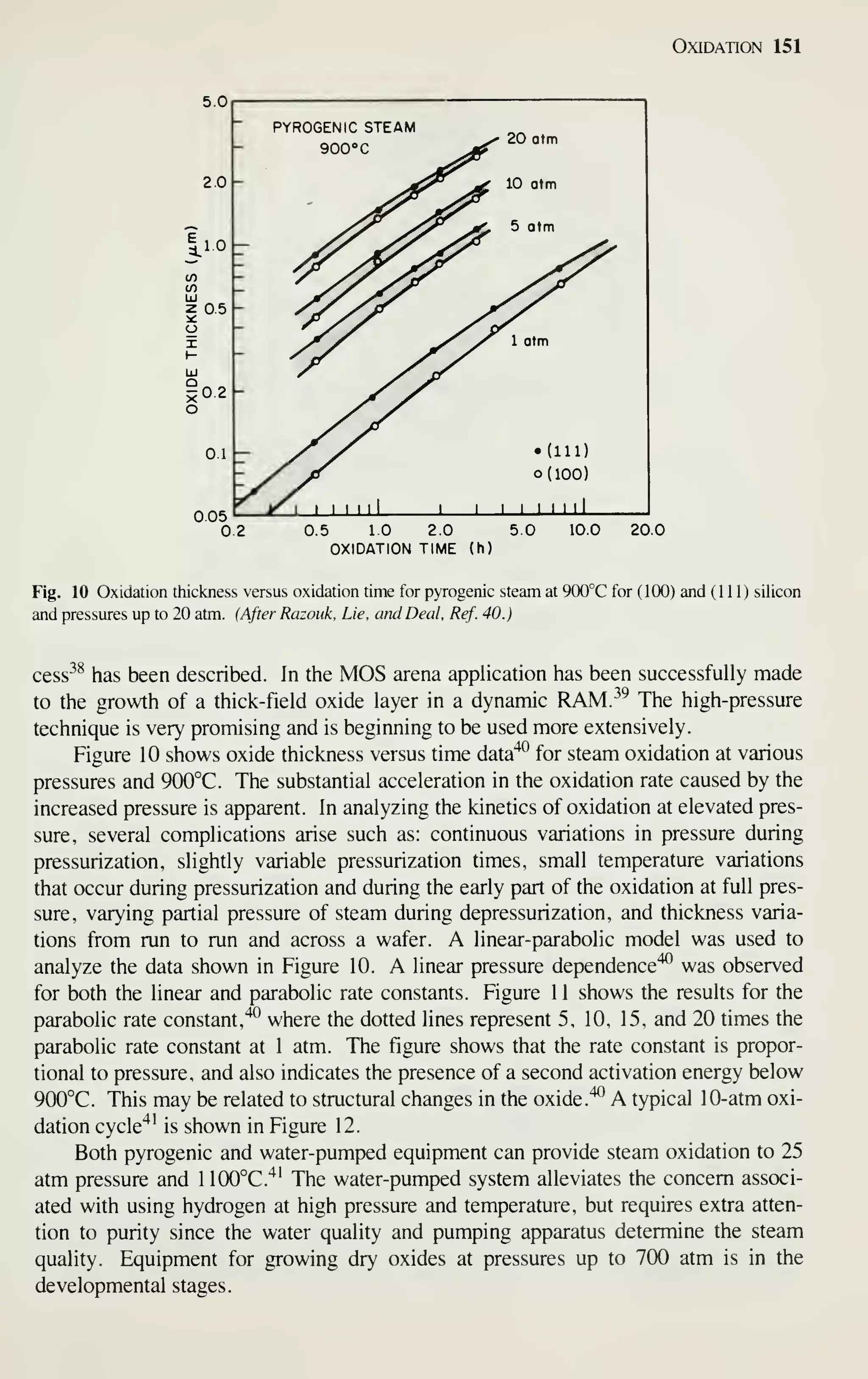

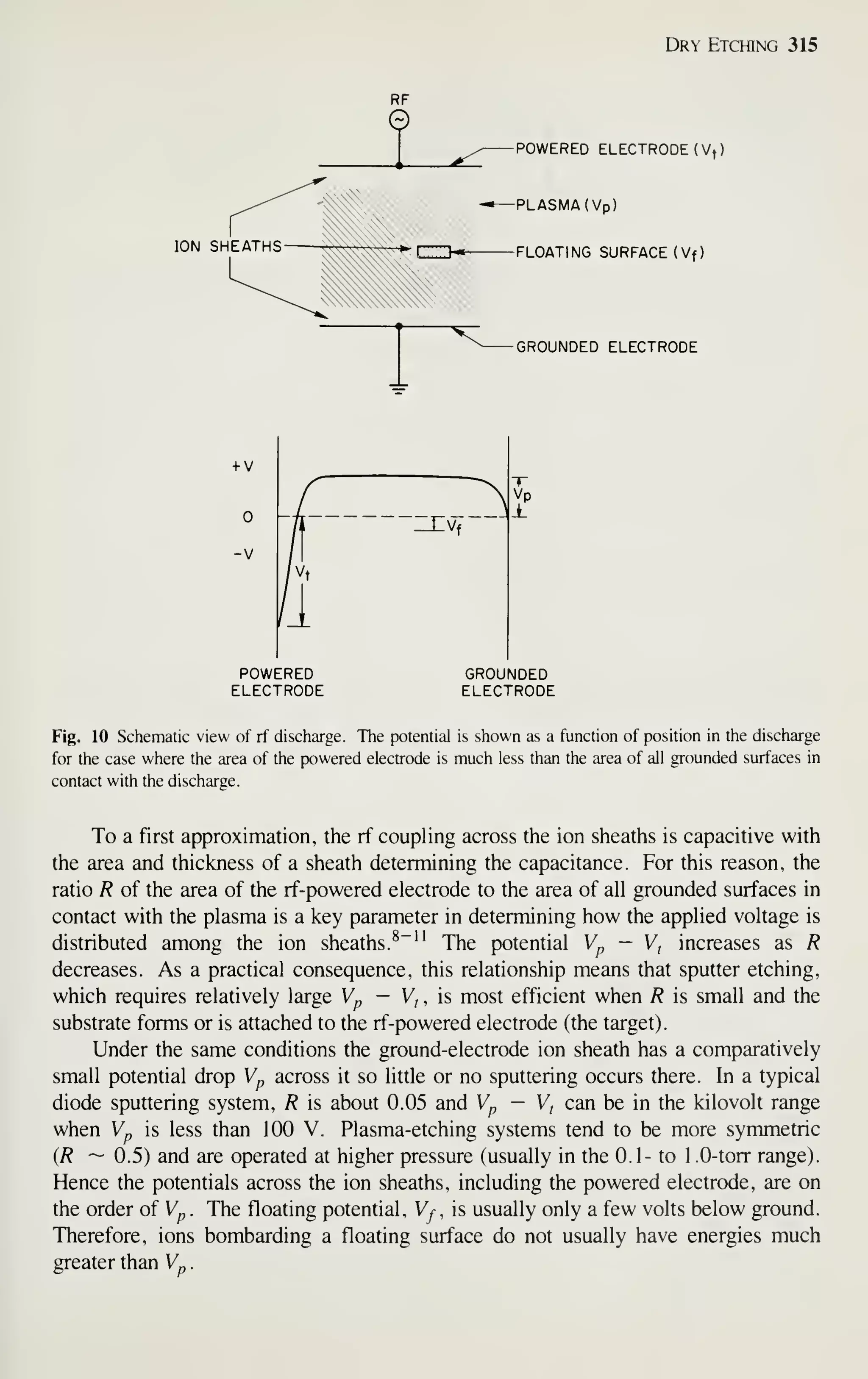

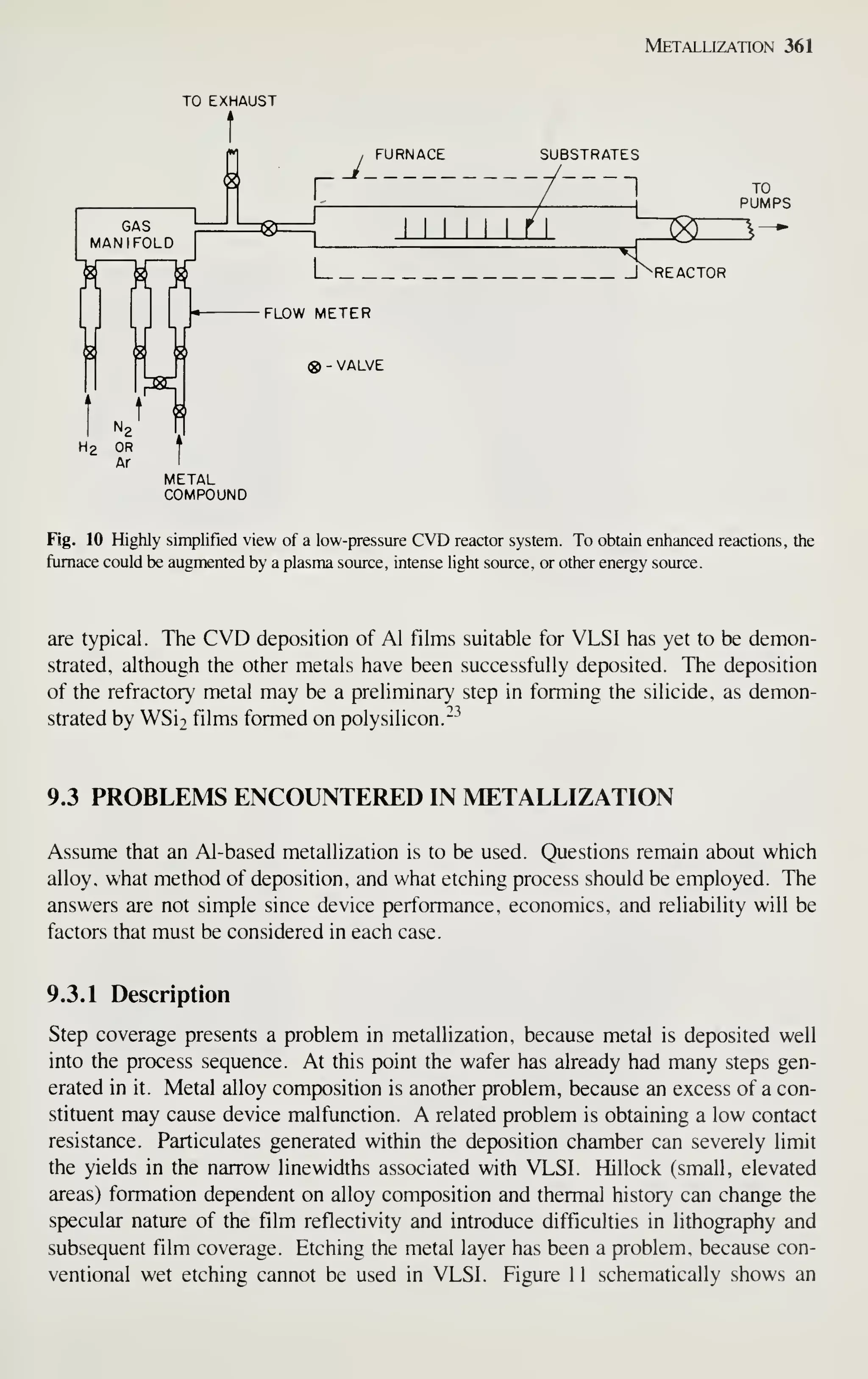

impetuses for such phenomenal market growth are the intrinsic pervasiveness of elec-

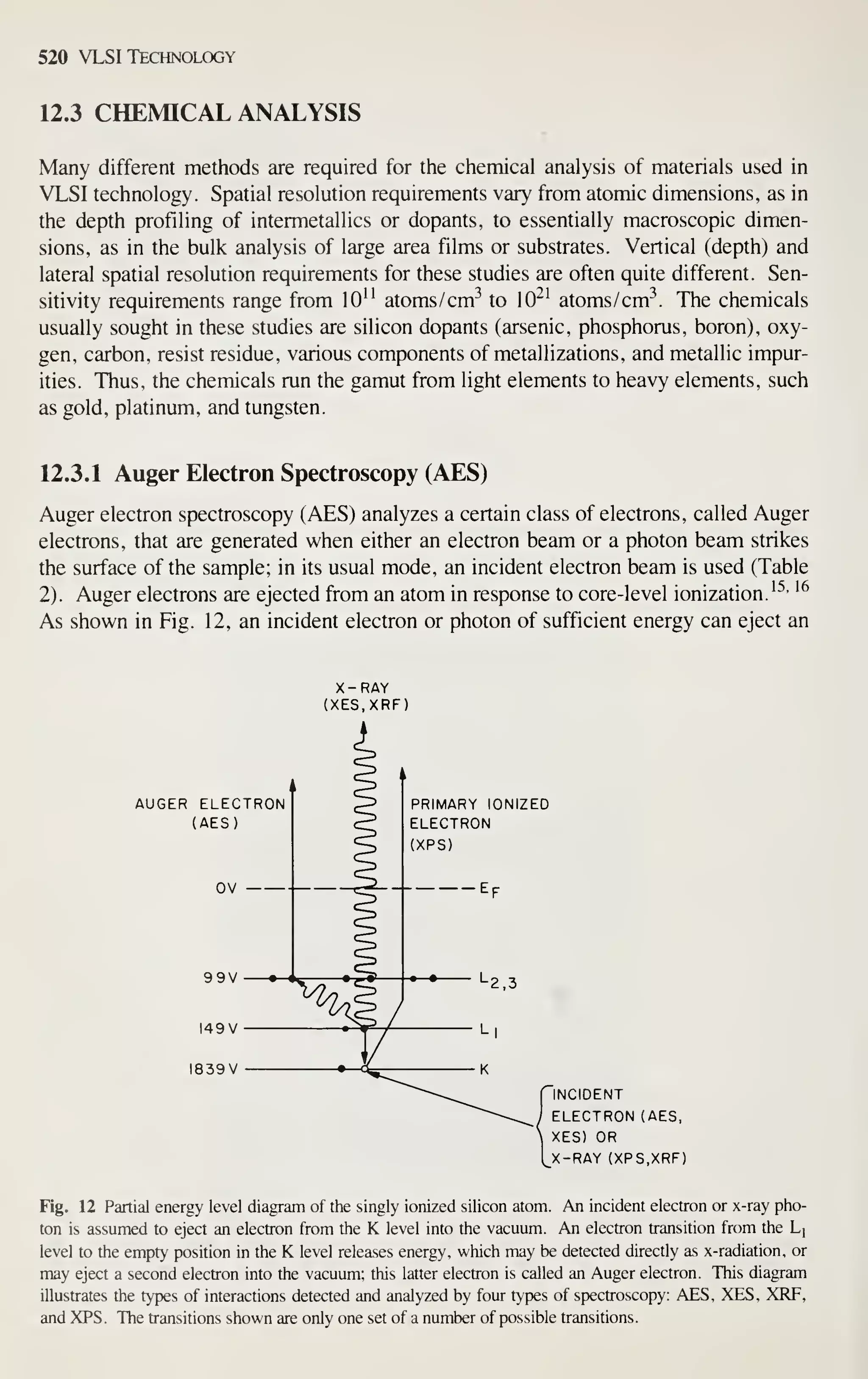

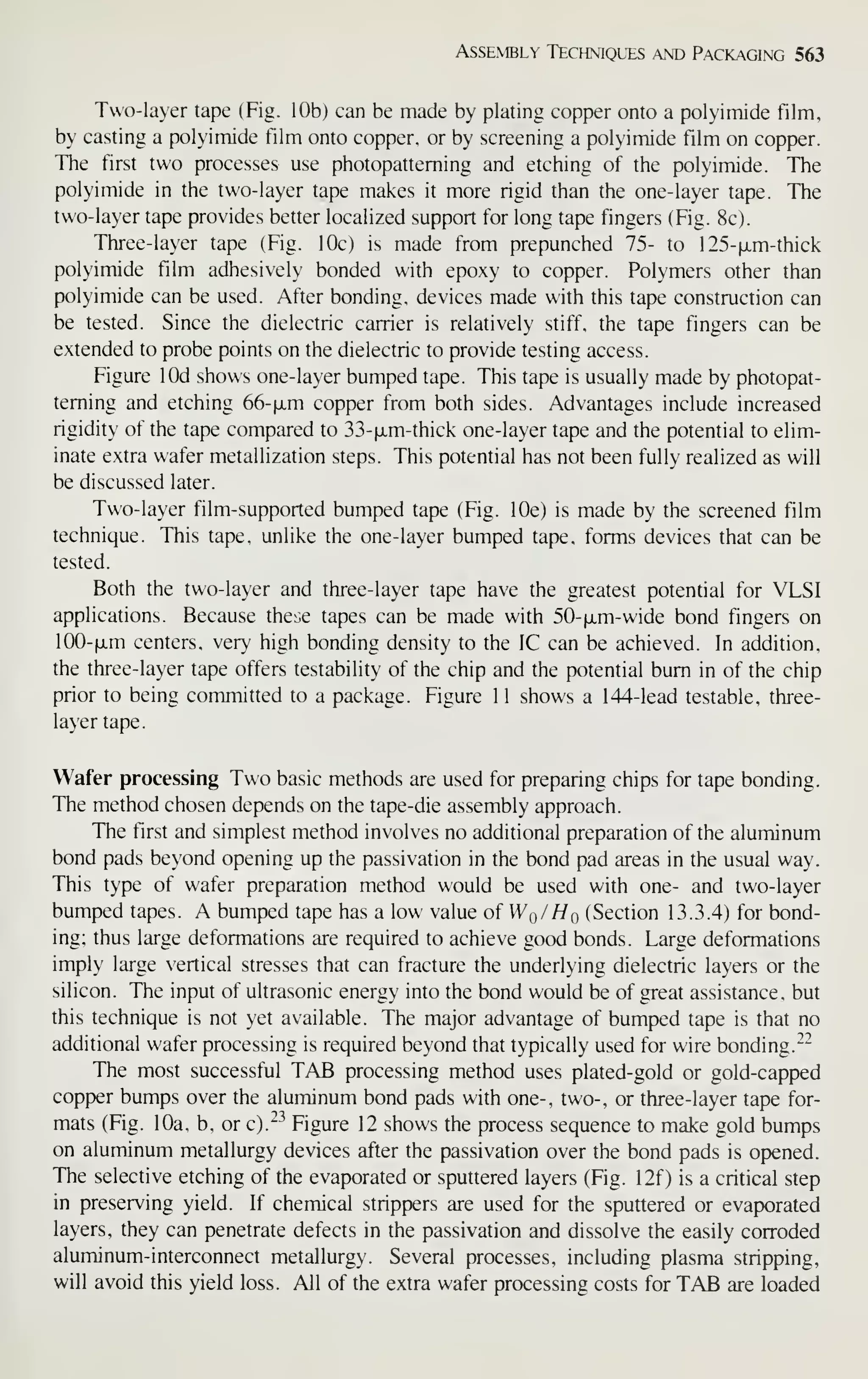

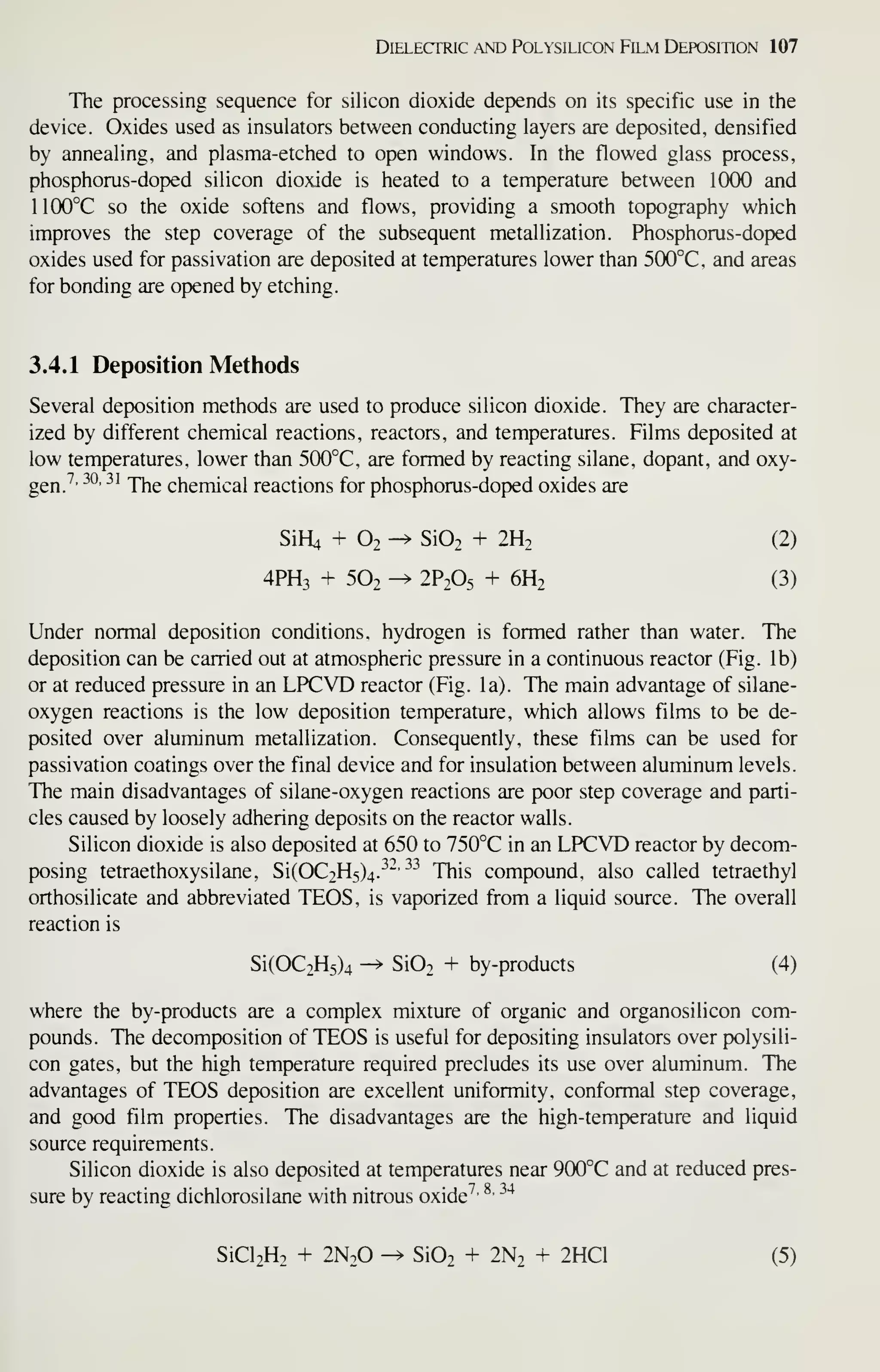

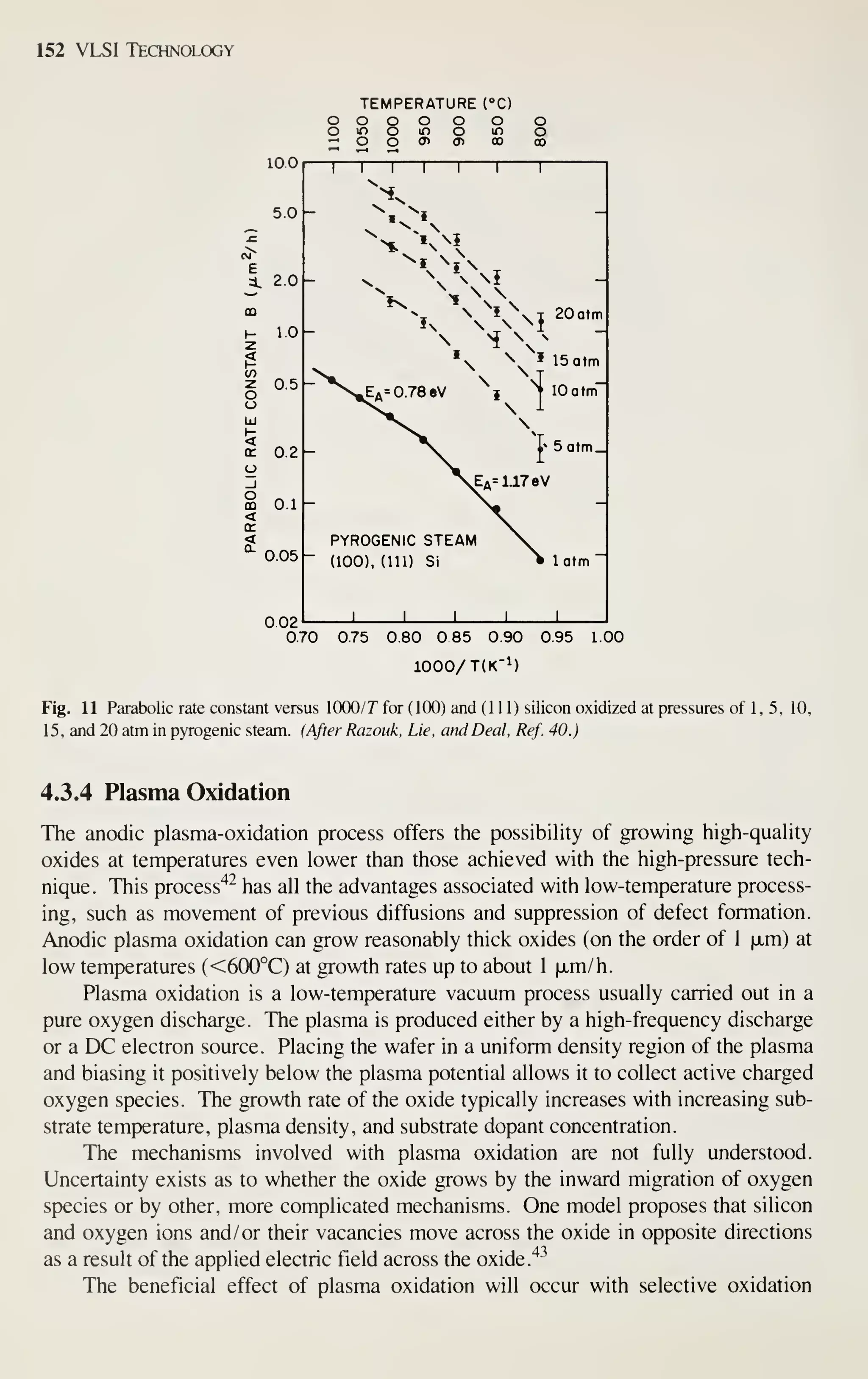

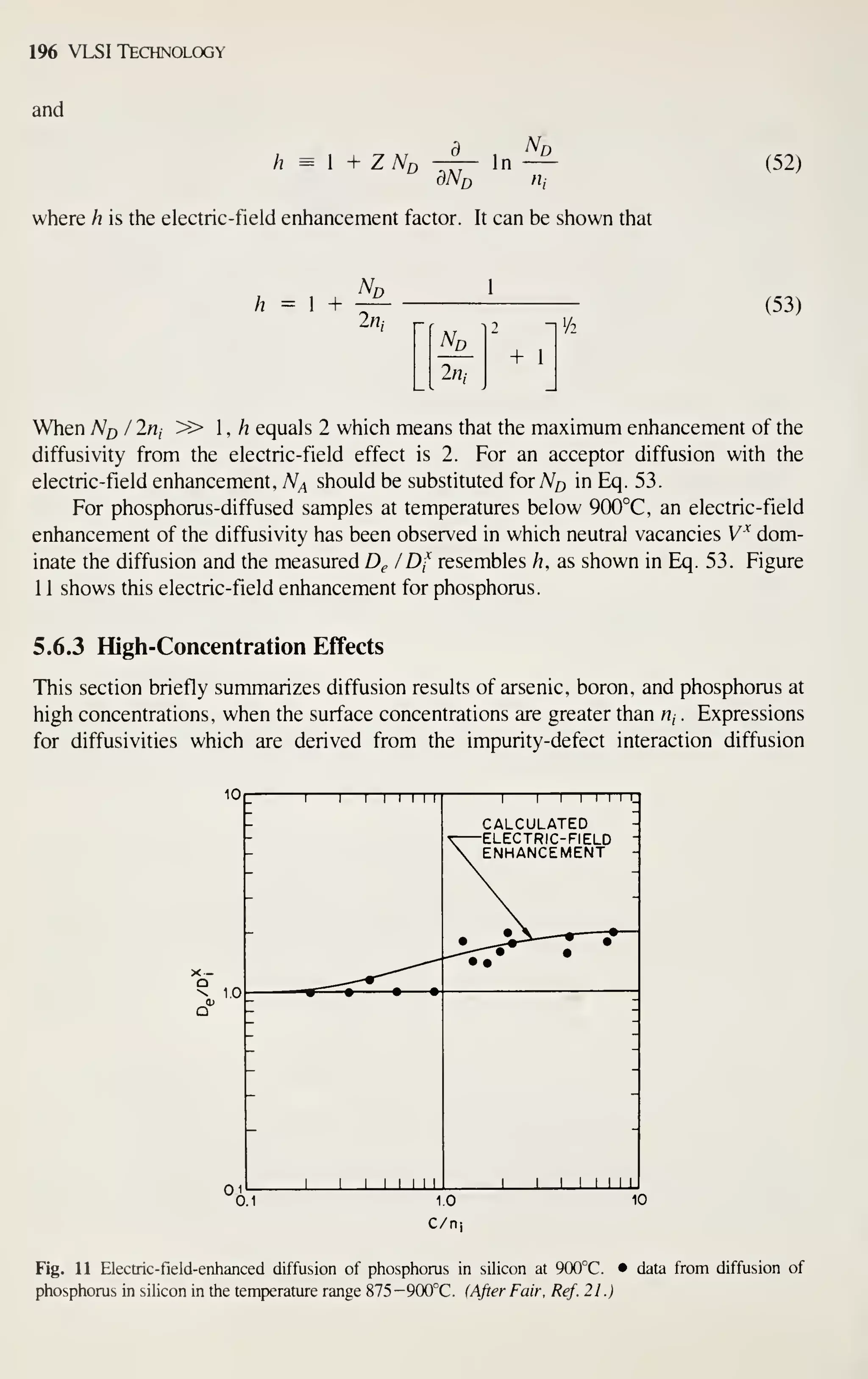

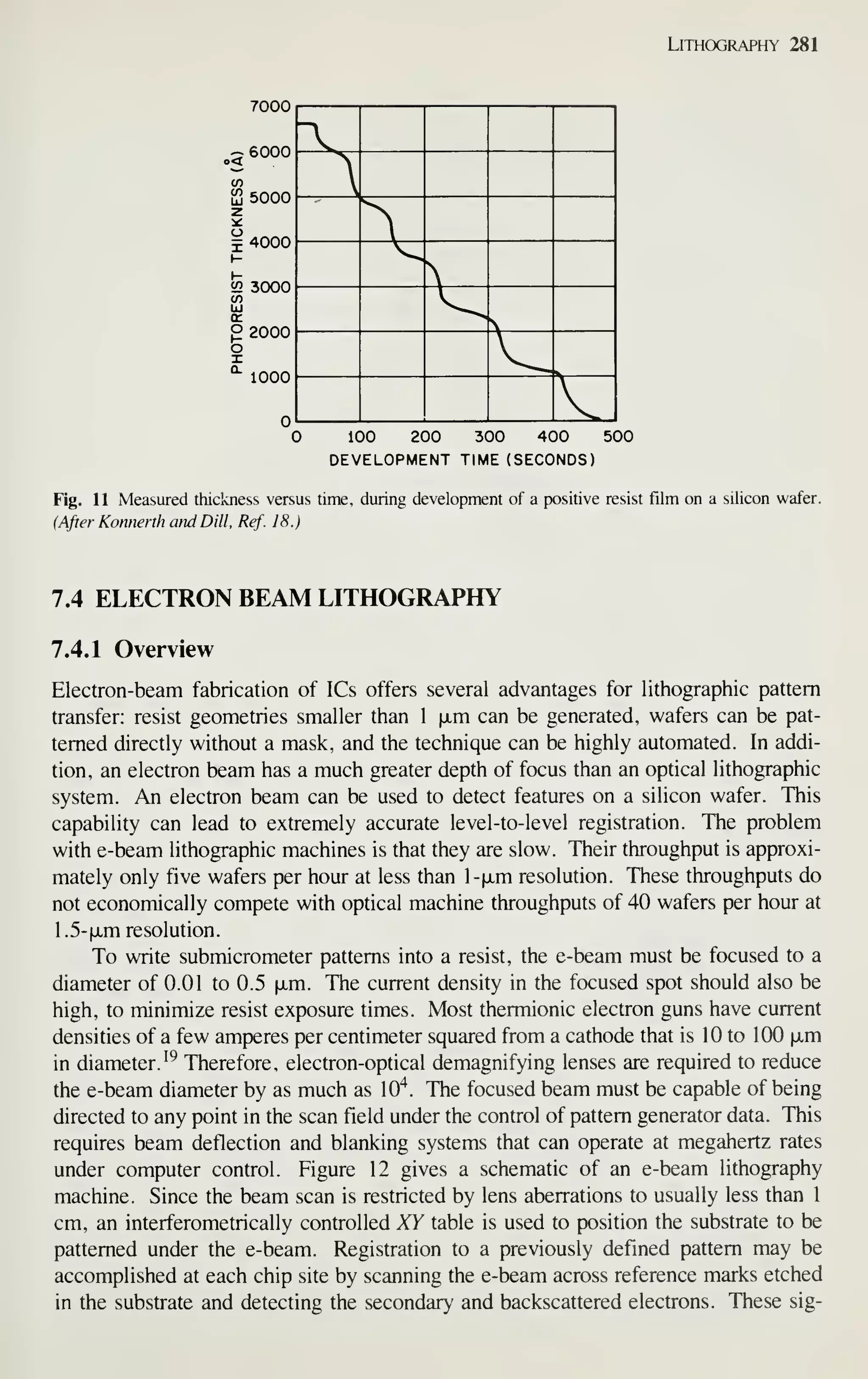

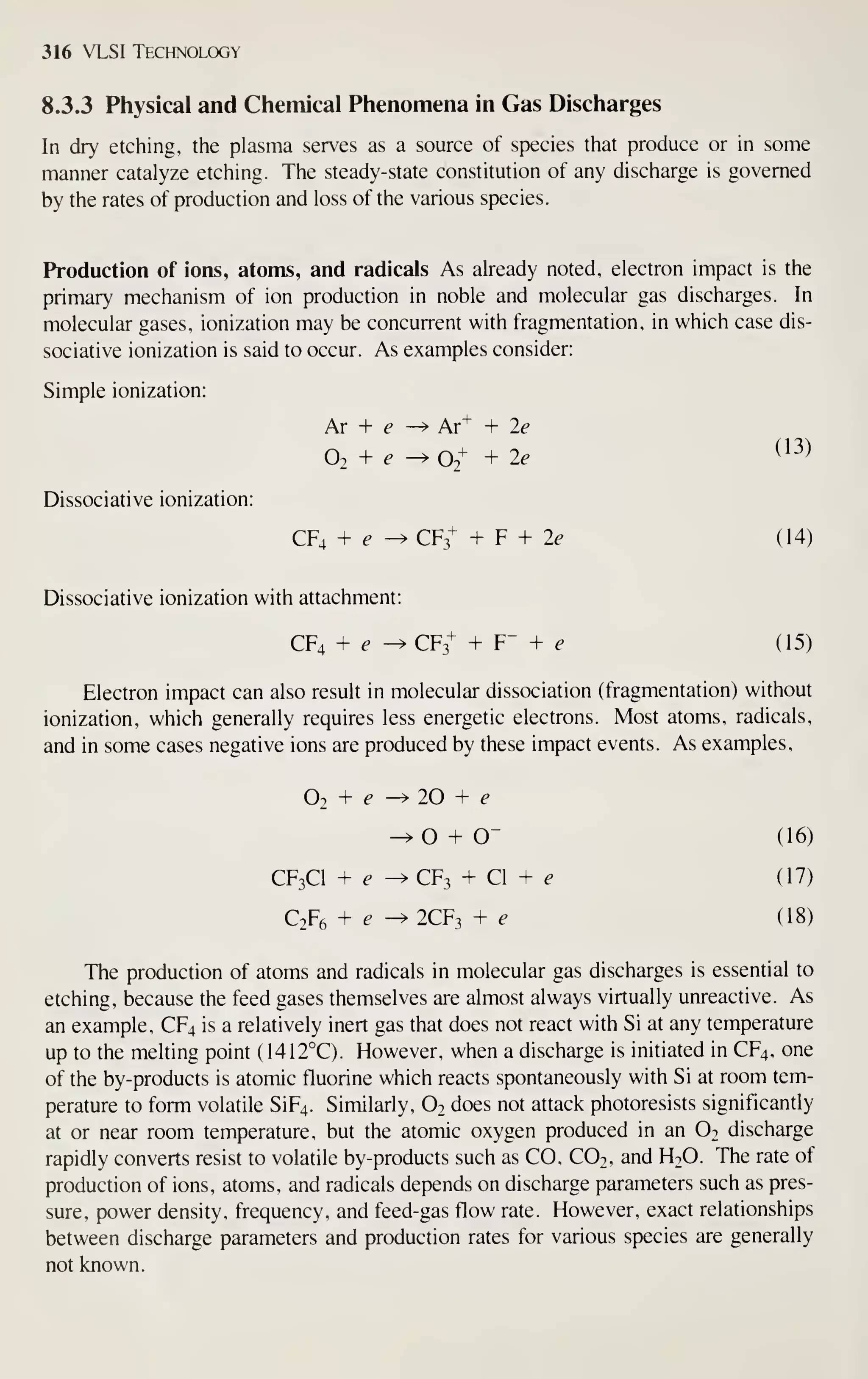

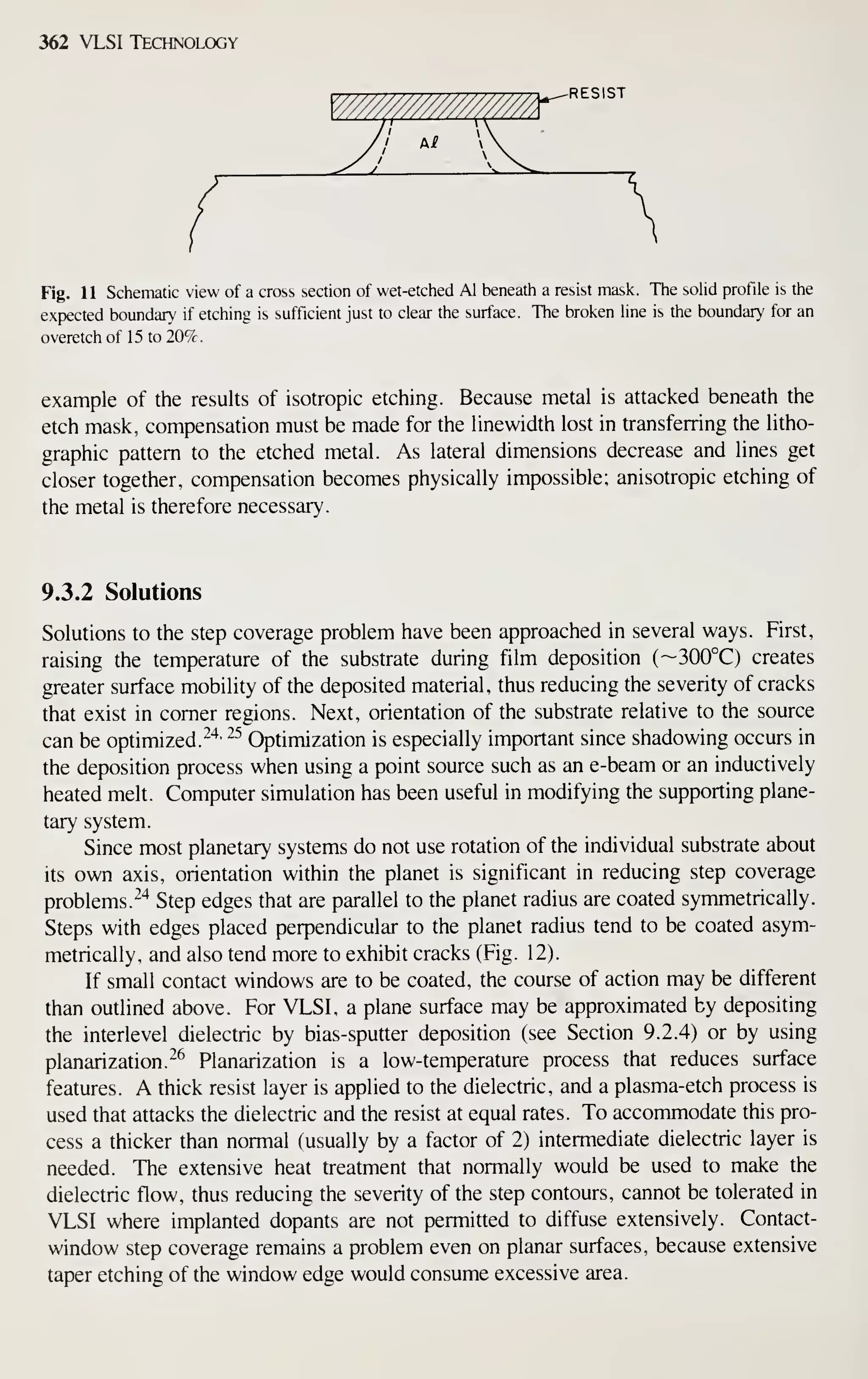

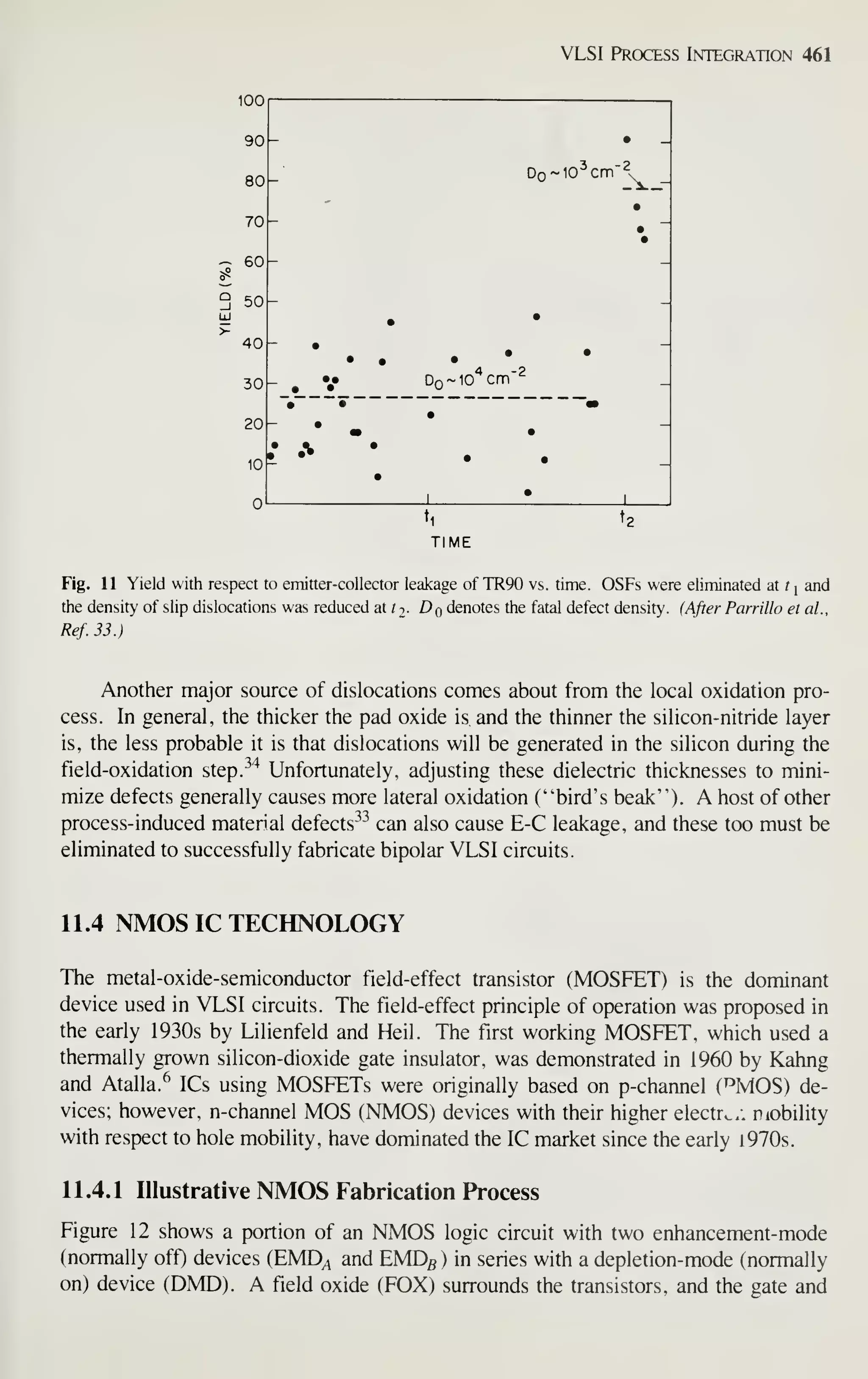

tronic products and the continued technological breakthroughs in integrated circuits.

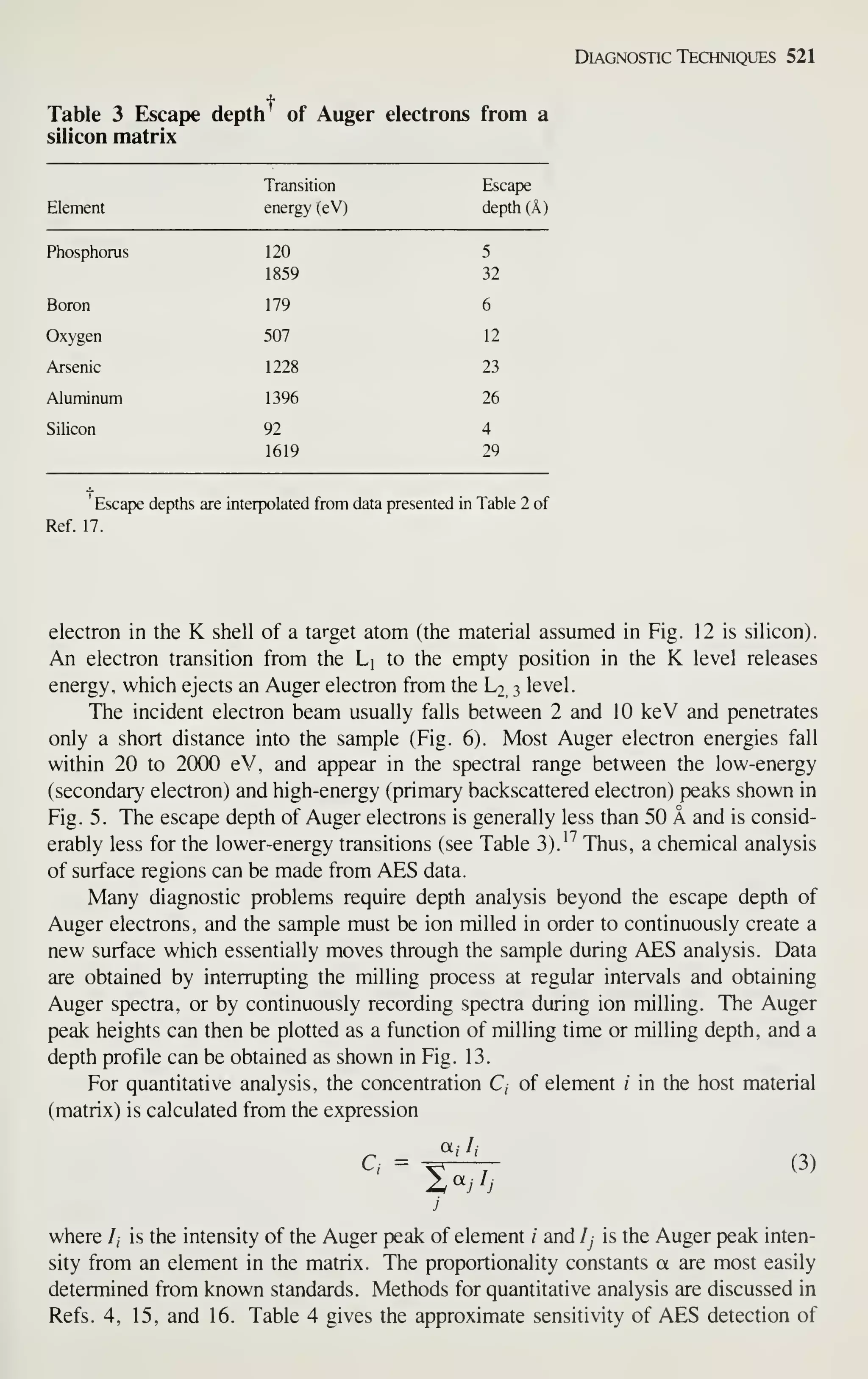

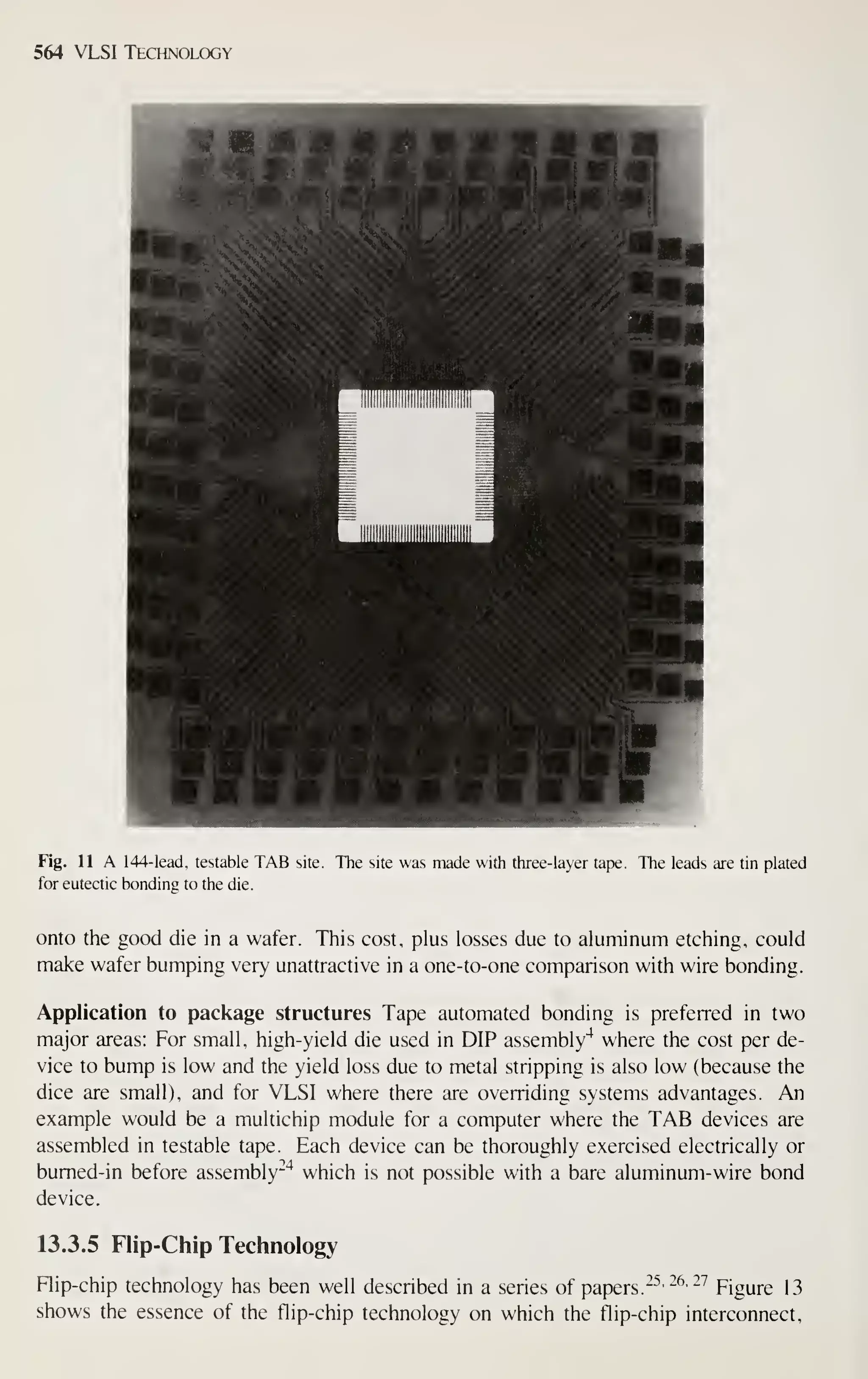

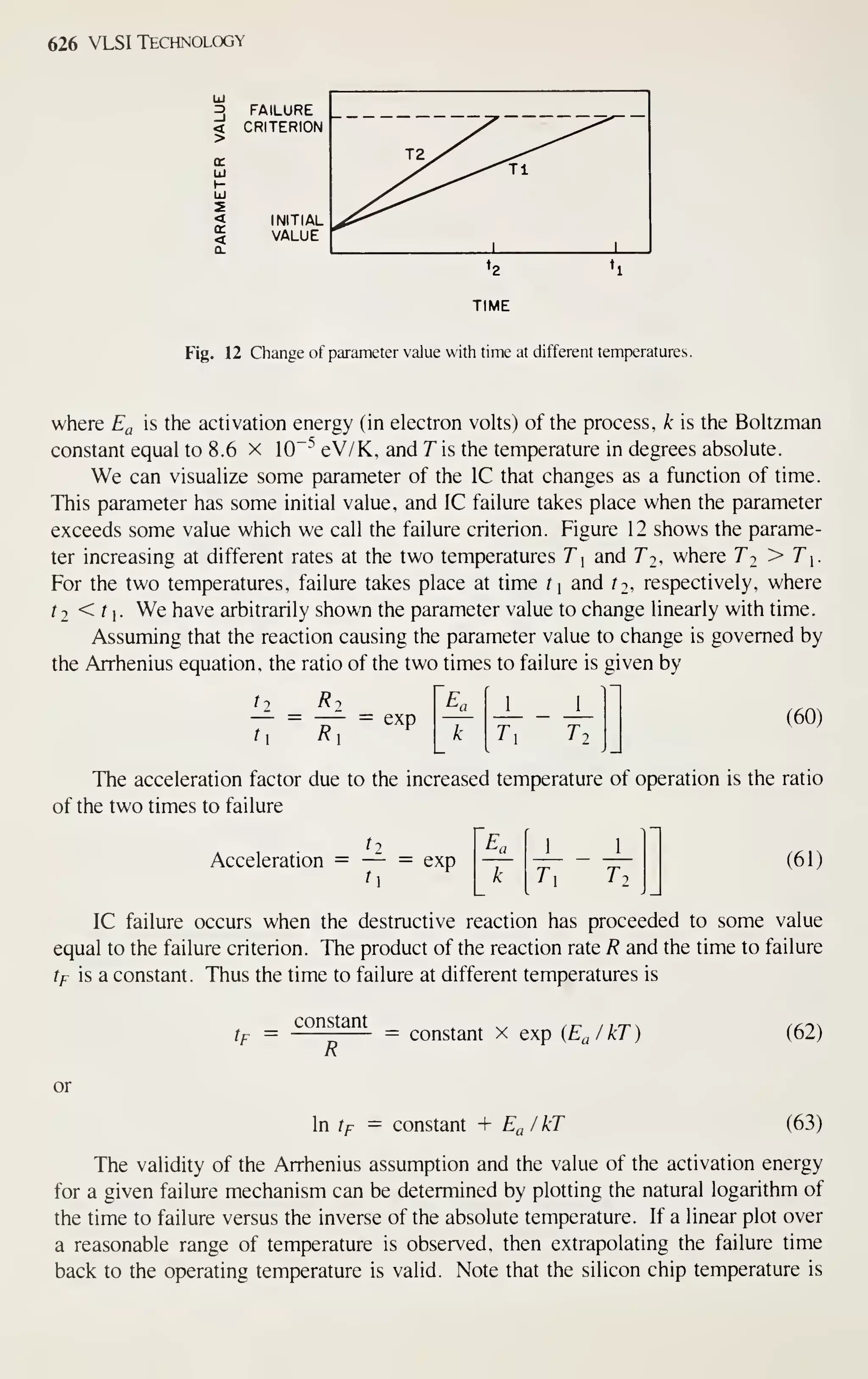

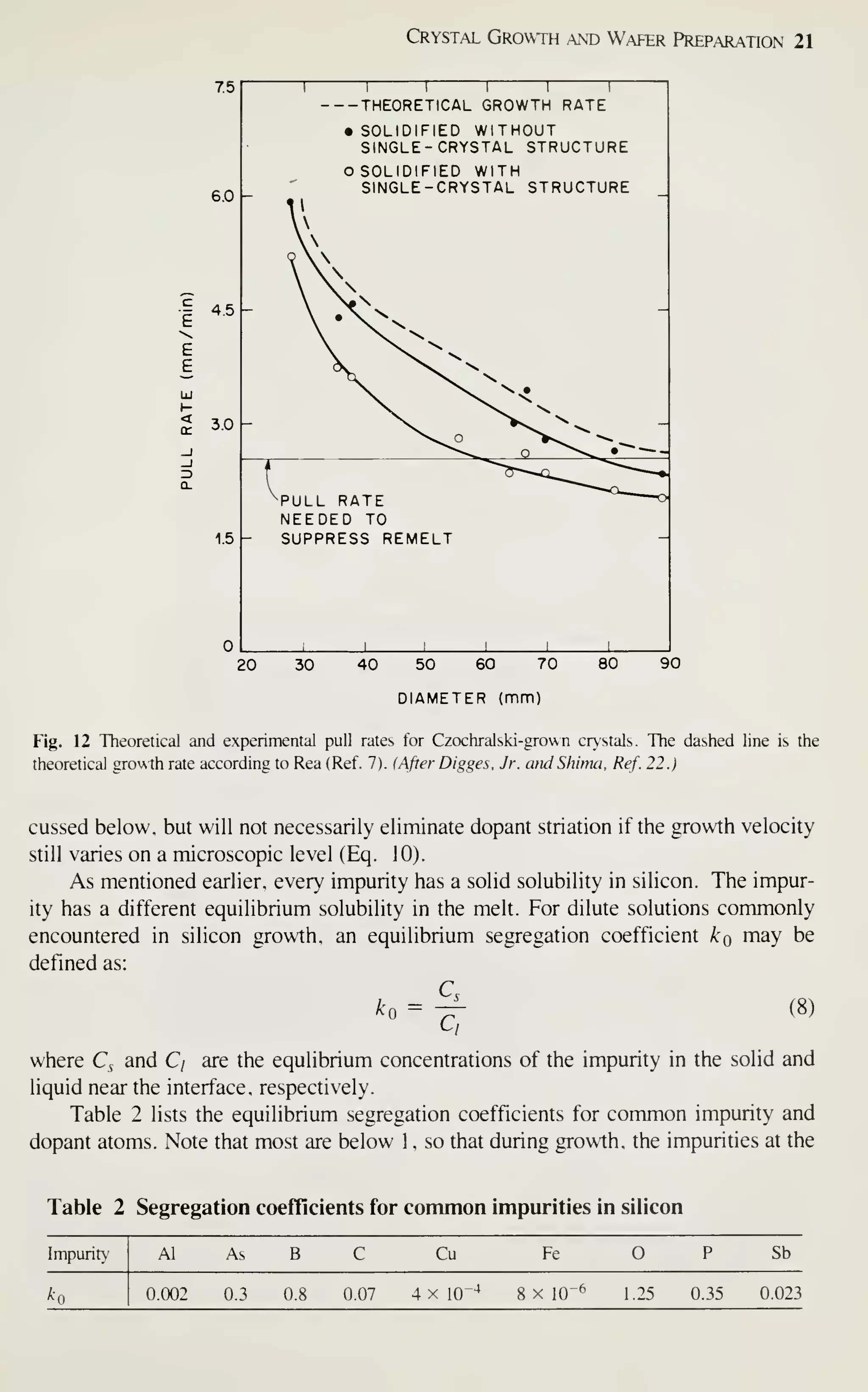

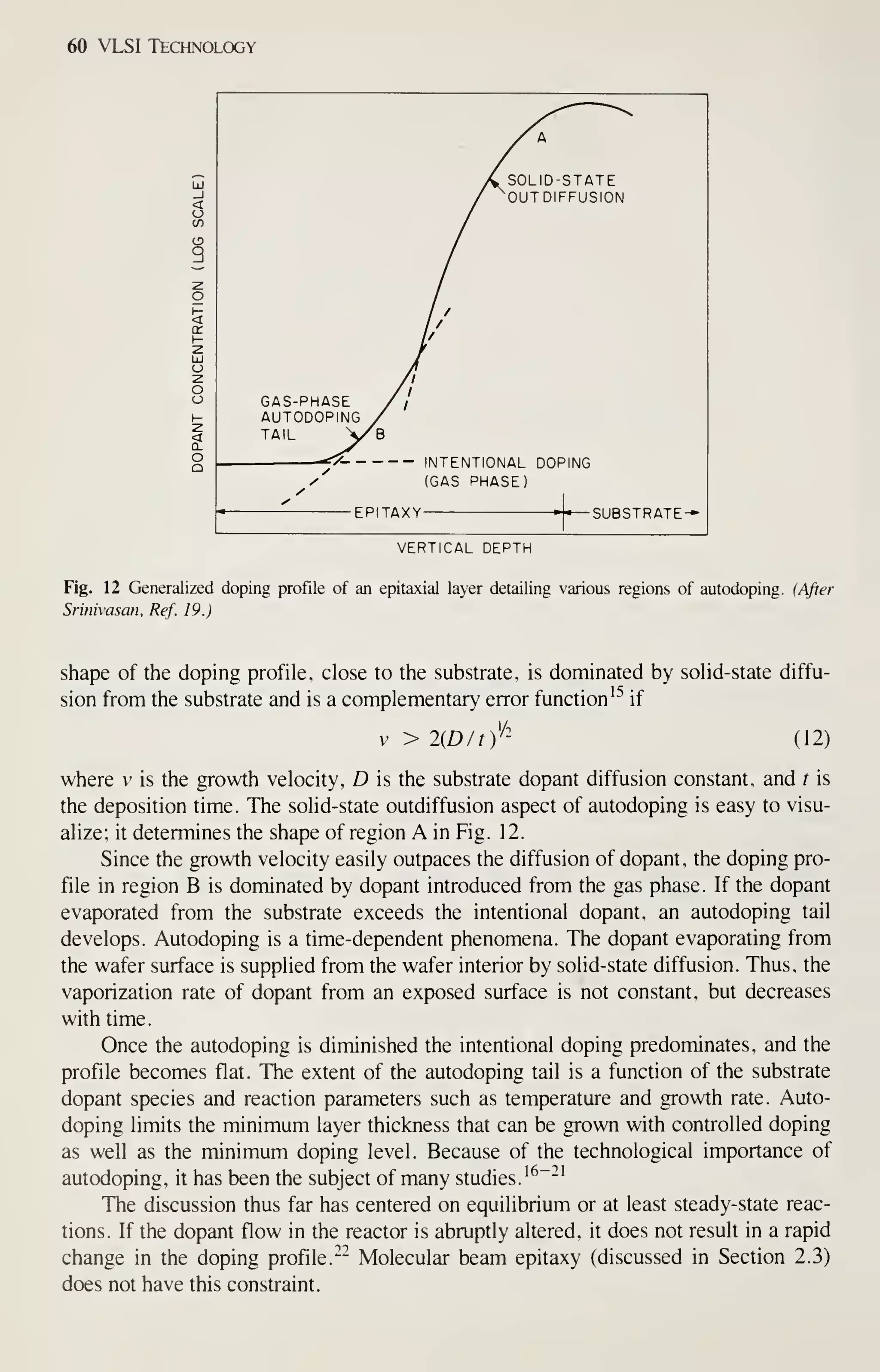

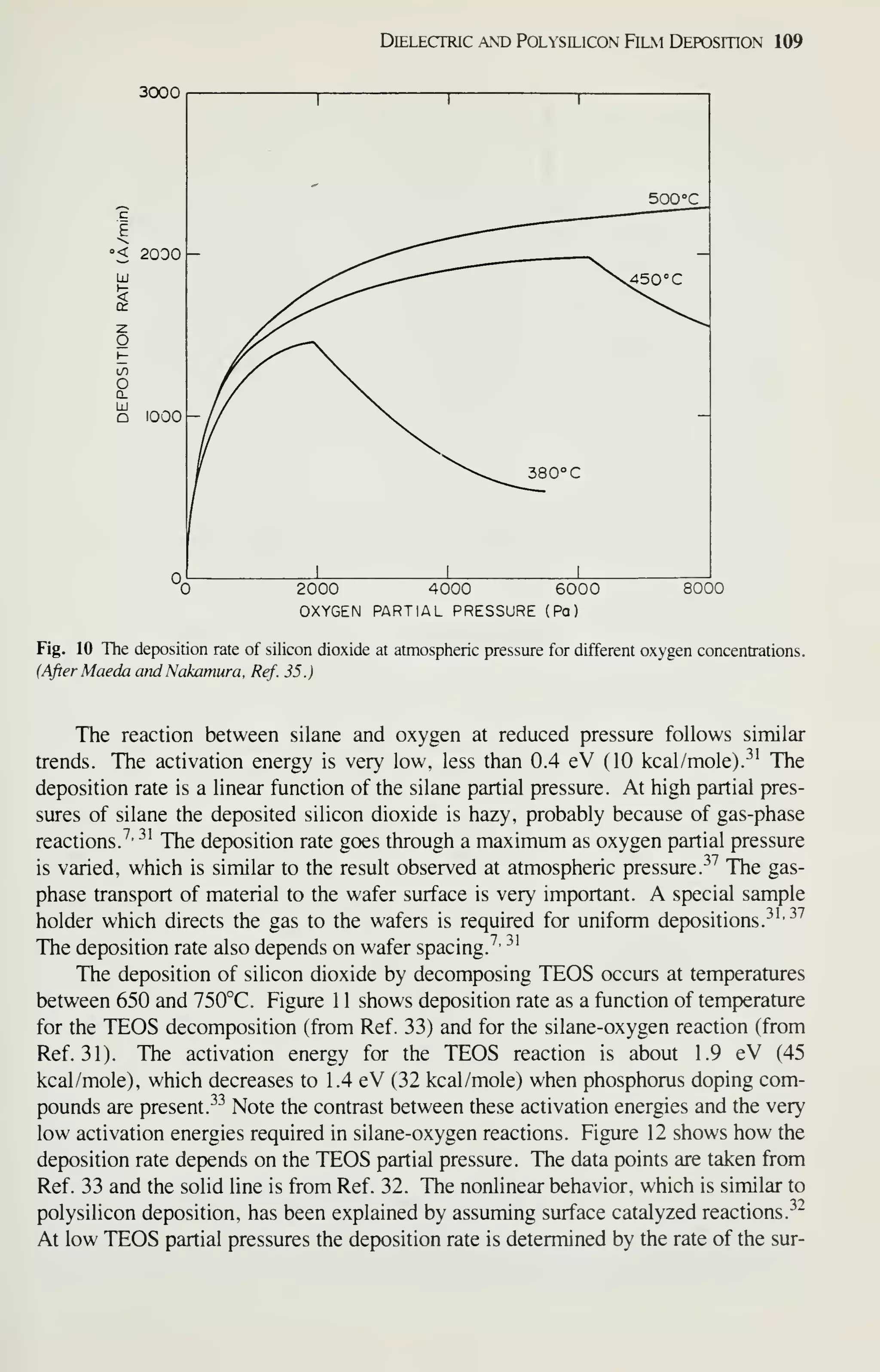

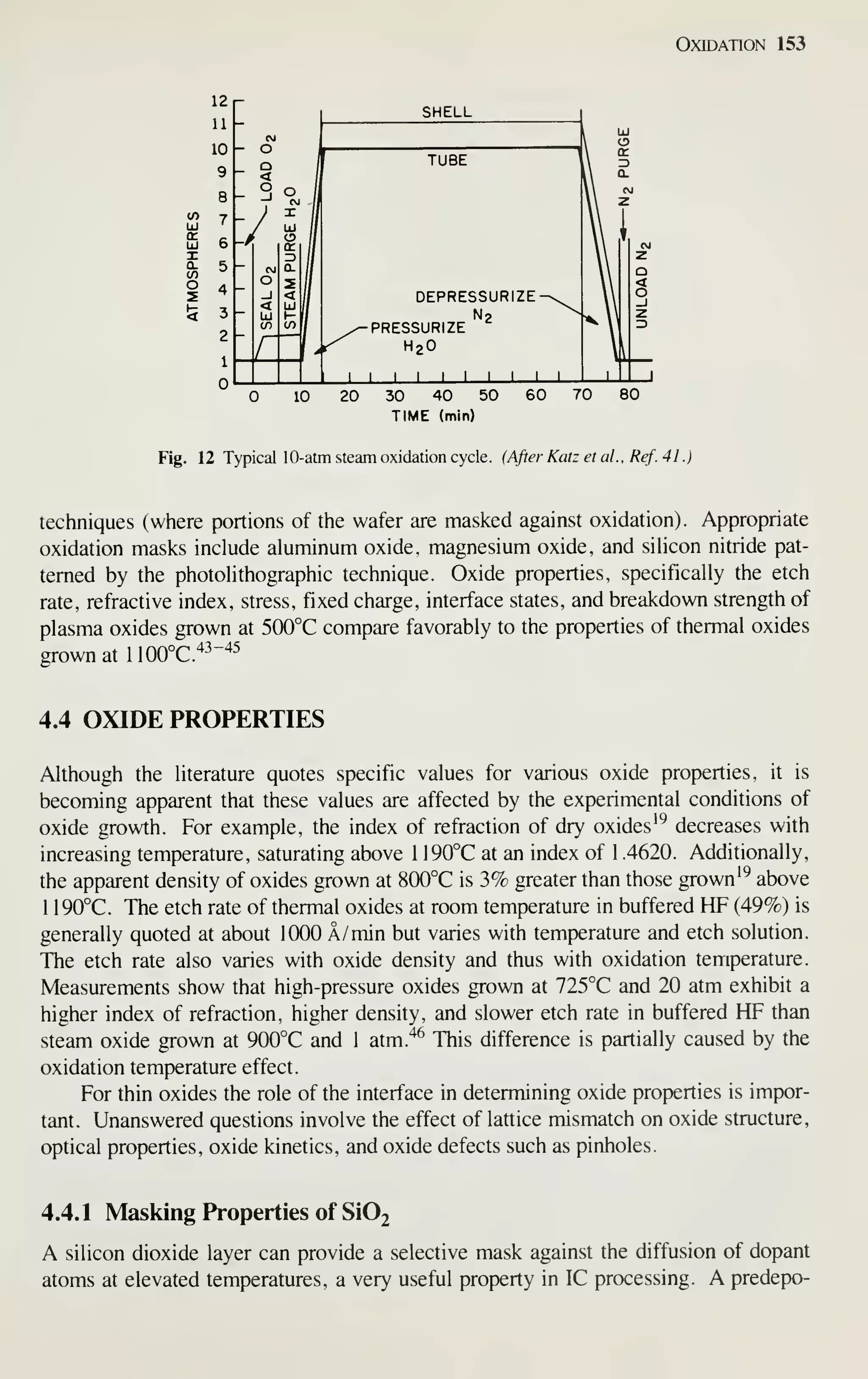

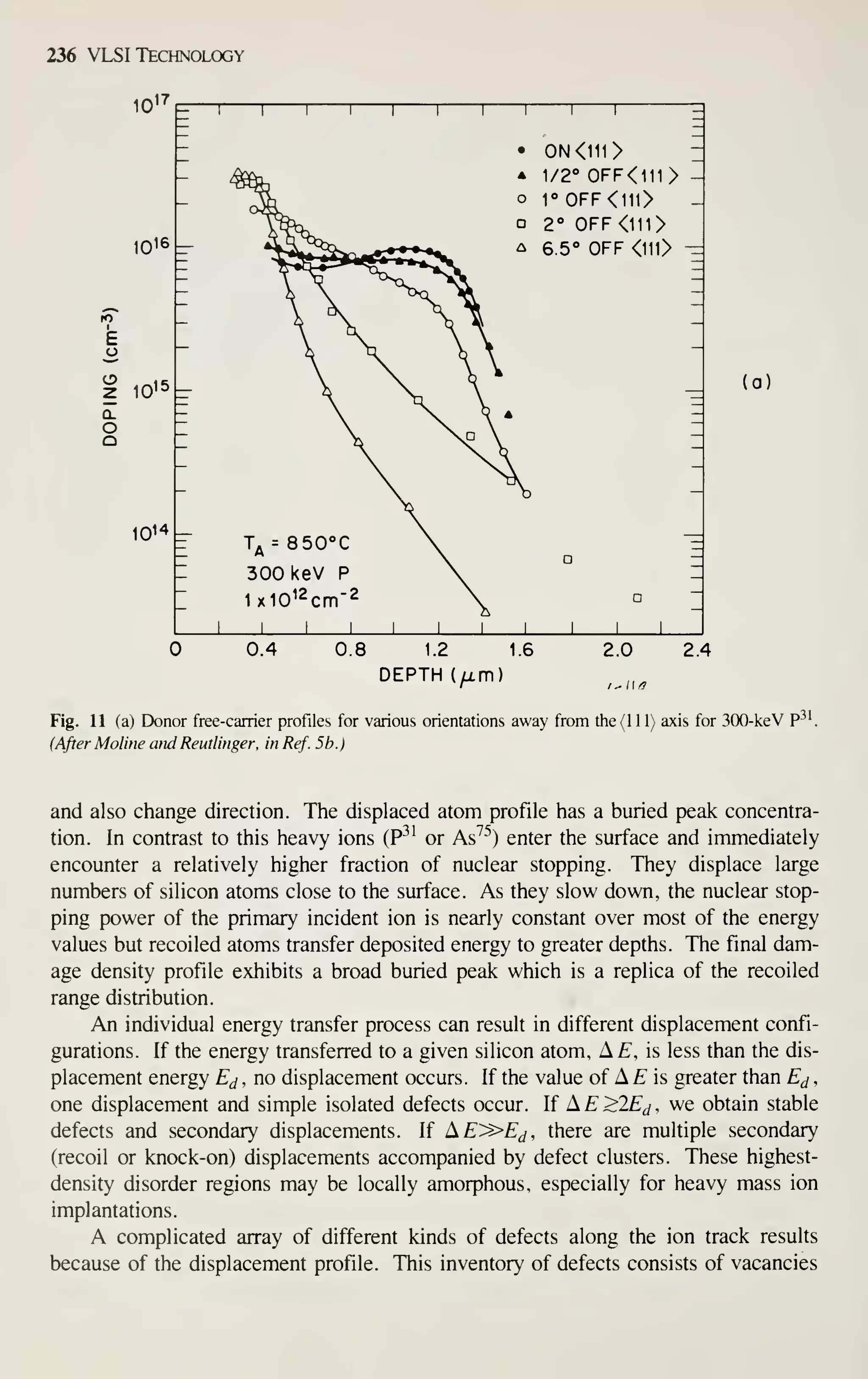

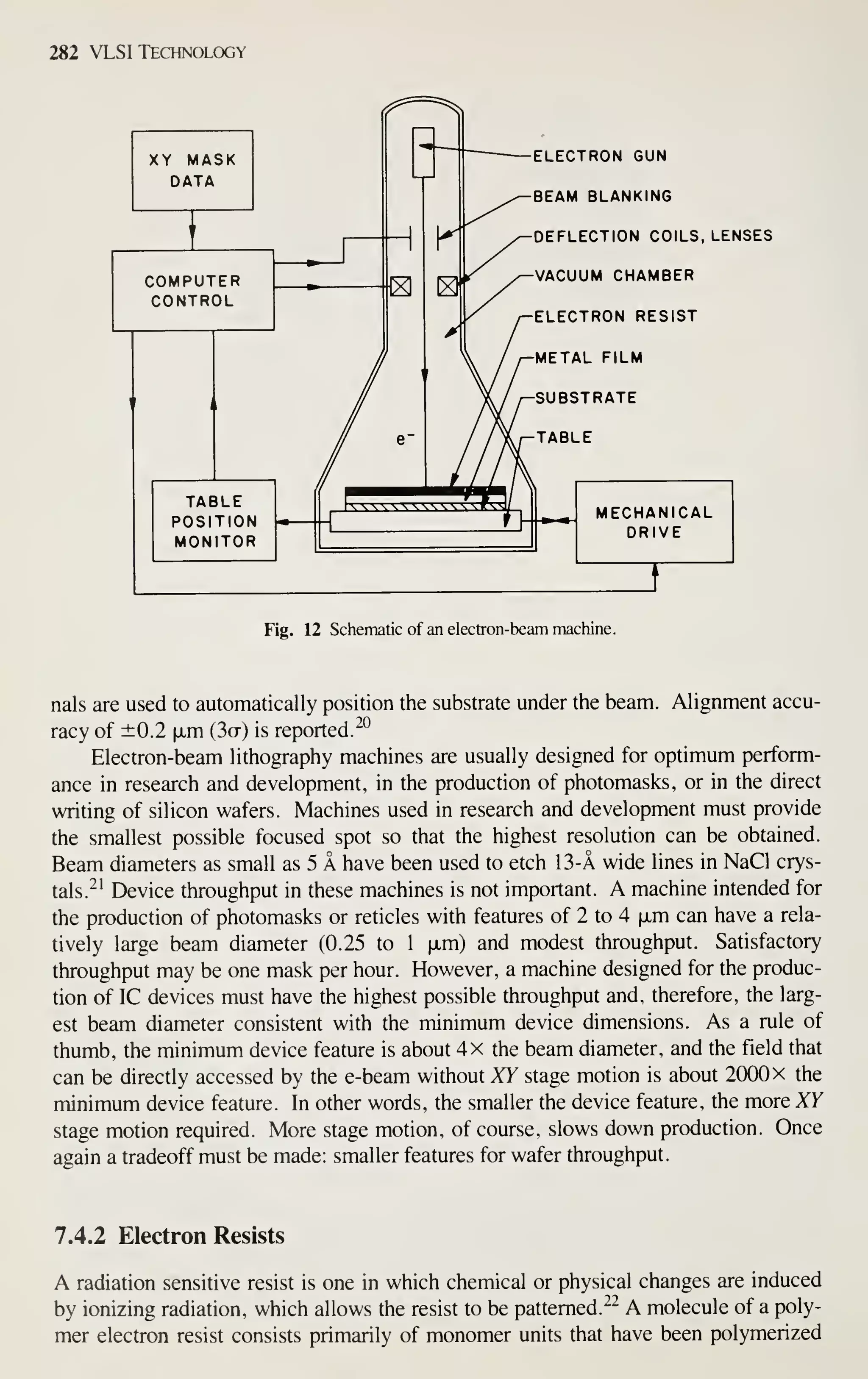

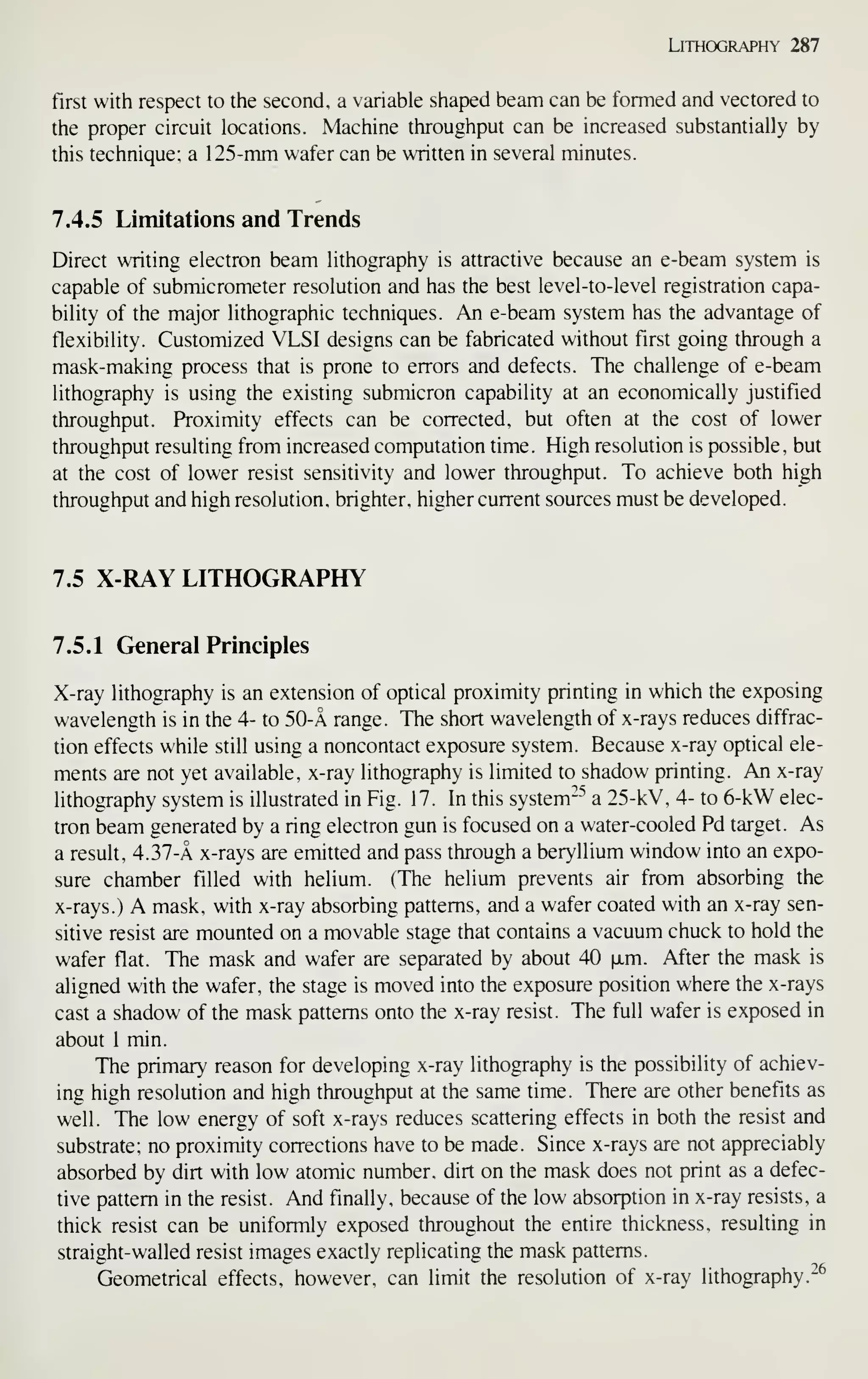

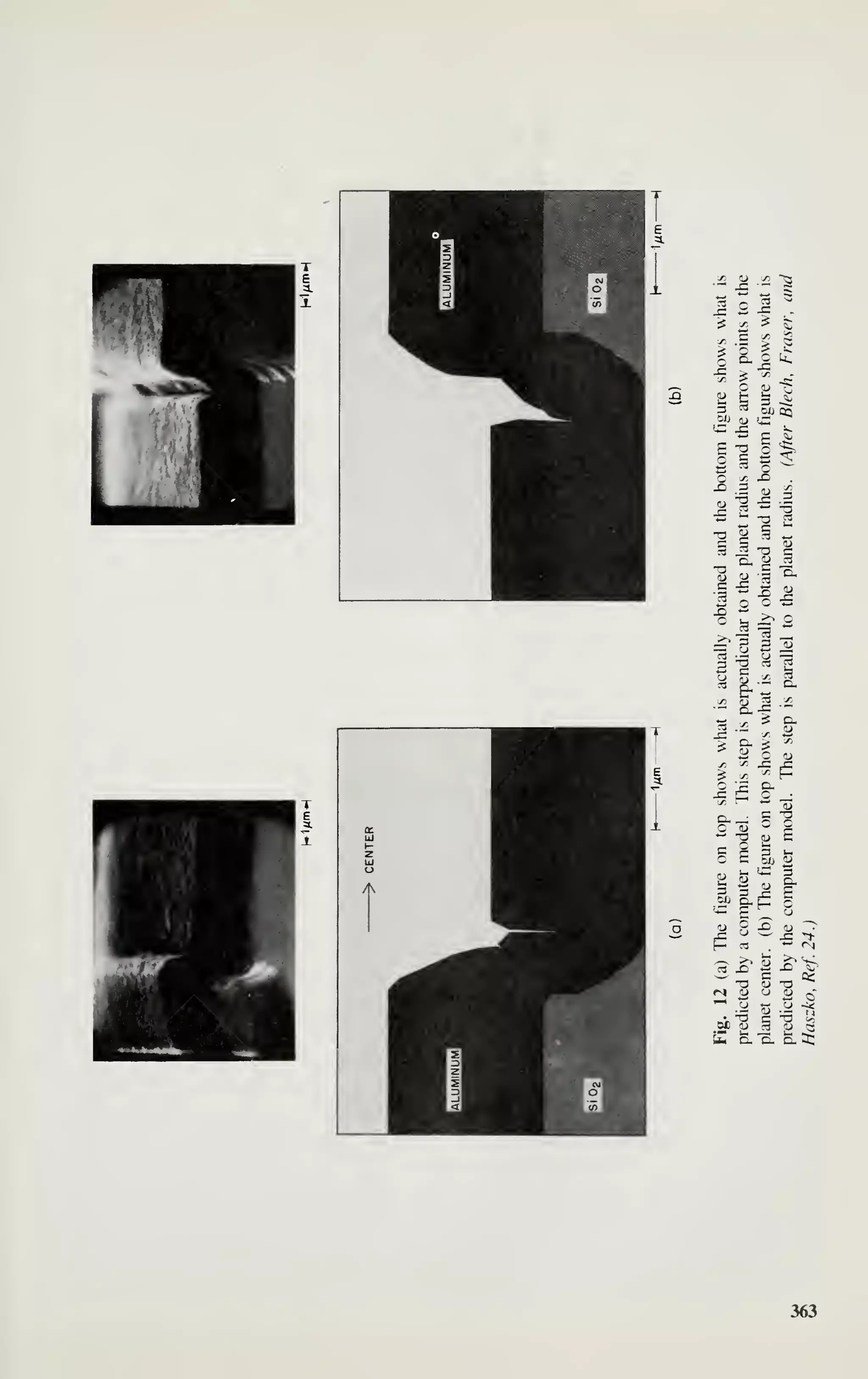

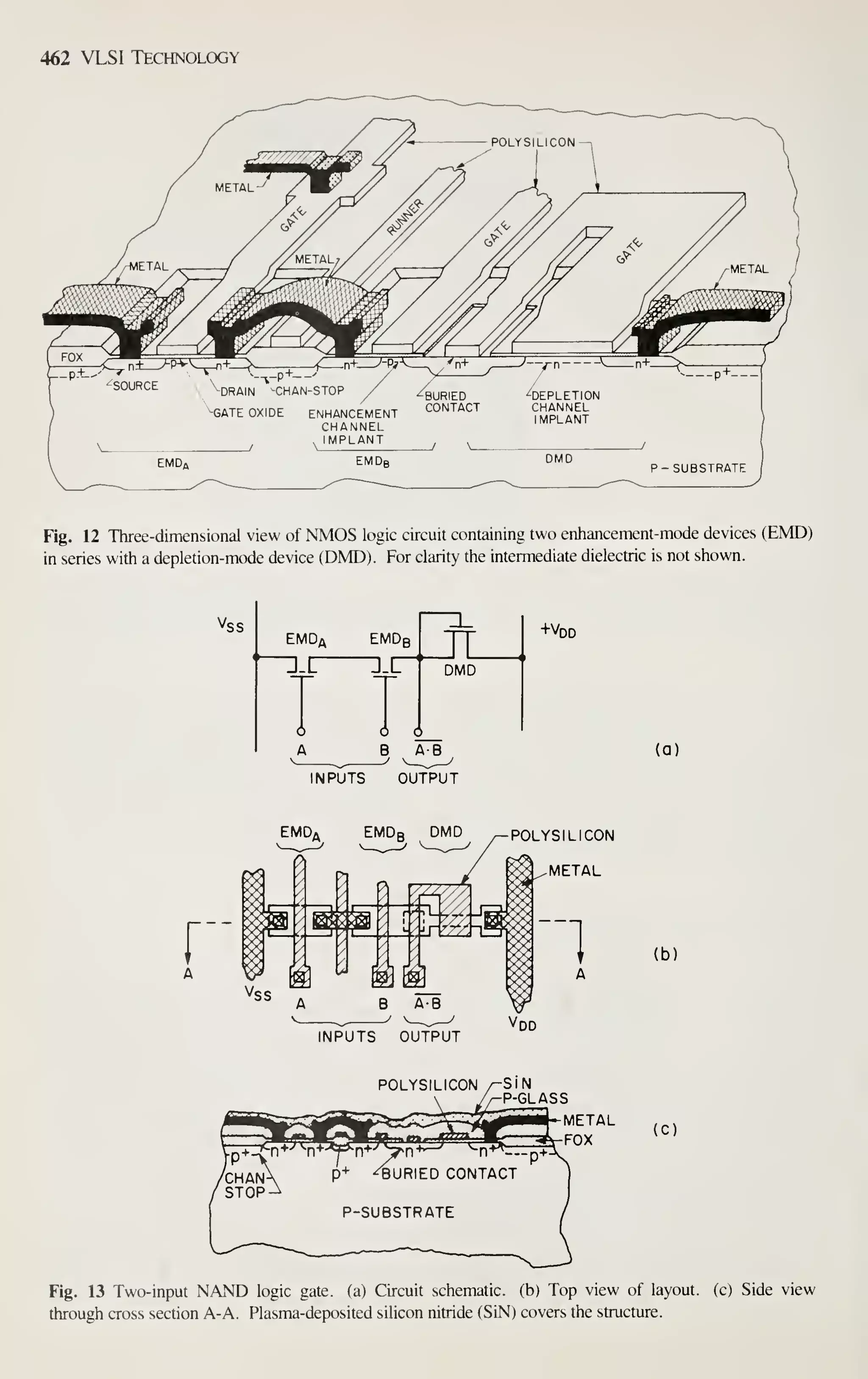

The world market of electronics (about twice the size of the US market) will grow at a

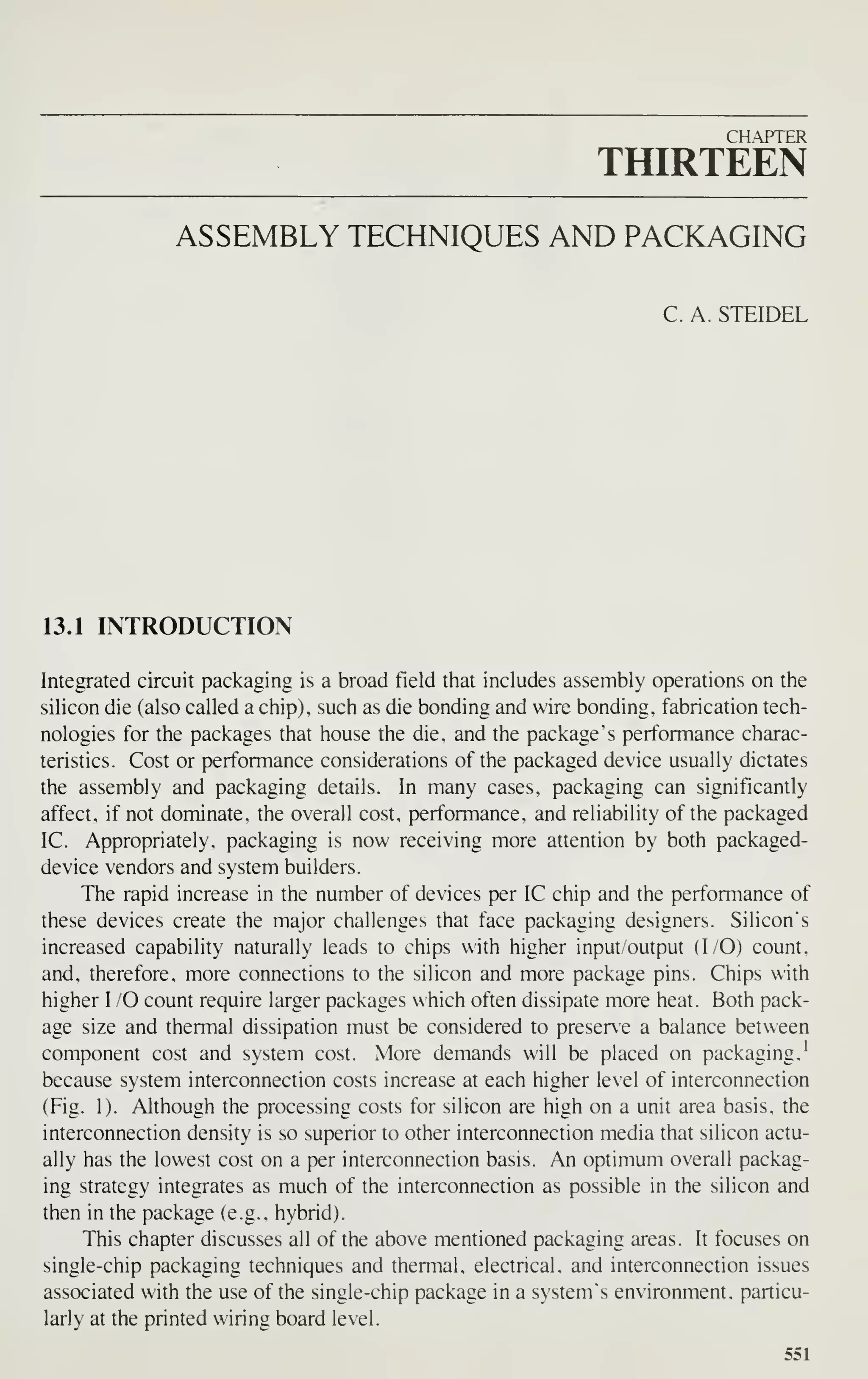

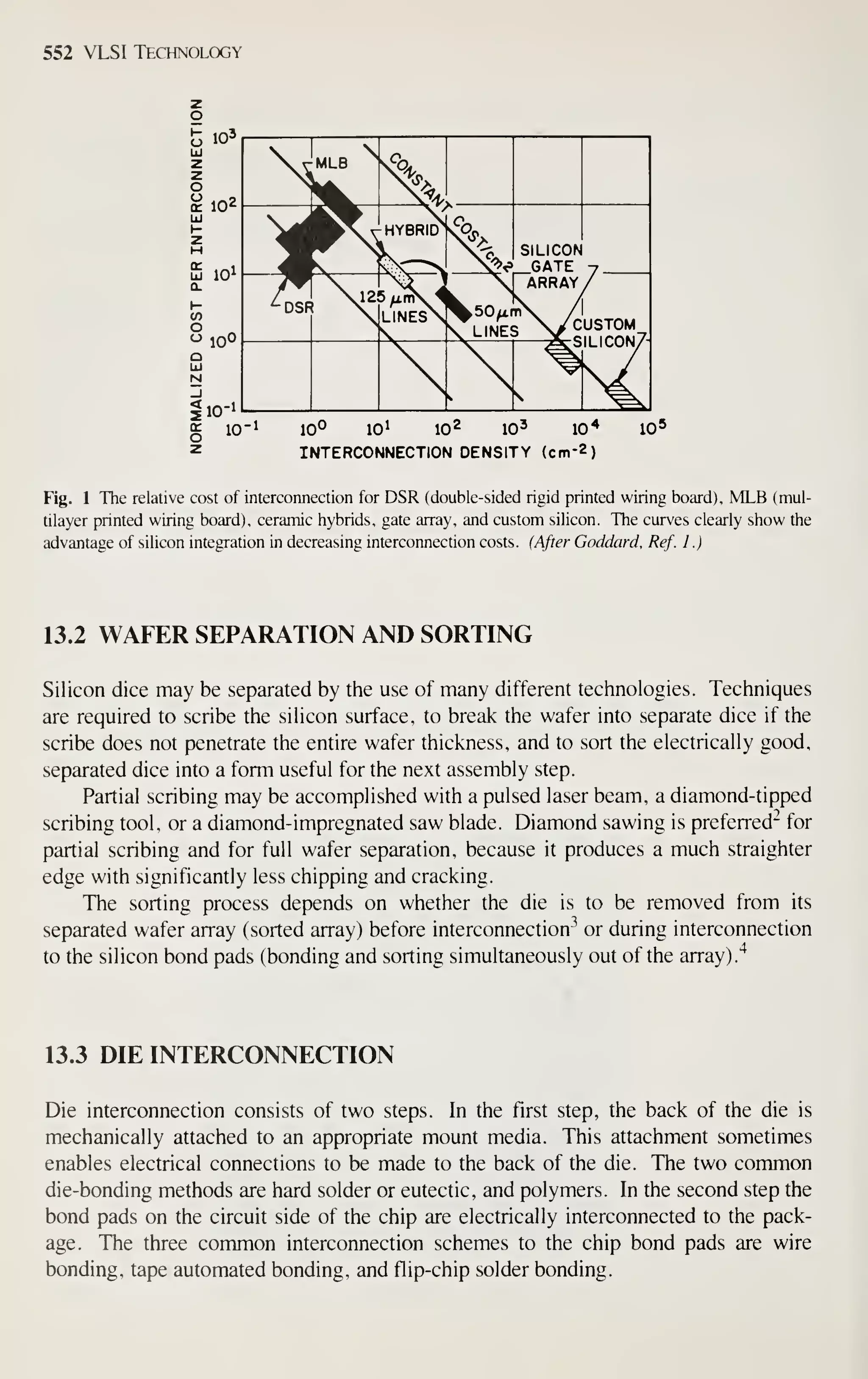

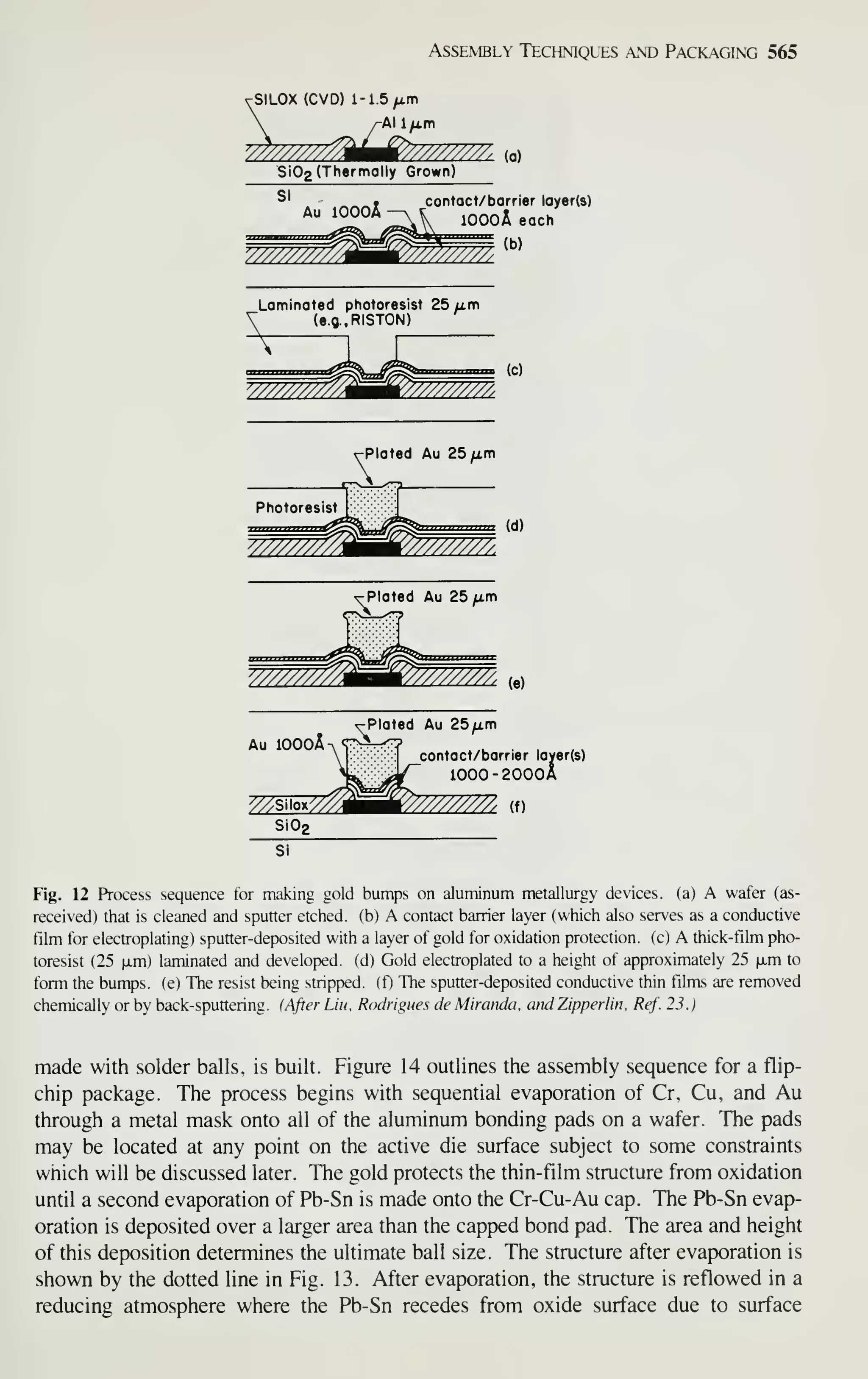

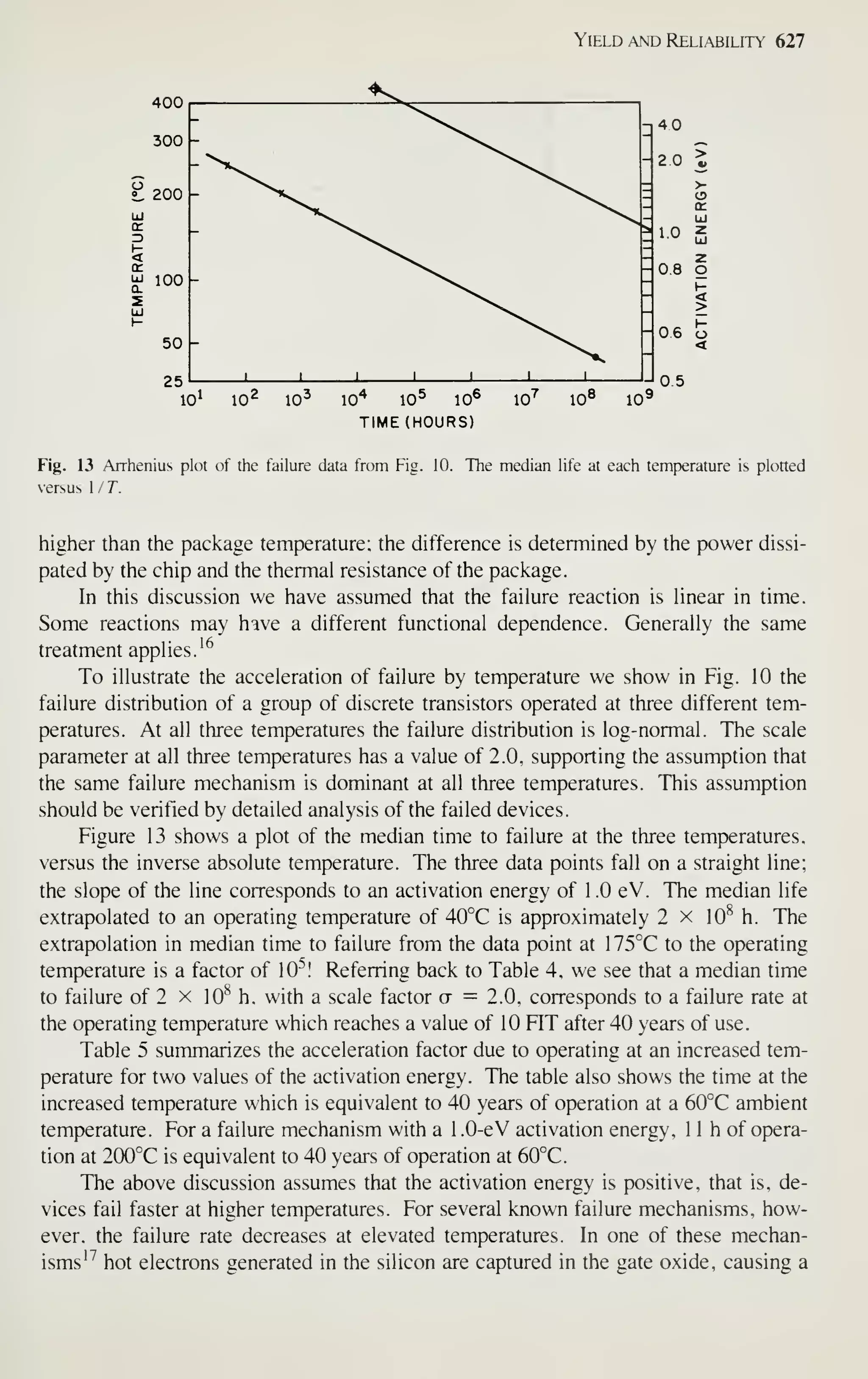

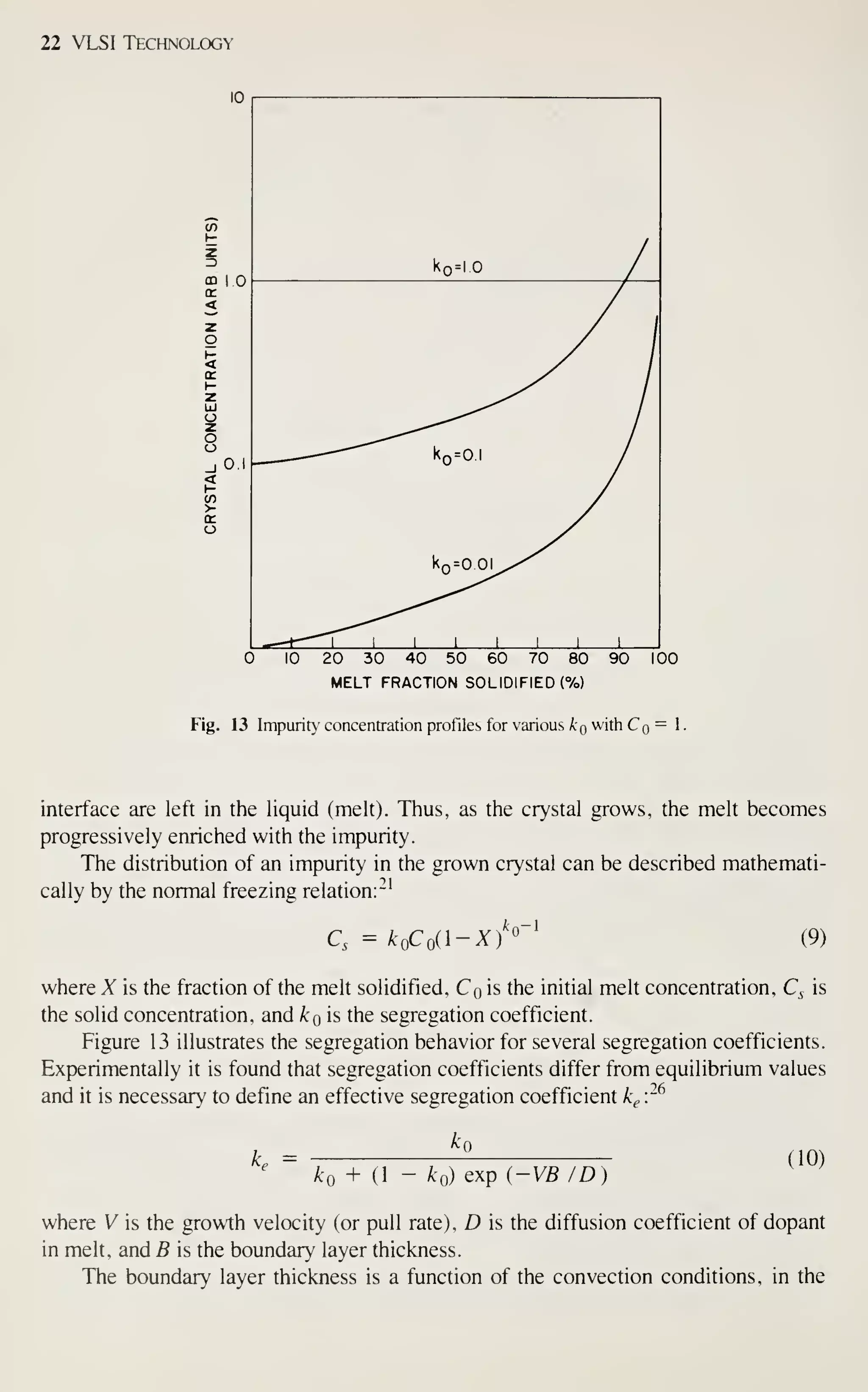

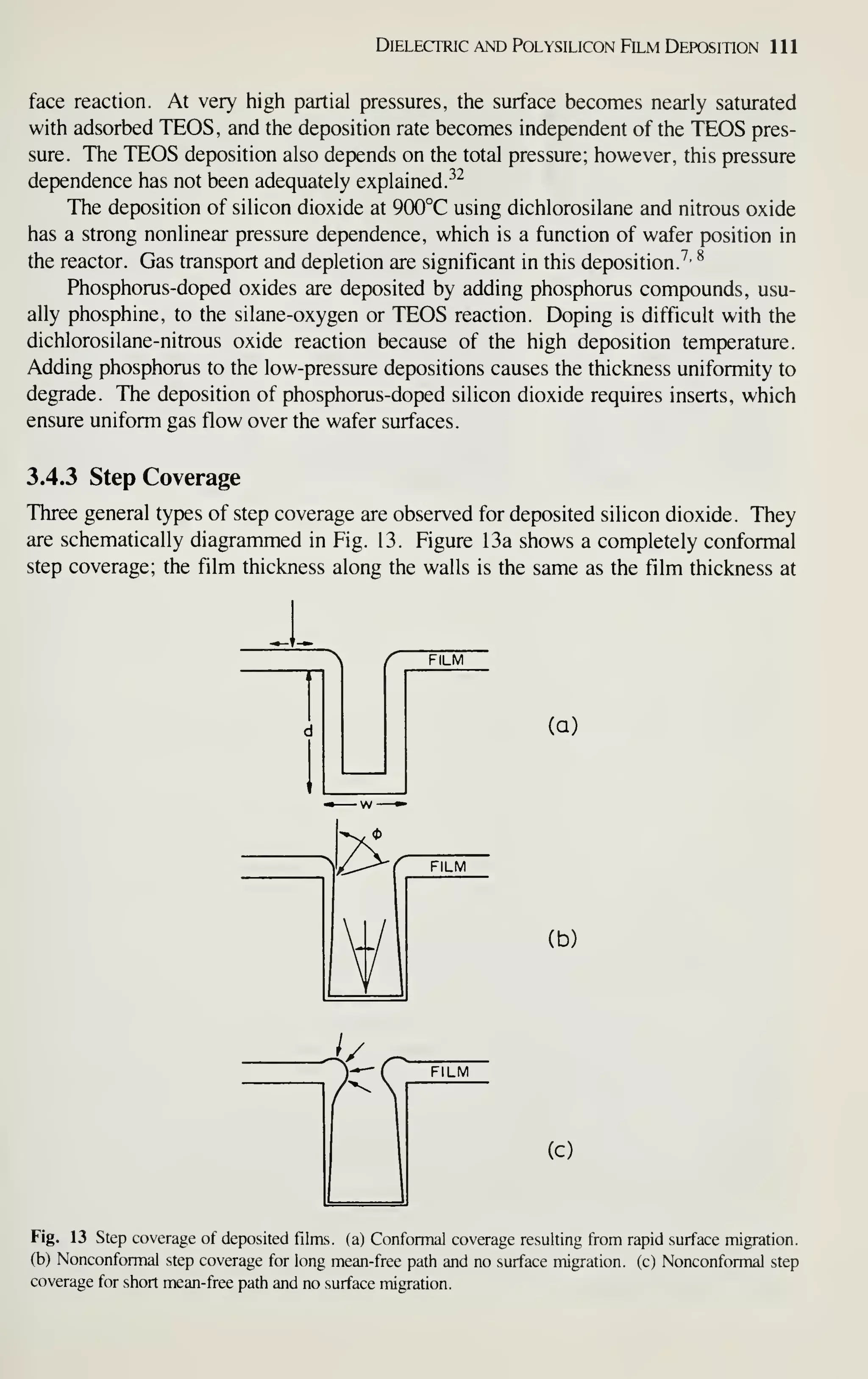

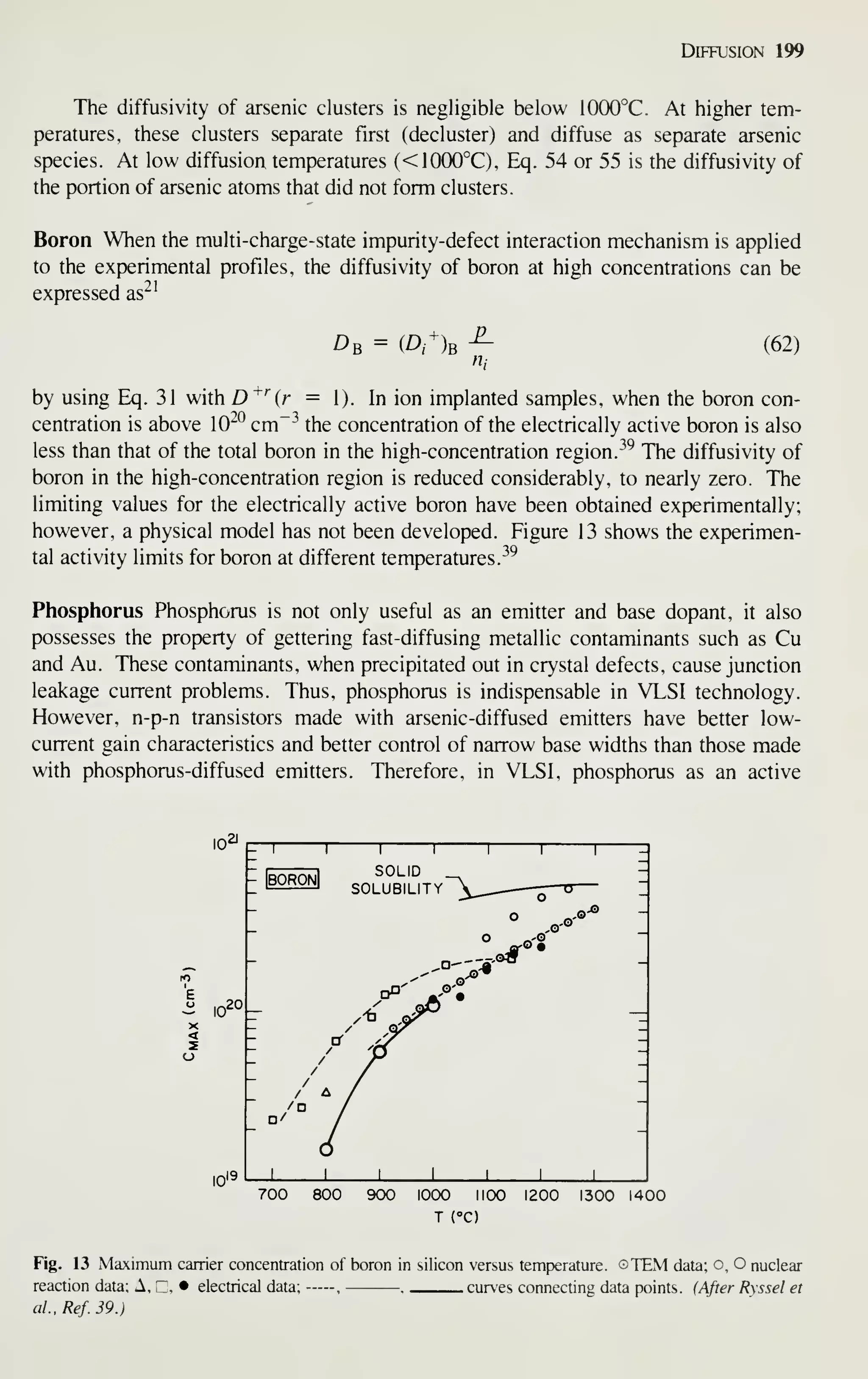

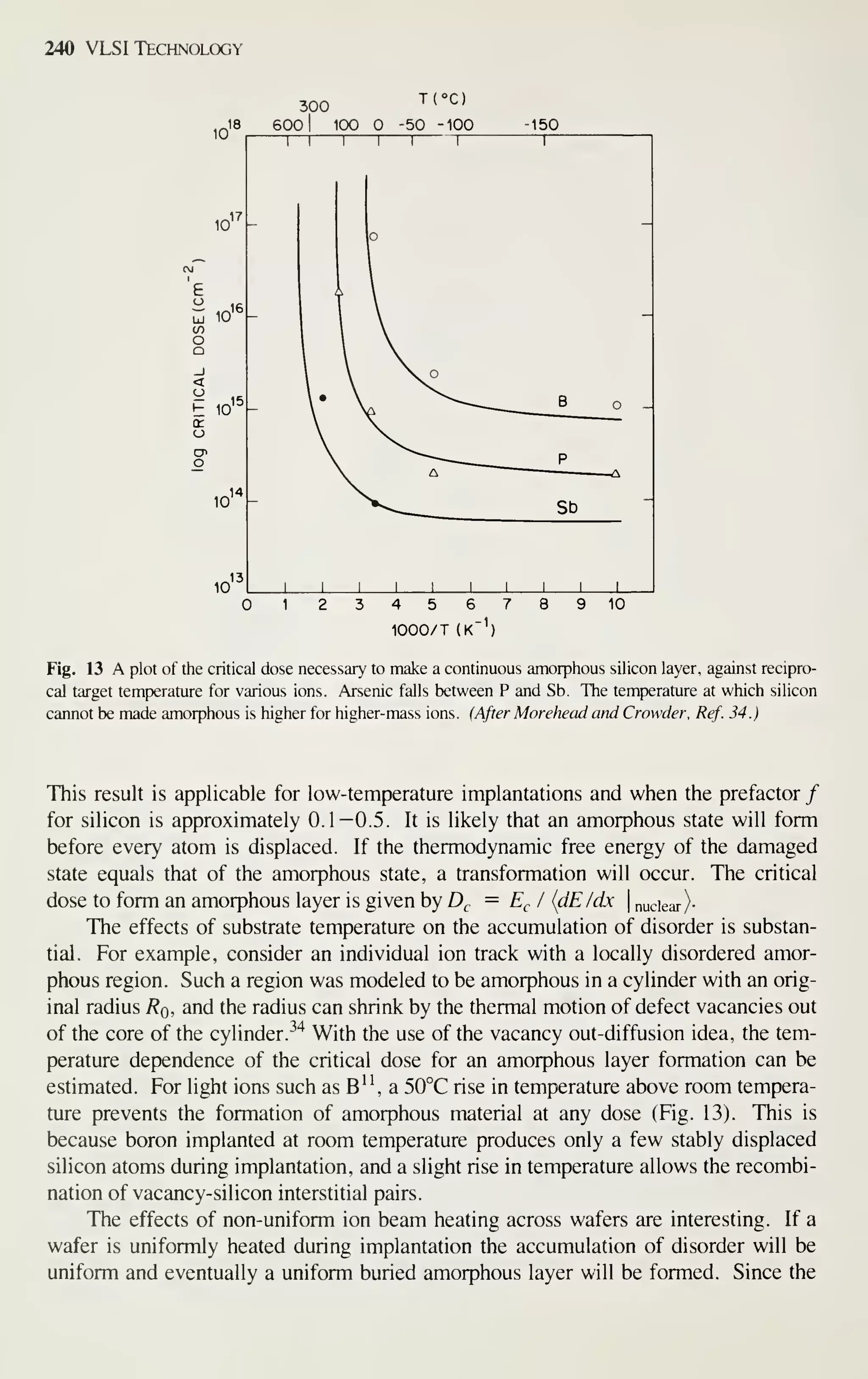

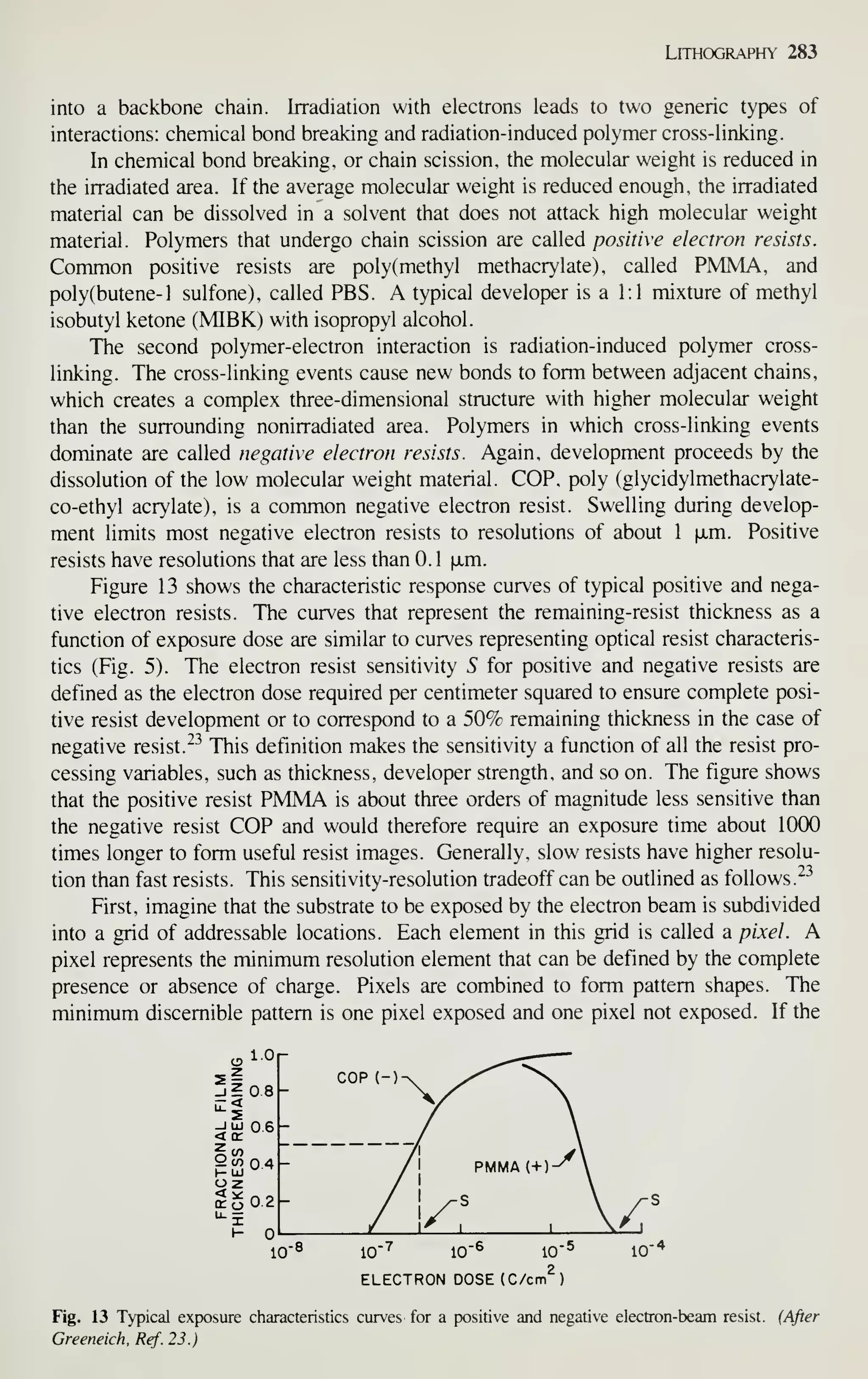

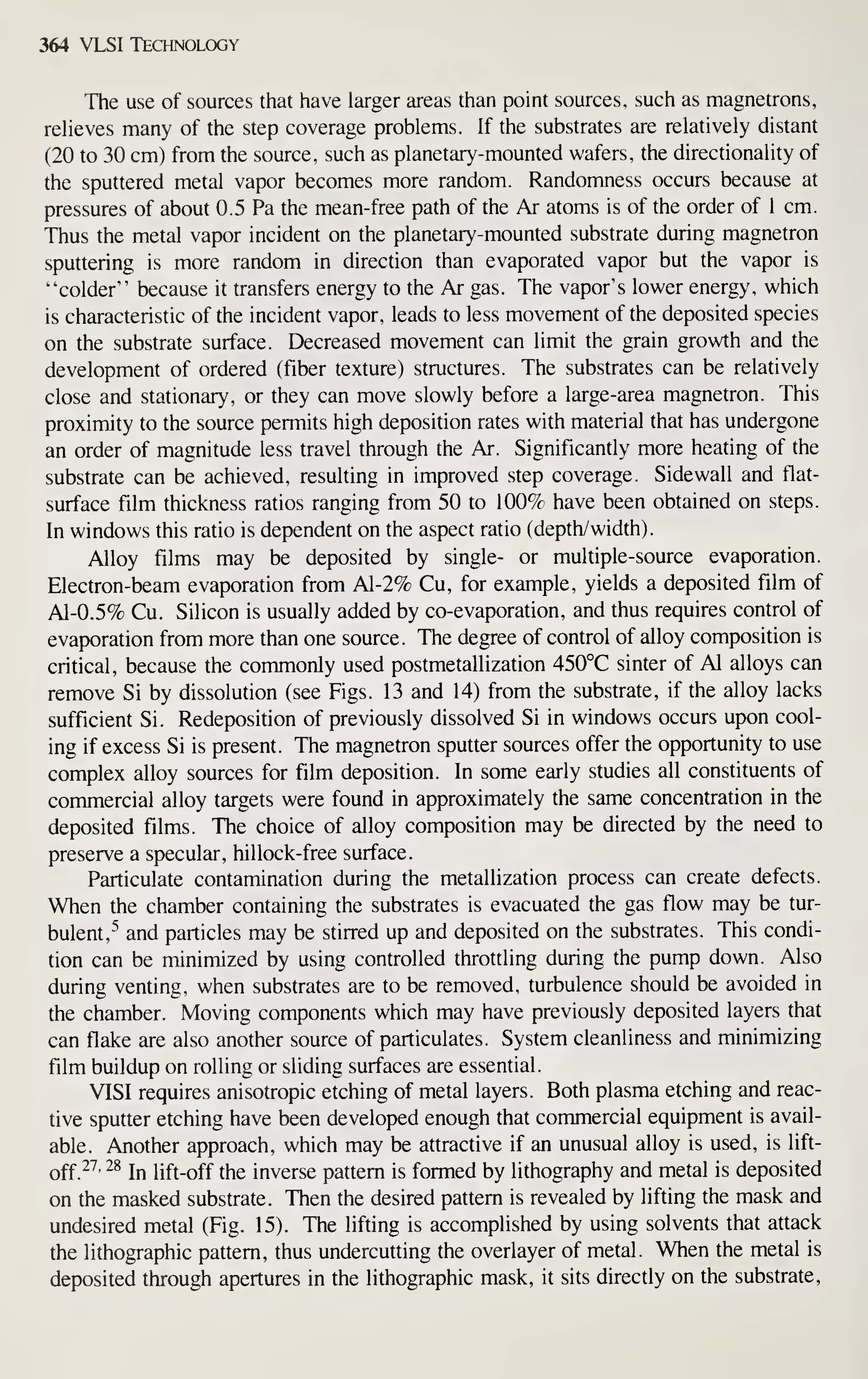

comparable rate.^ In 10 years, it will rival the automobile, chemical, and steel indus-

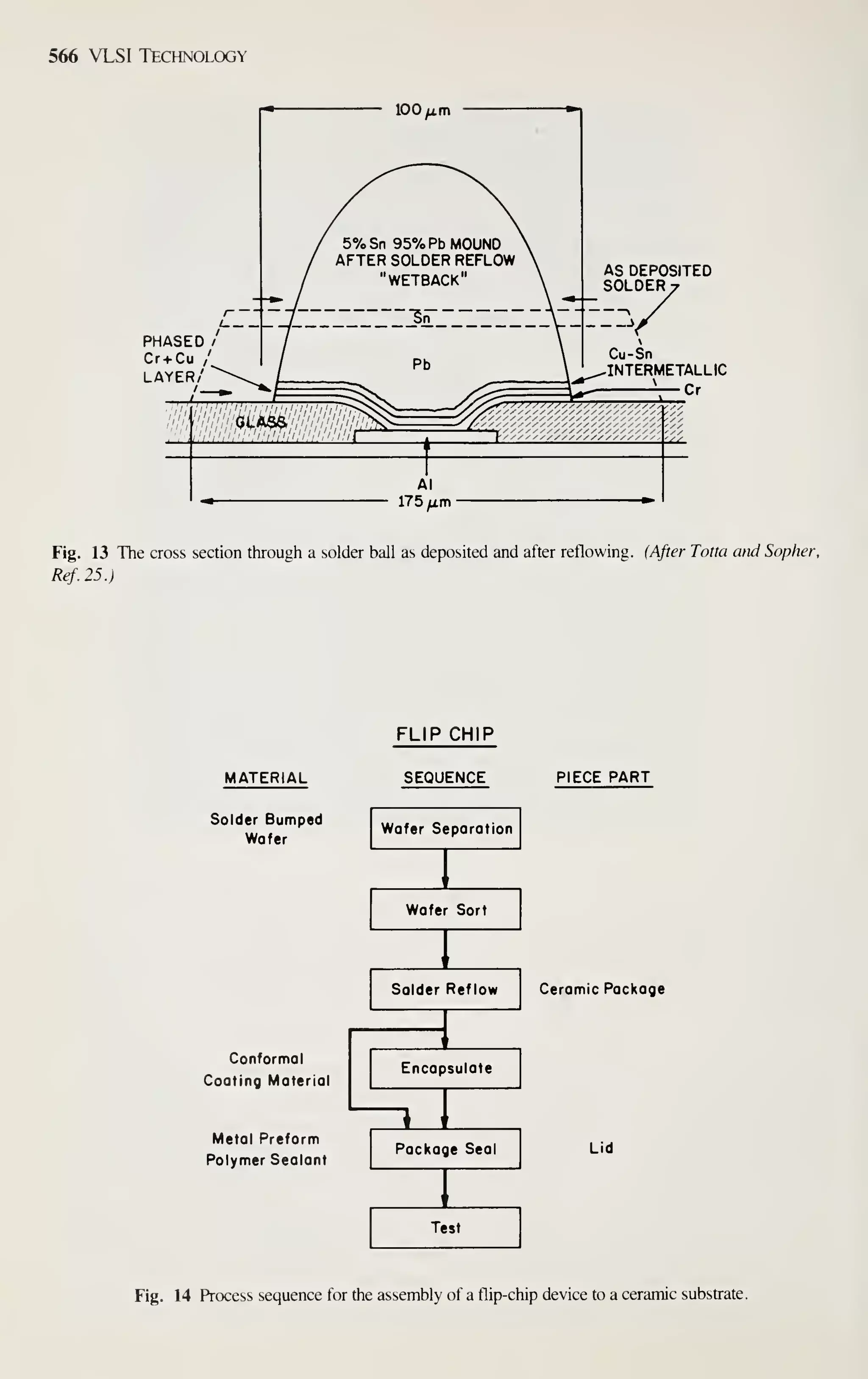

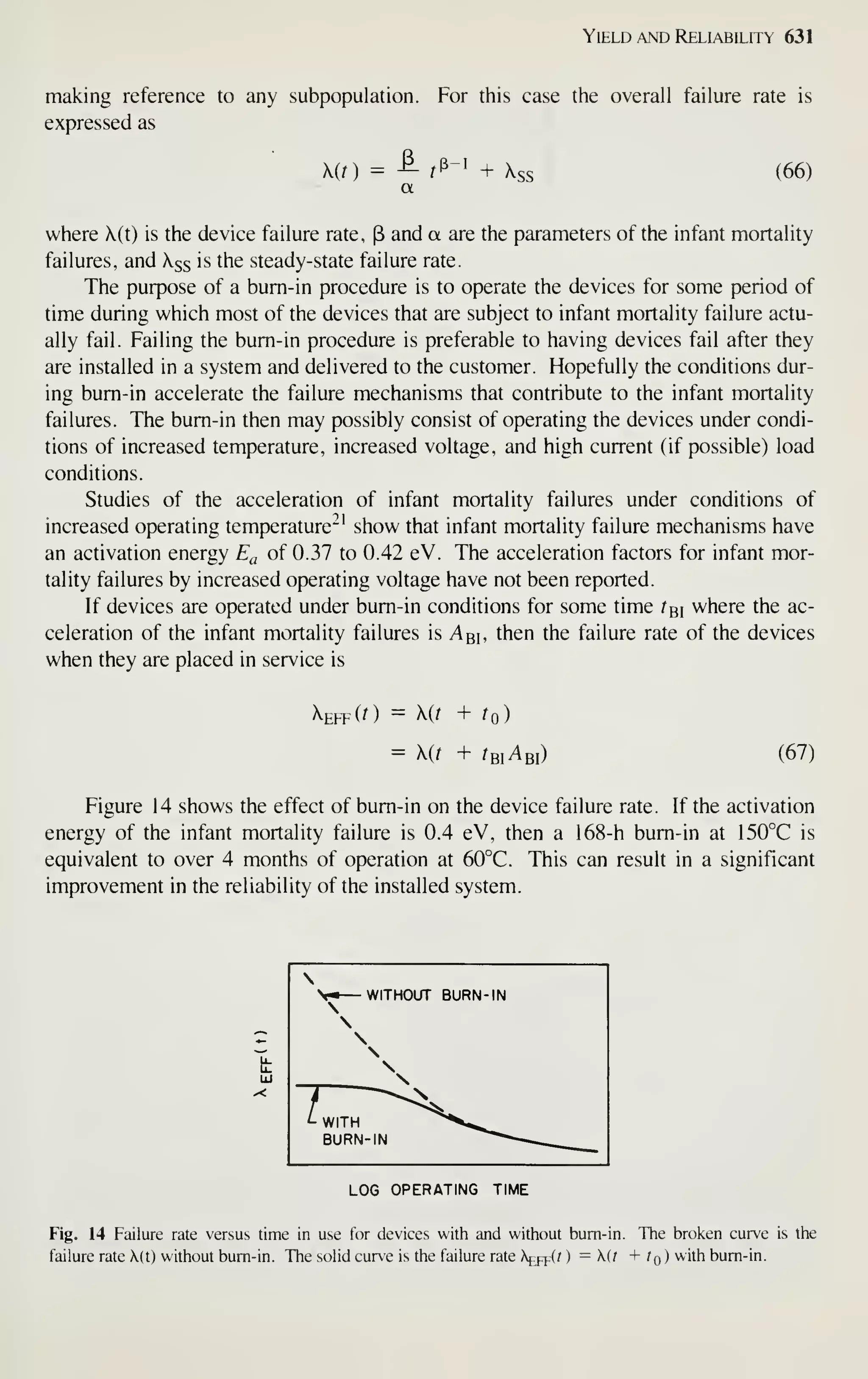

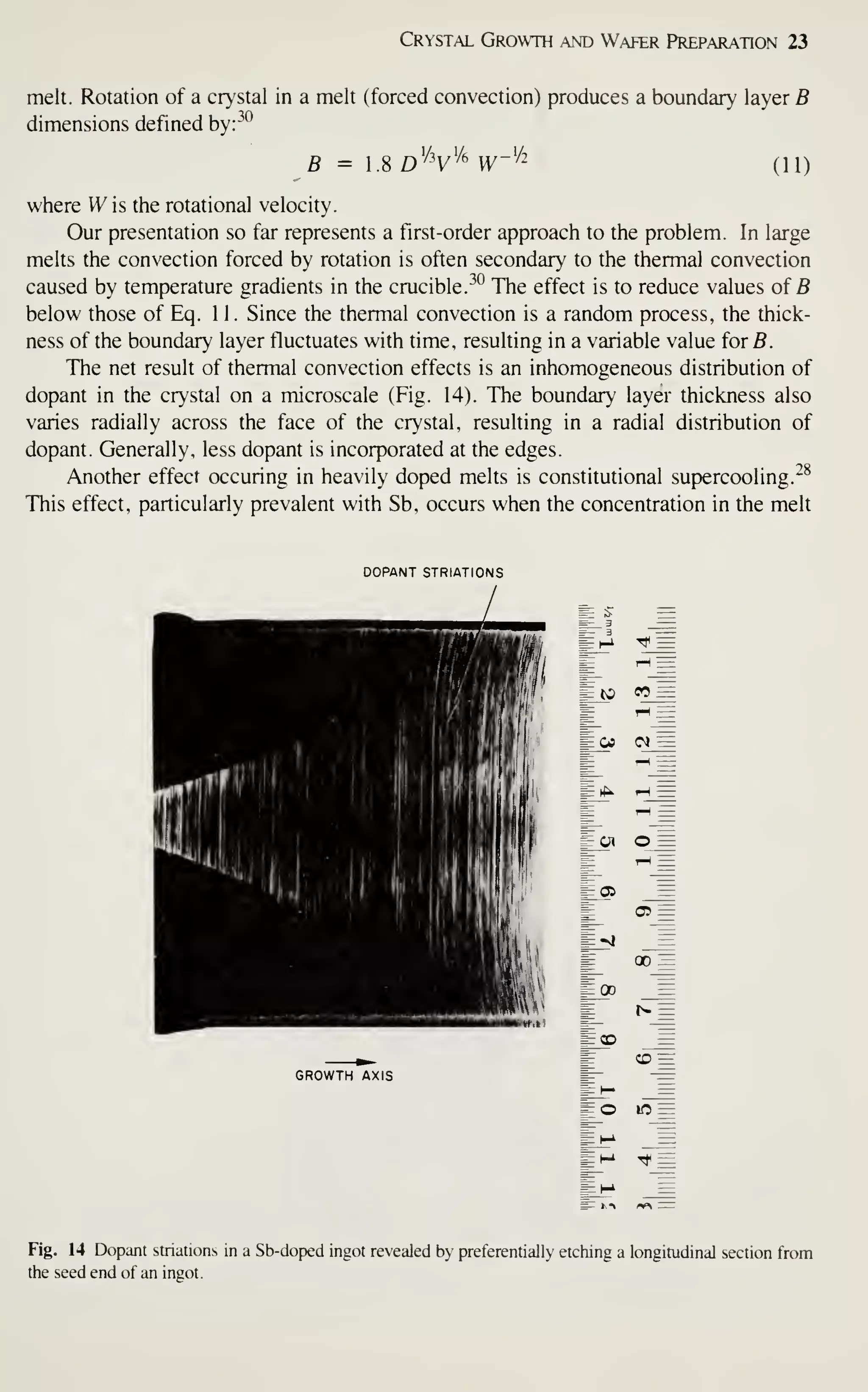

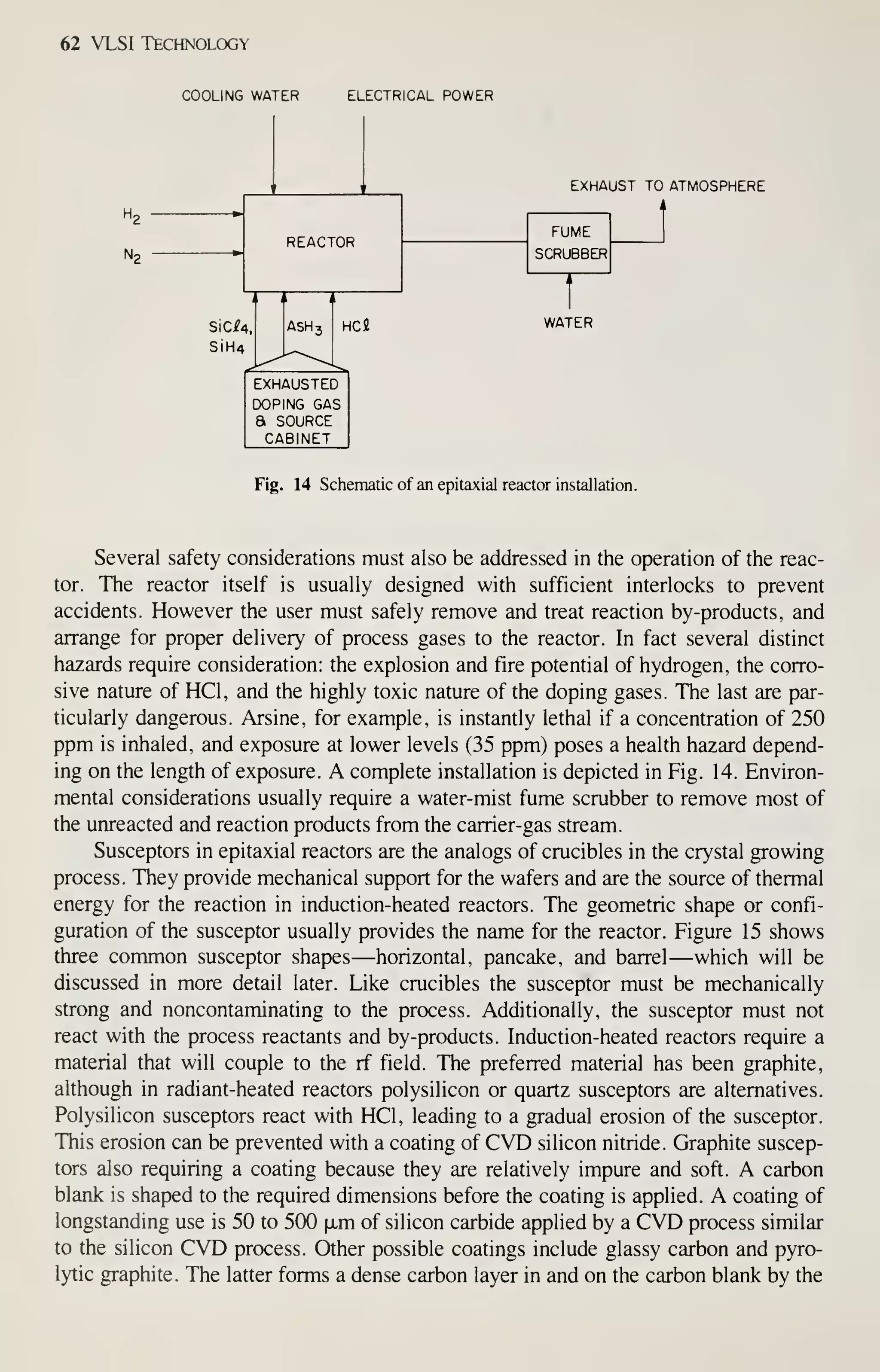

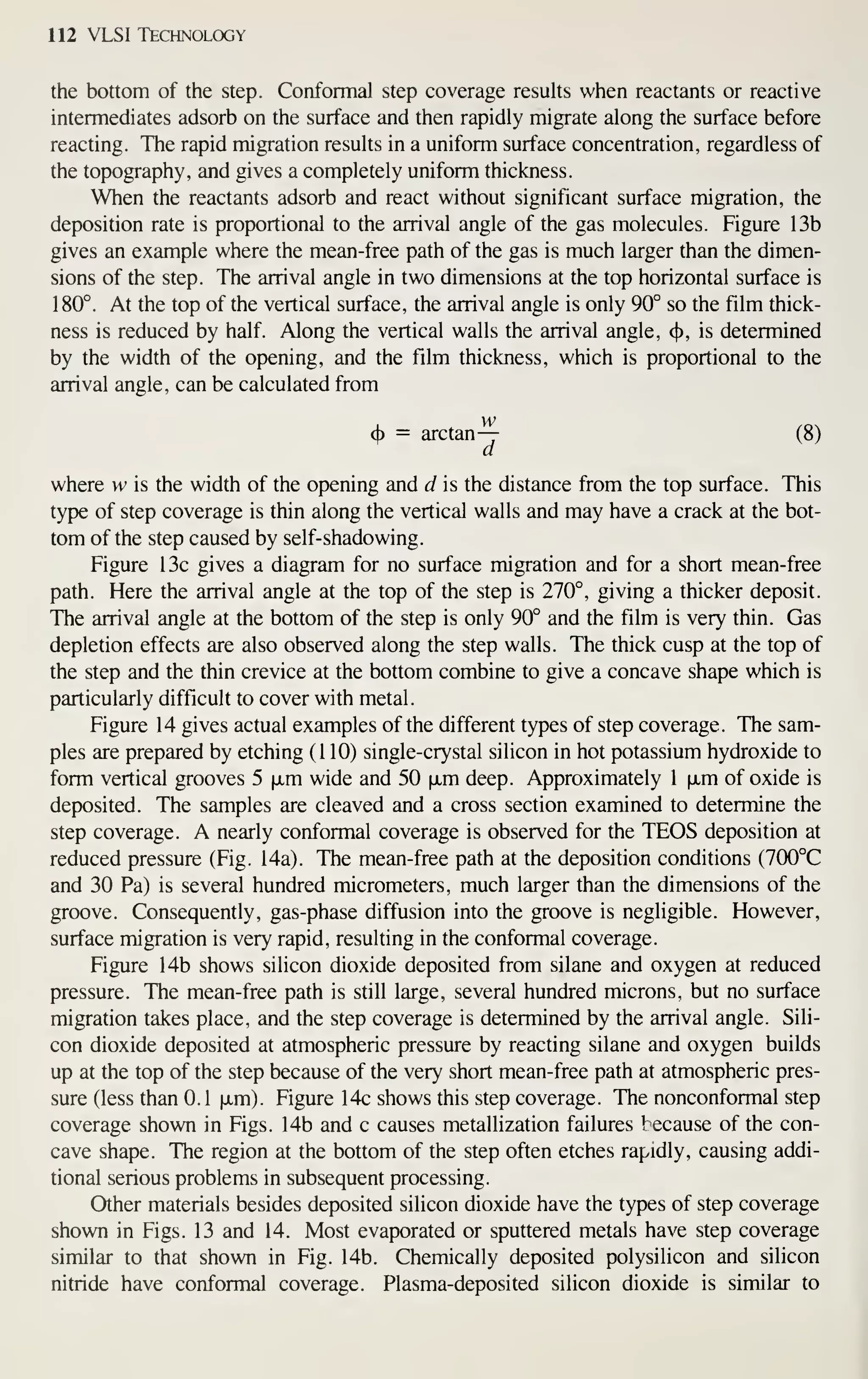

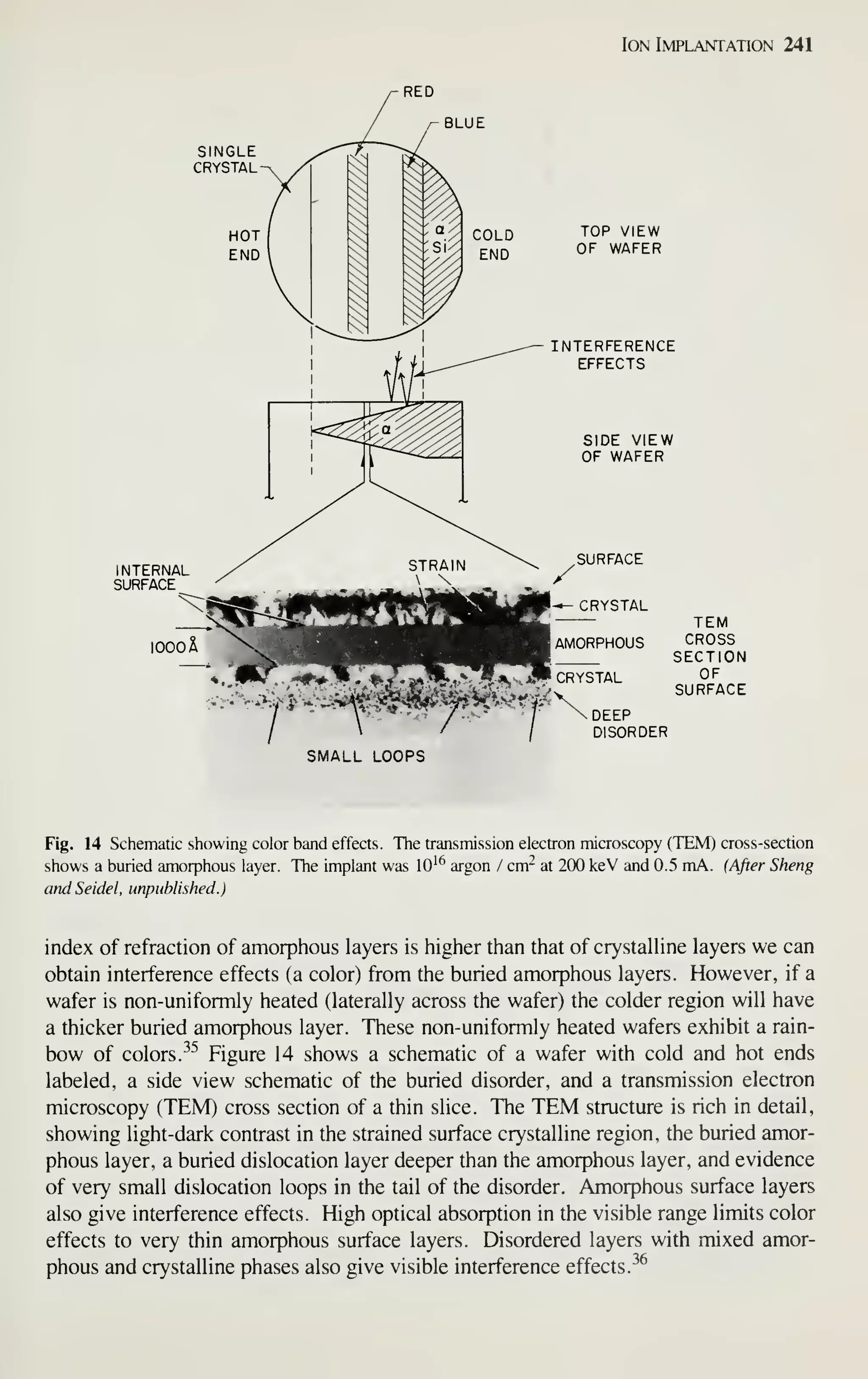

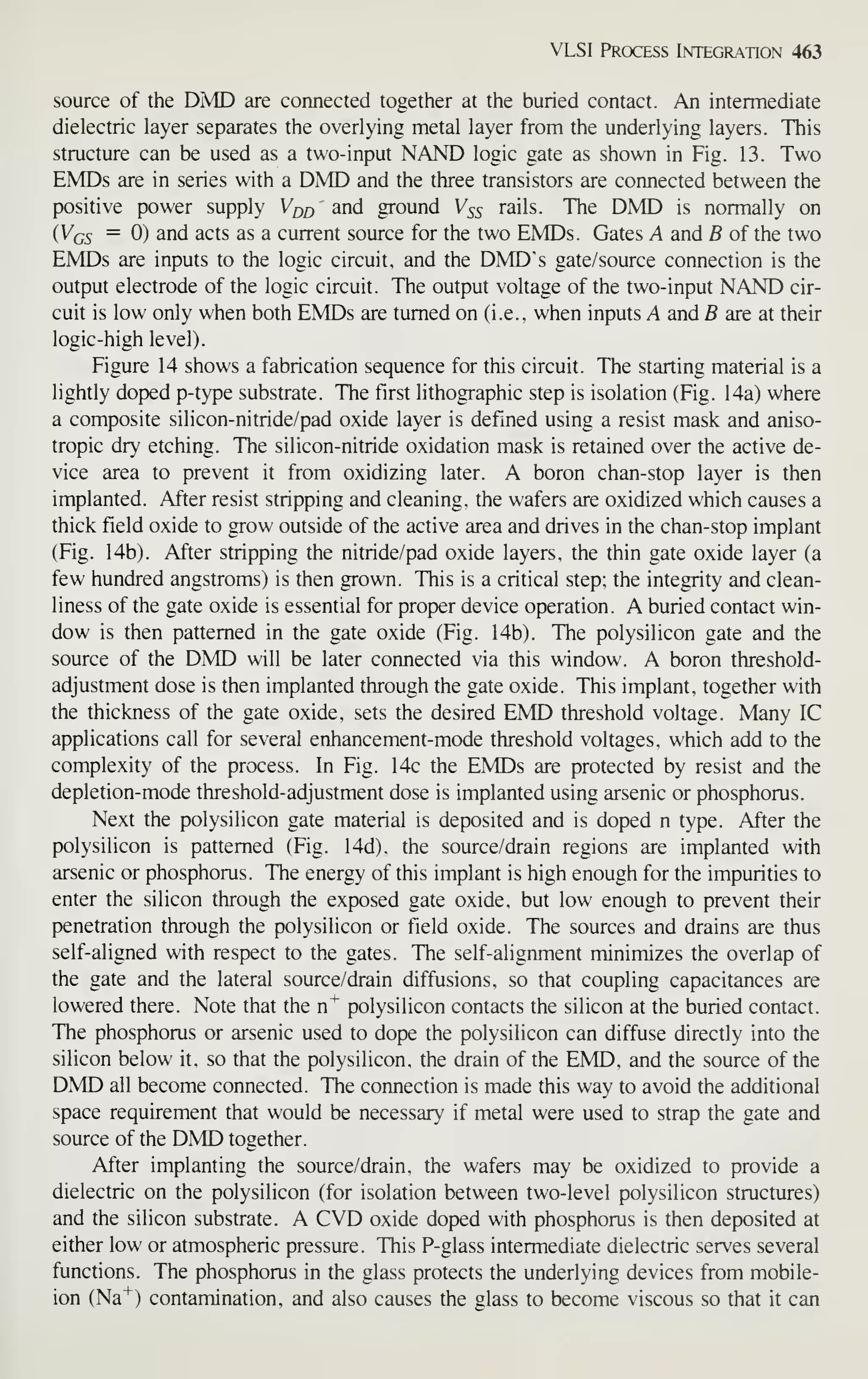

tries in sales volume.

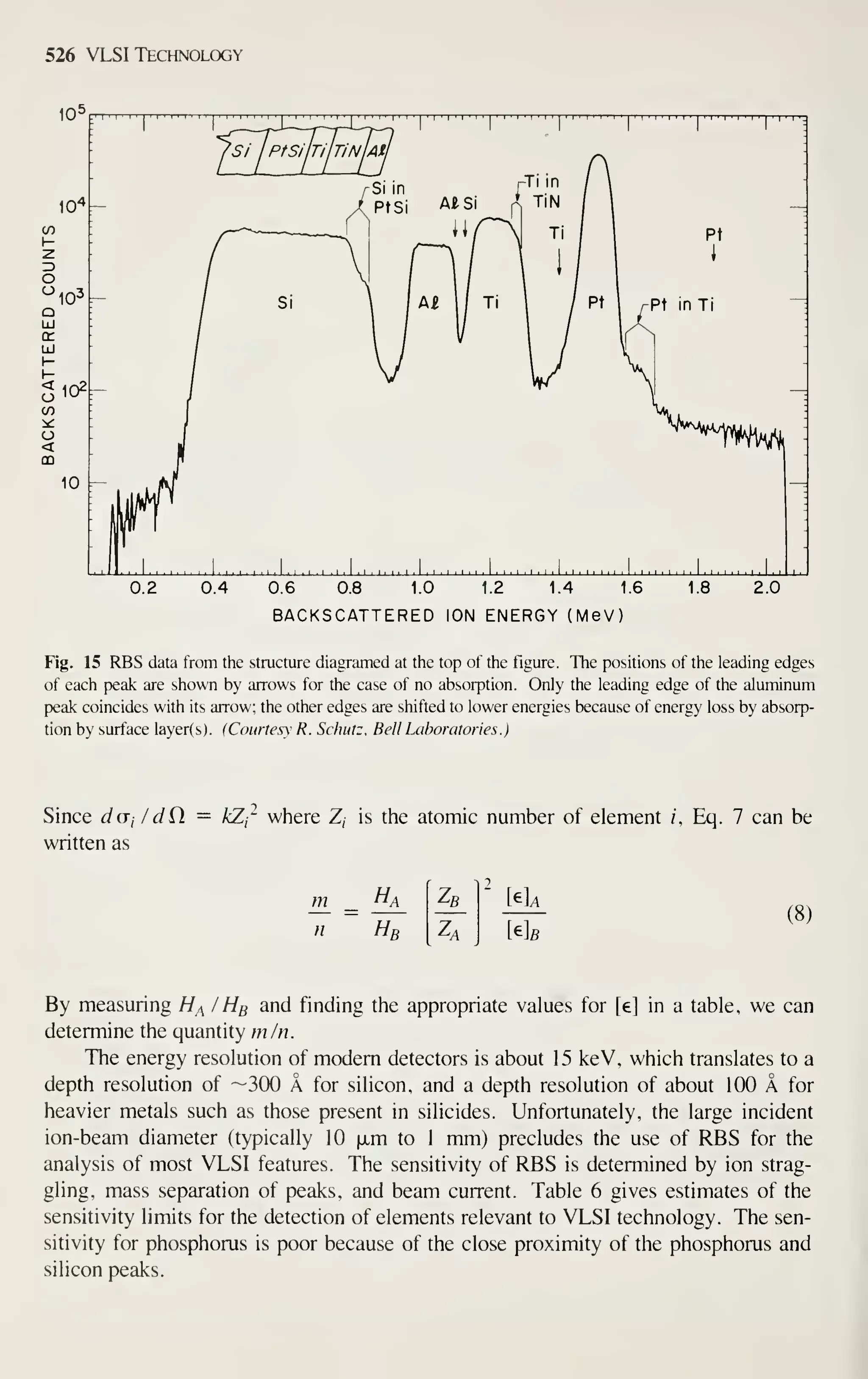

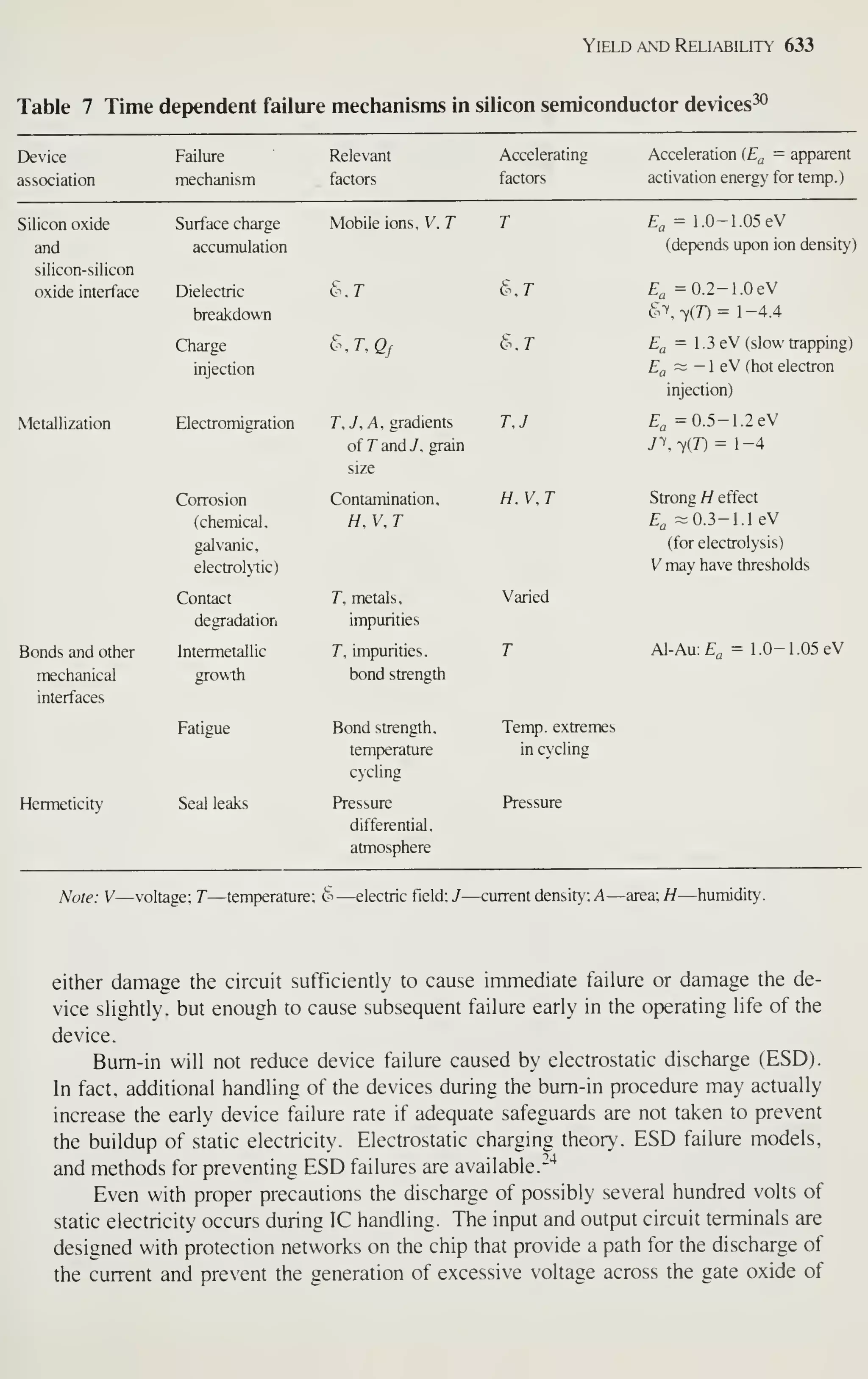

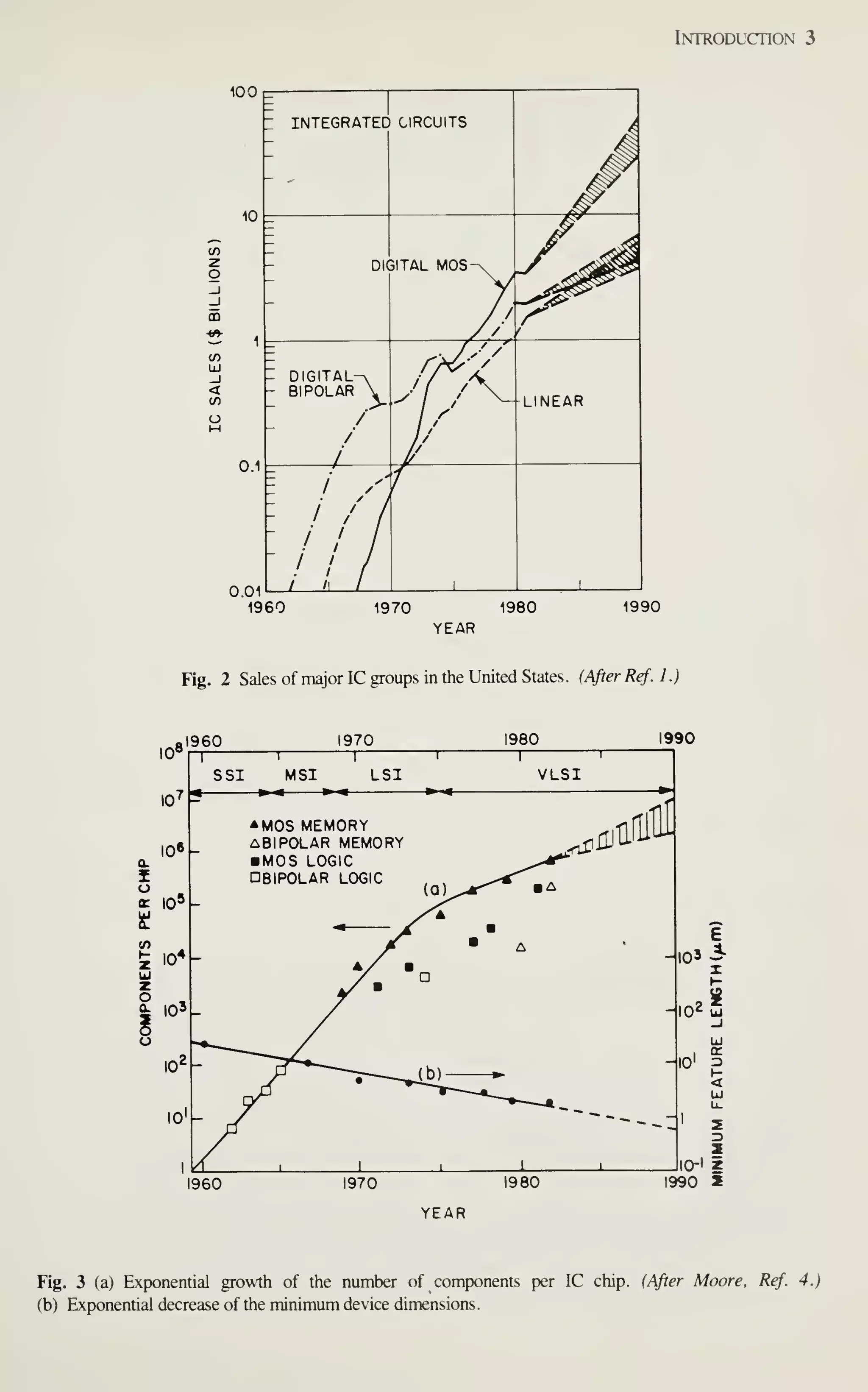

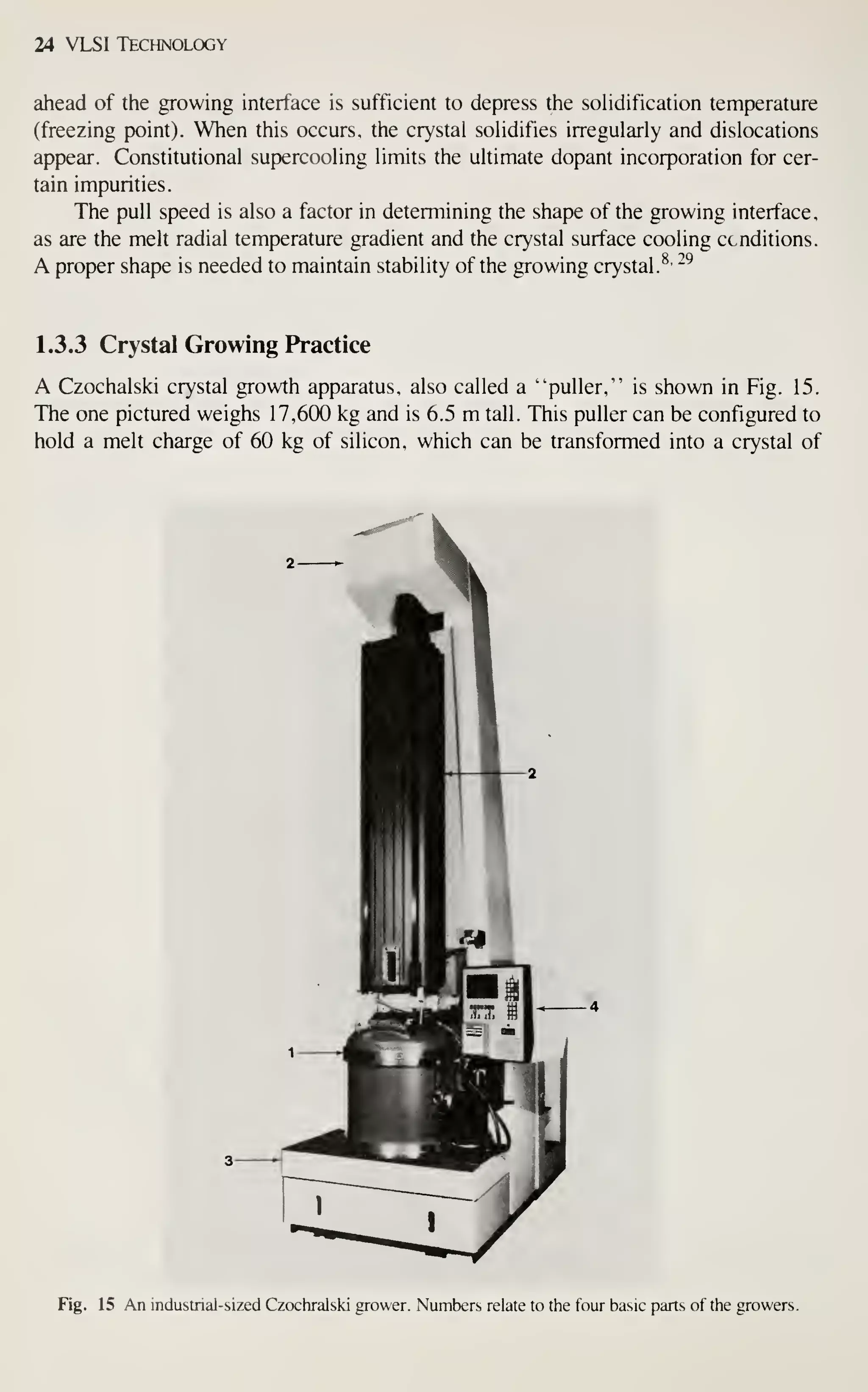

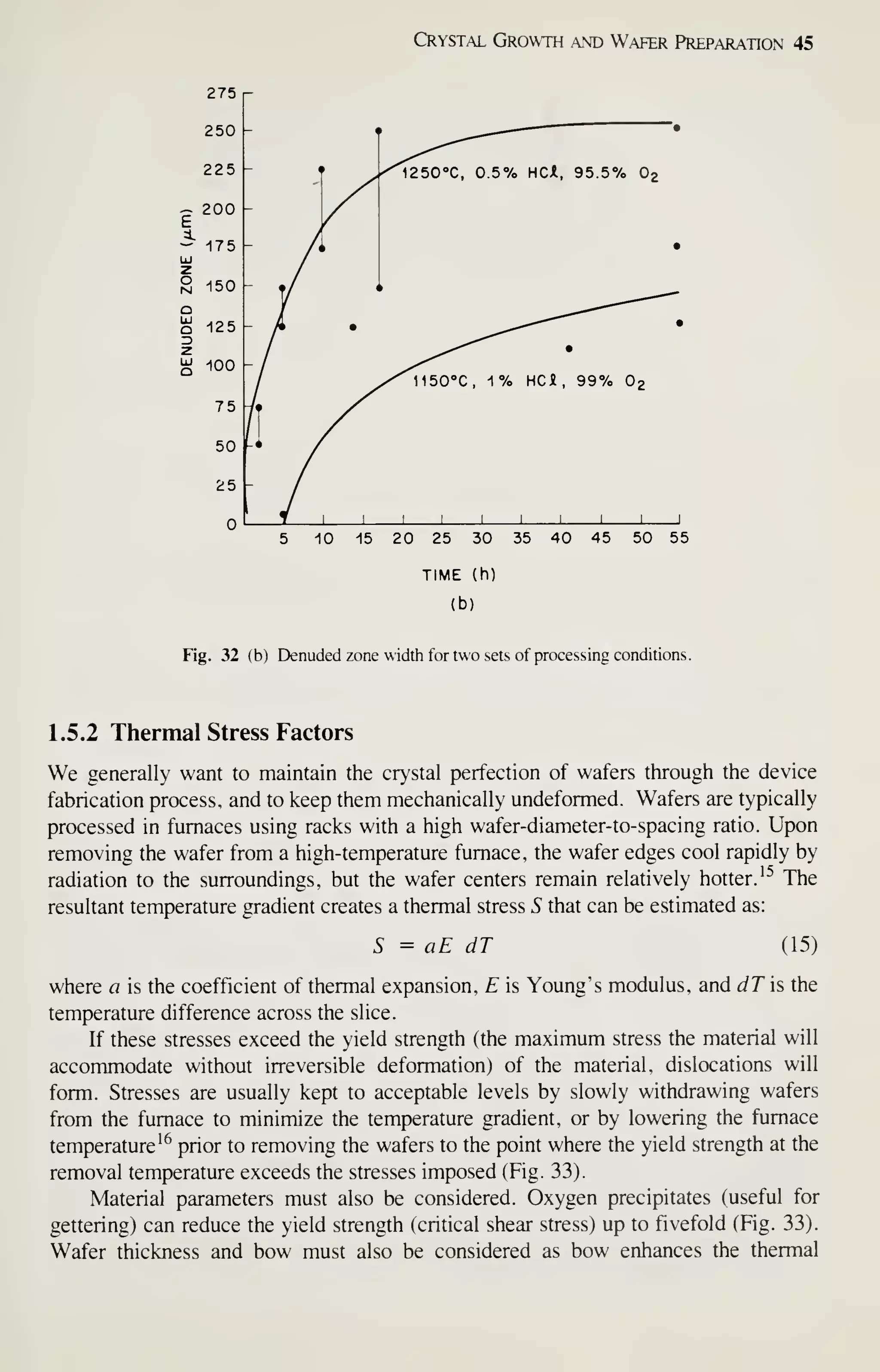

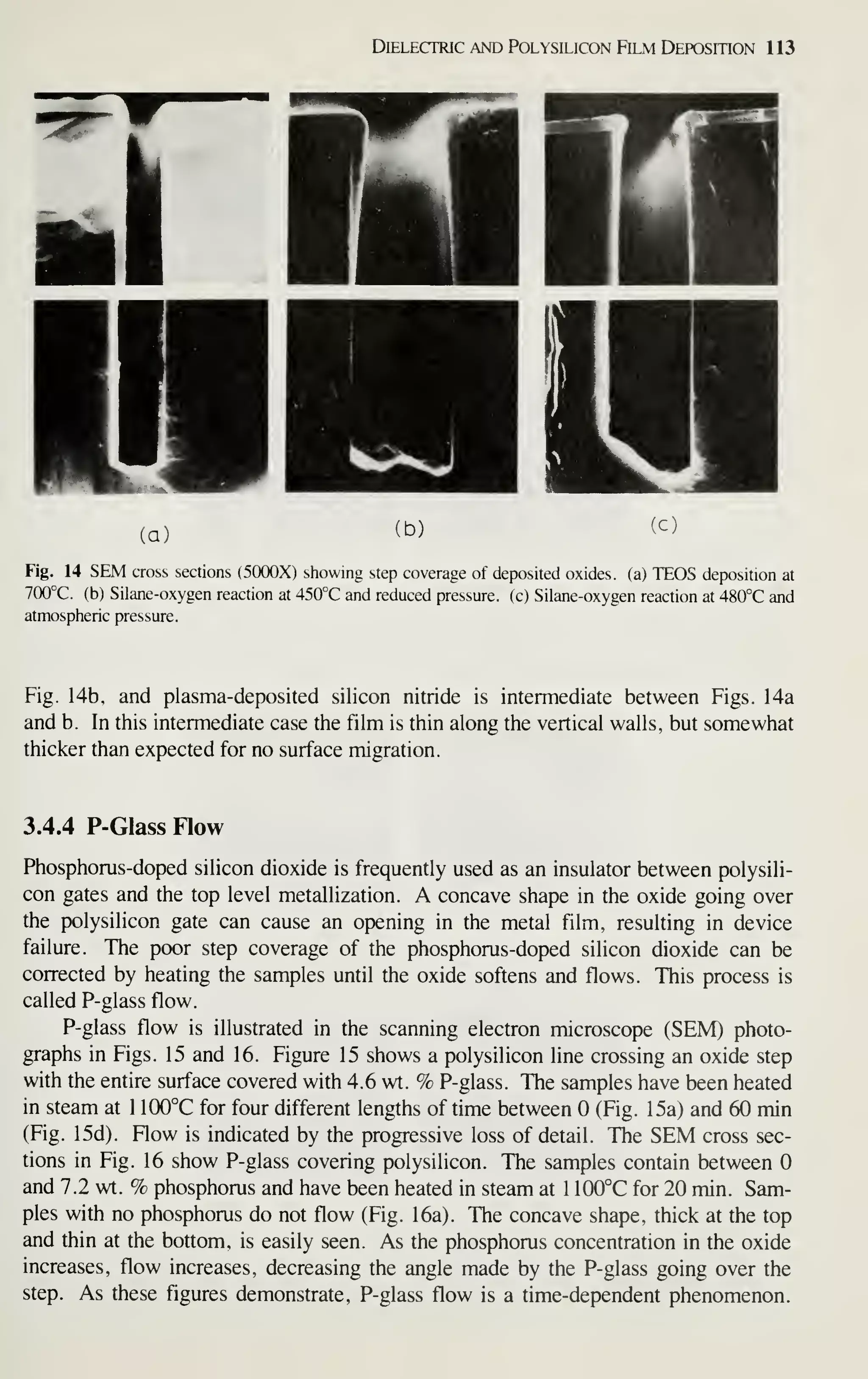

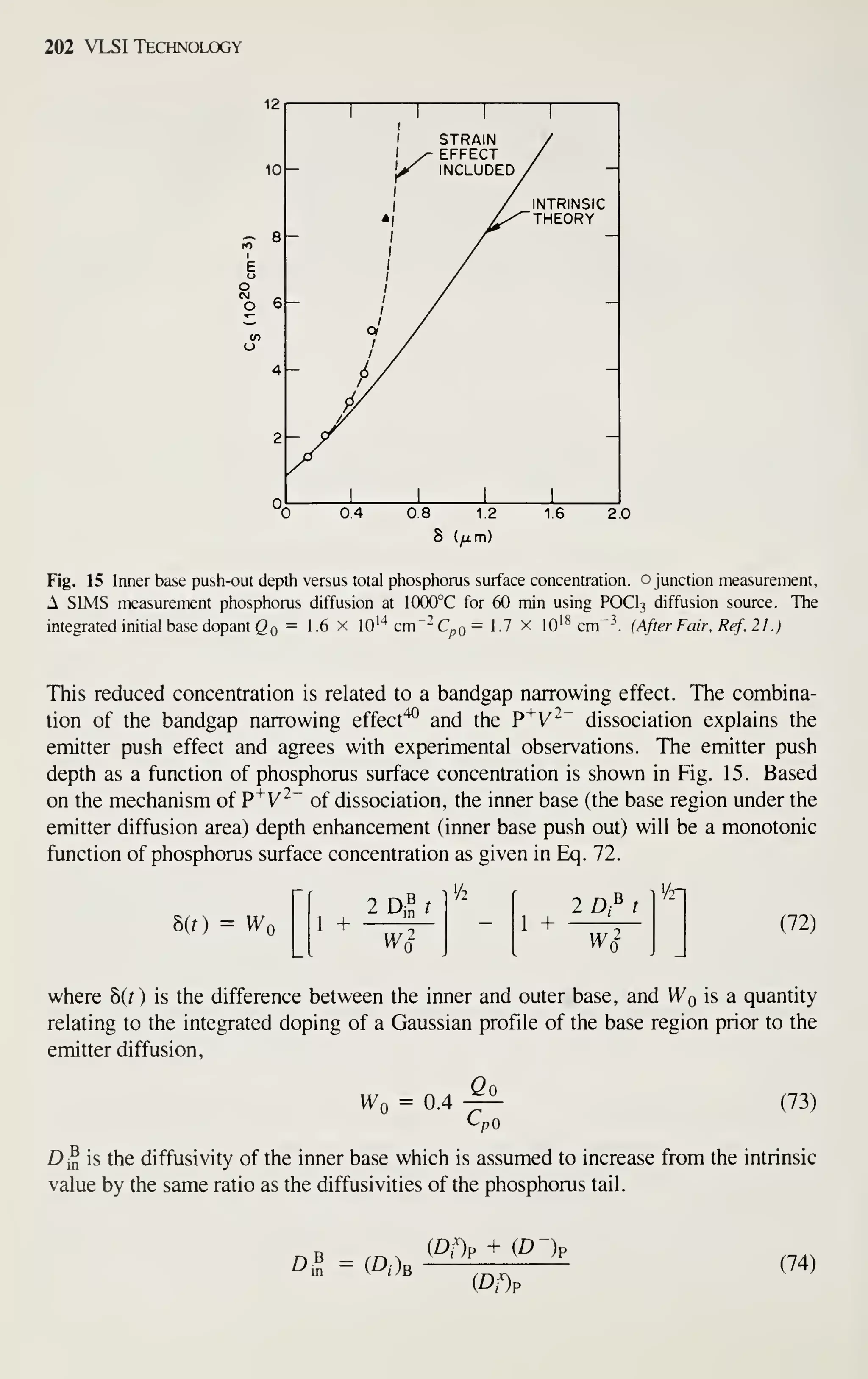

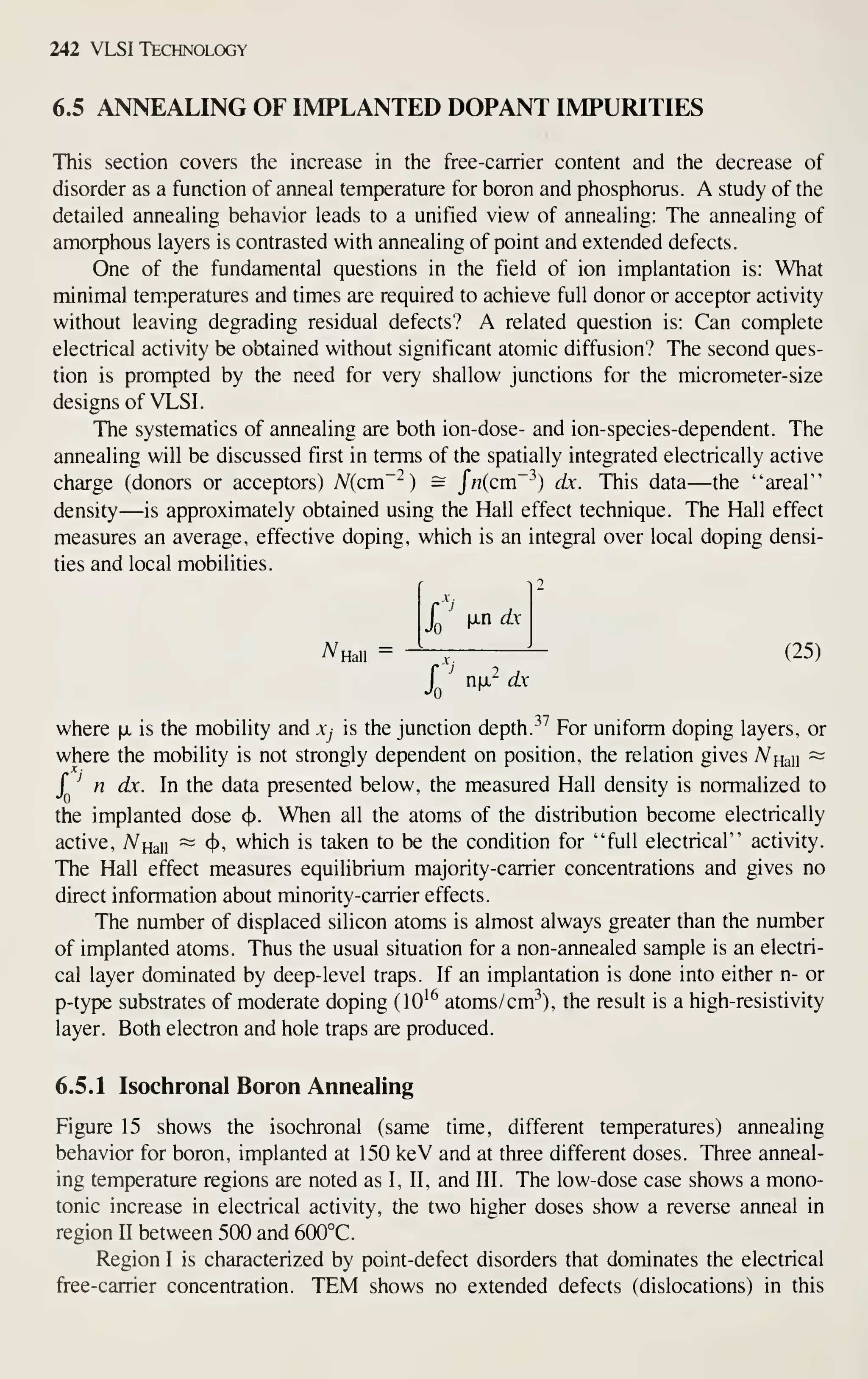

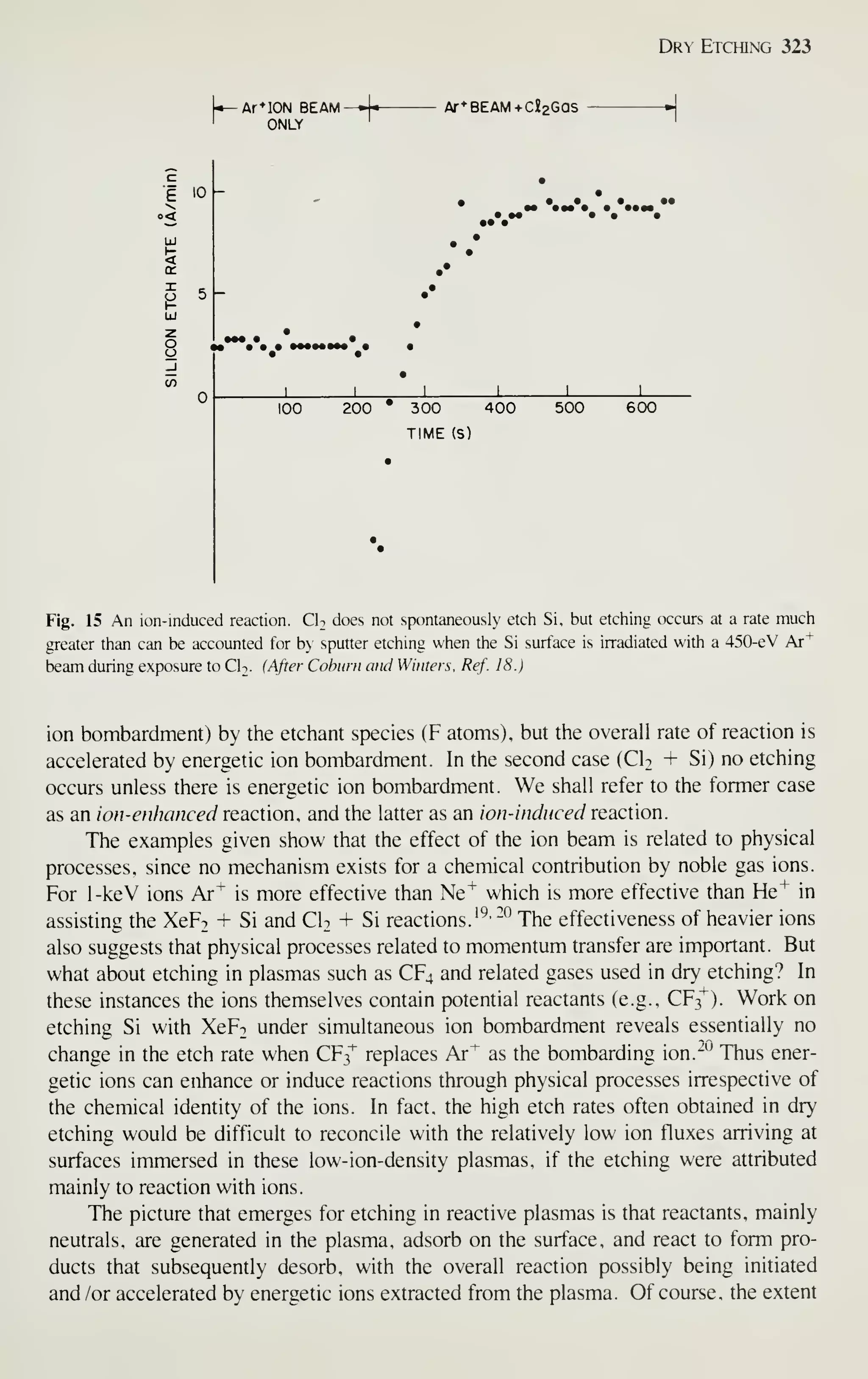

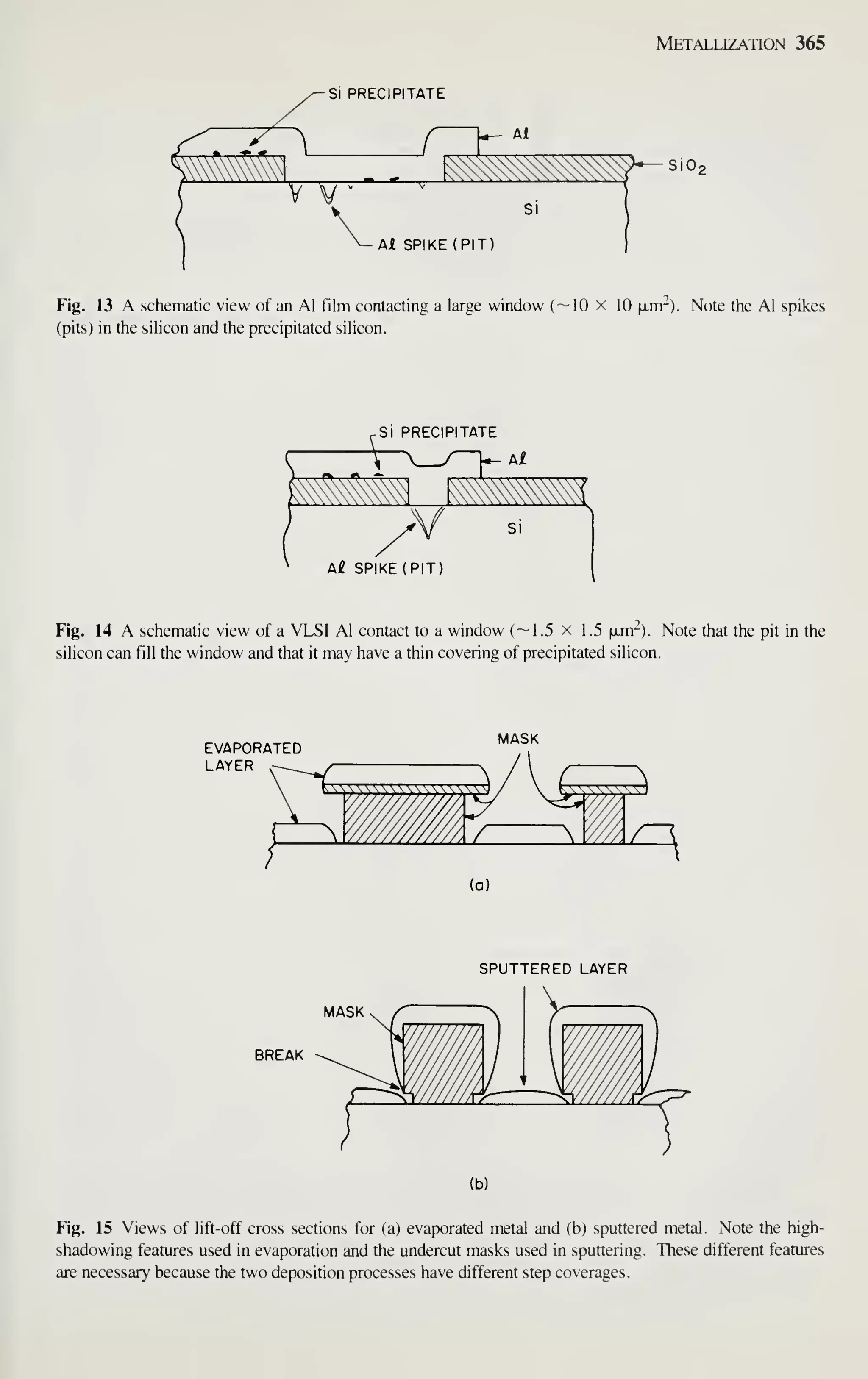

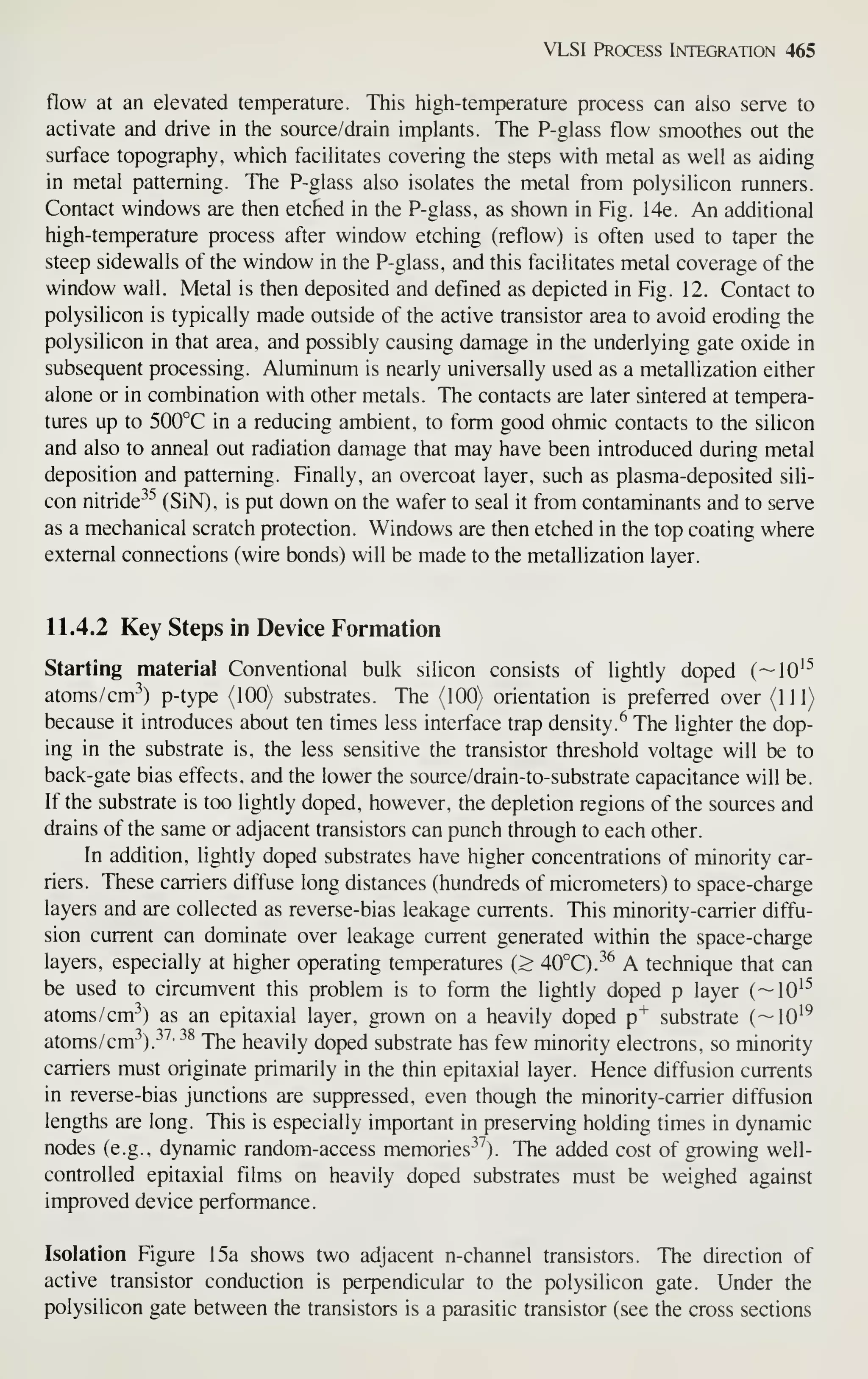

Figure 2 shows the sales of major IC groups and how sales have changed in

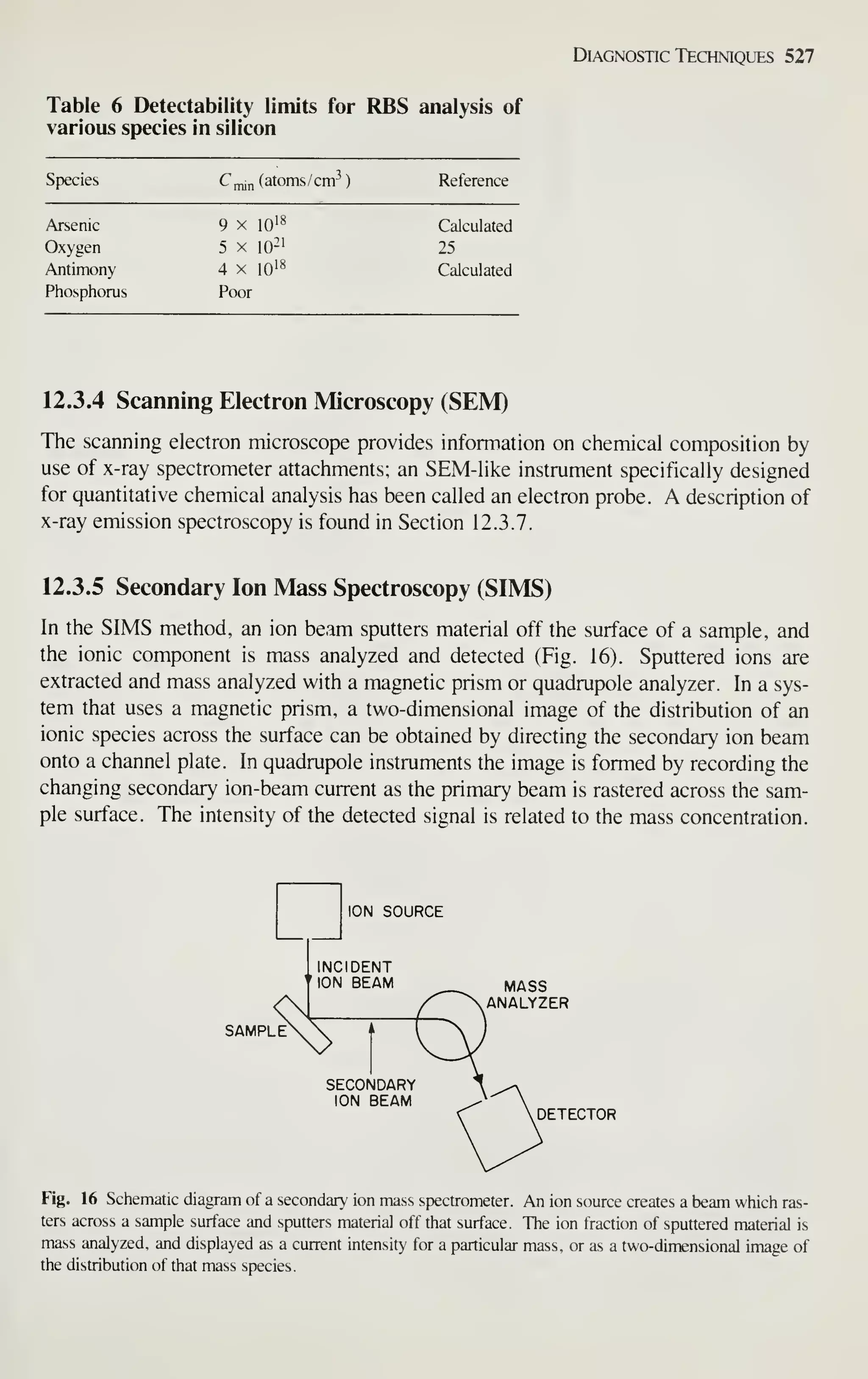

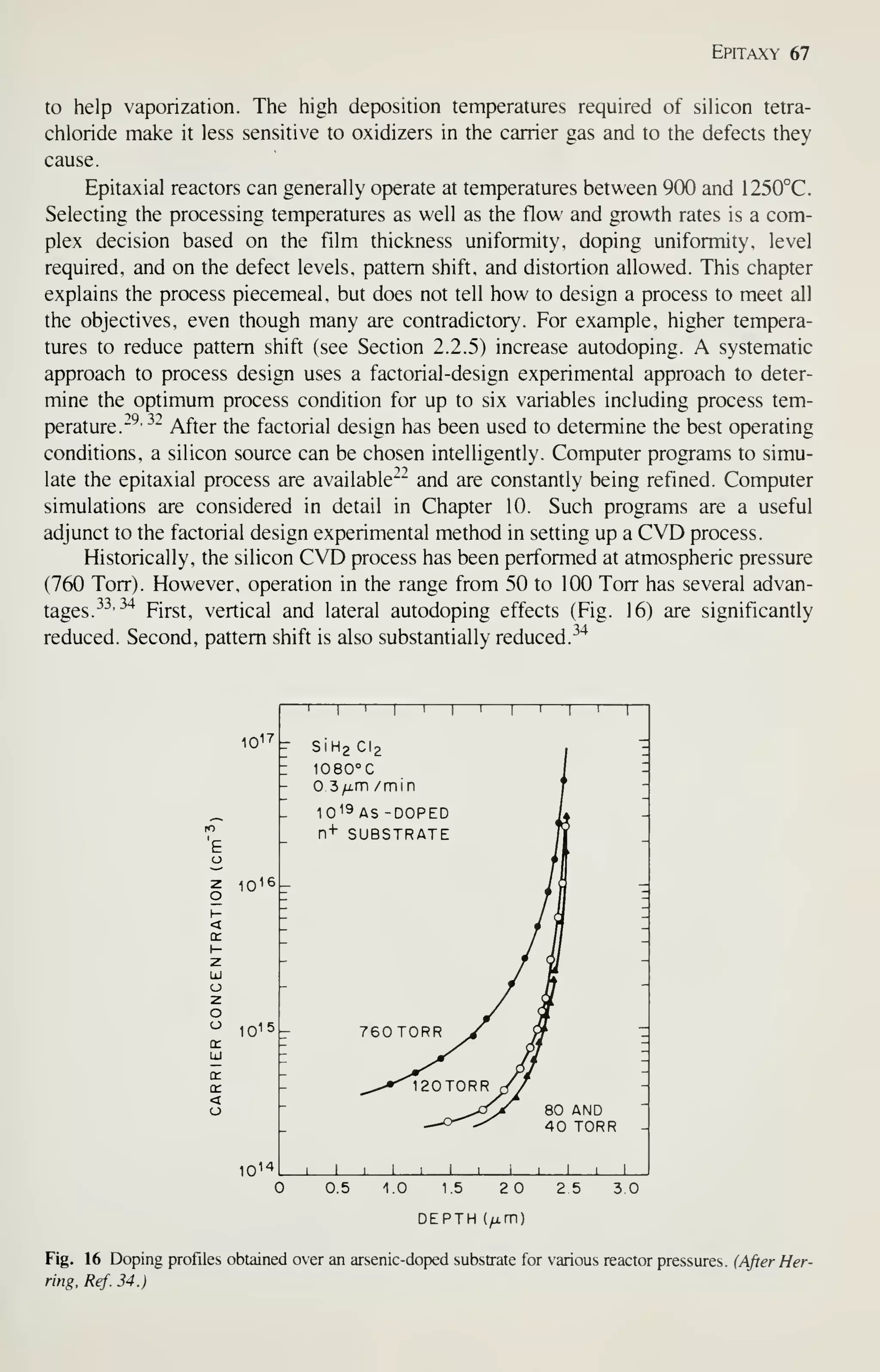

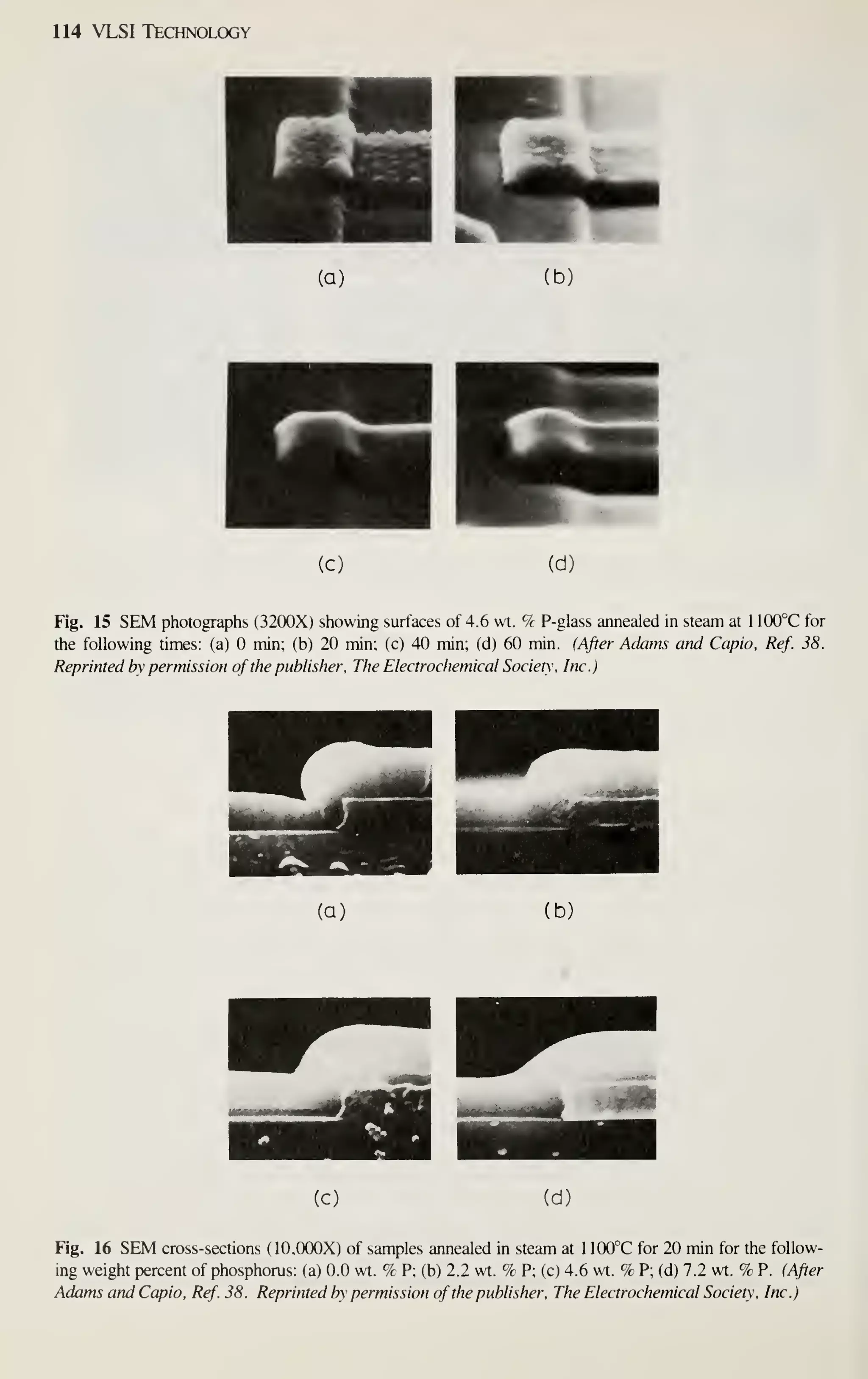

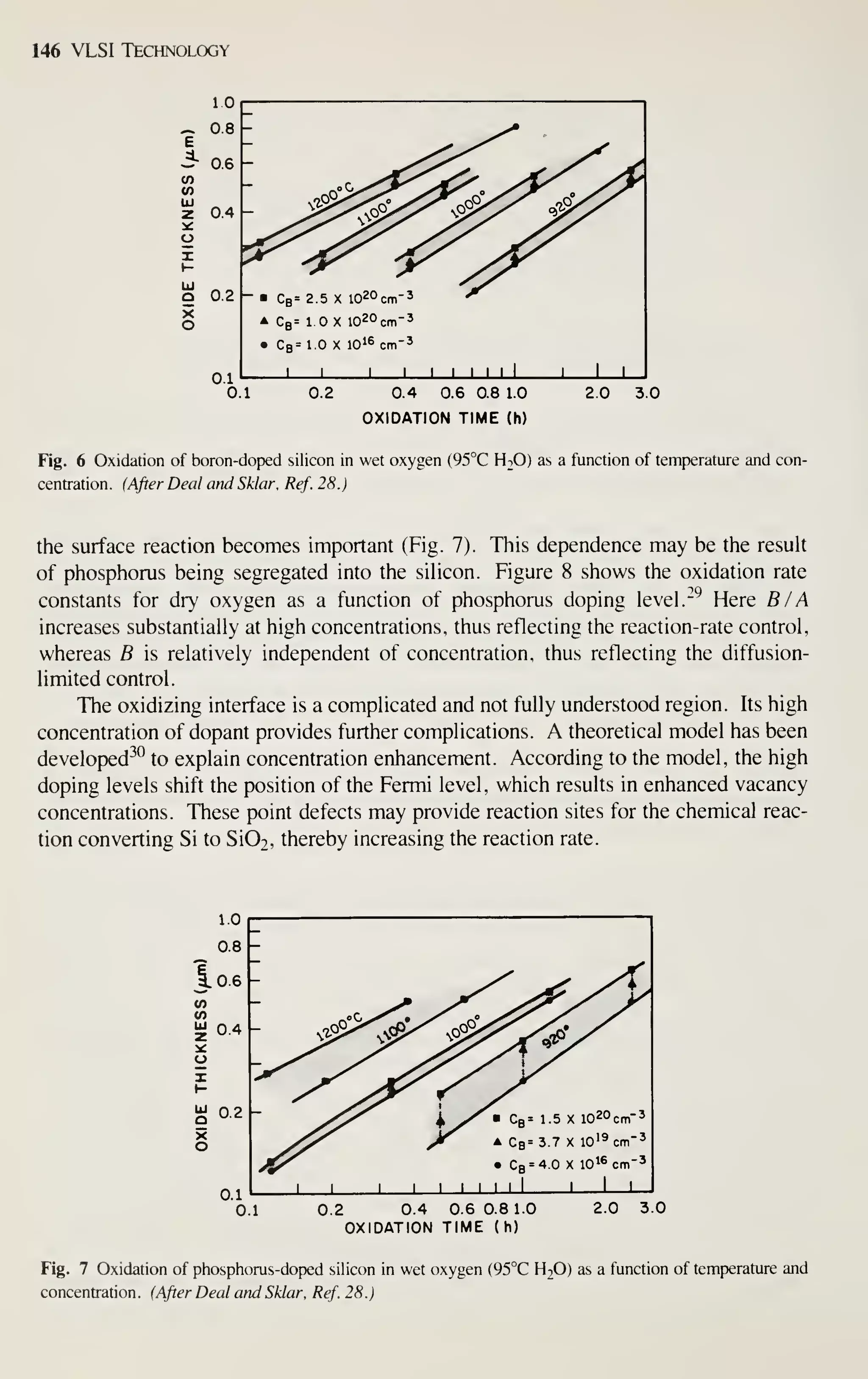

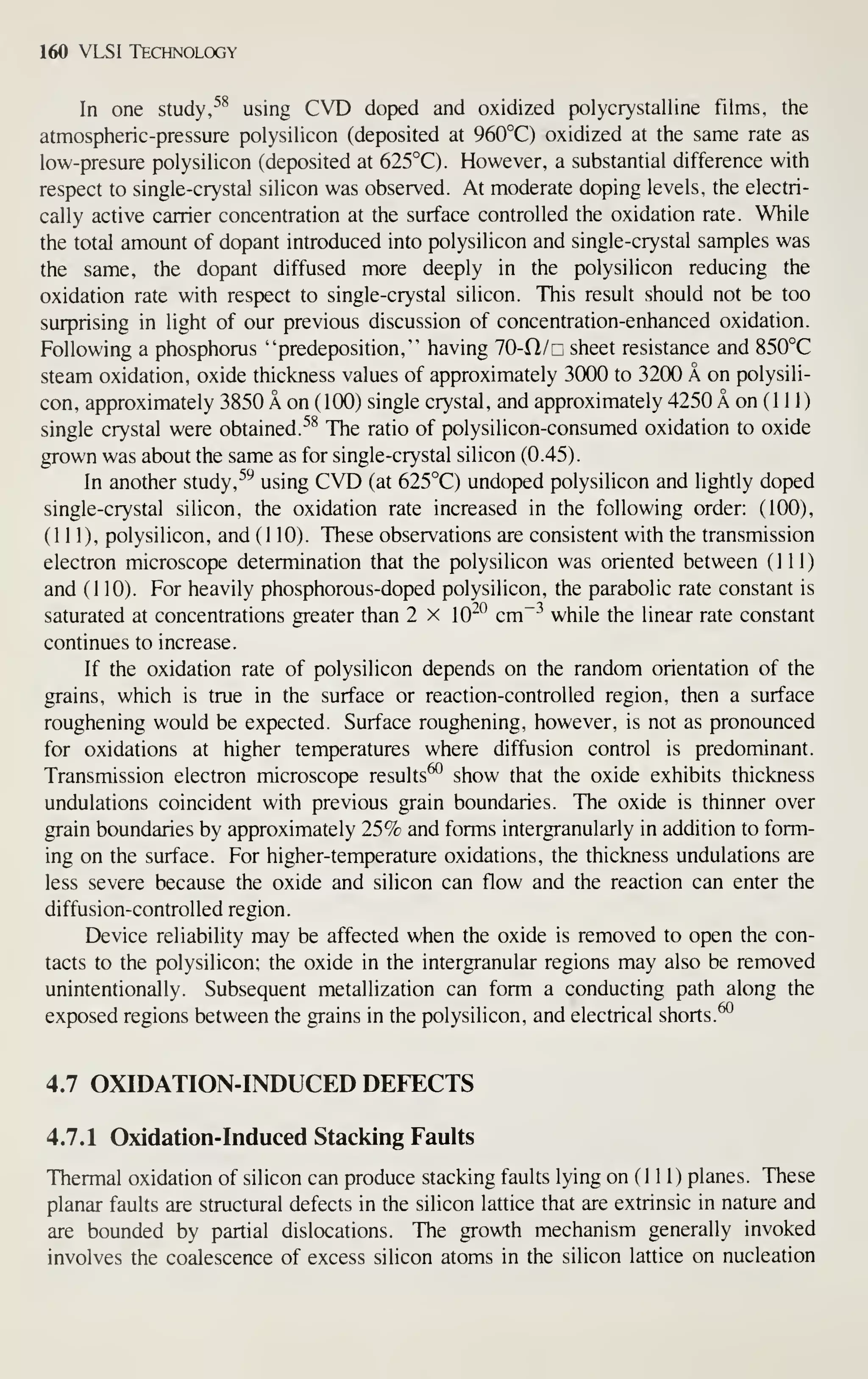

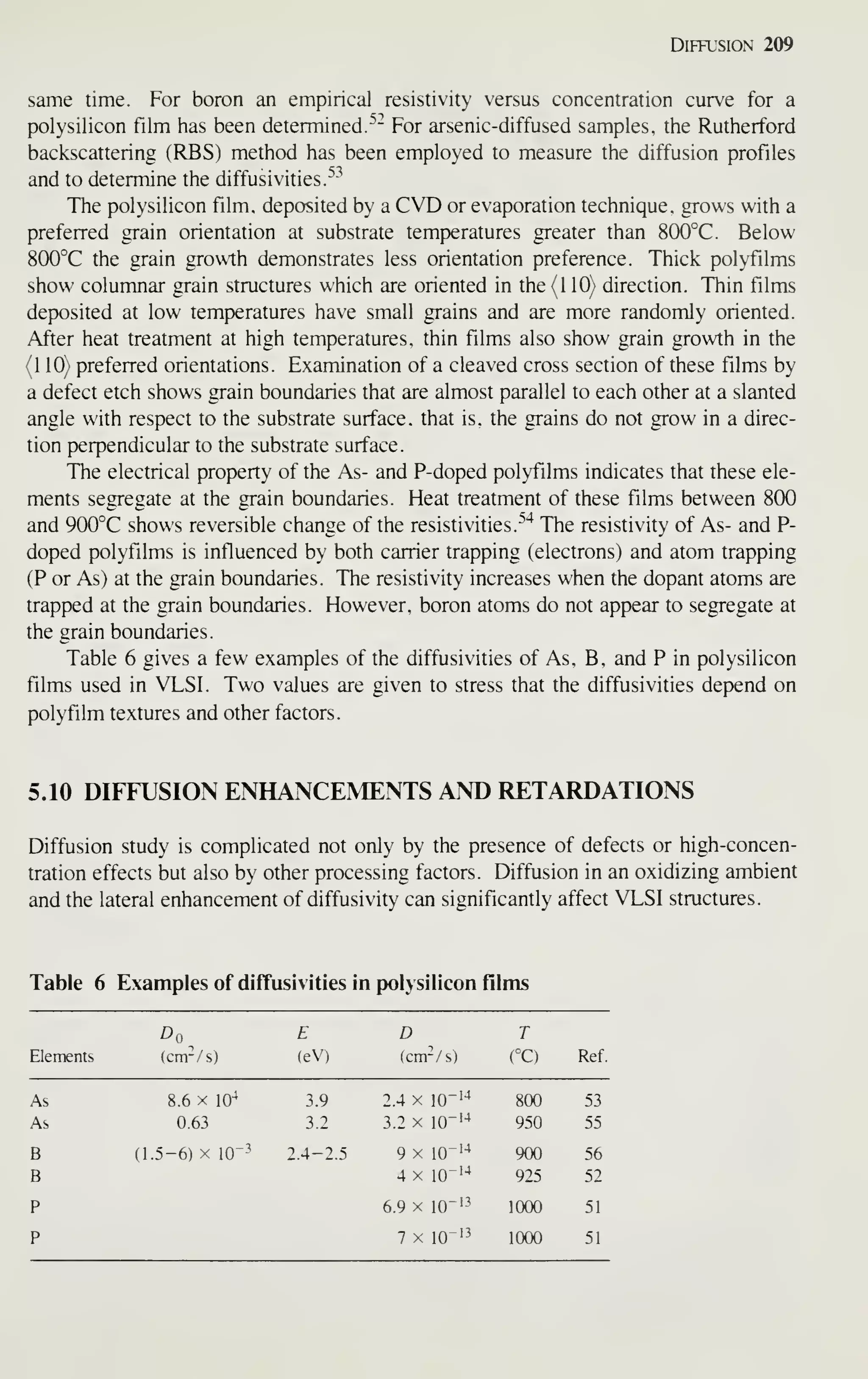

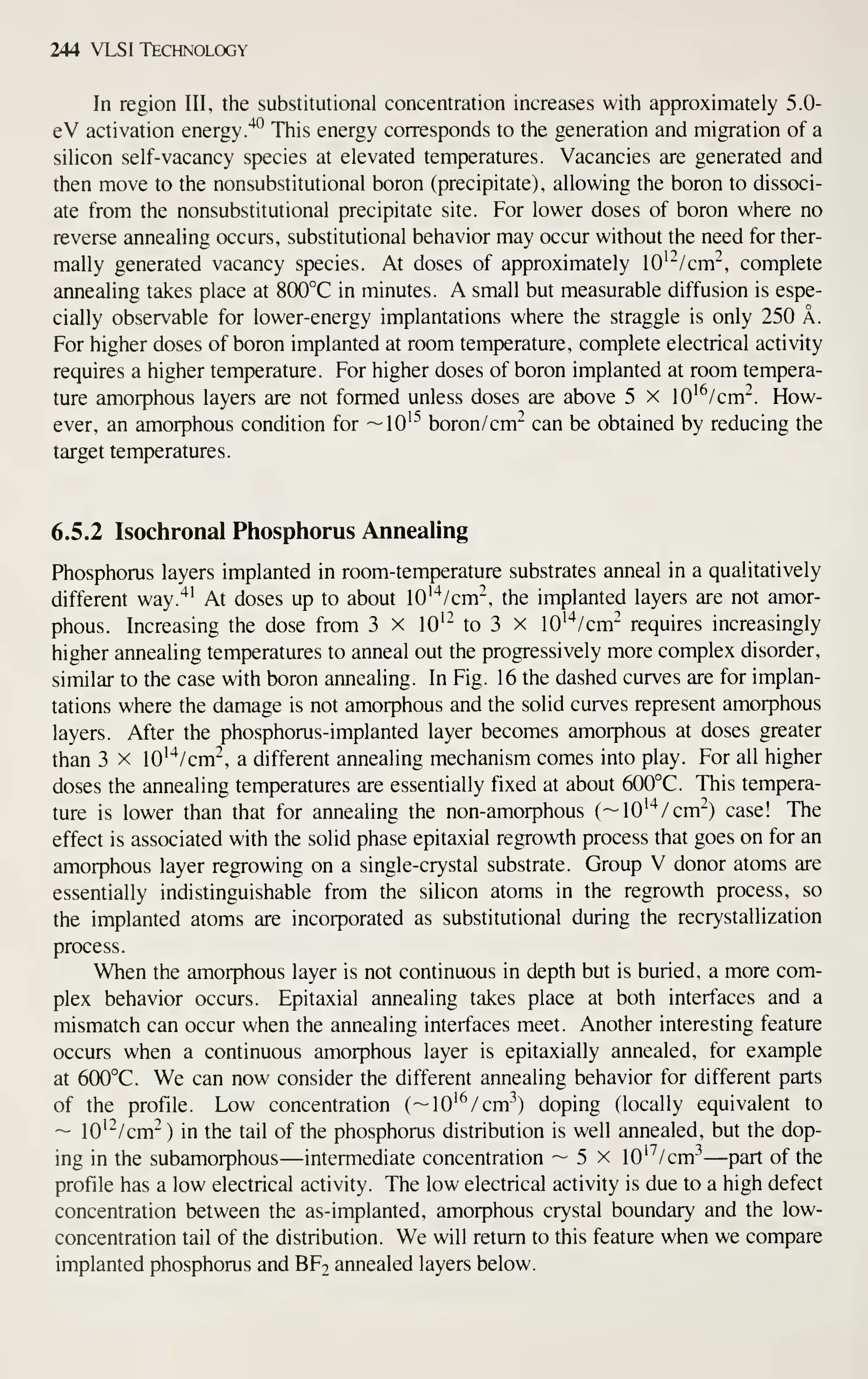

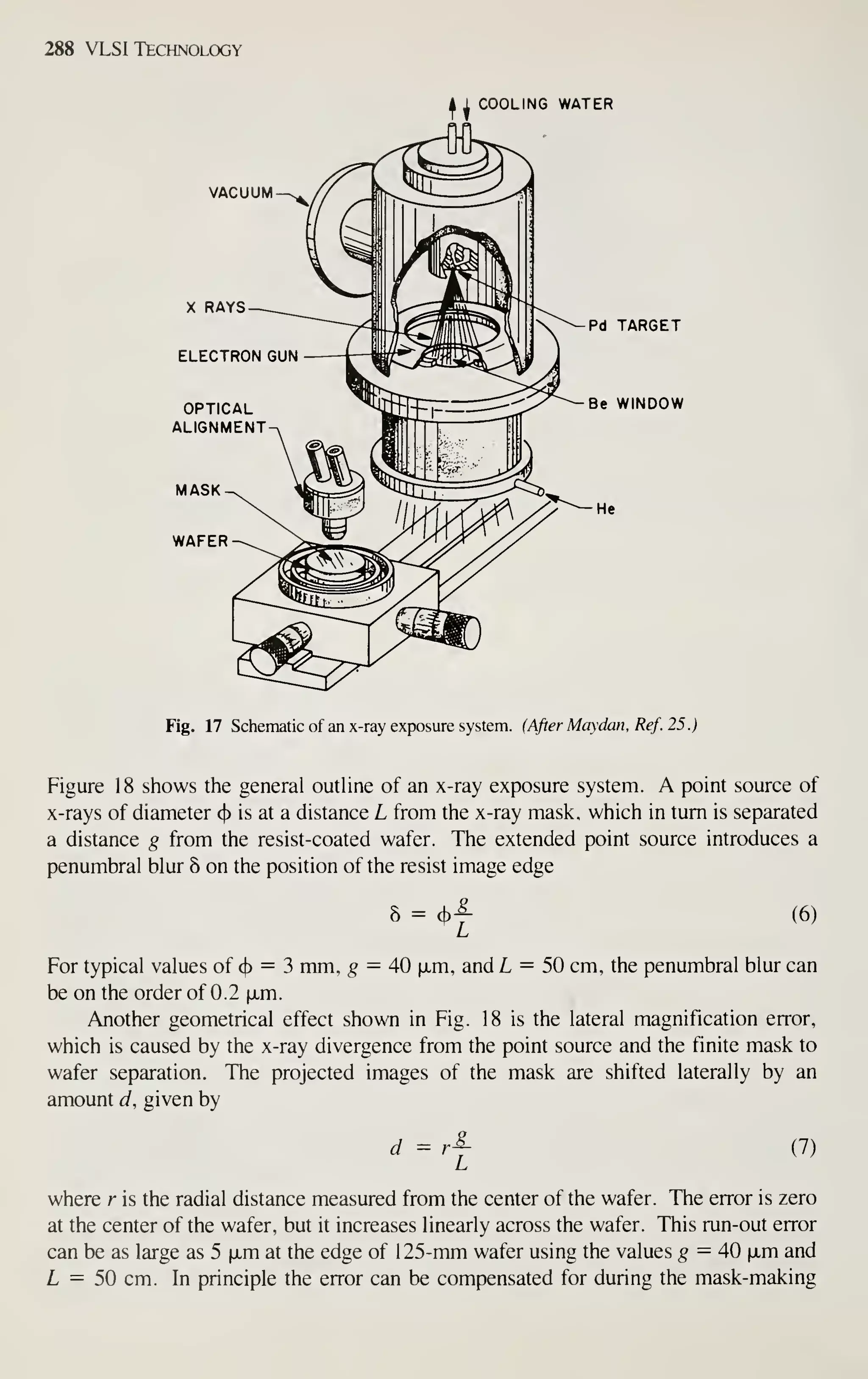

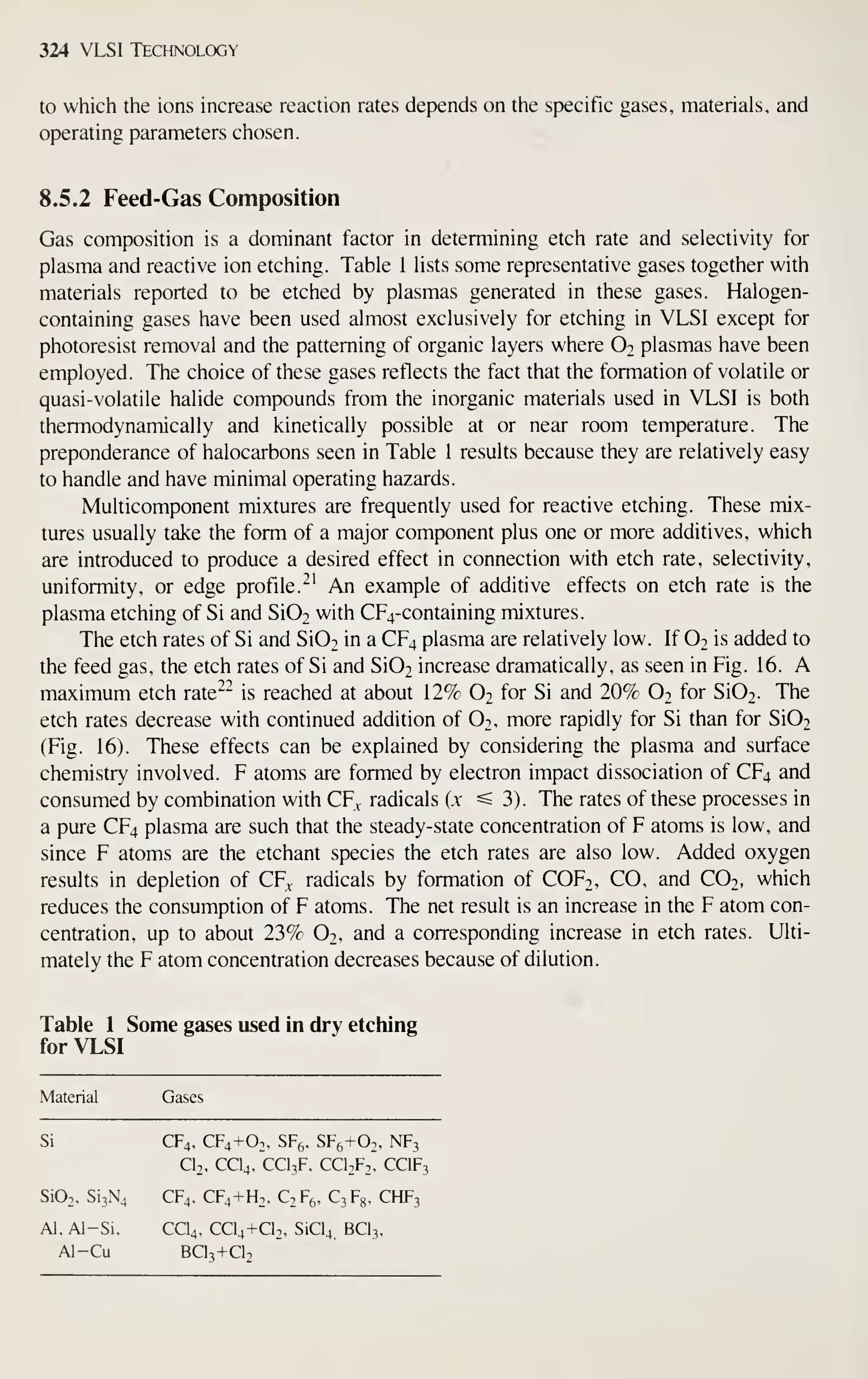

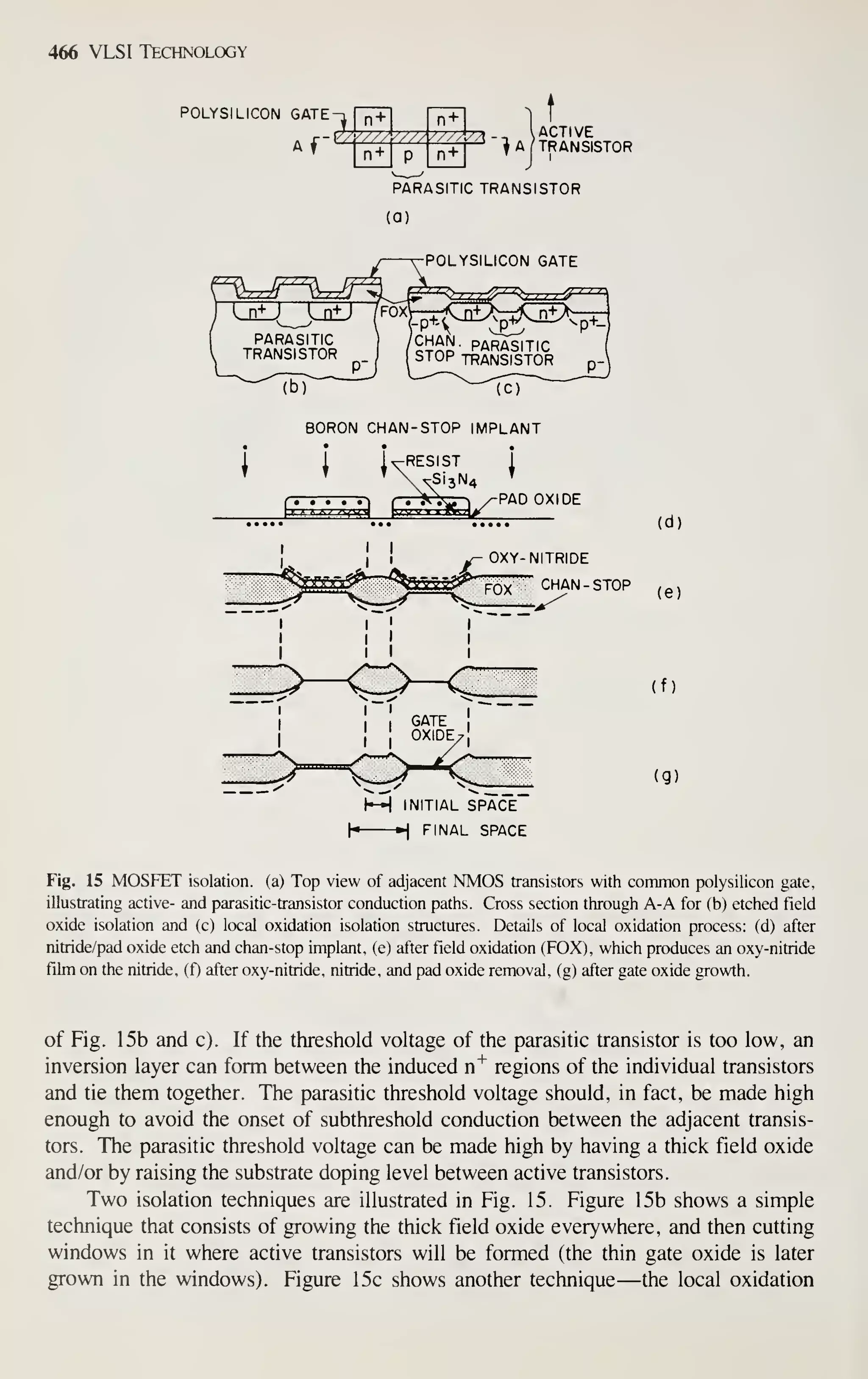

recent years.' In the 1960s the IC market was broadly based on bipolar transistors.

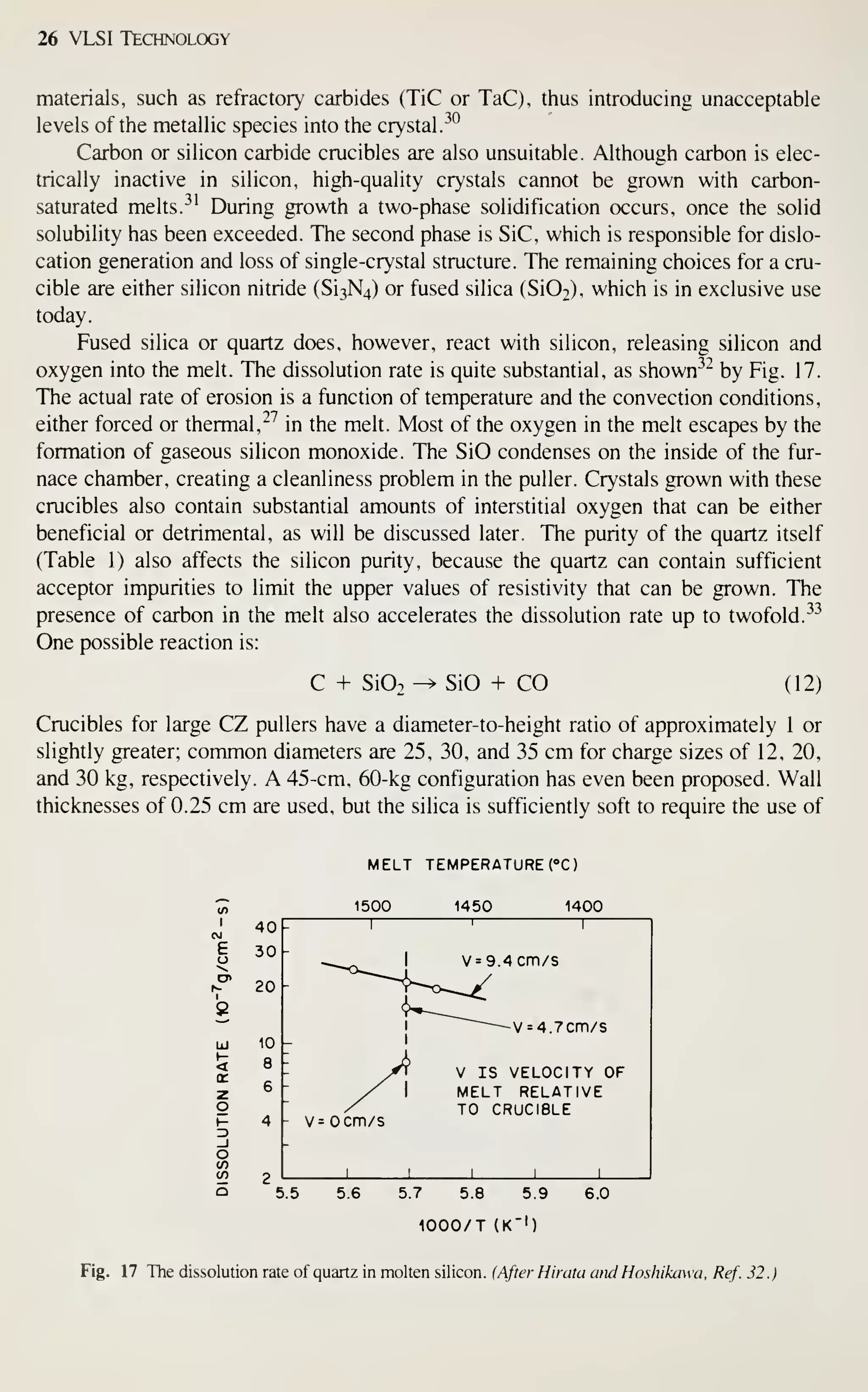

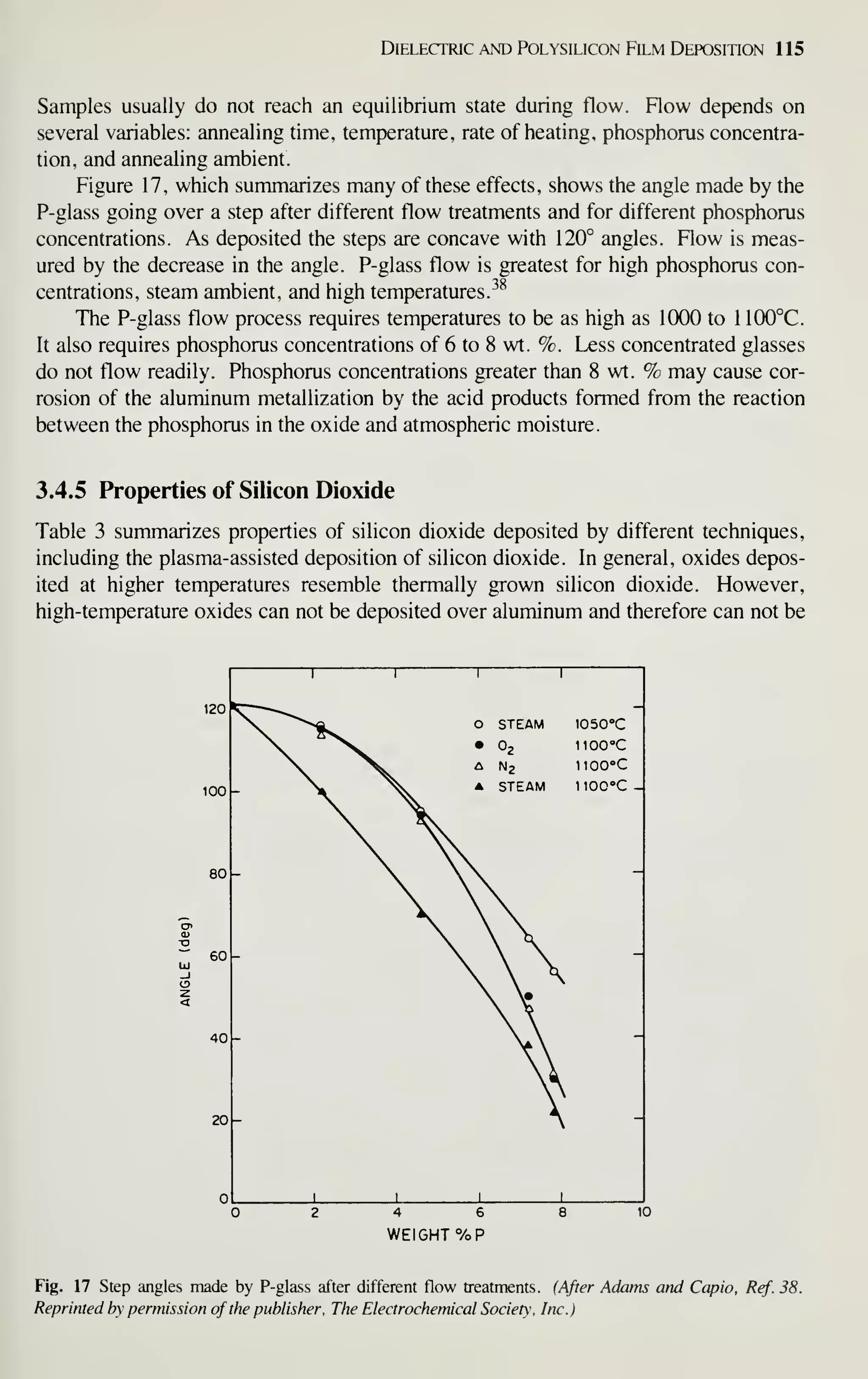

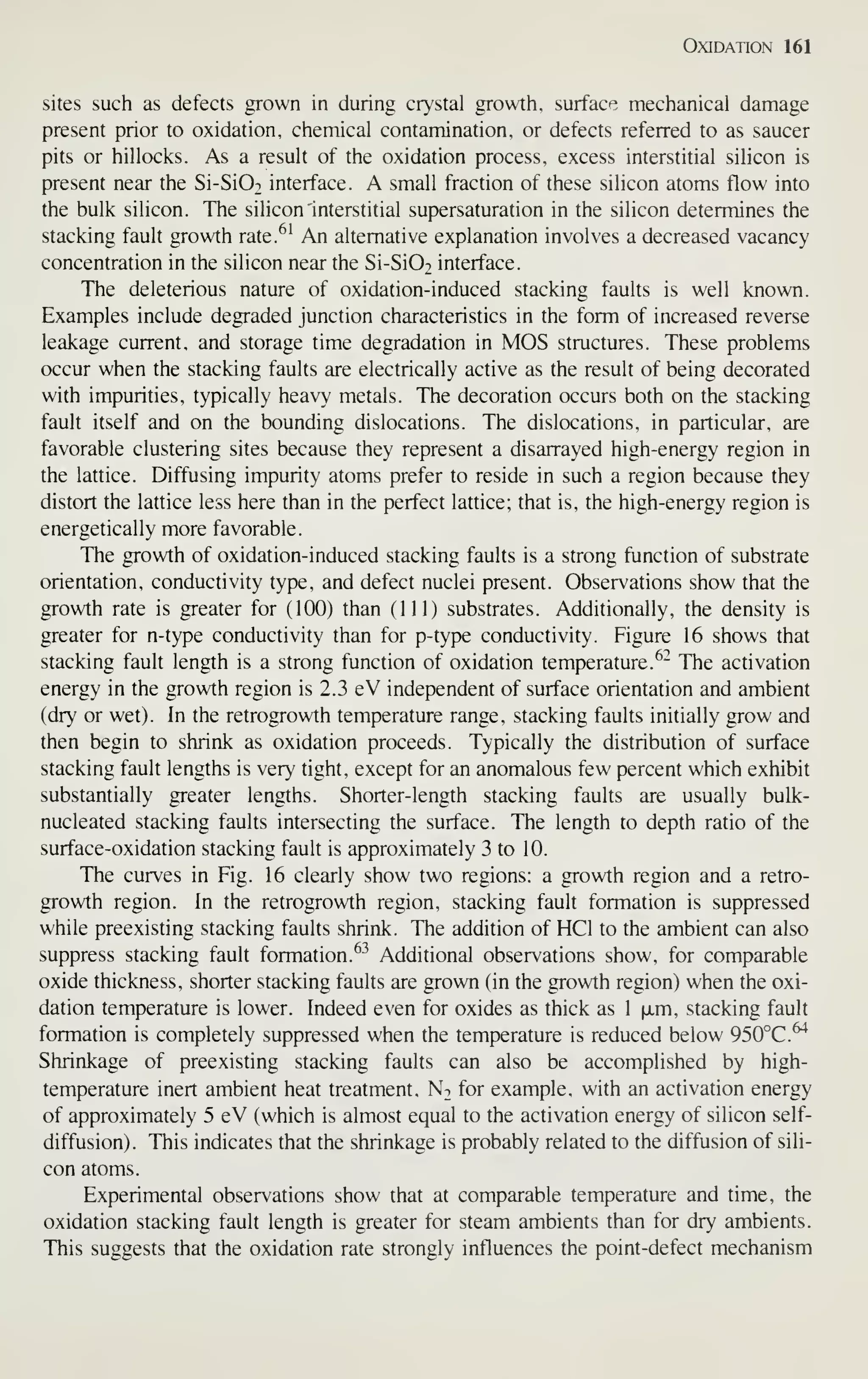

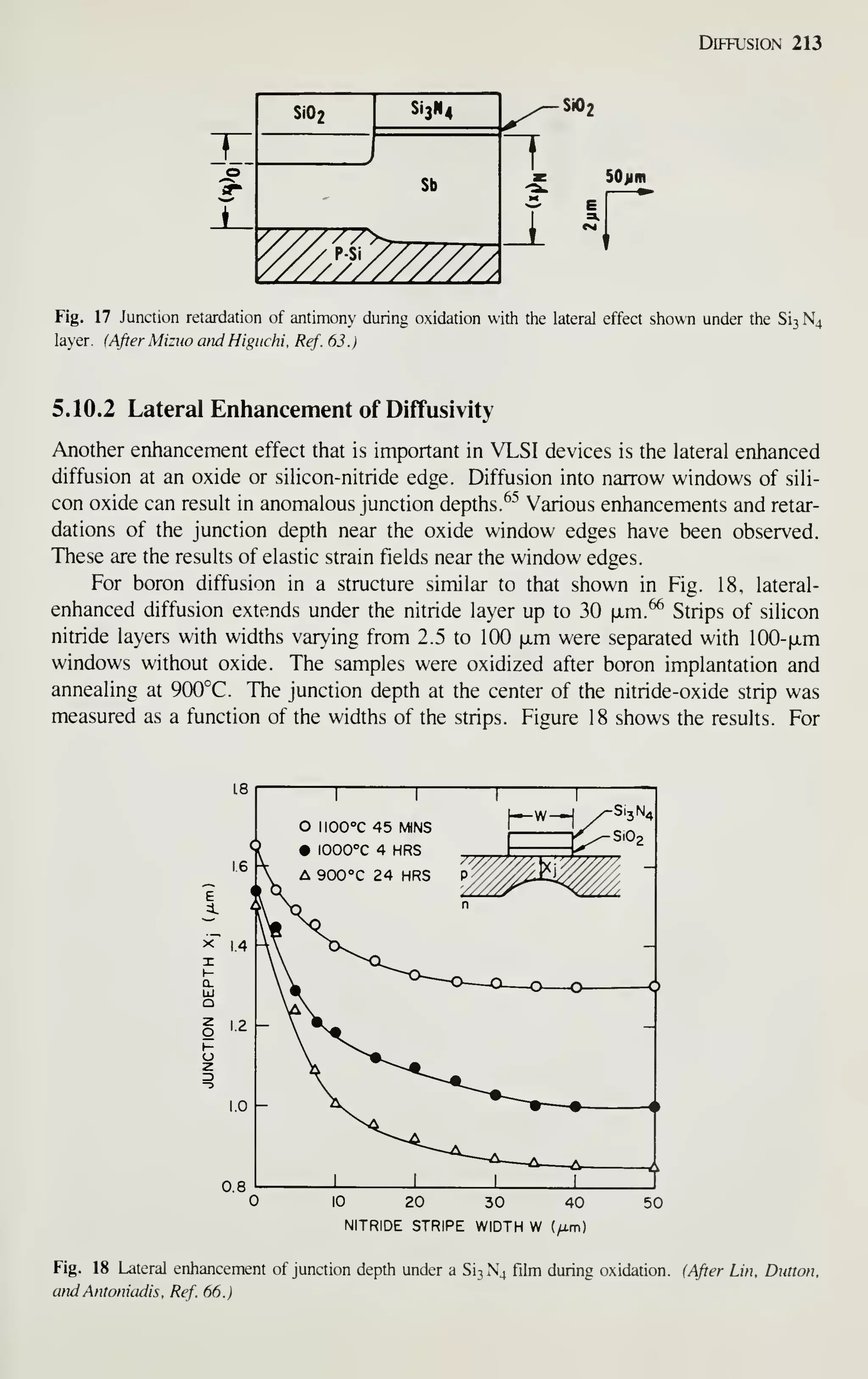

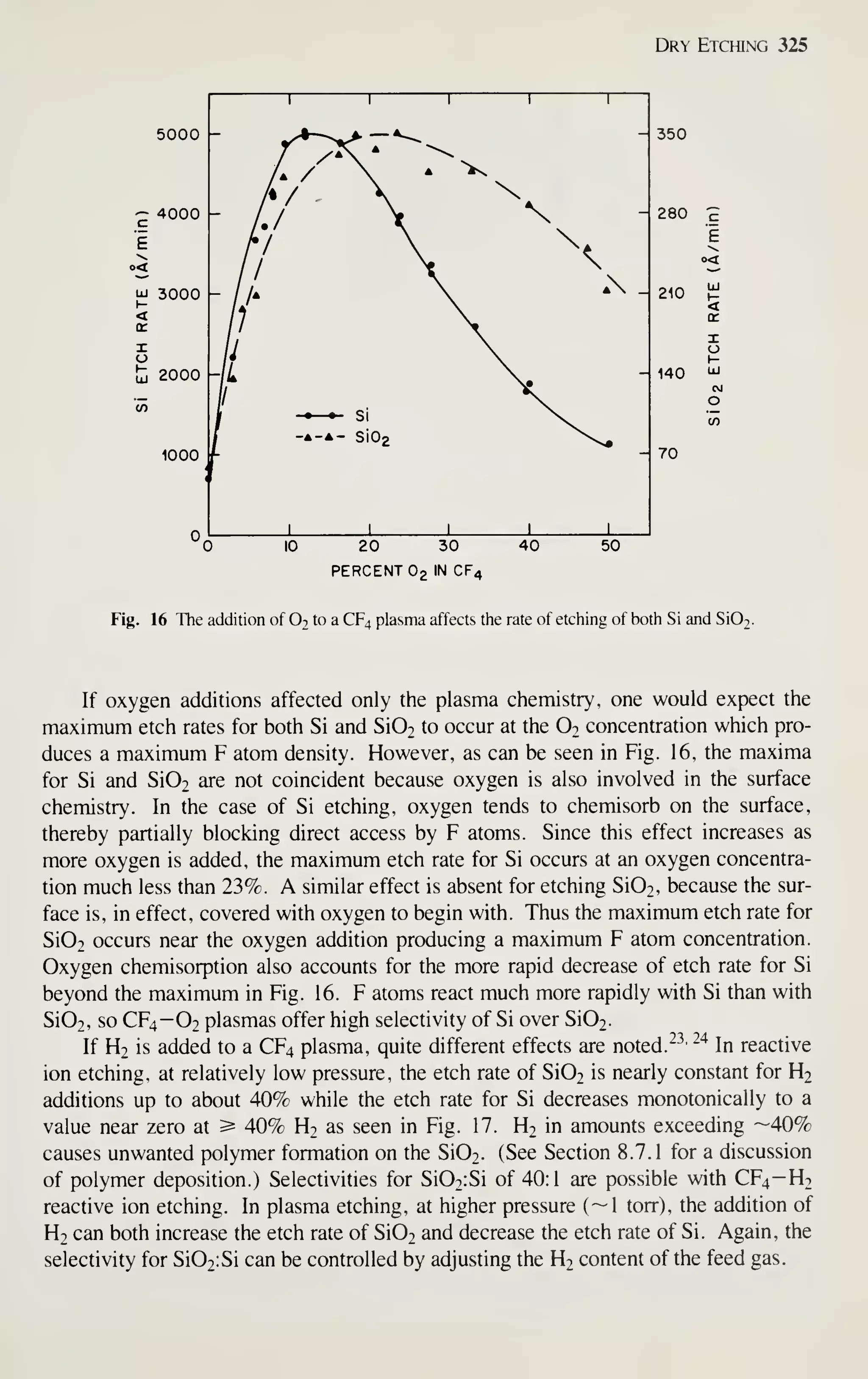

Since 1975, however, digital MOS ICs have prevailed. At present, even the intrinsic

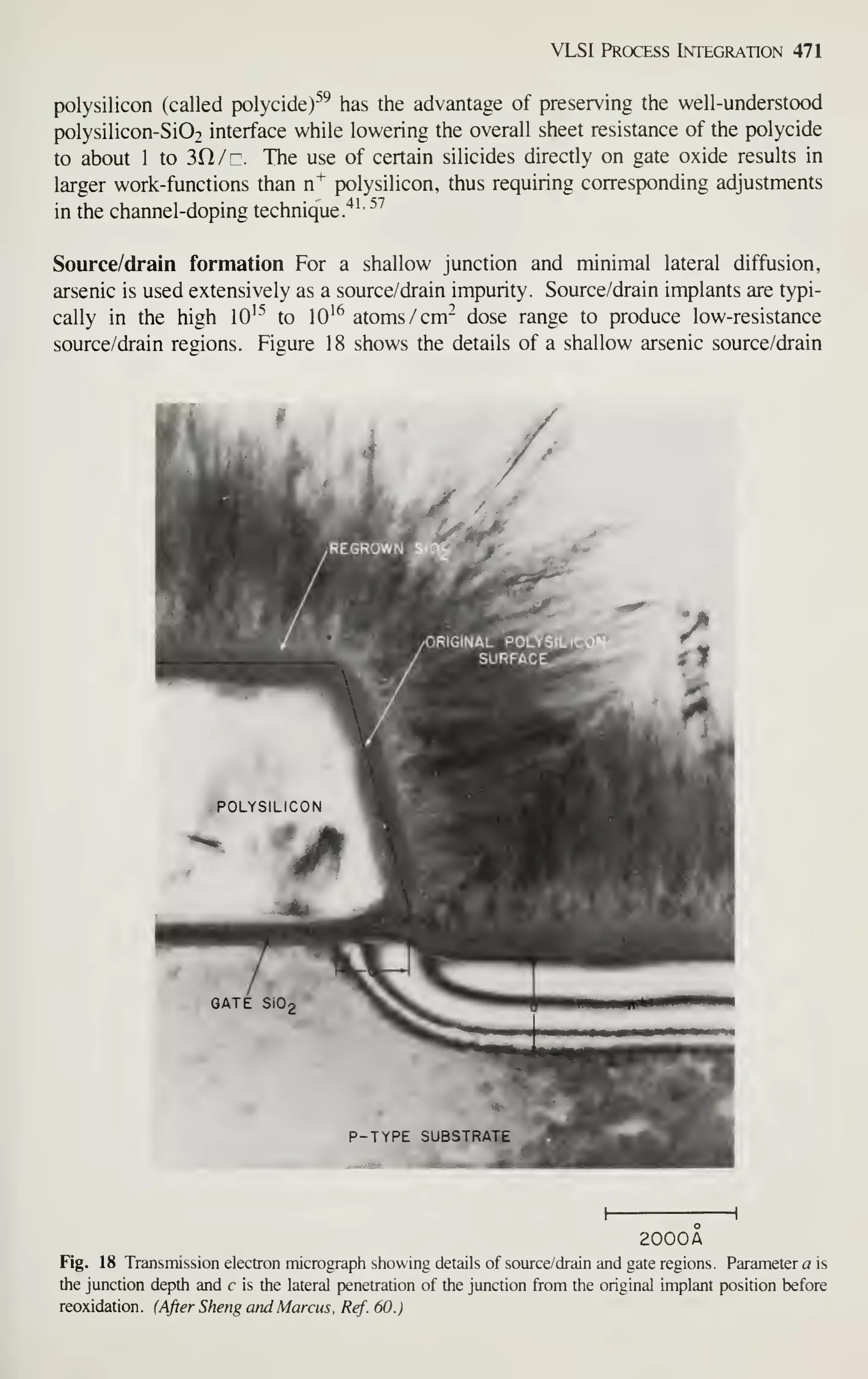

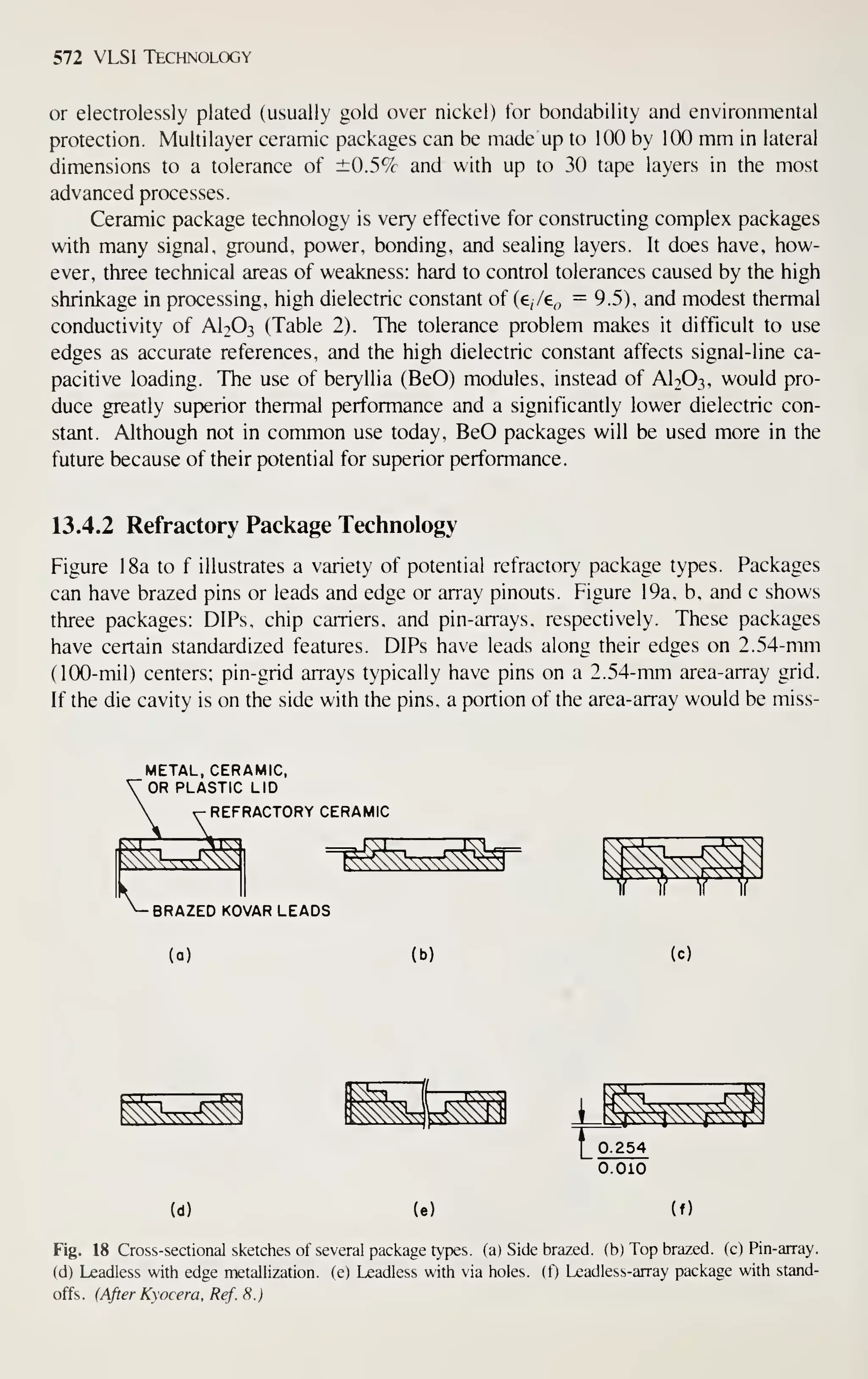

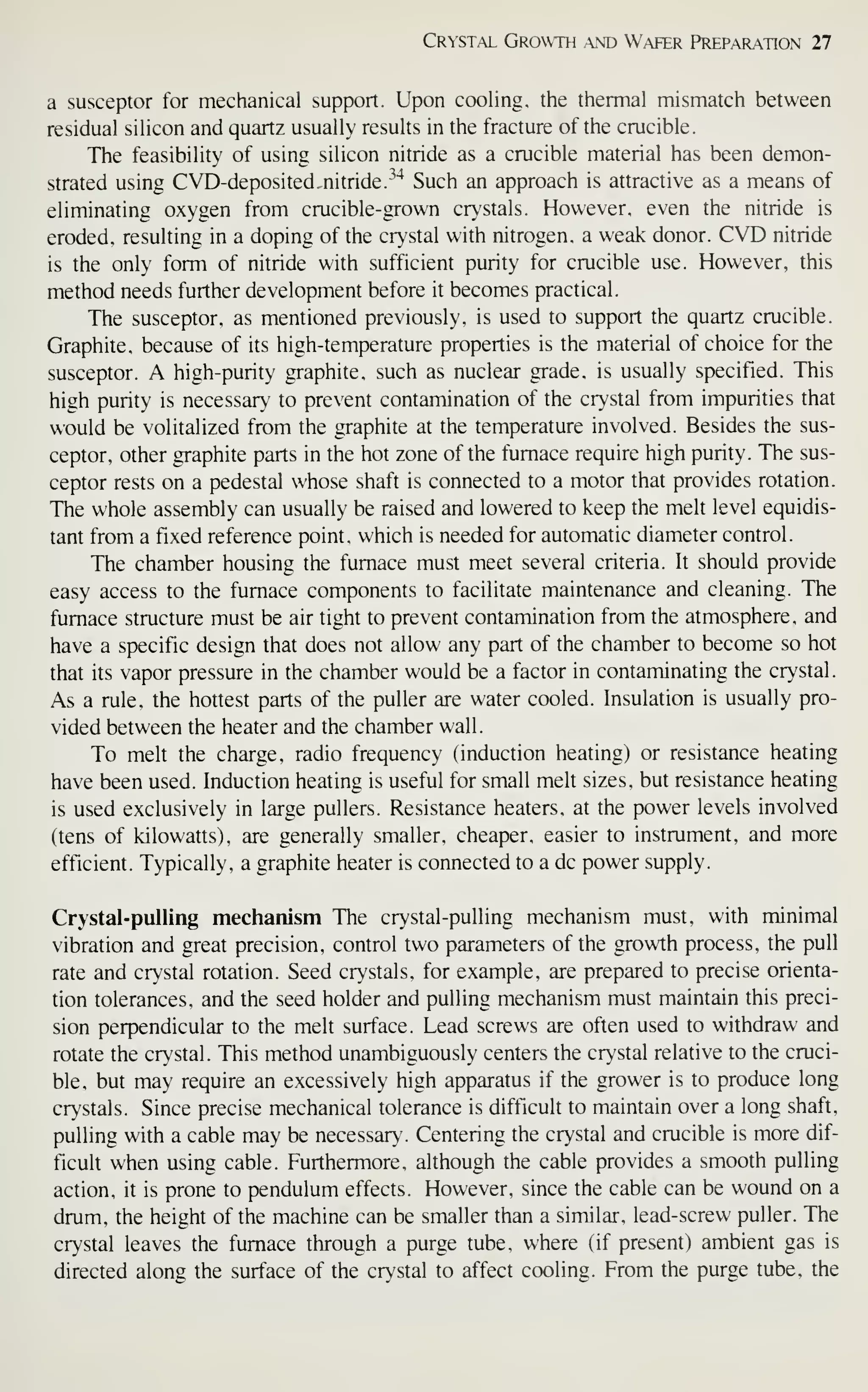

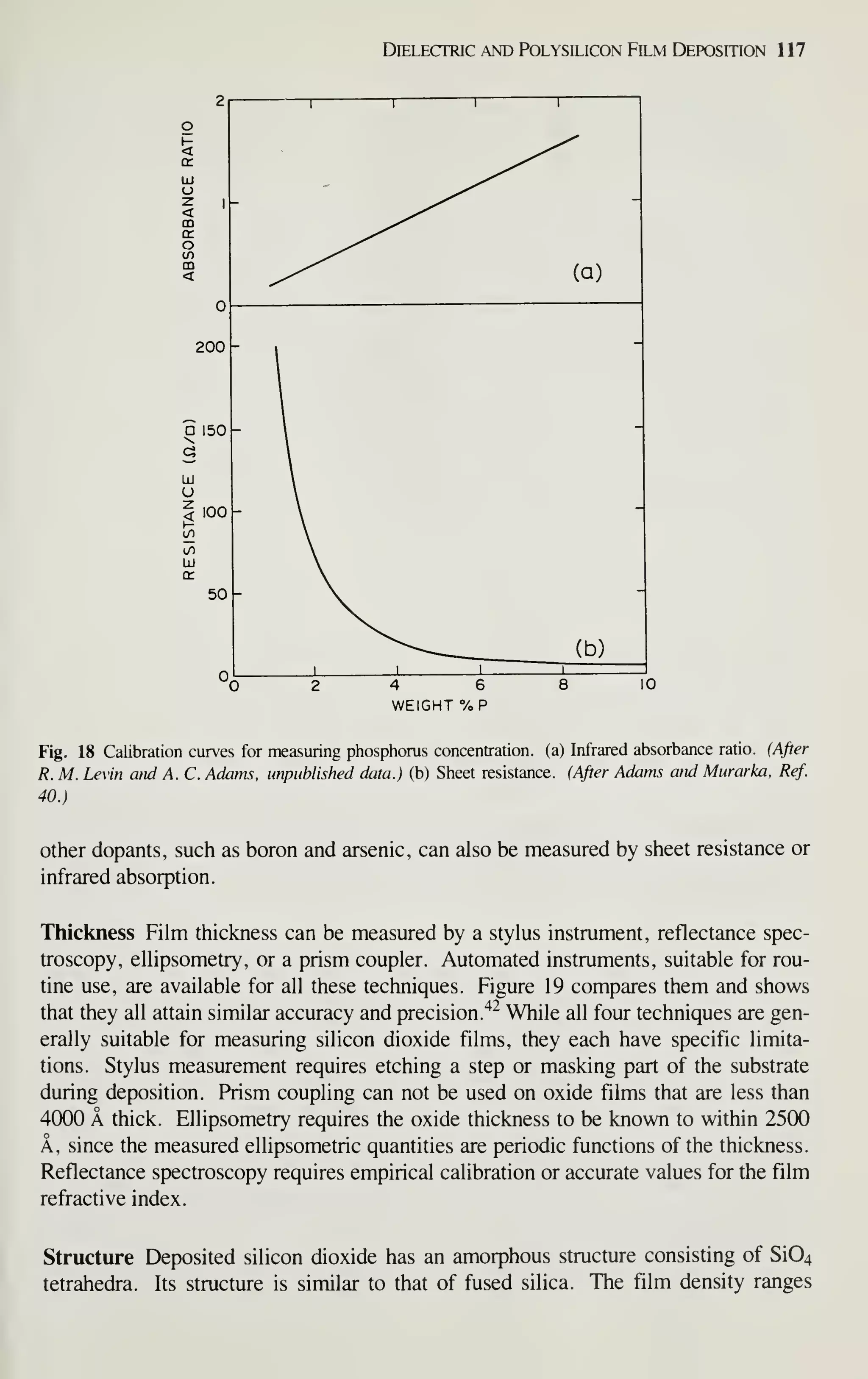

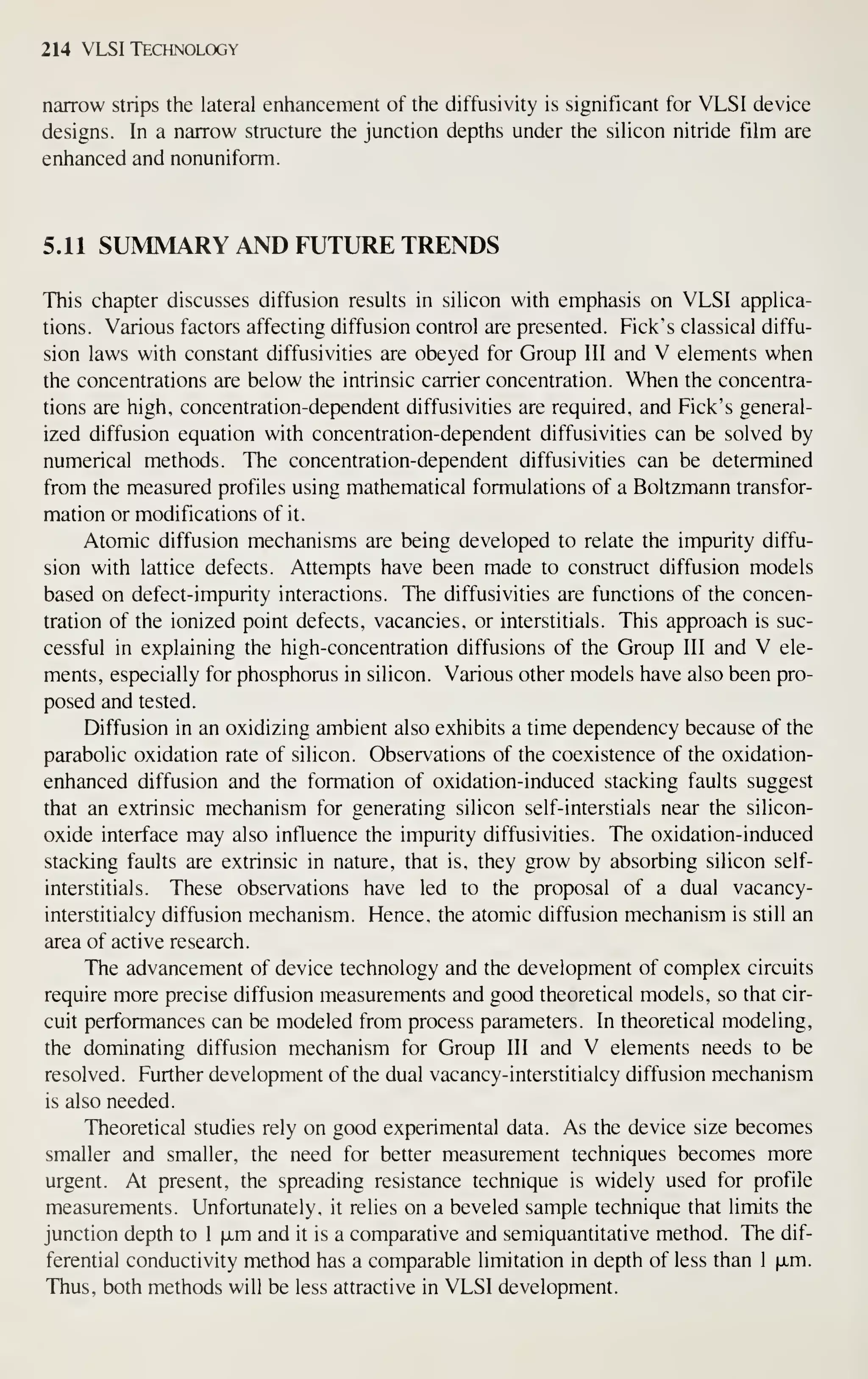

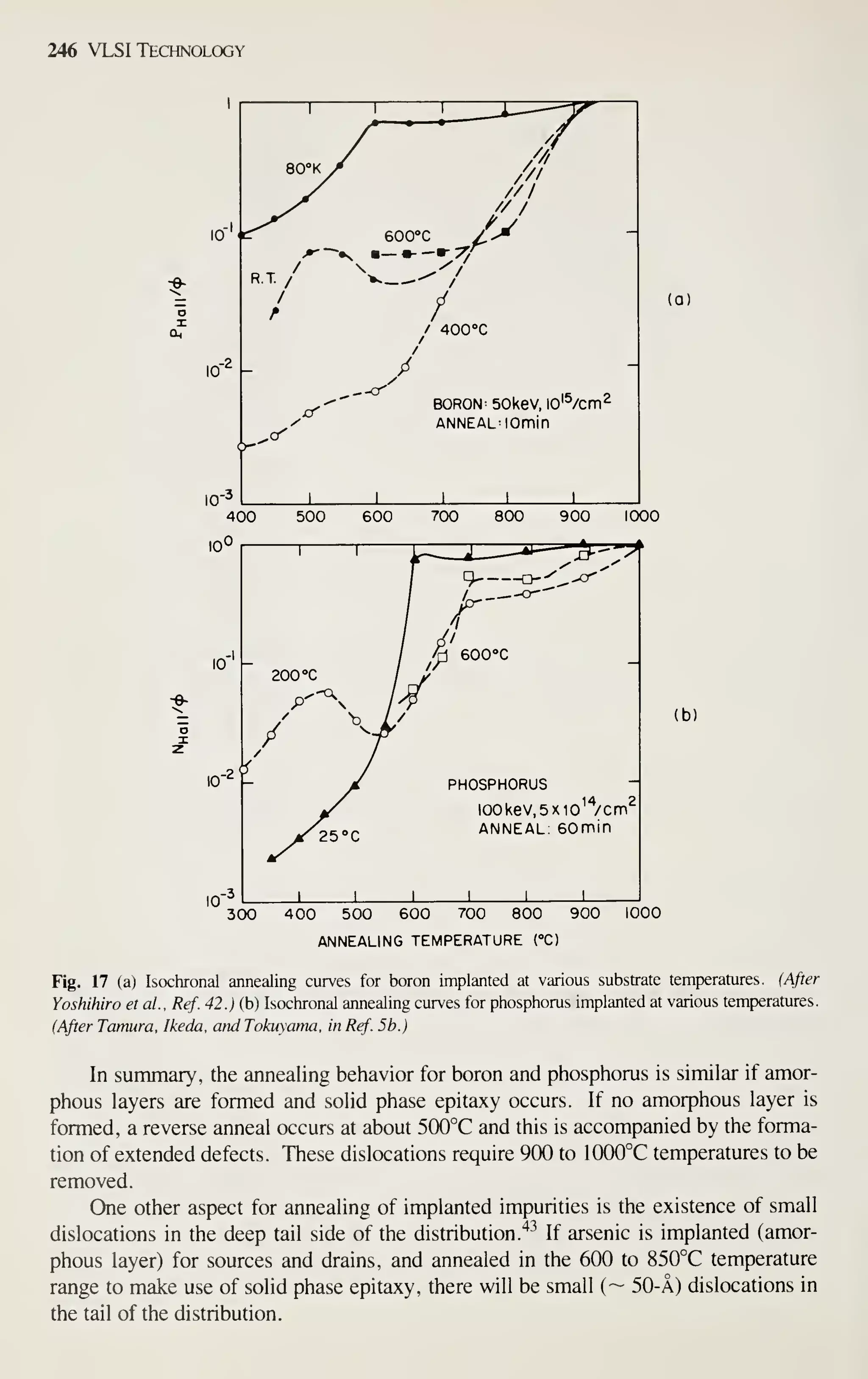

speed advantage of bipolar transistors is being challenged by MOSFETs. Because of

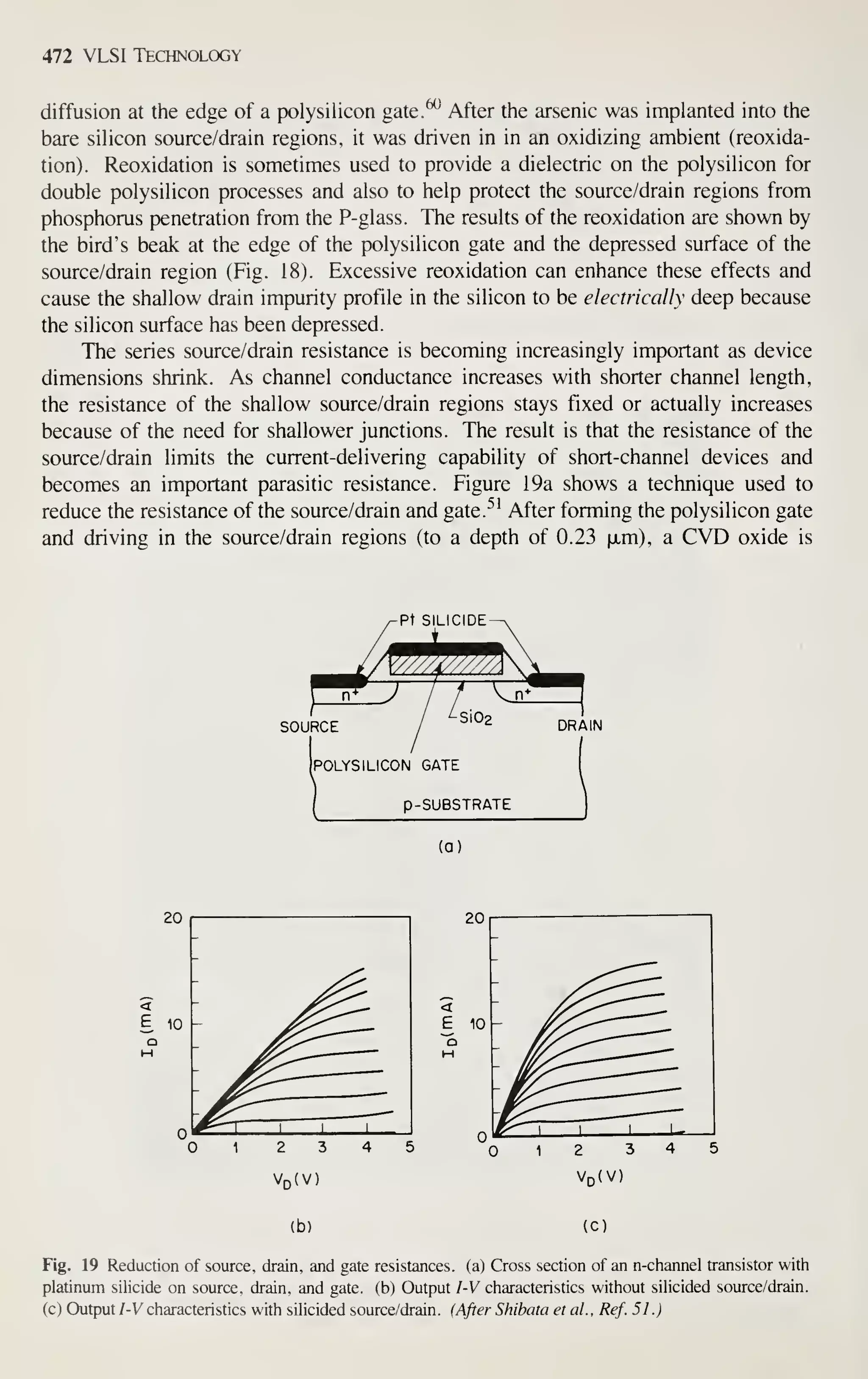

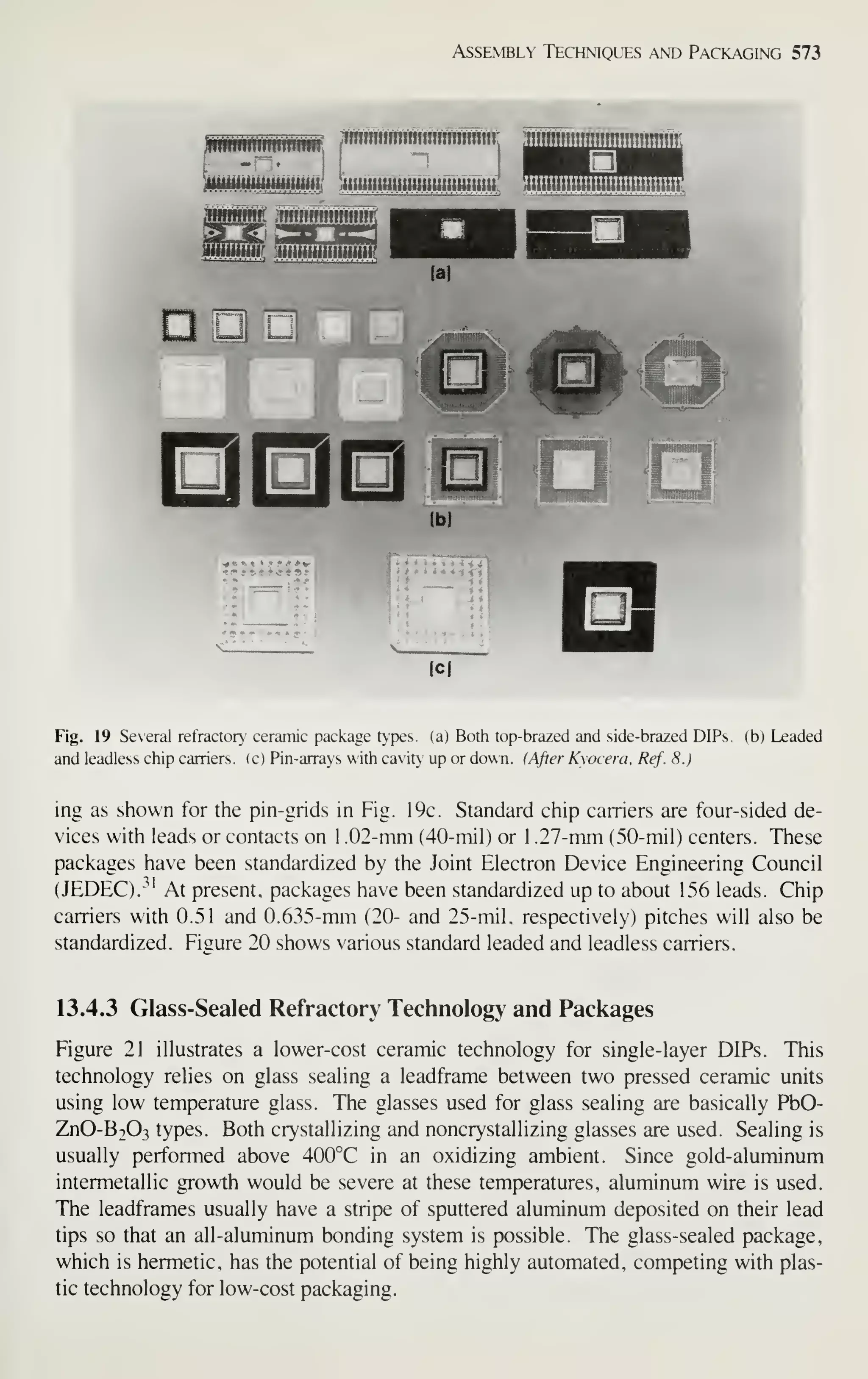

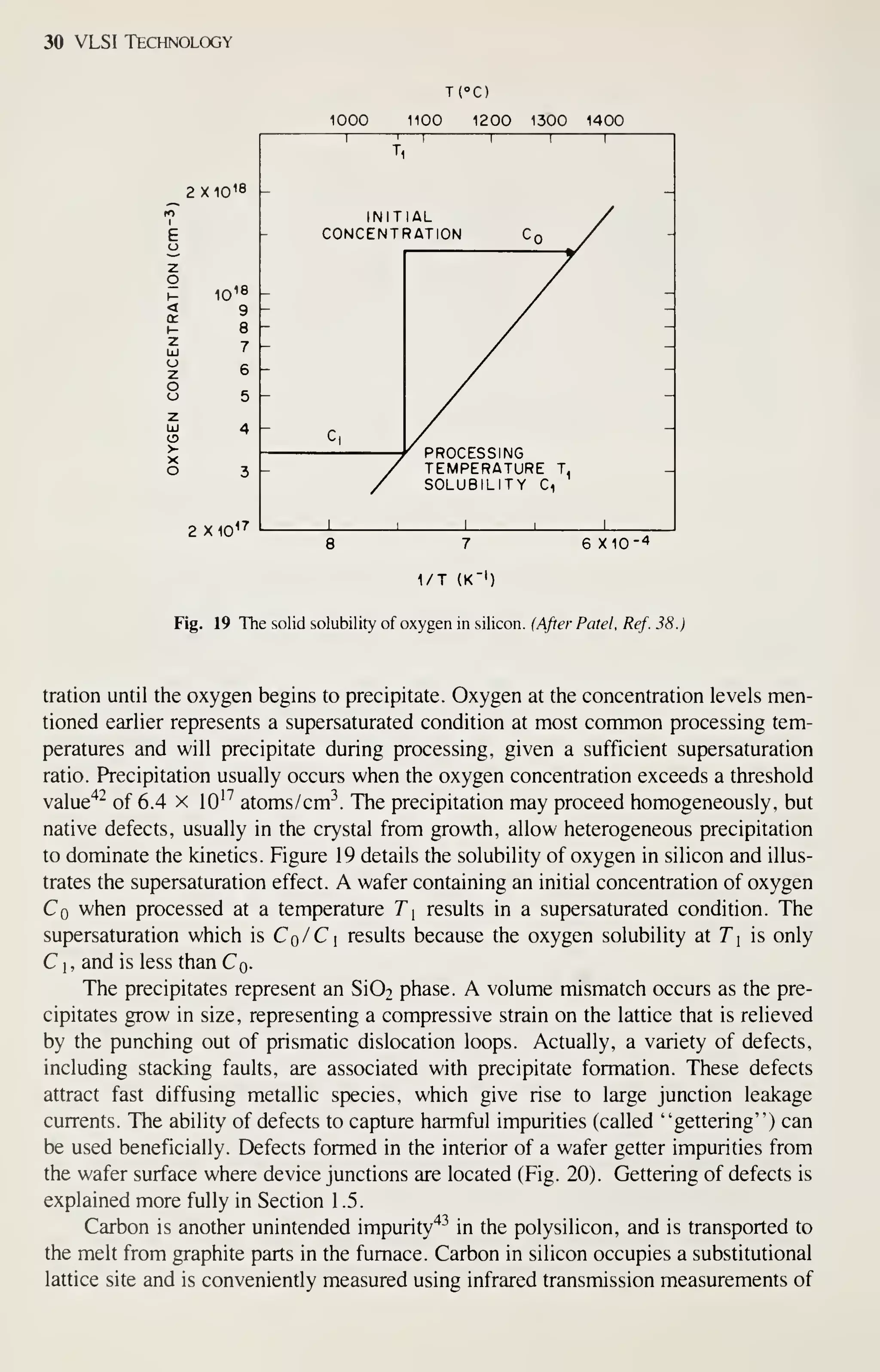

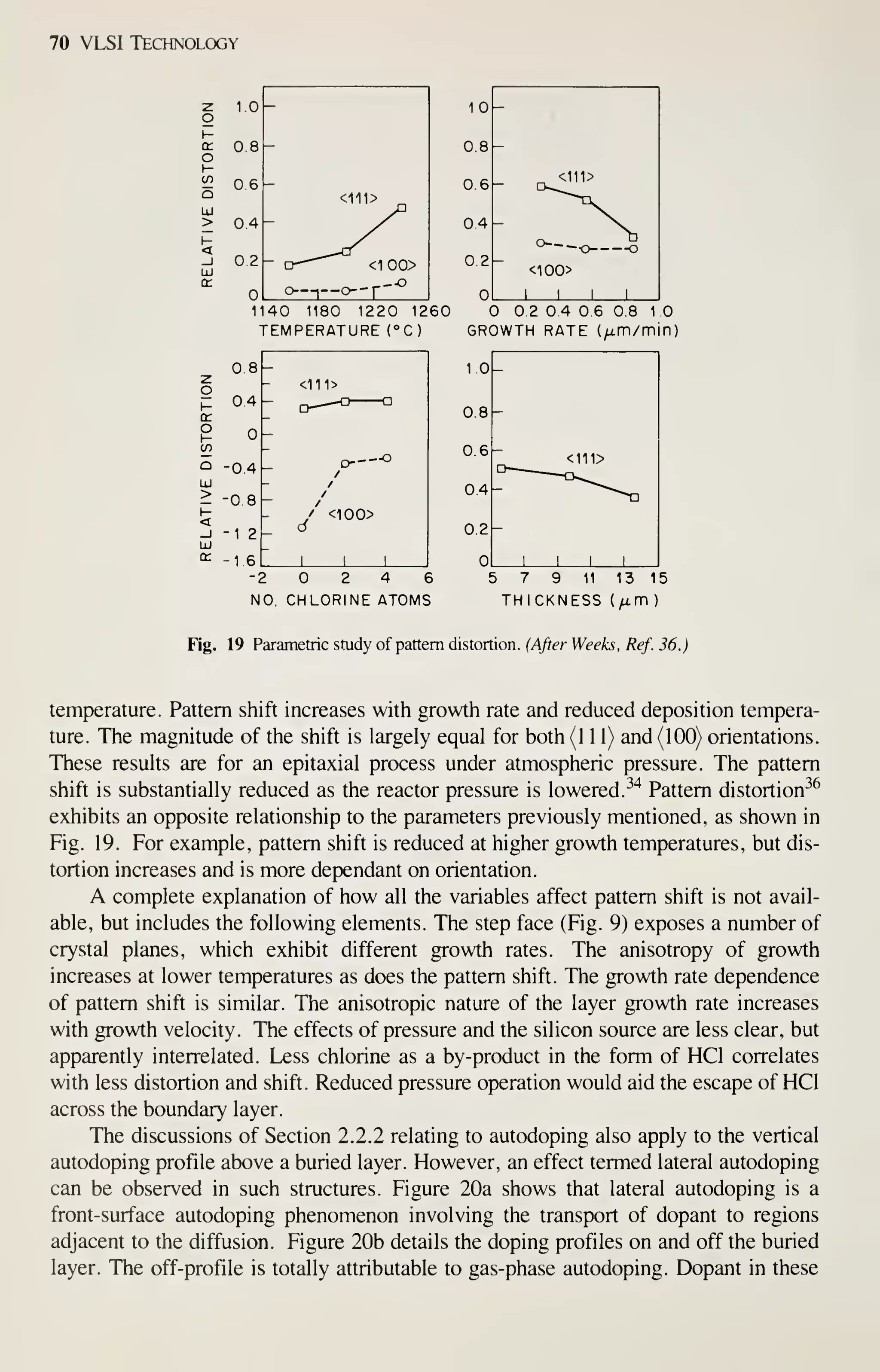

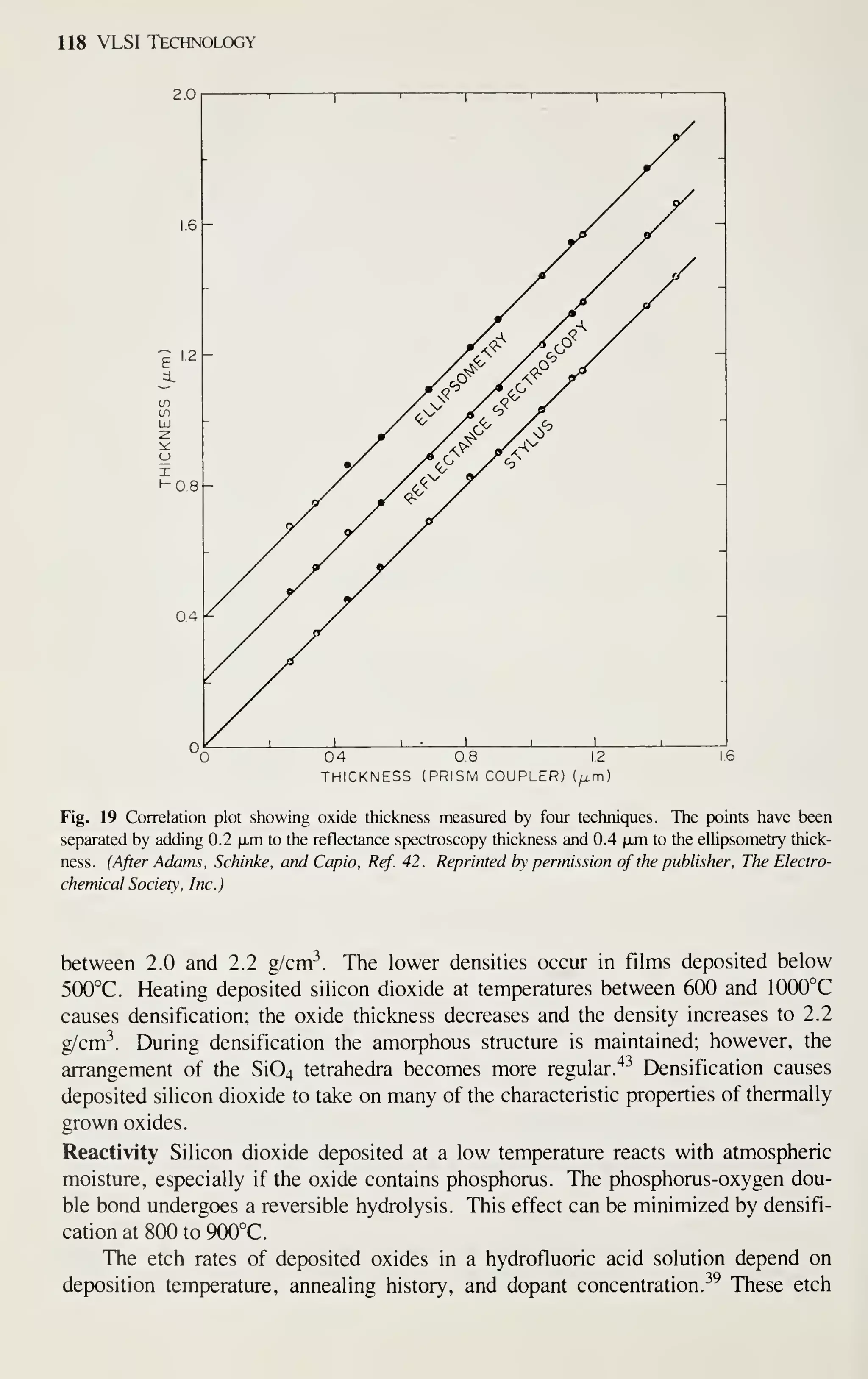

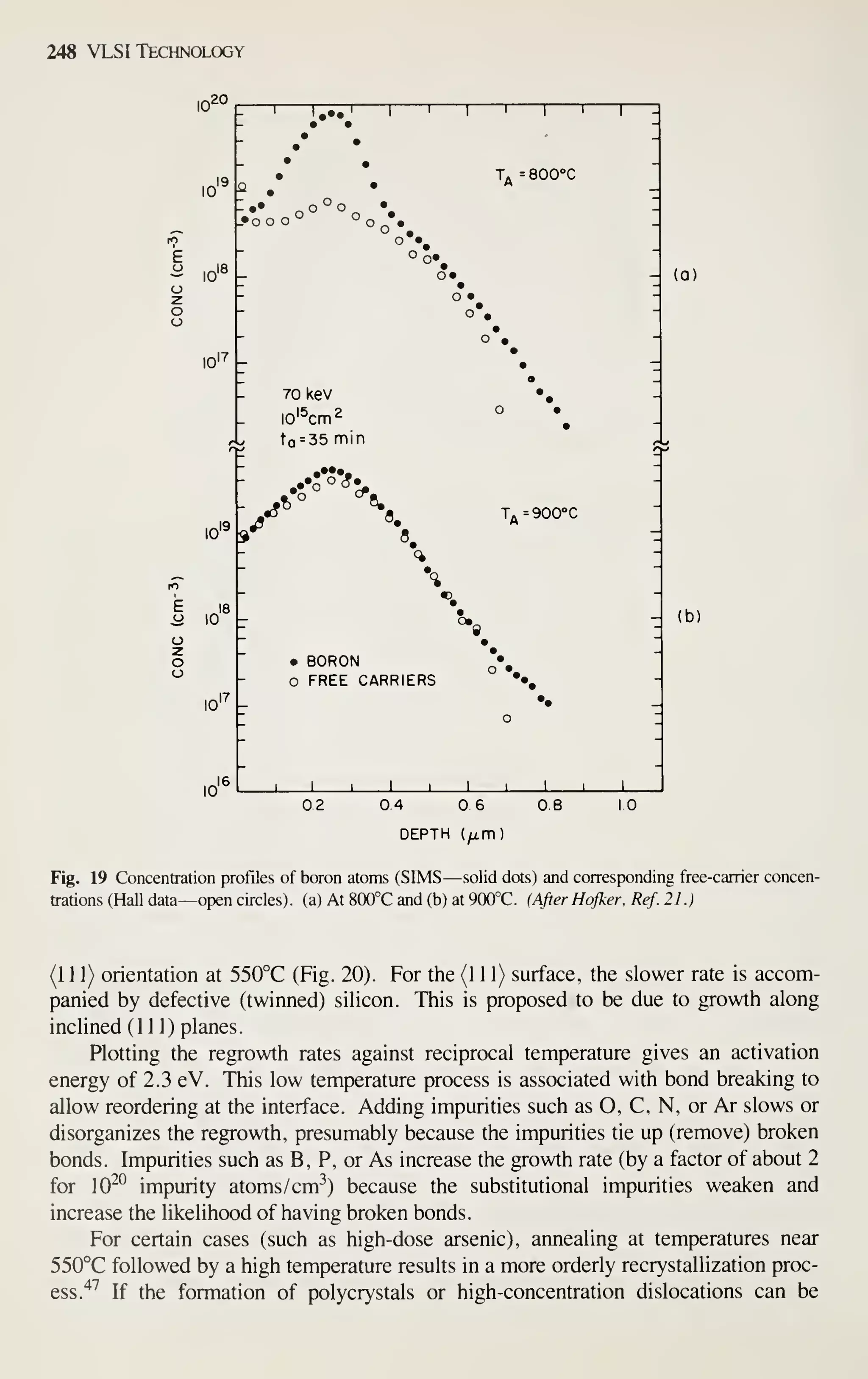

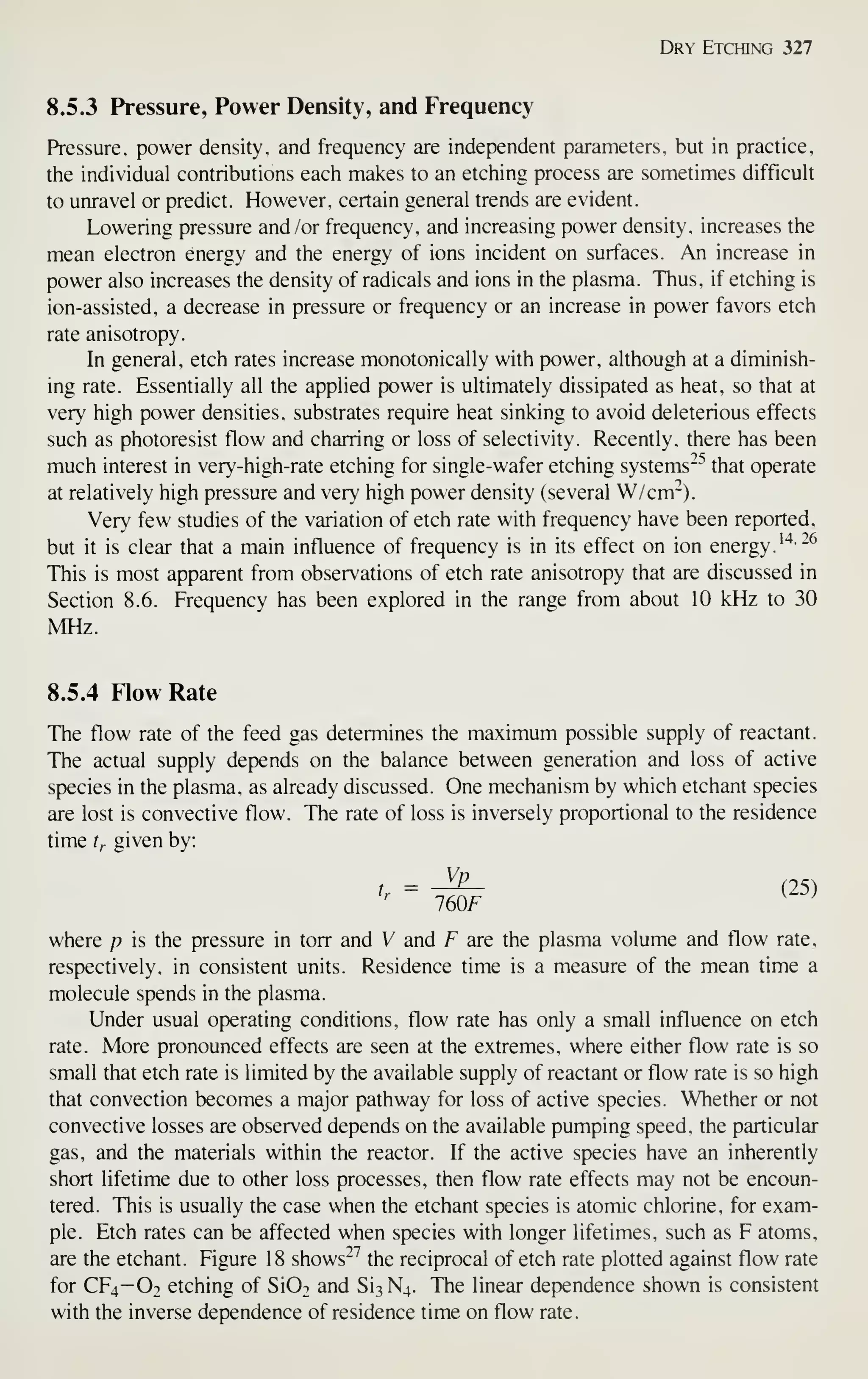

the advantages in device miniaturization, low power dissipation, and high yield, by

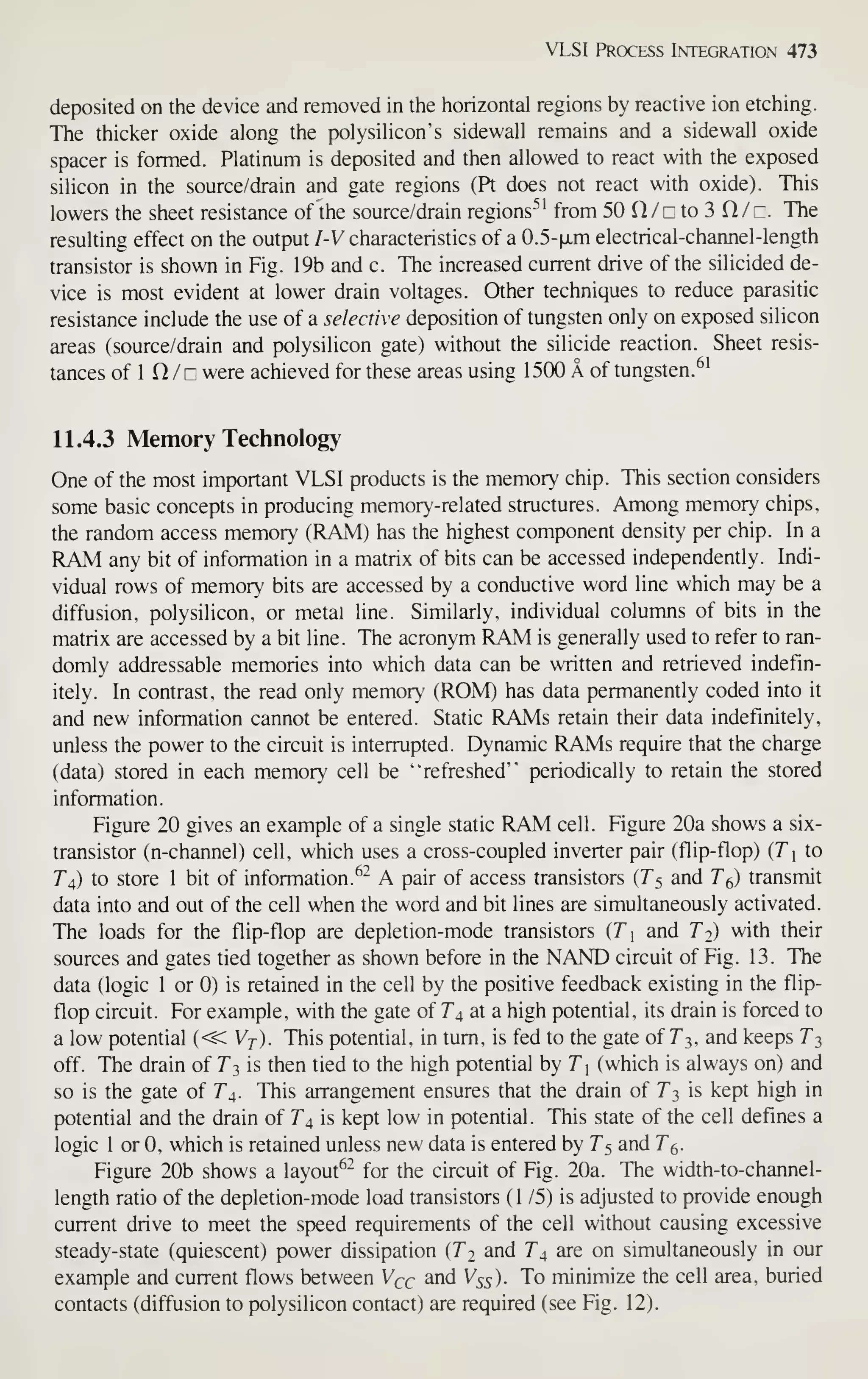

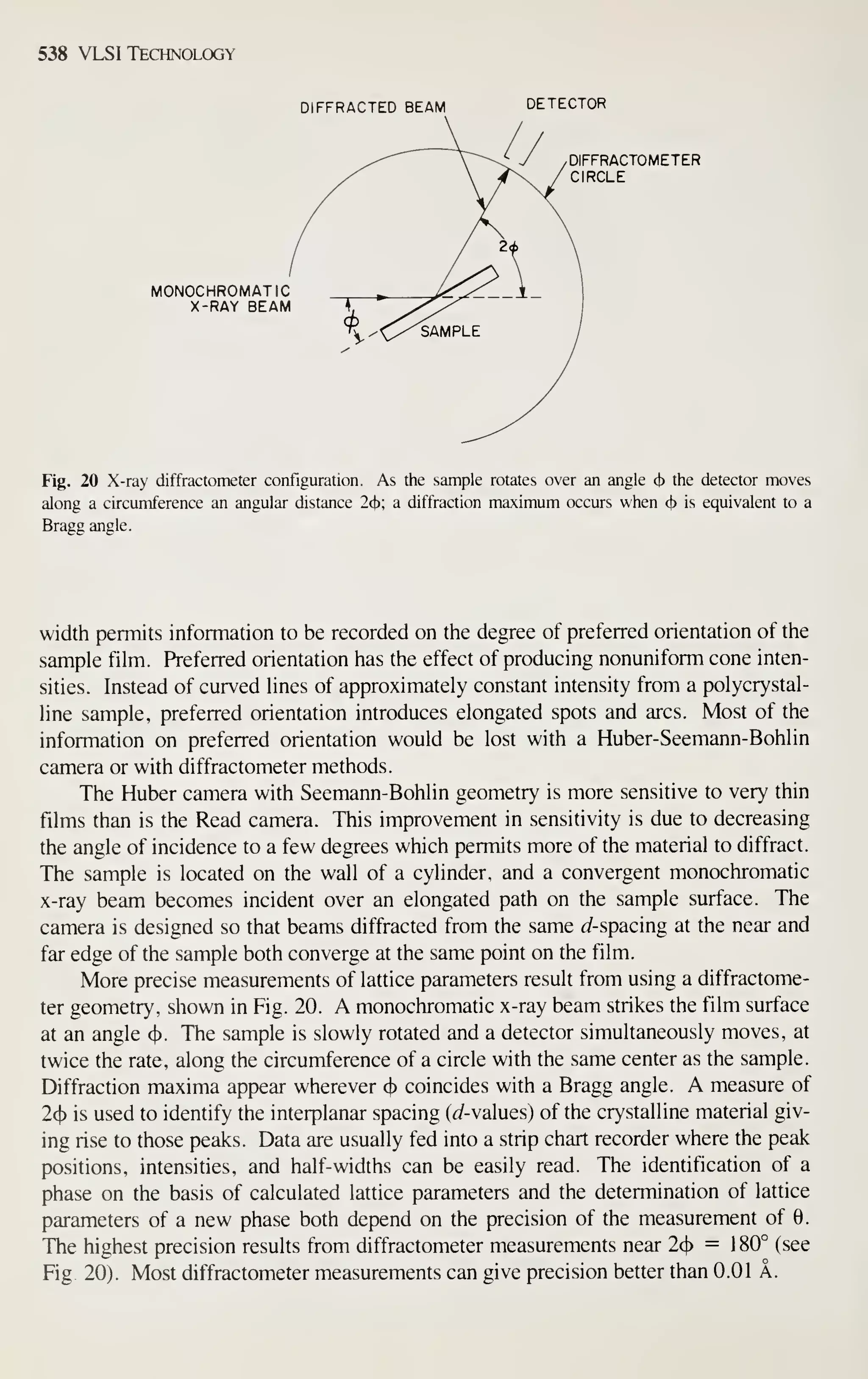

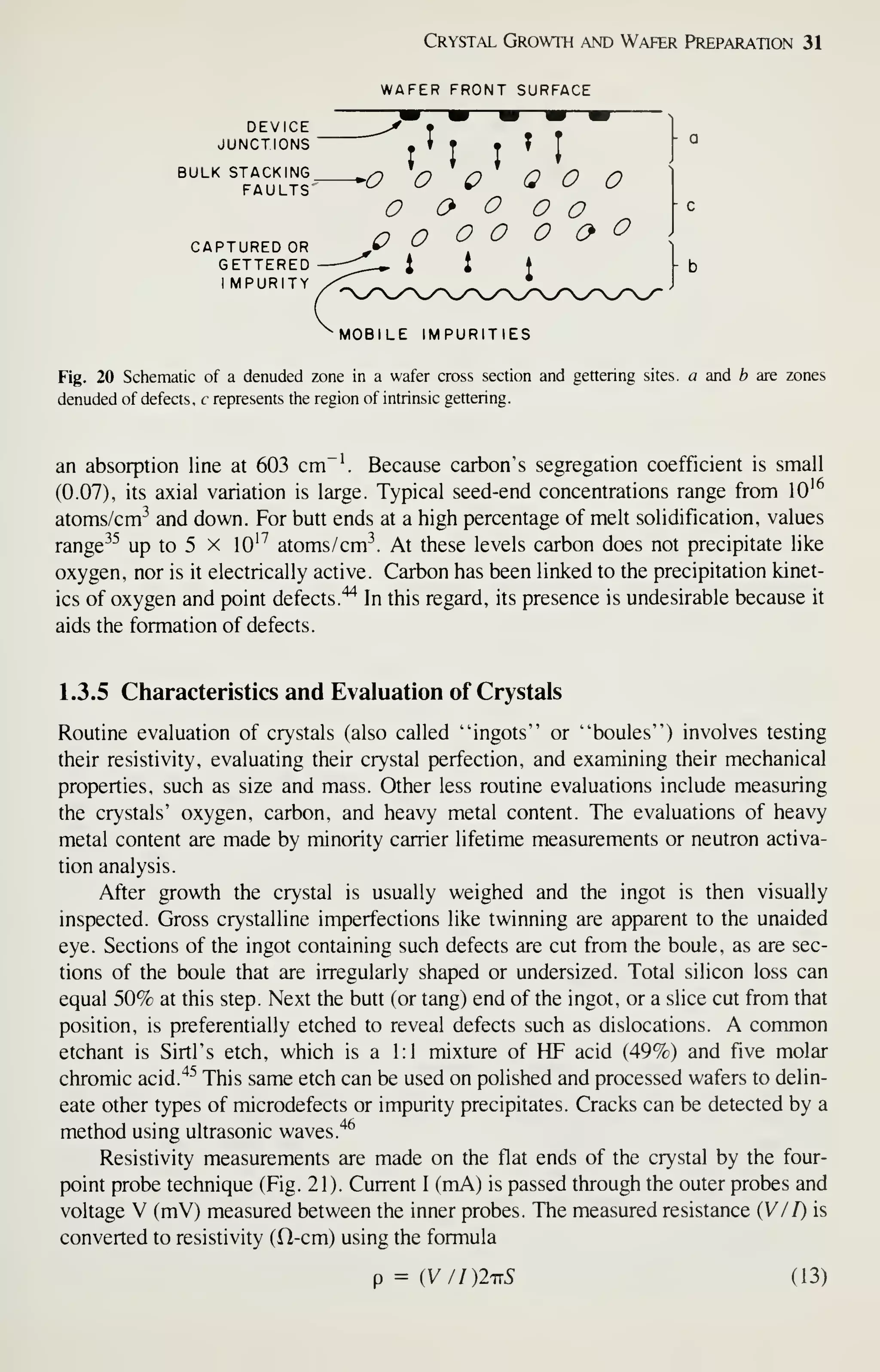

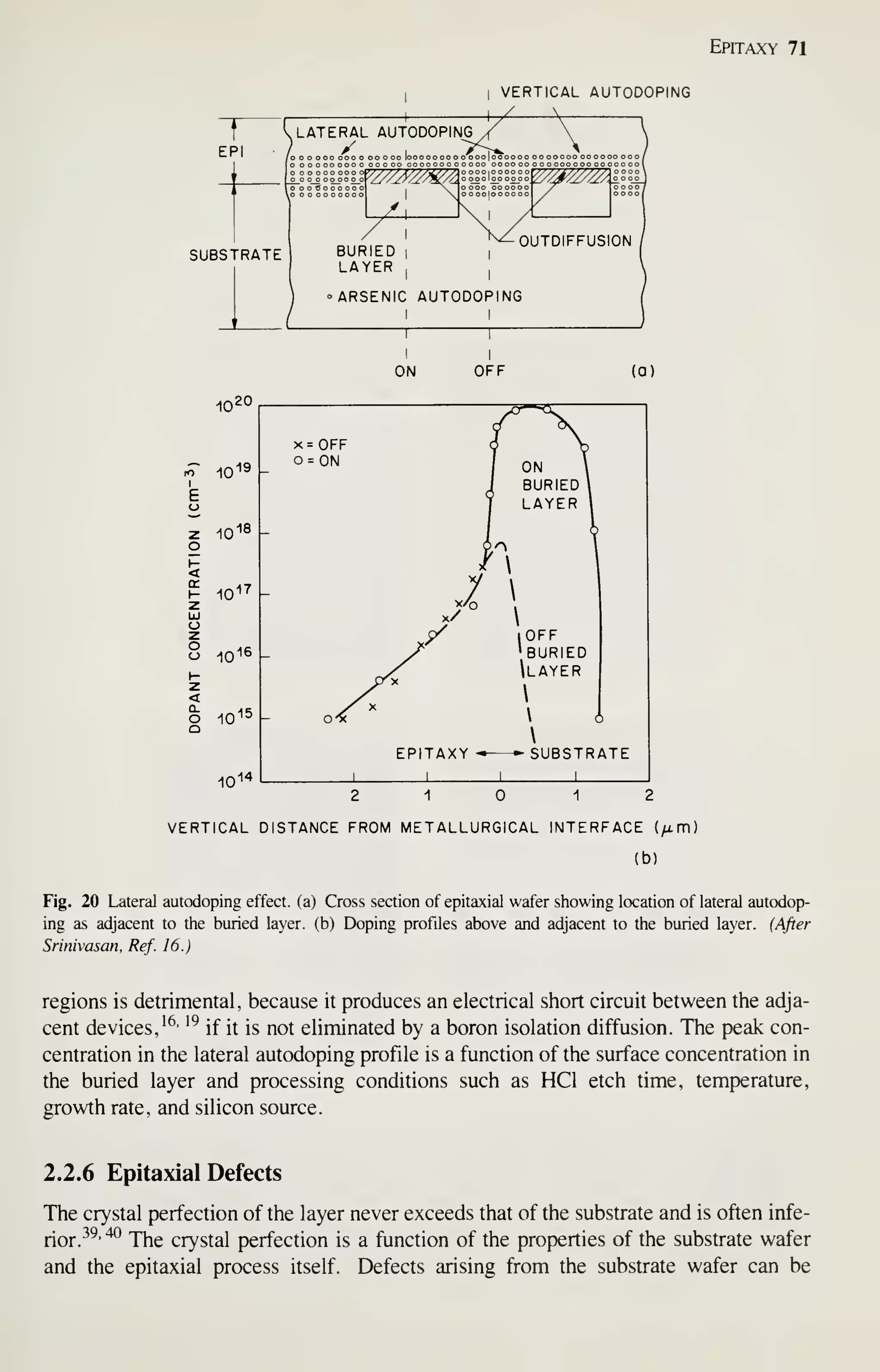

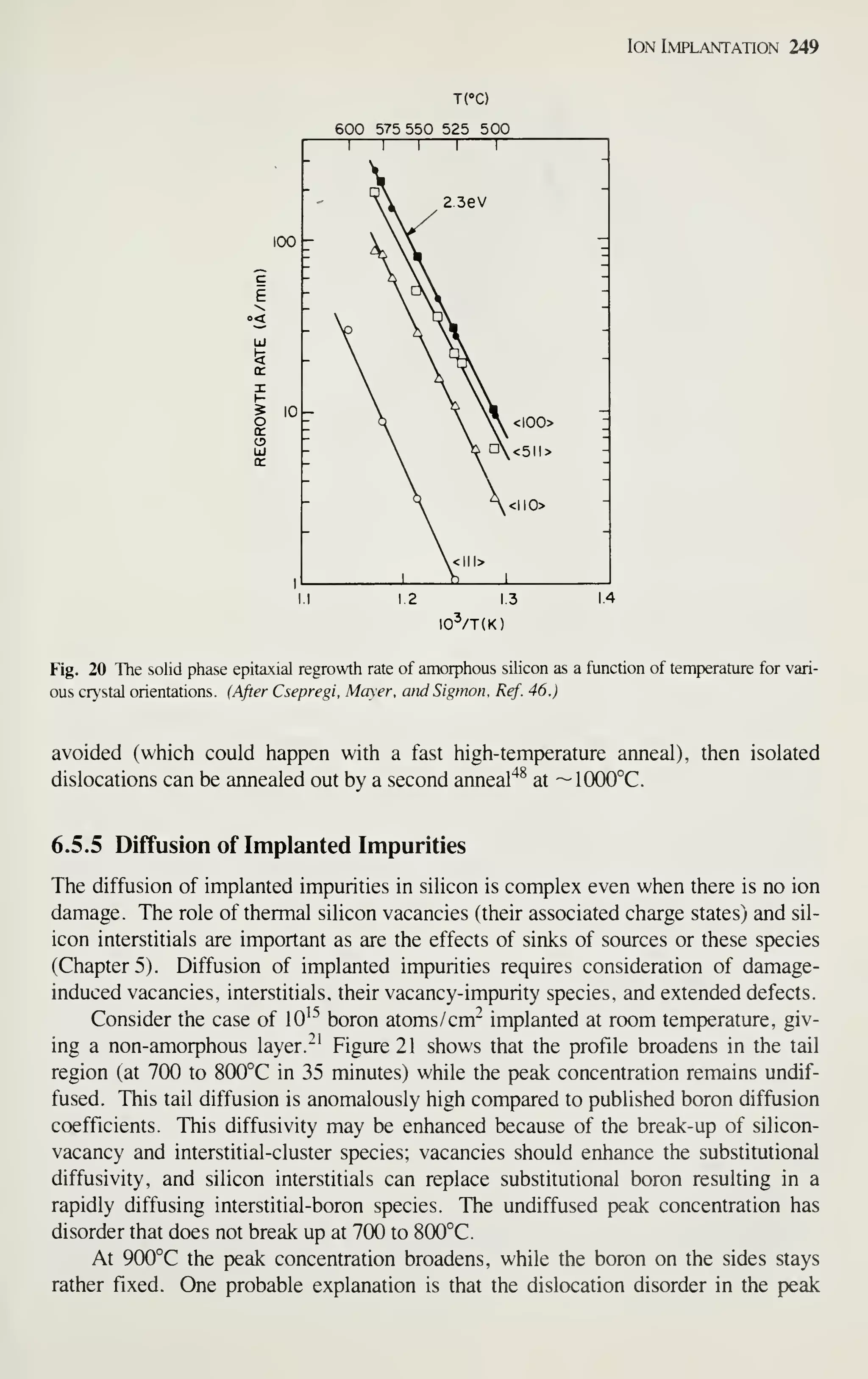

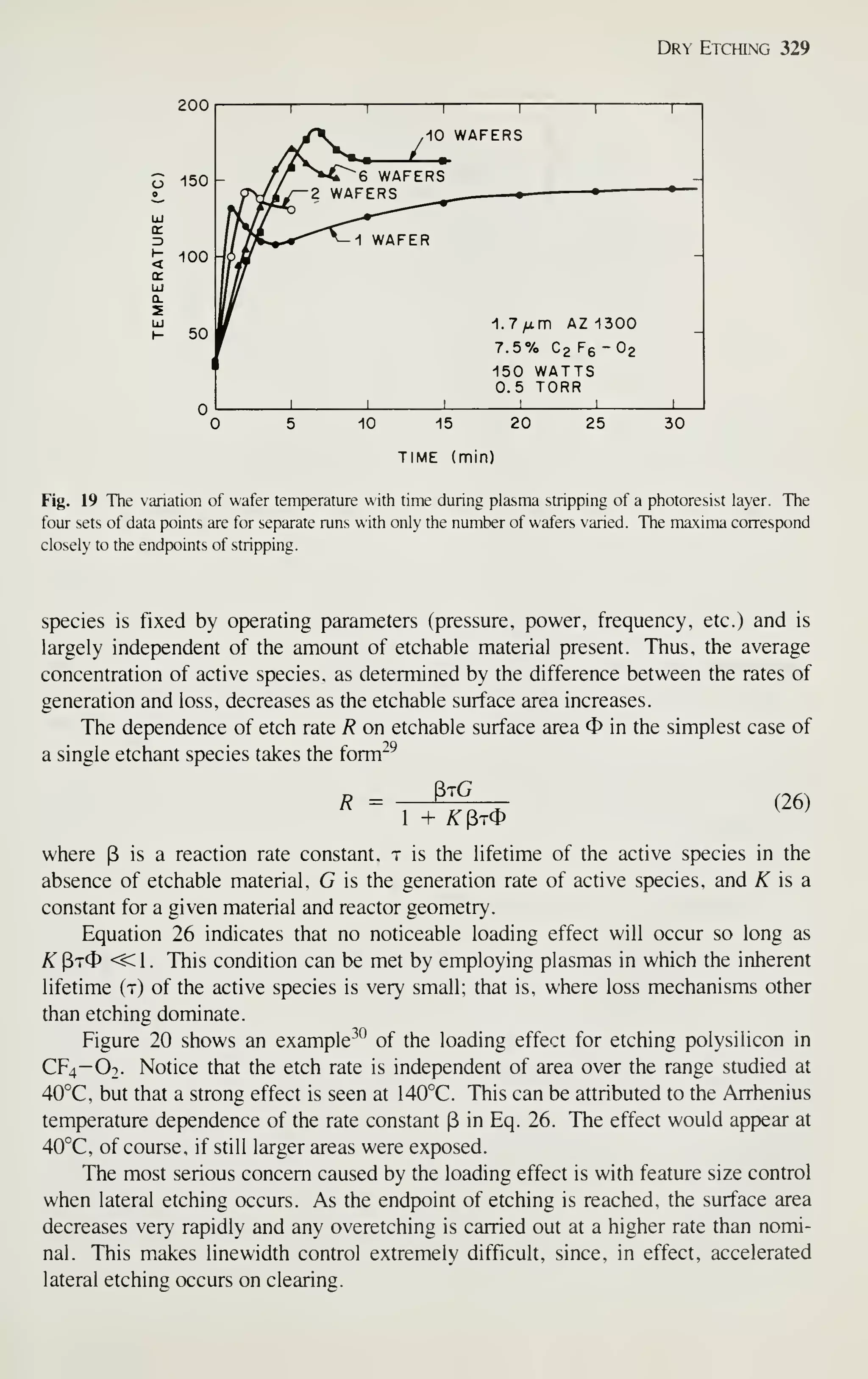

1990 digital MOS ICs will dominate the IC market and capture a major market share

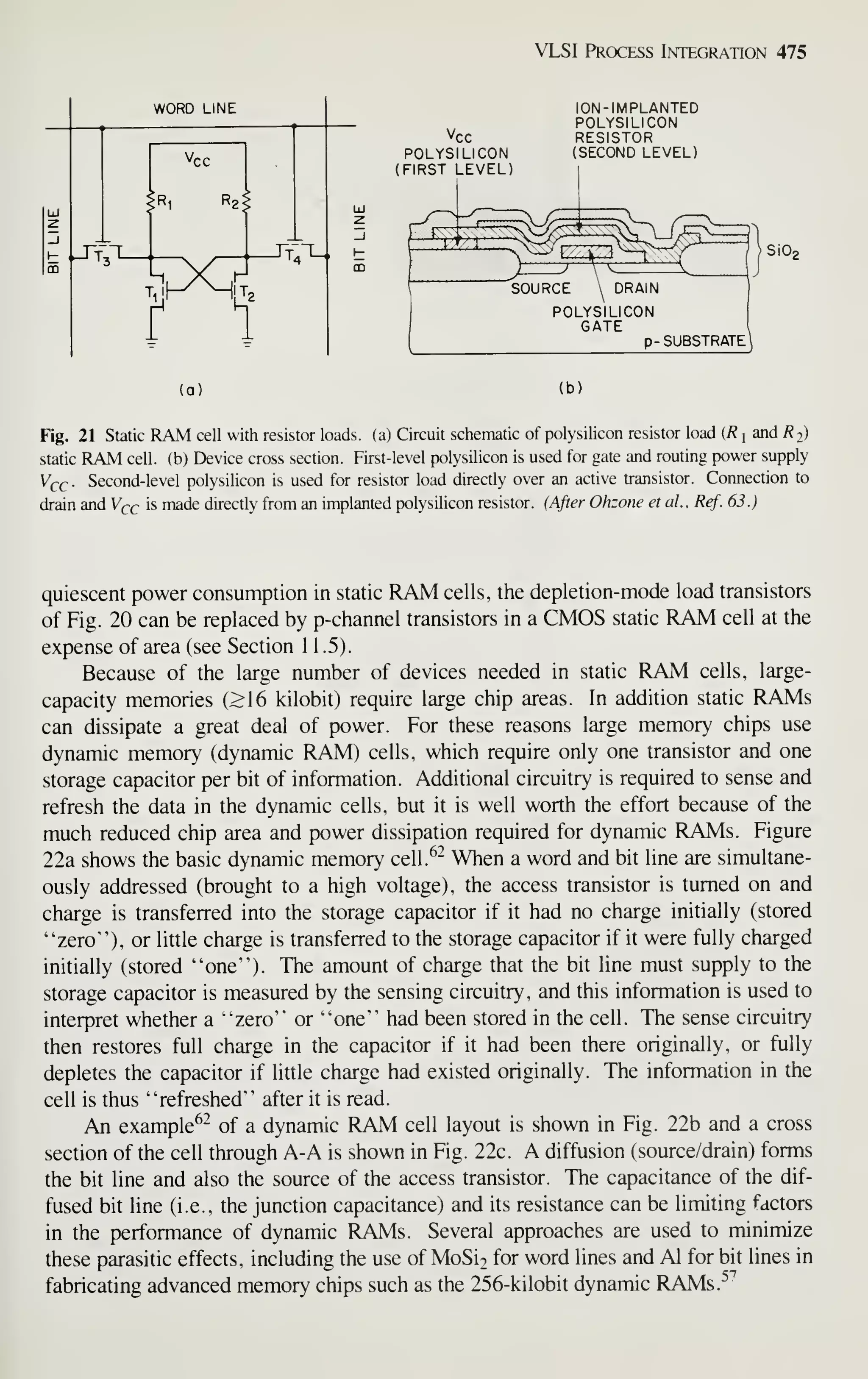

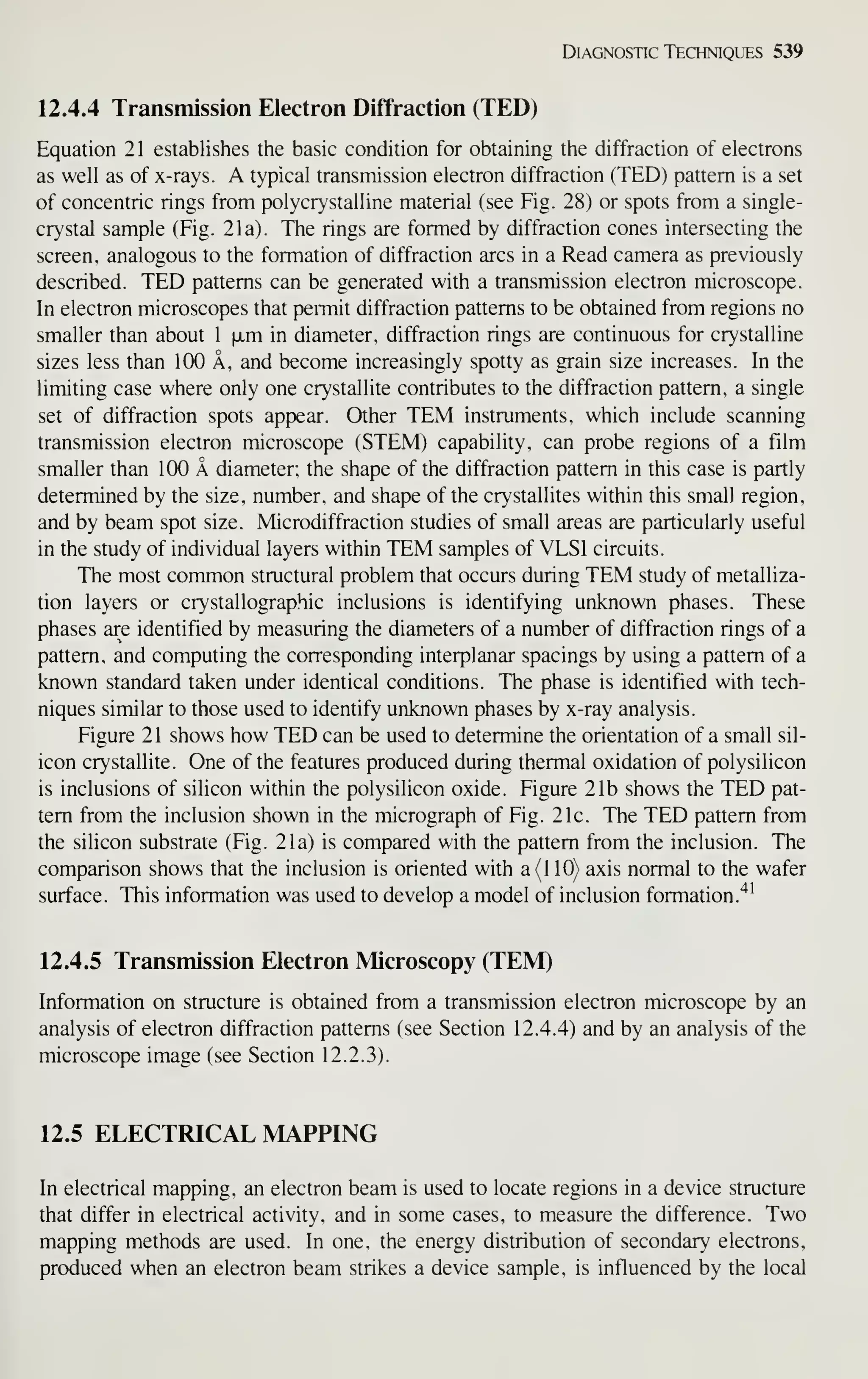

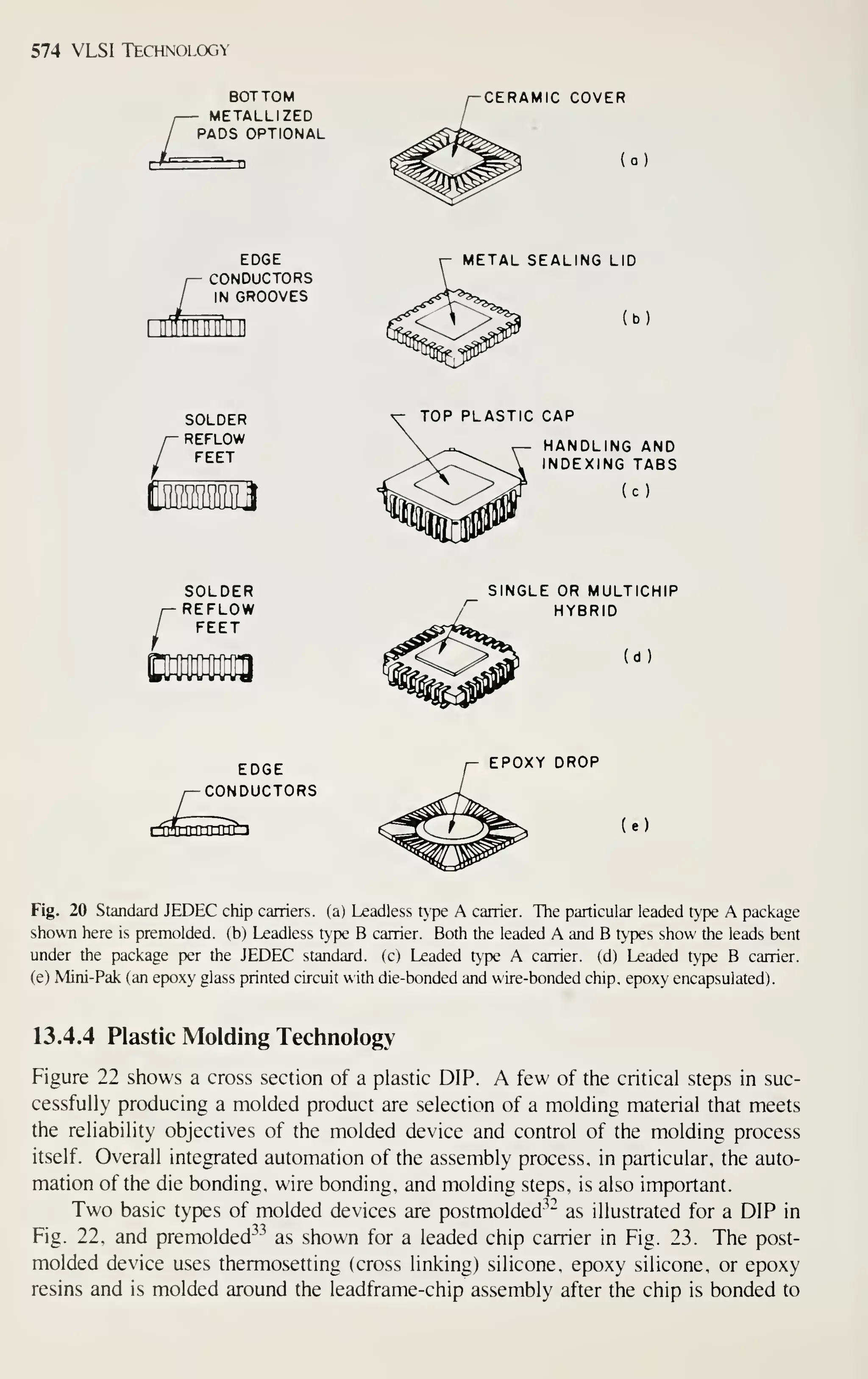

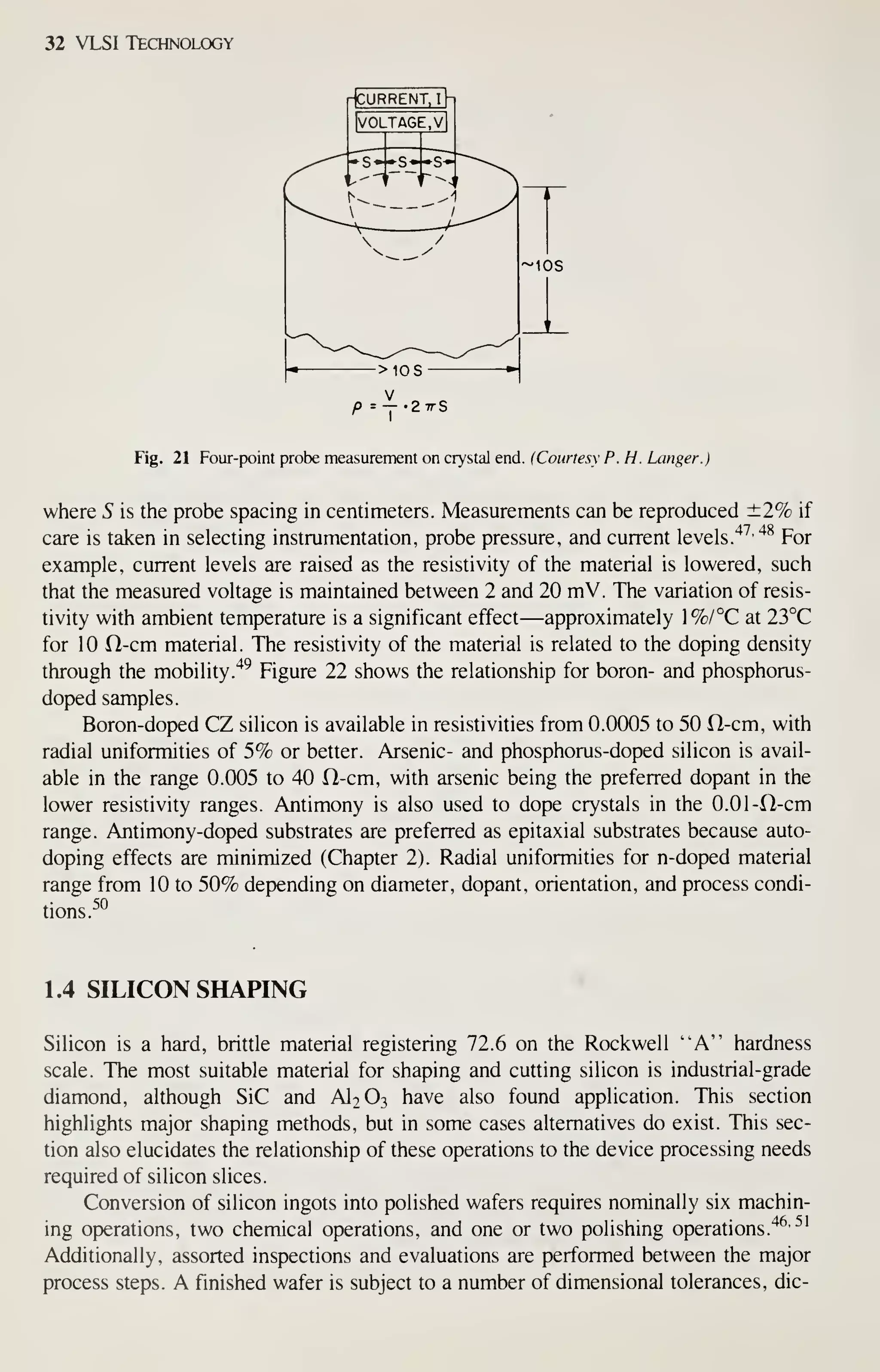

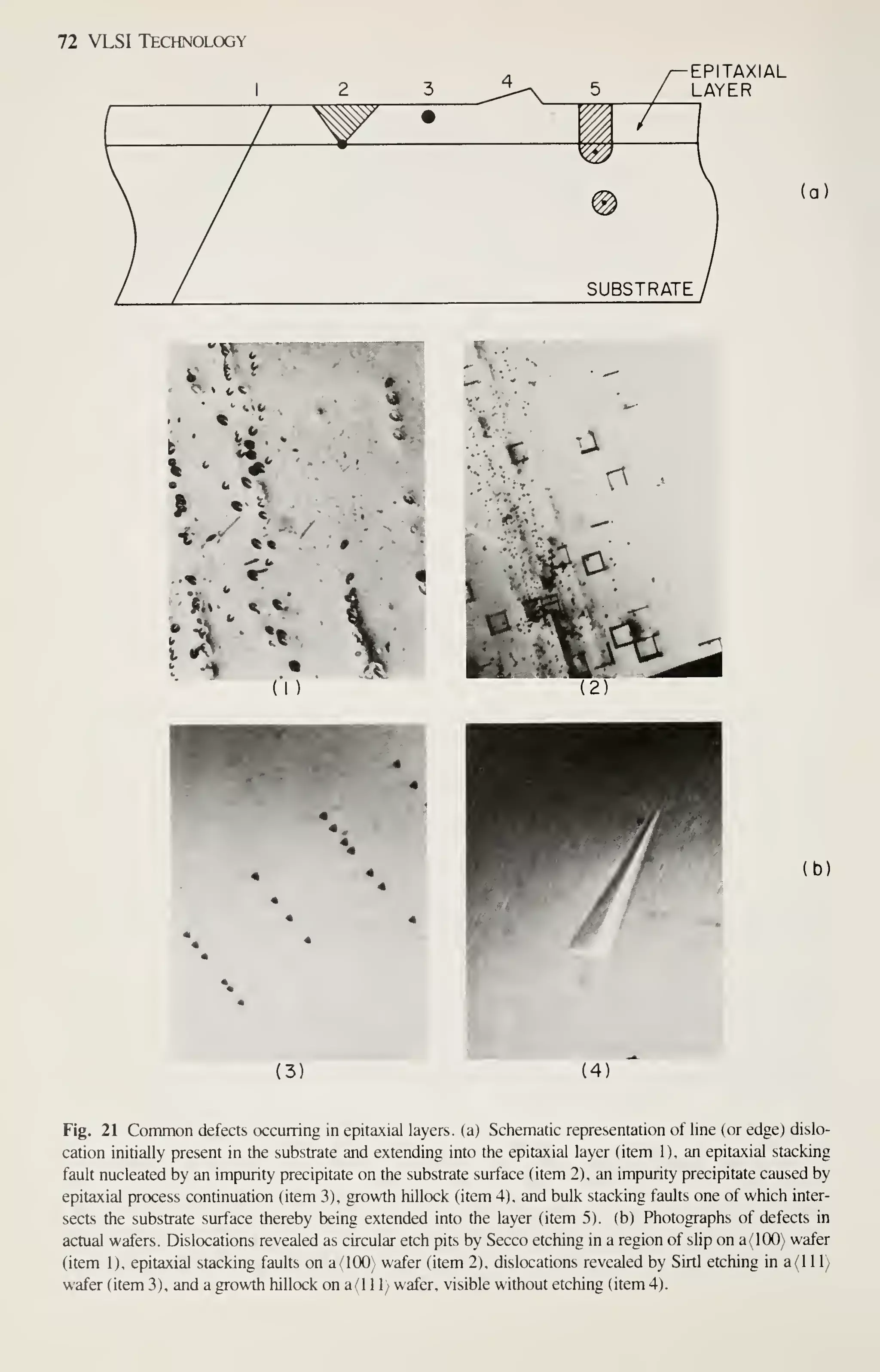

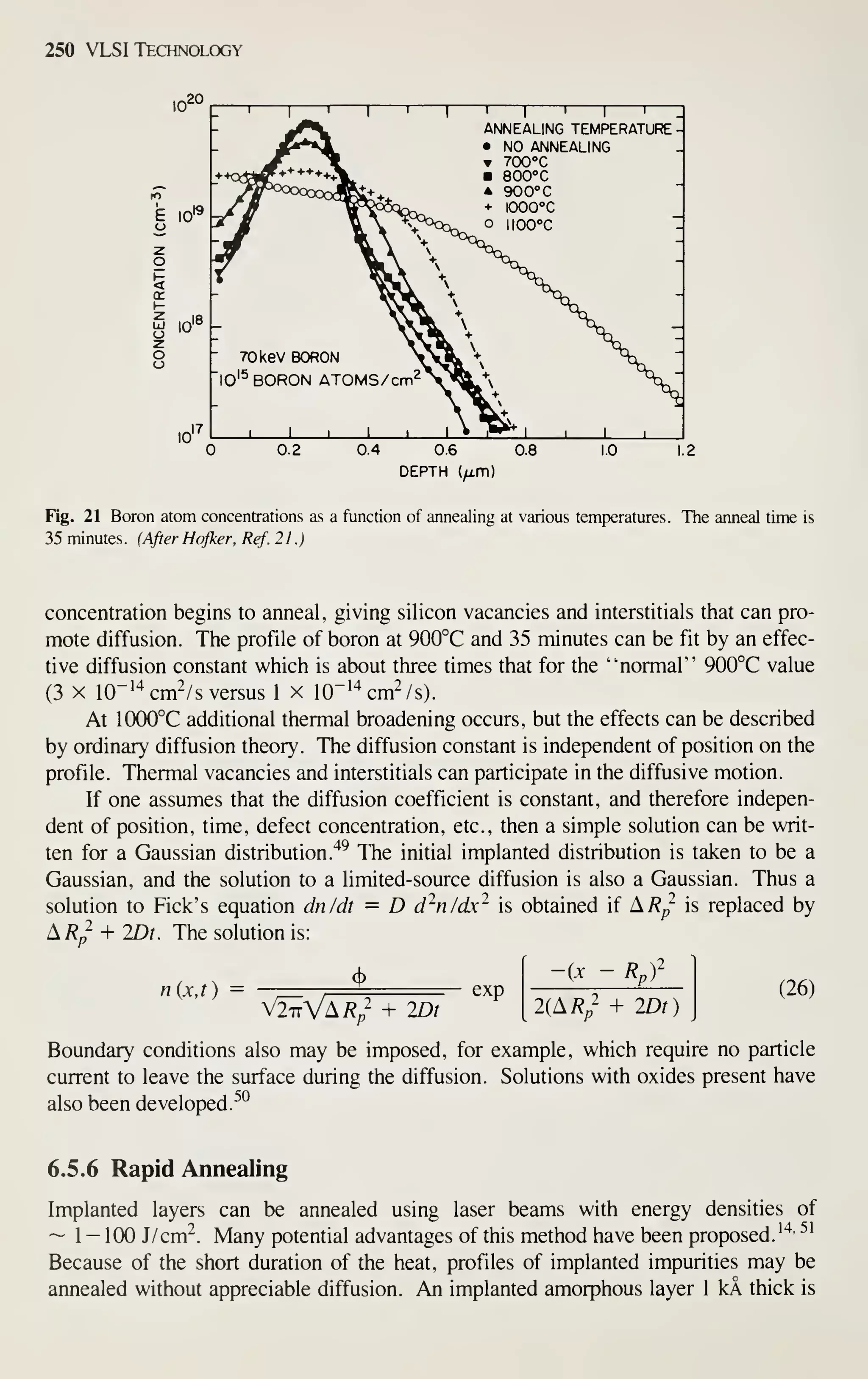

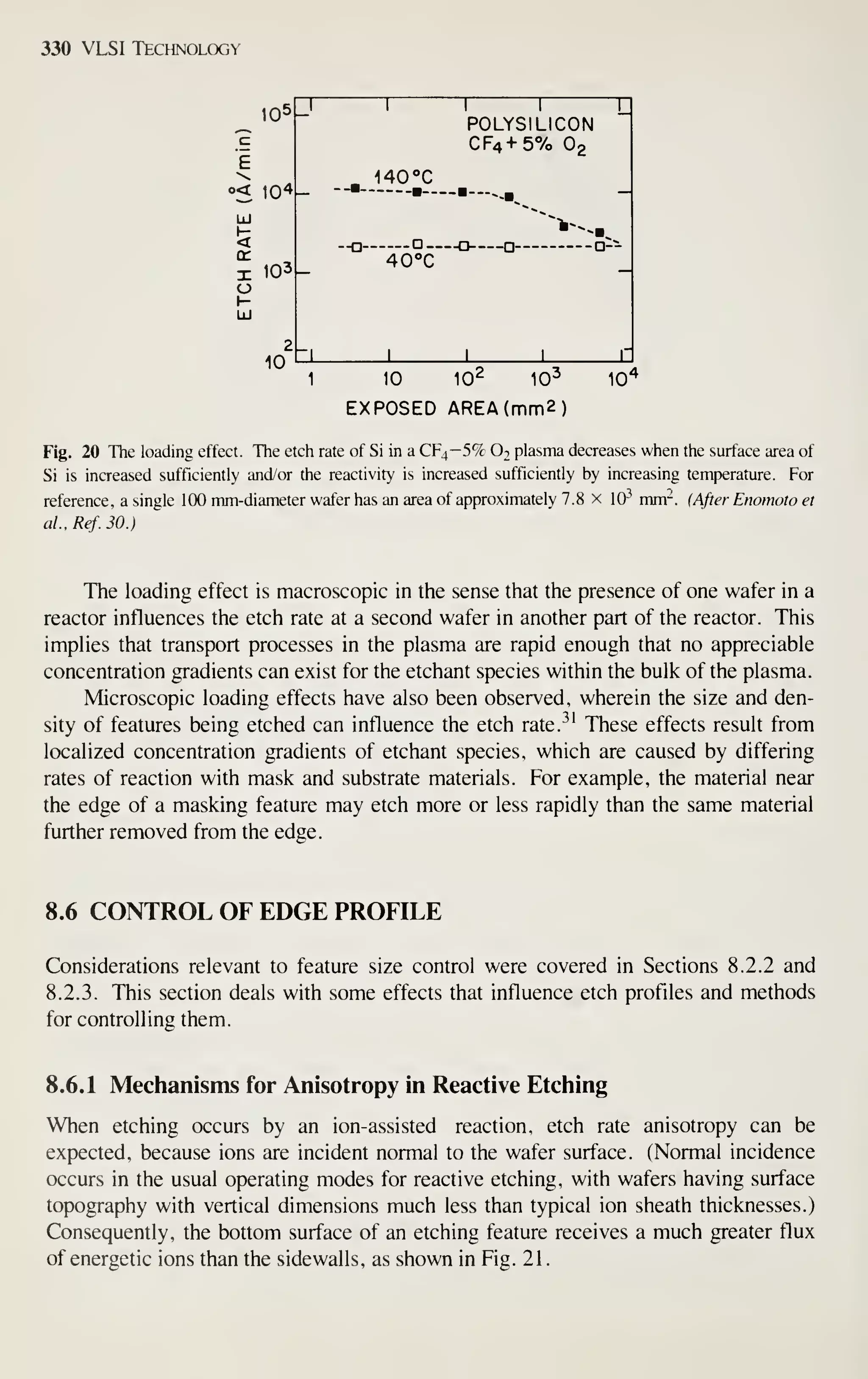

of all semiconductor devices sold. This book, therefore, emphasizes MOS-related

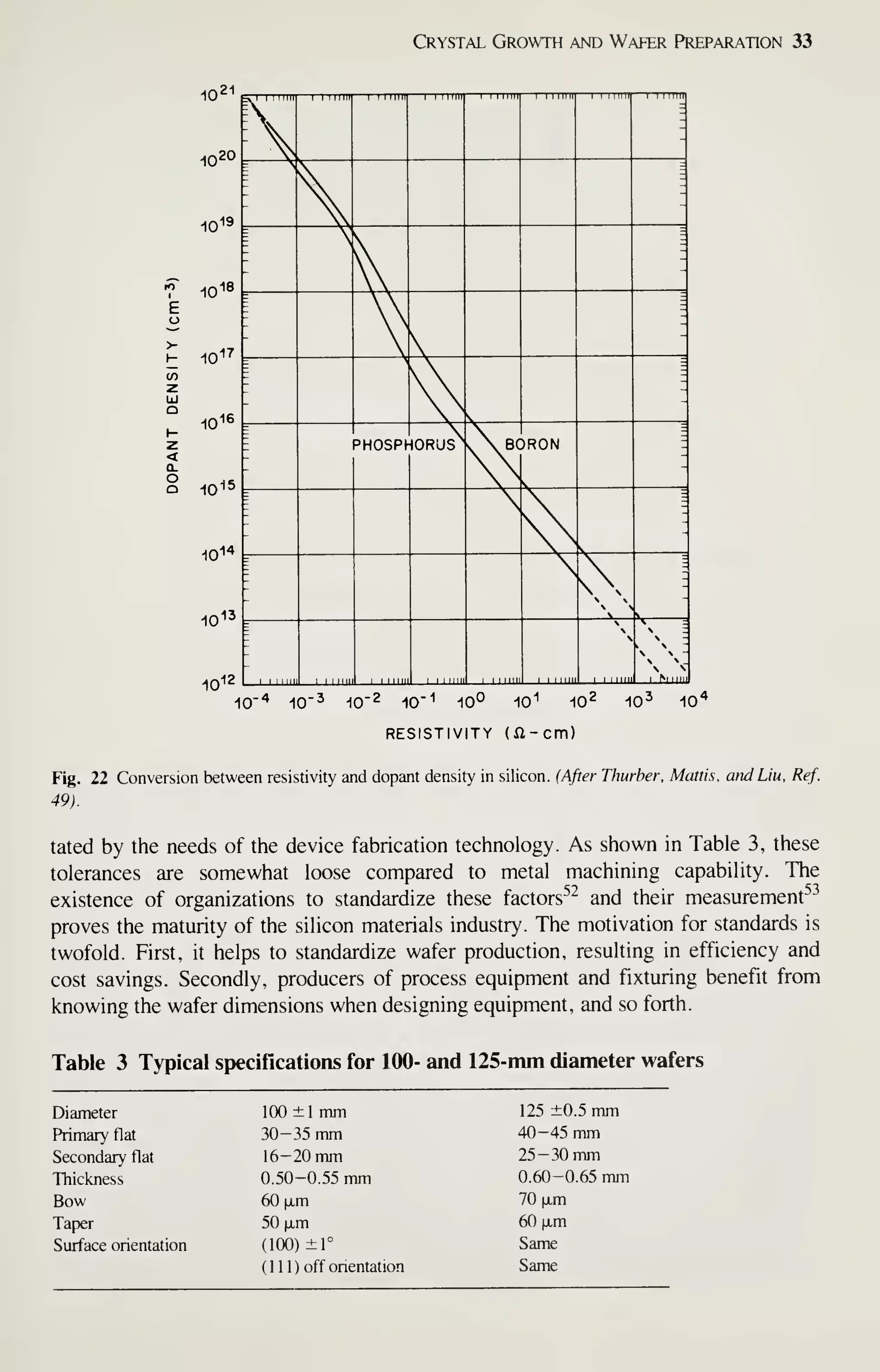

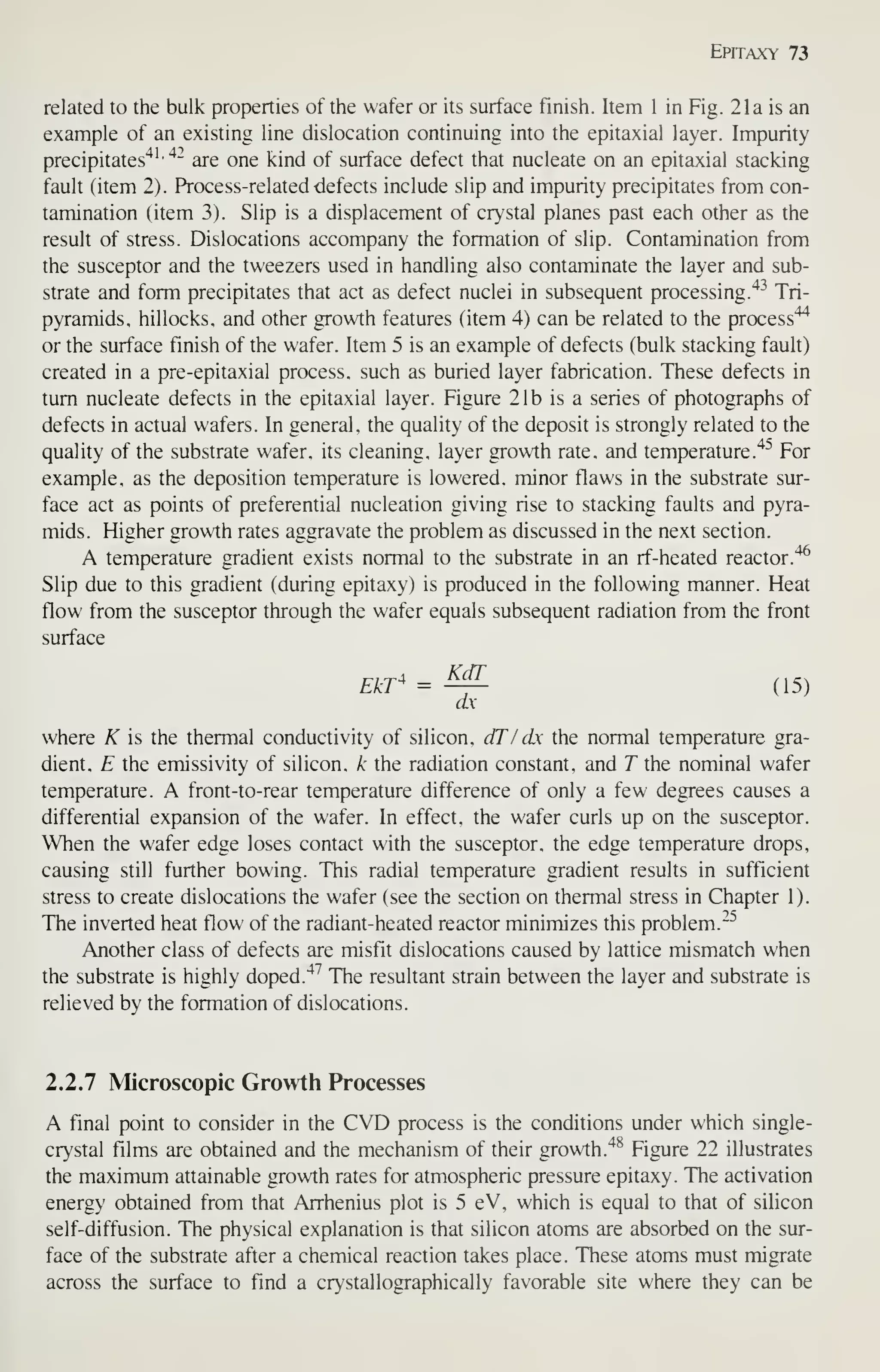

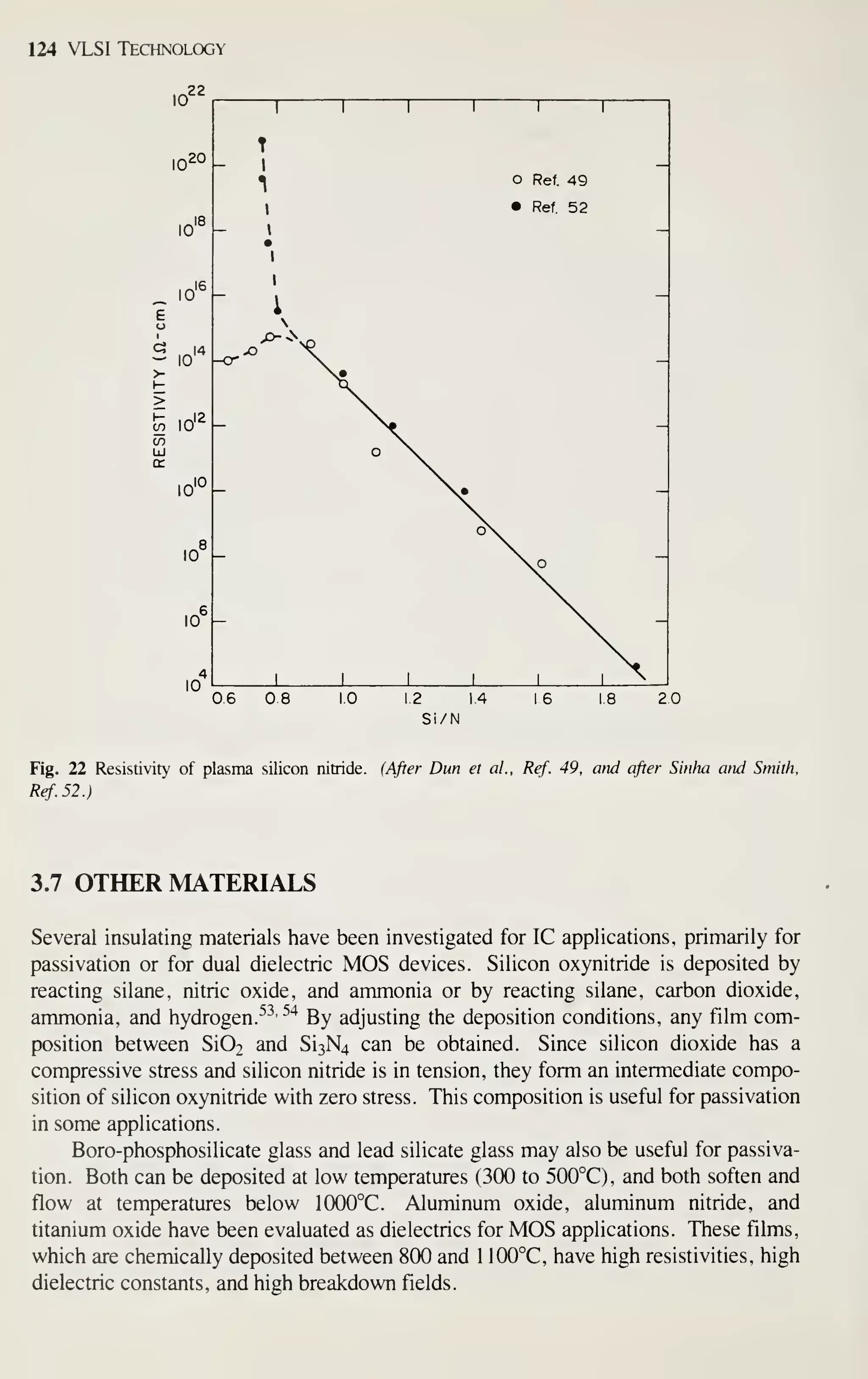

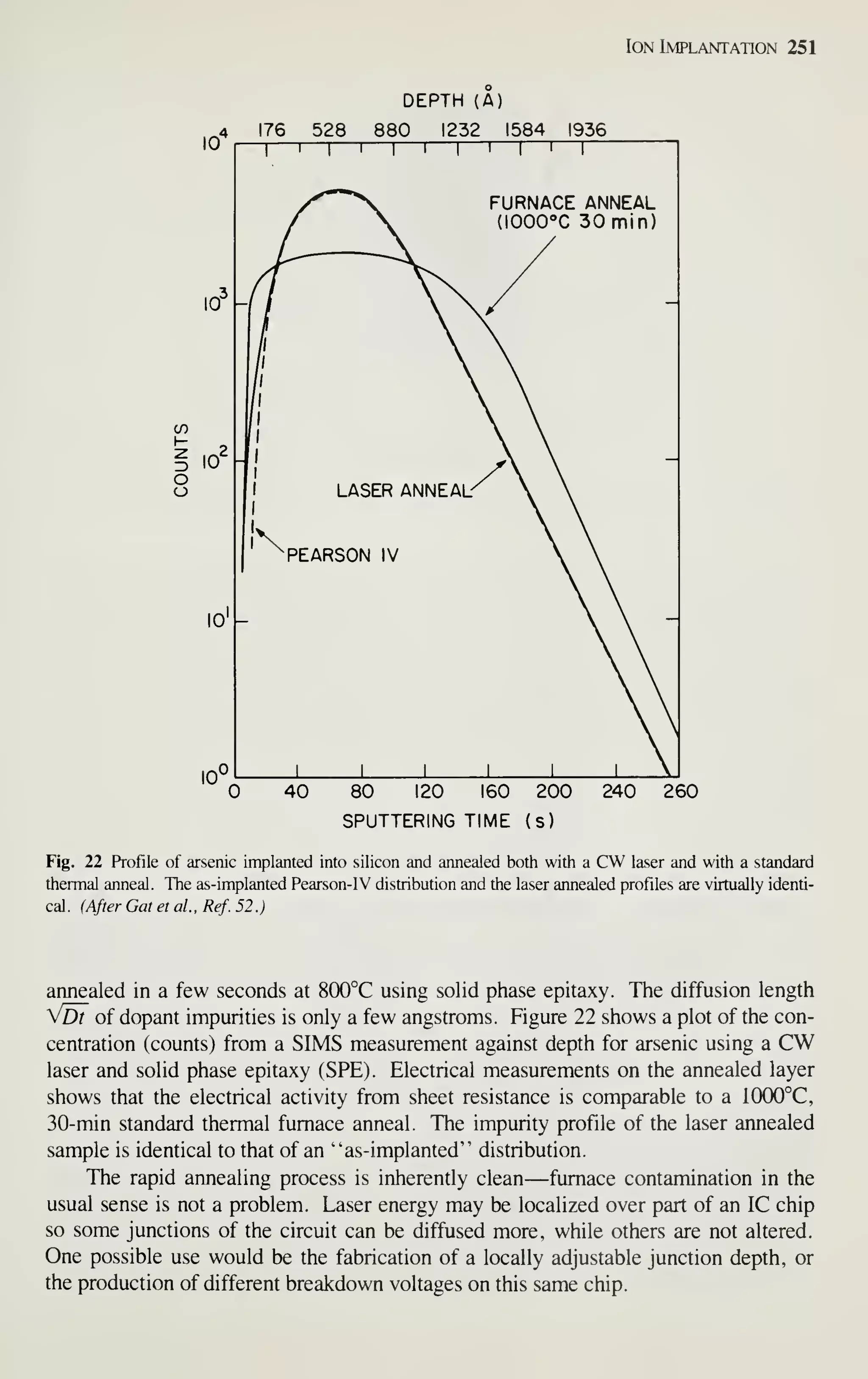

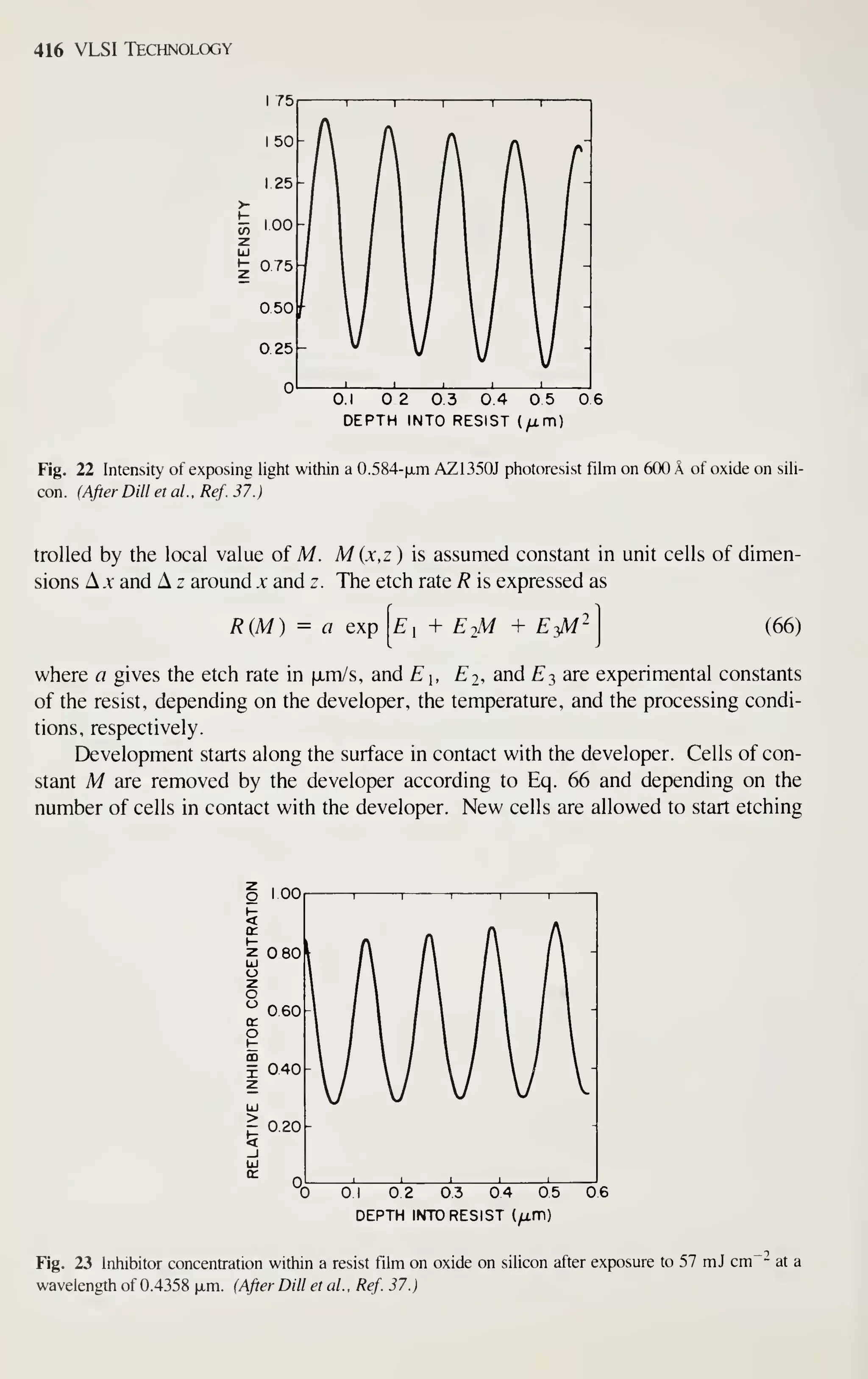

VLSI technology.

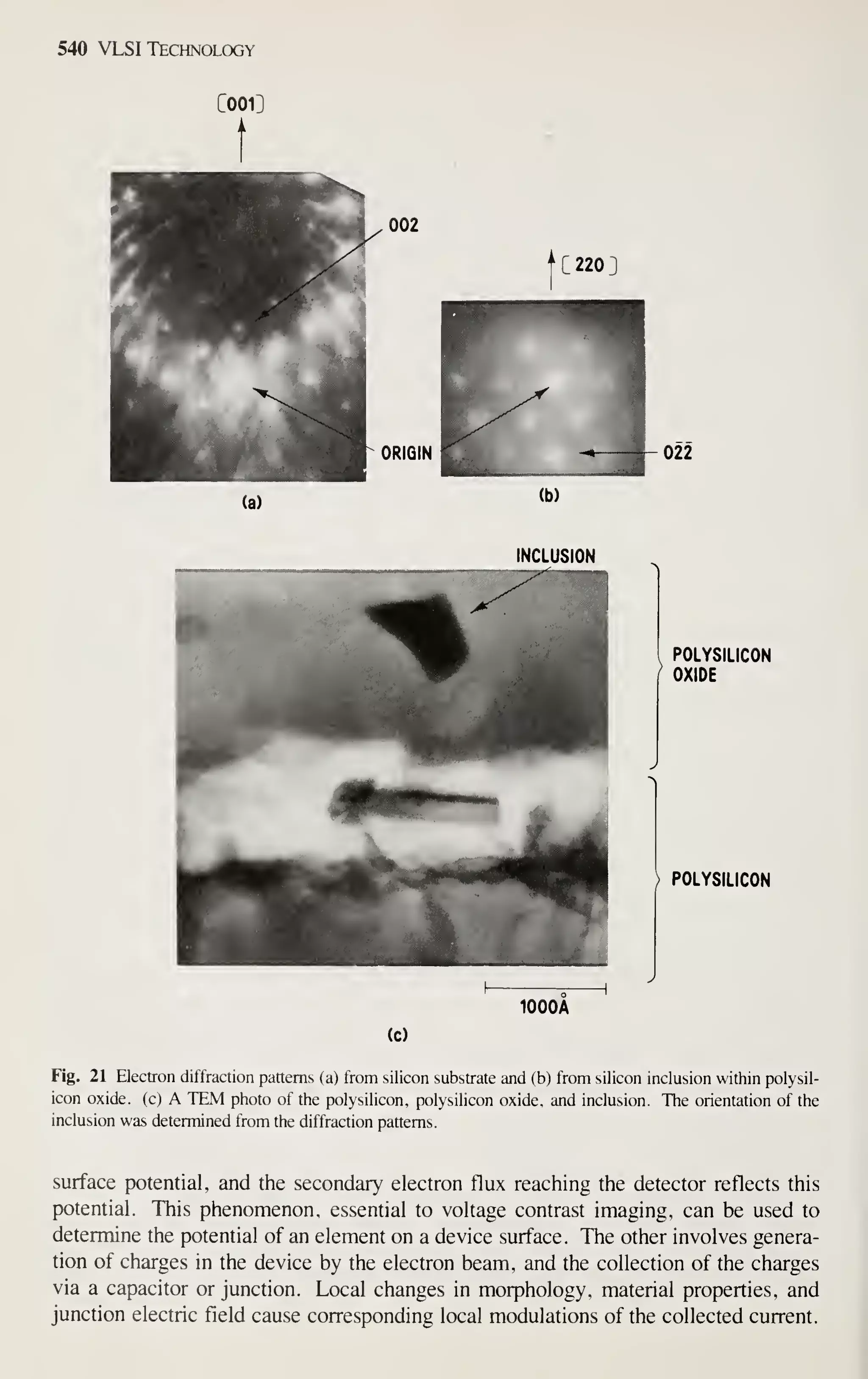

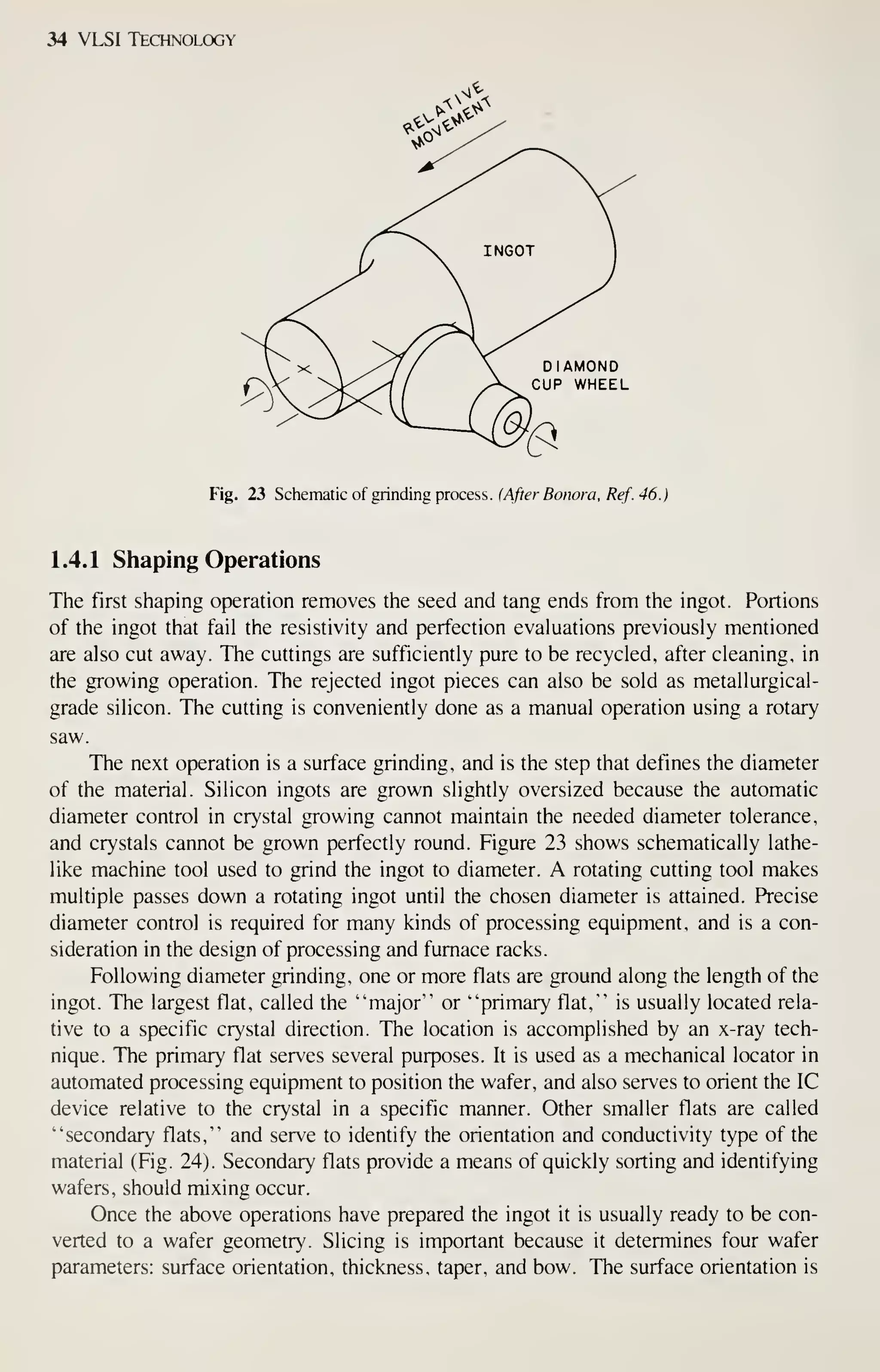

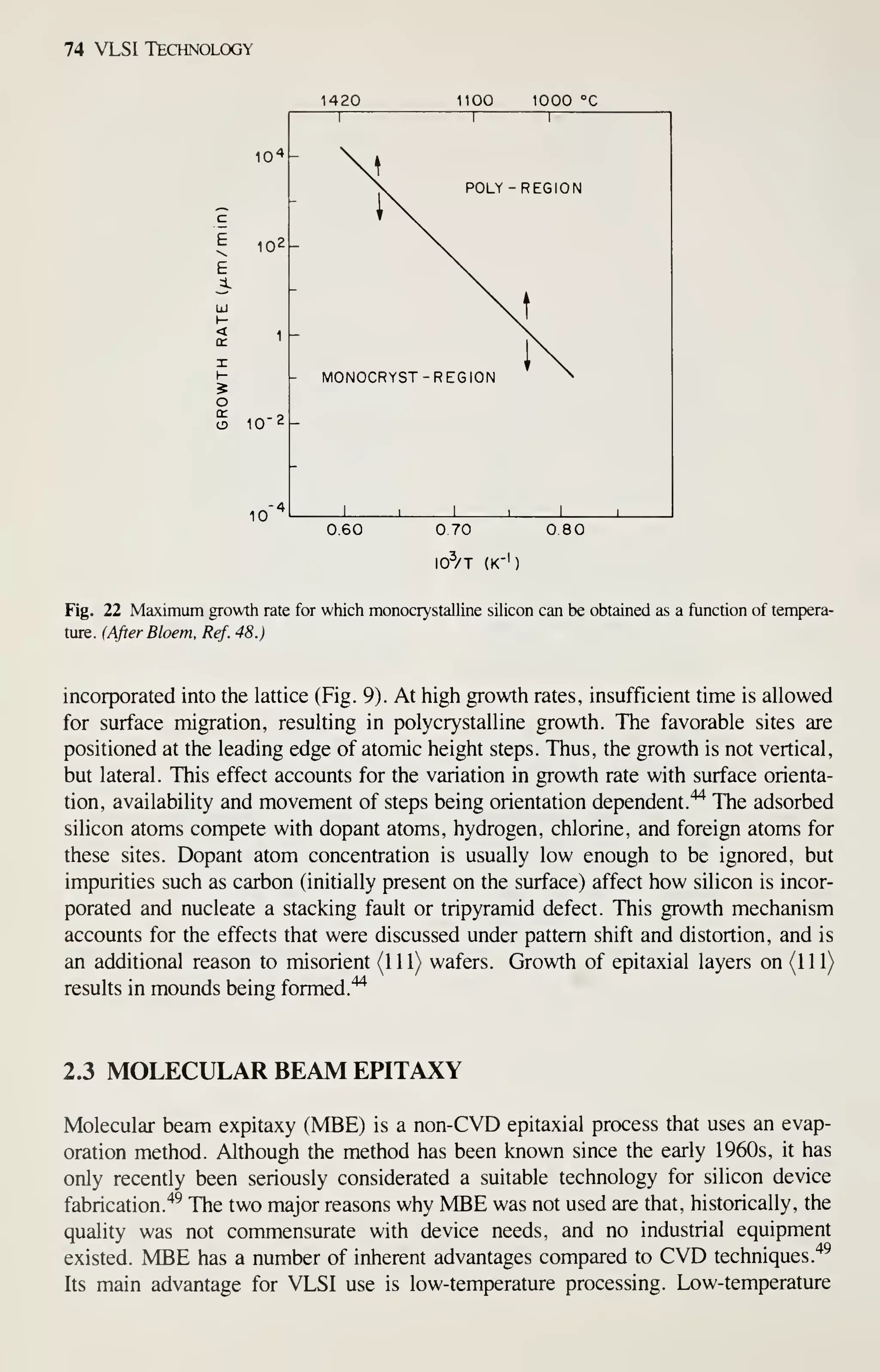

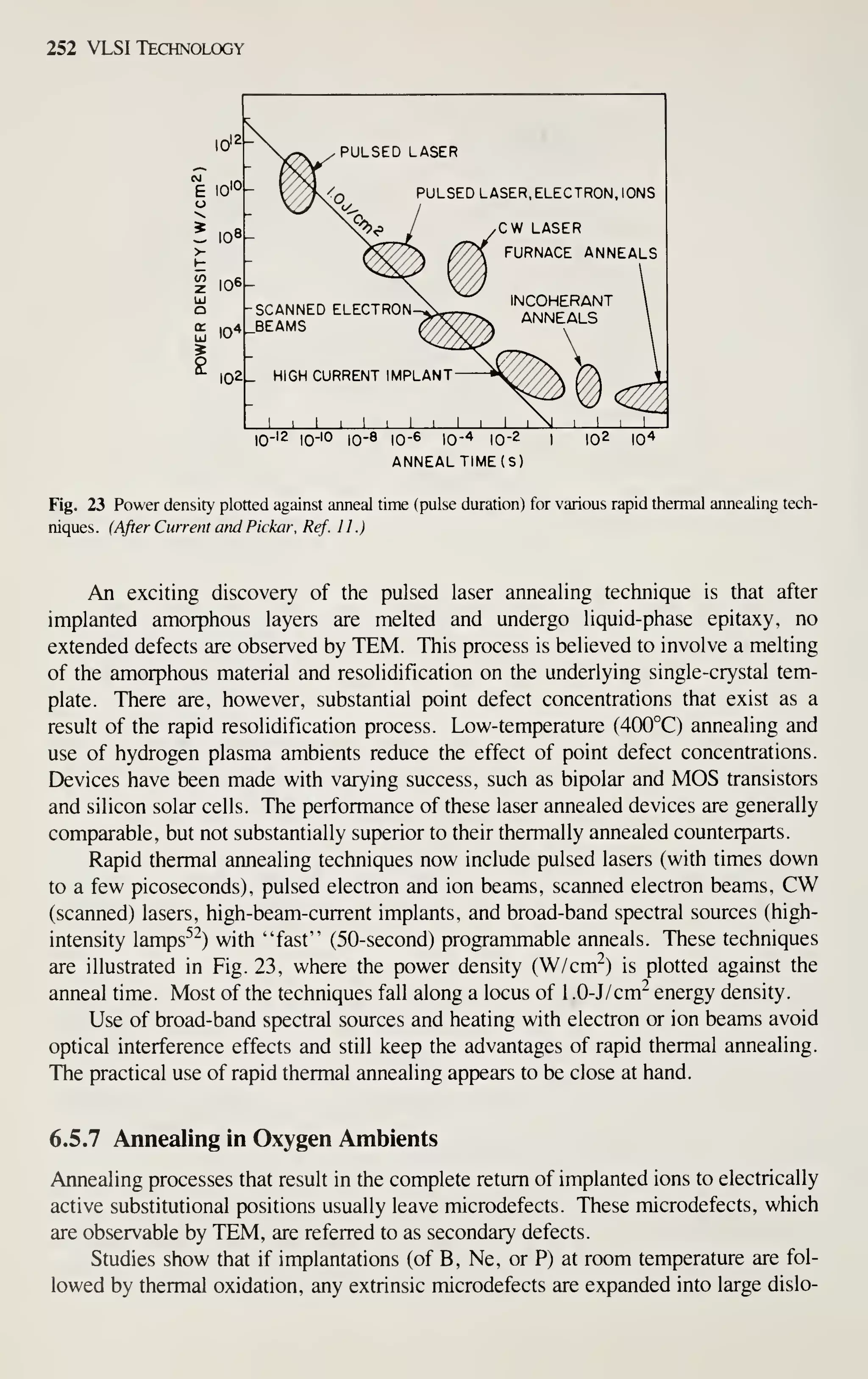

DEVICE MINIATURIZATION

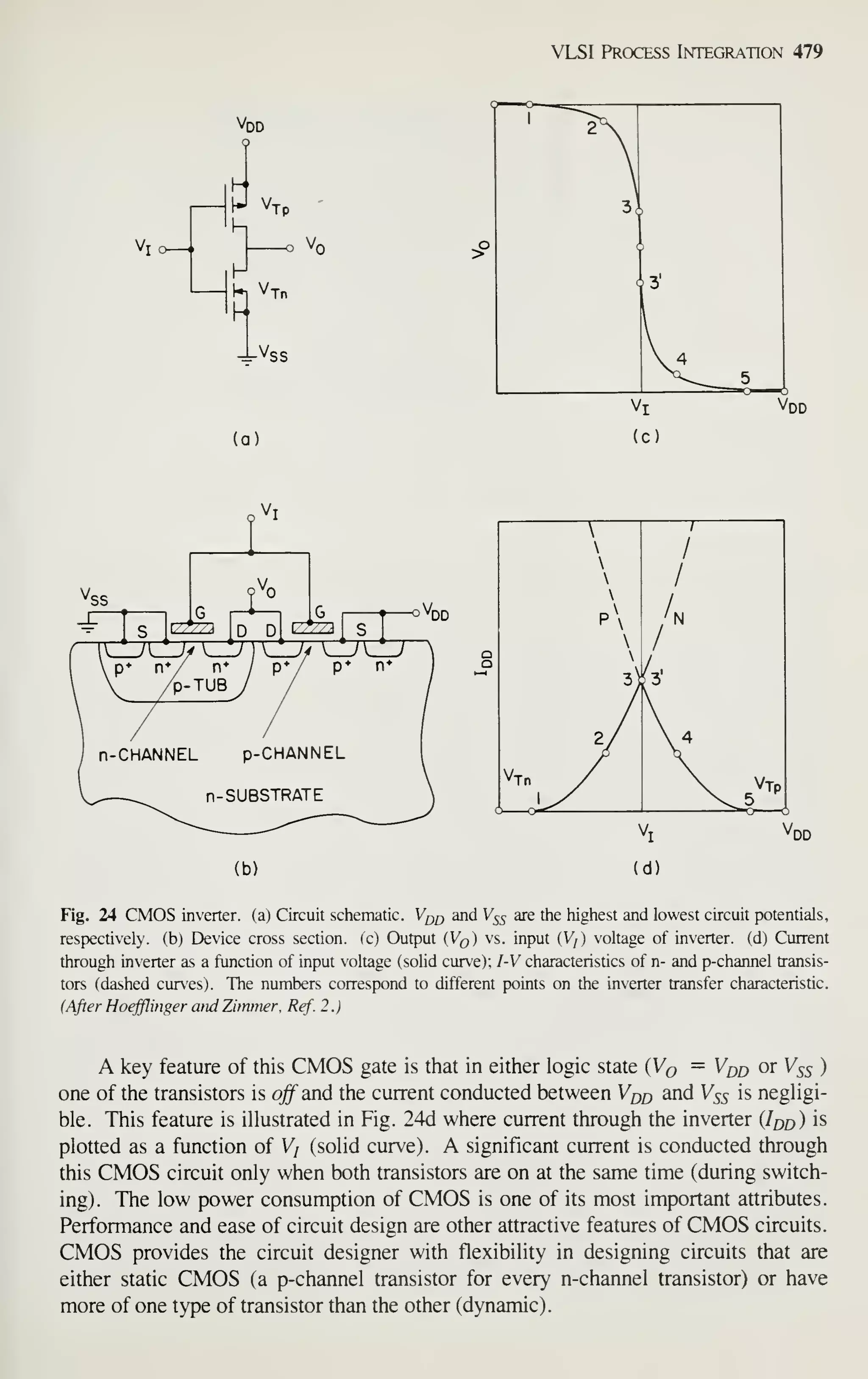

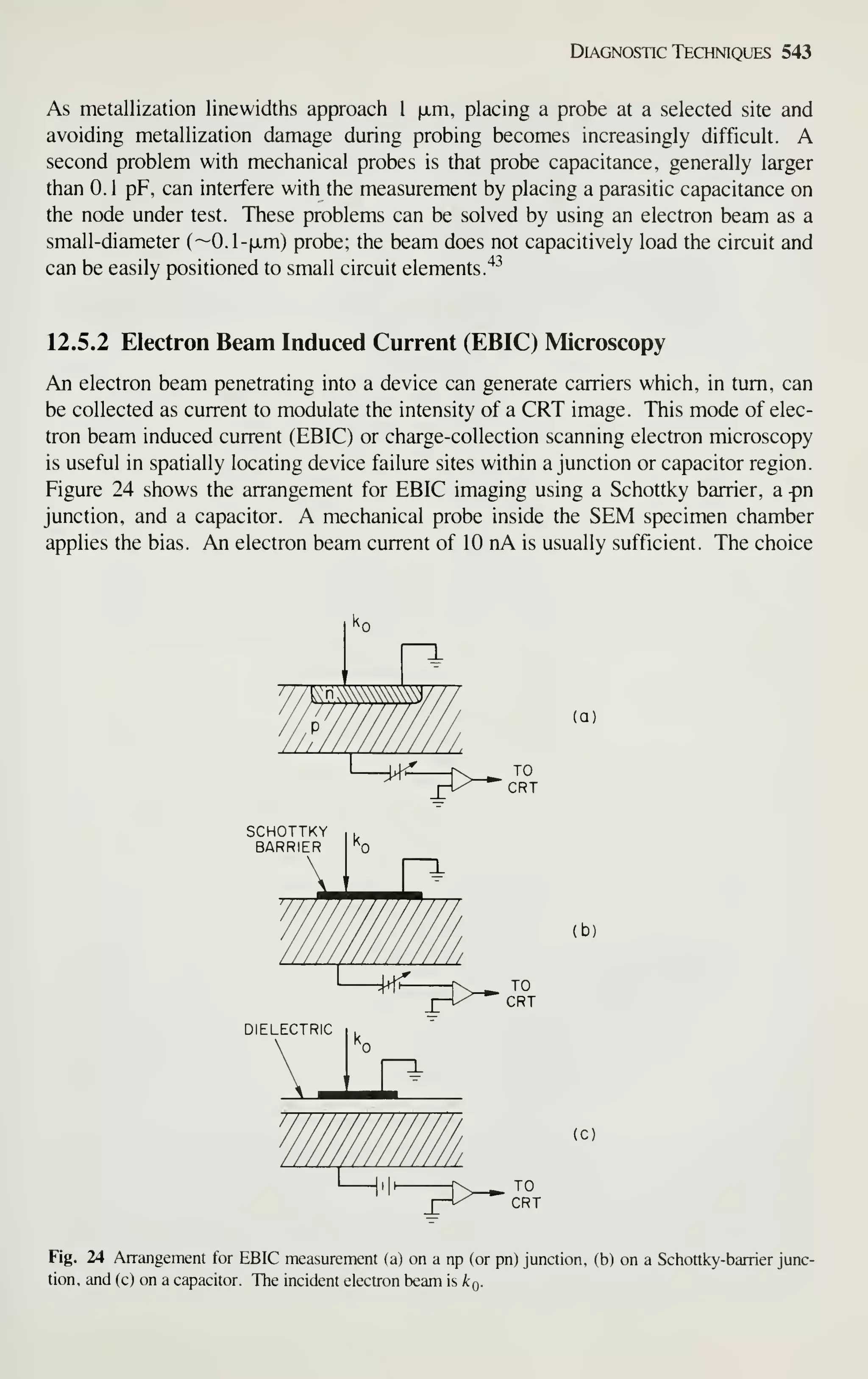

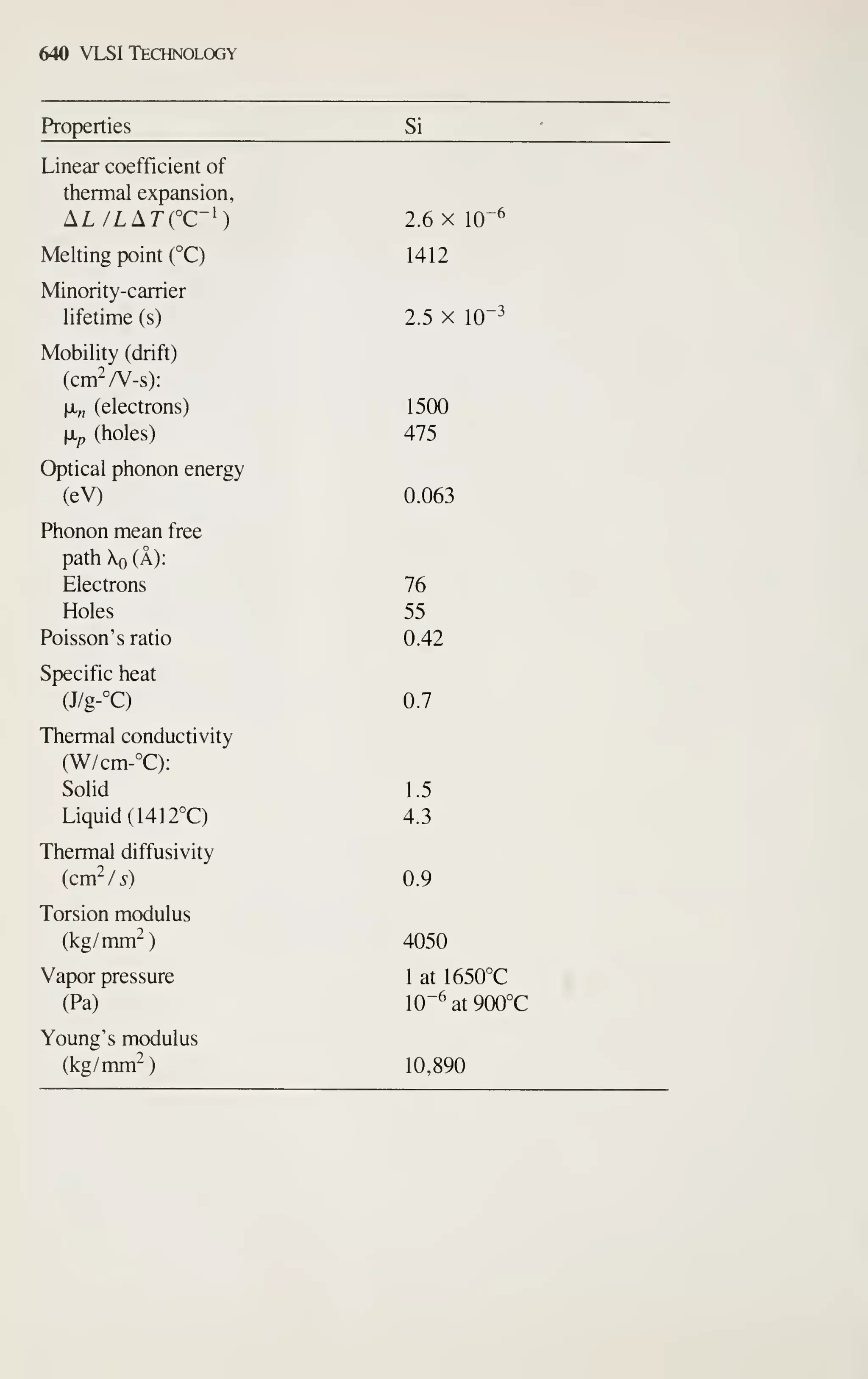

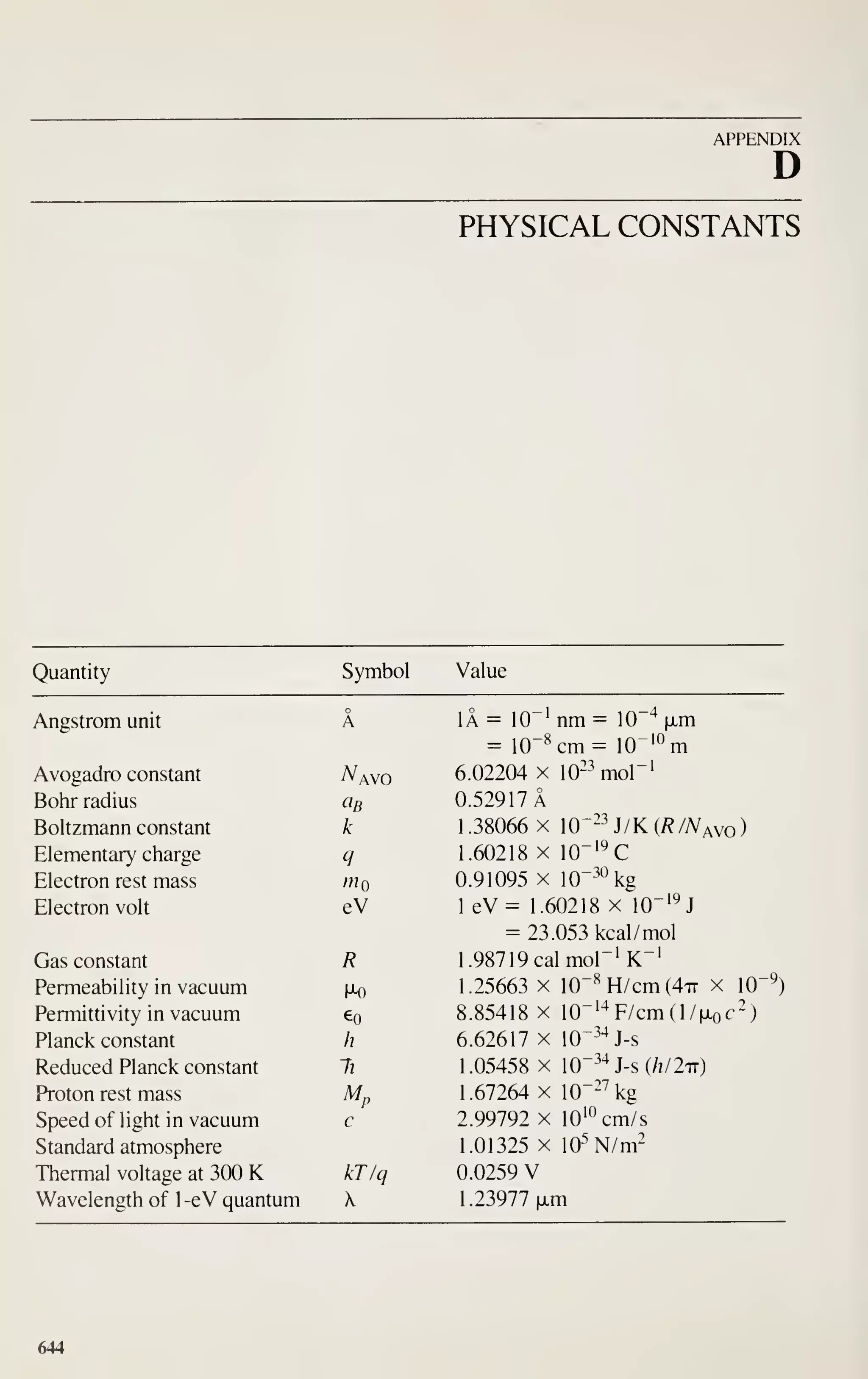

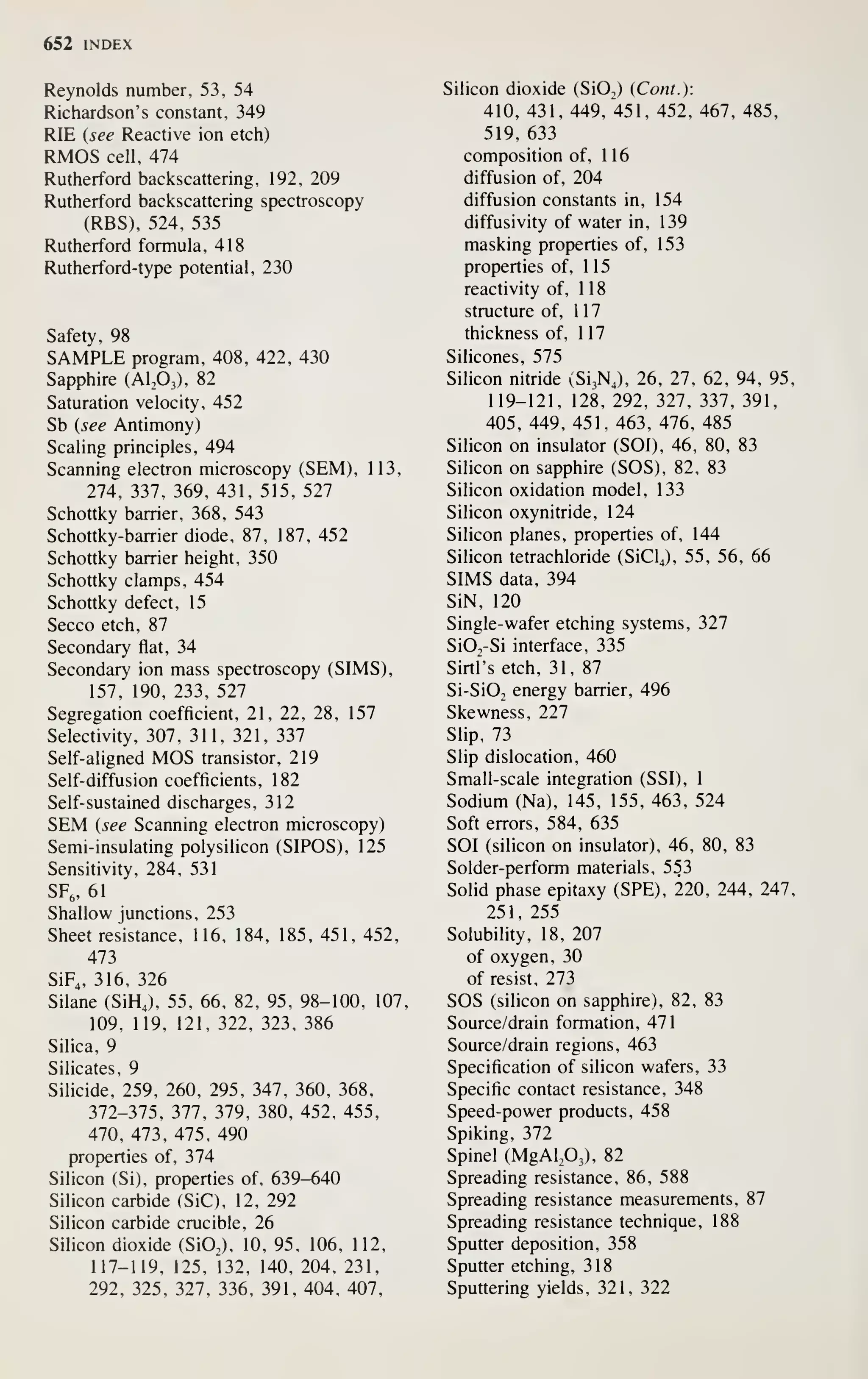

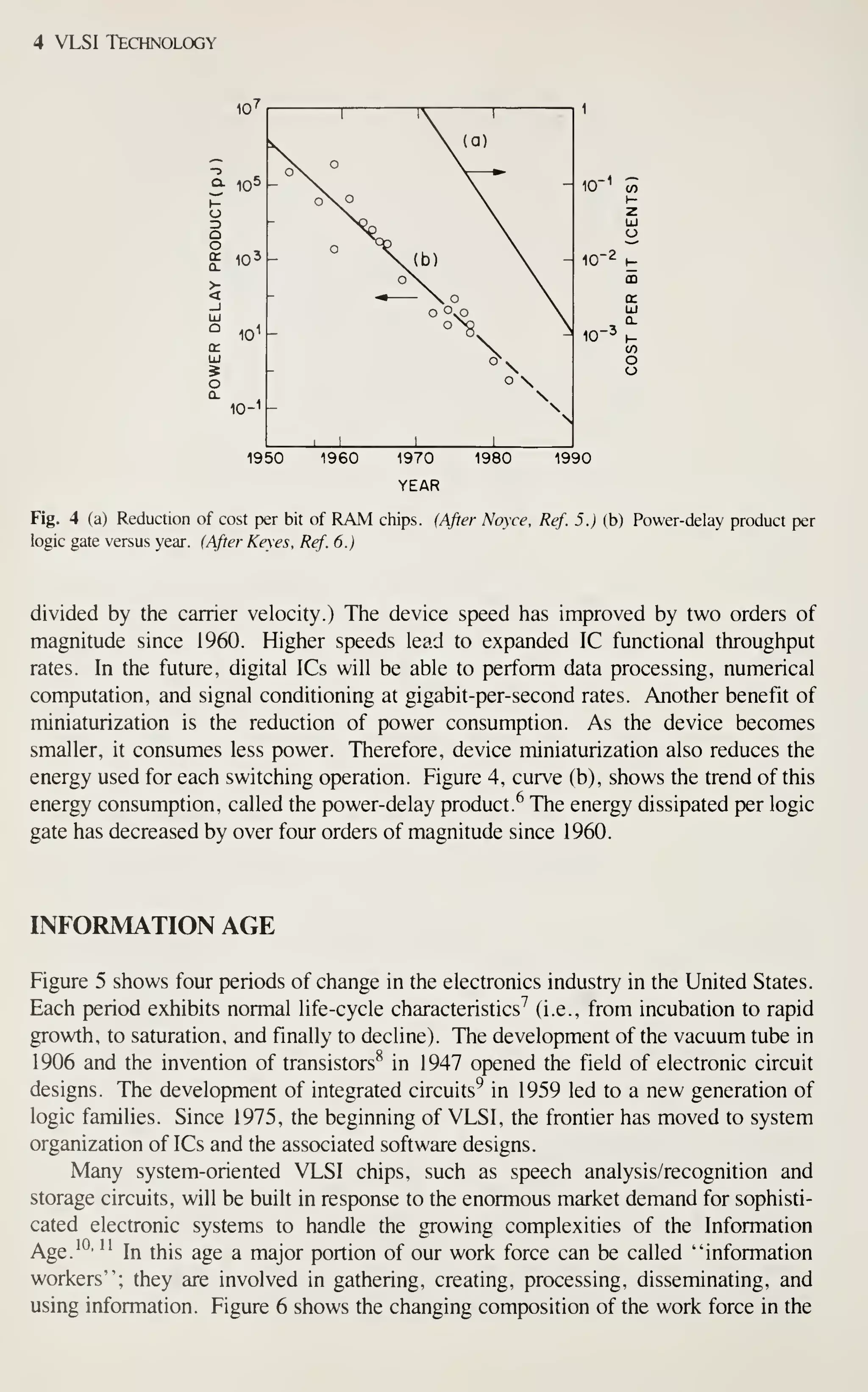

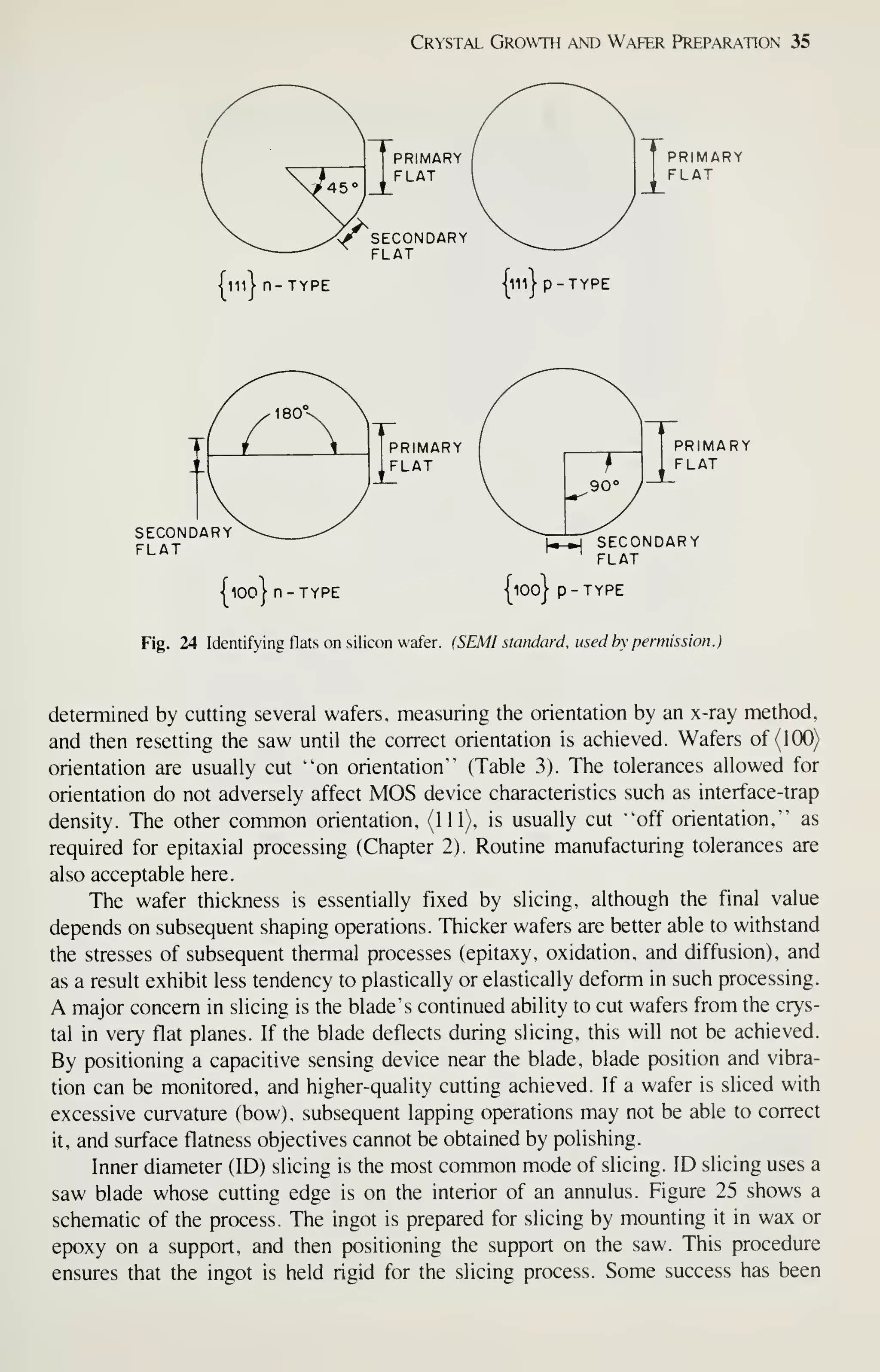

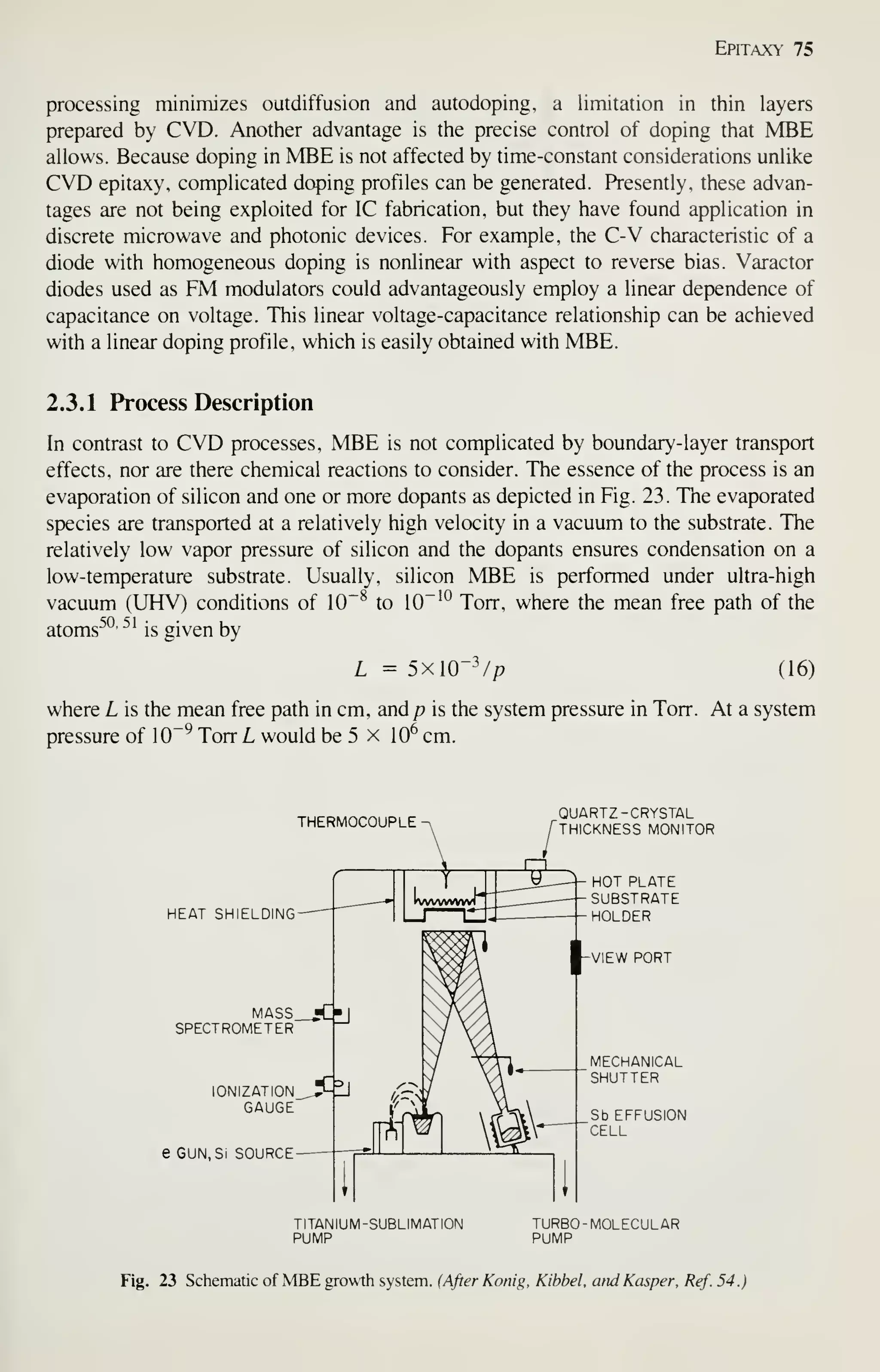

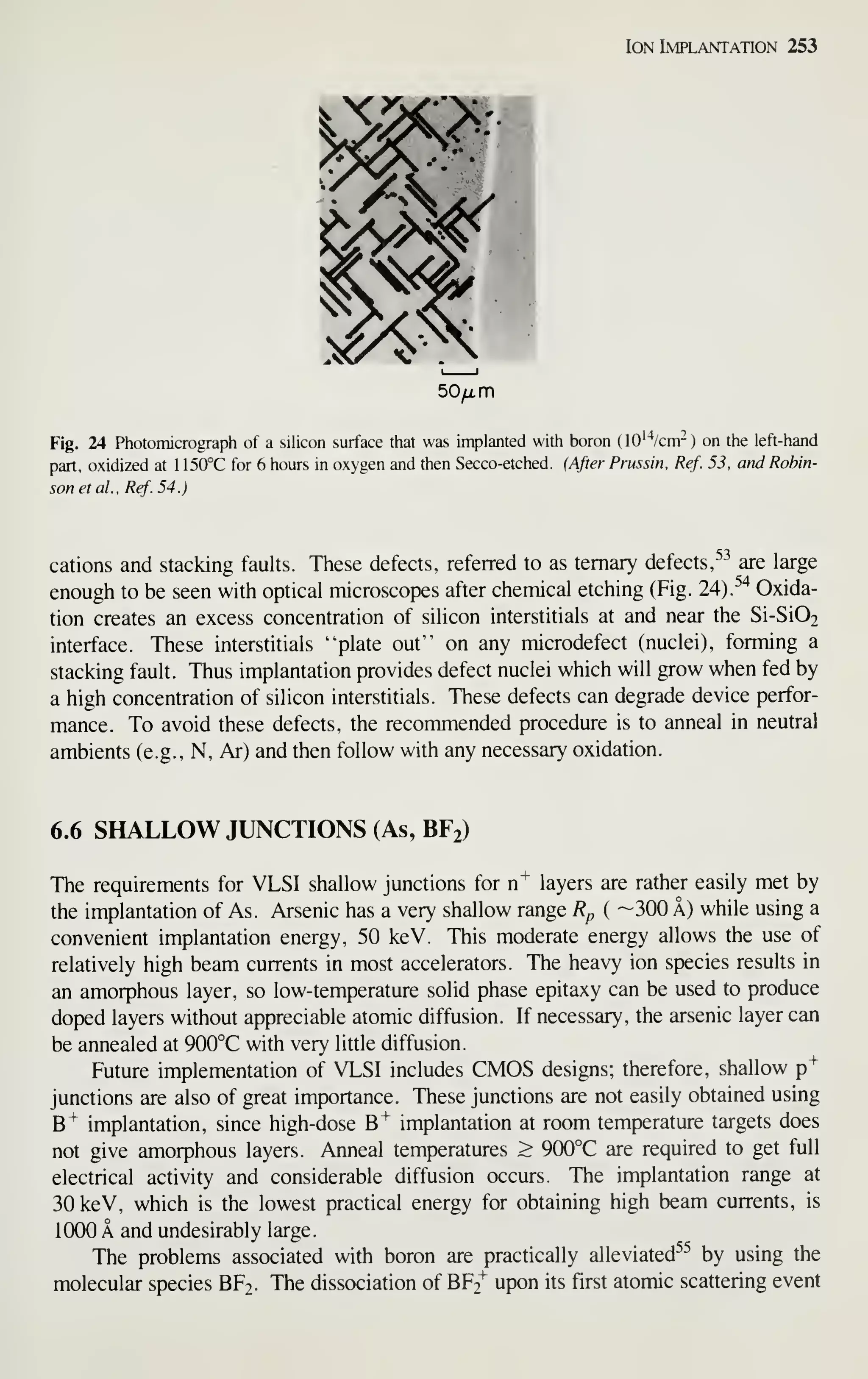

Figure 3, curve (a), shows the exponential growth of the number of components per

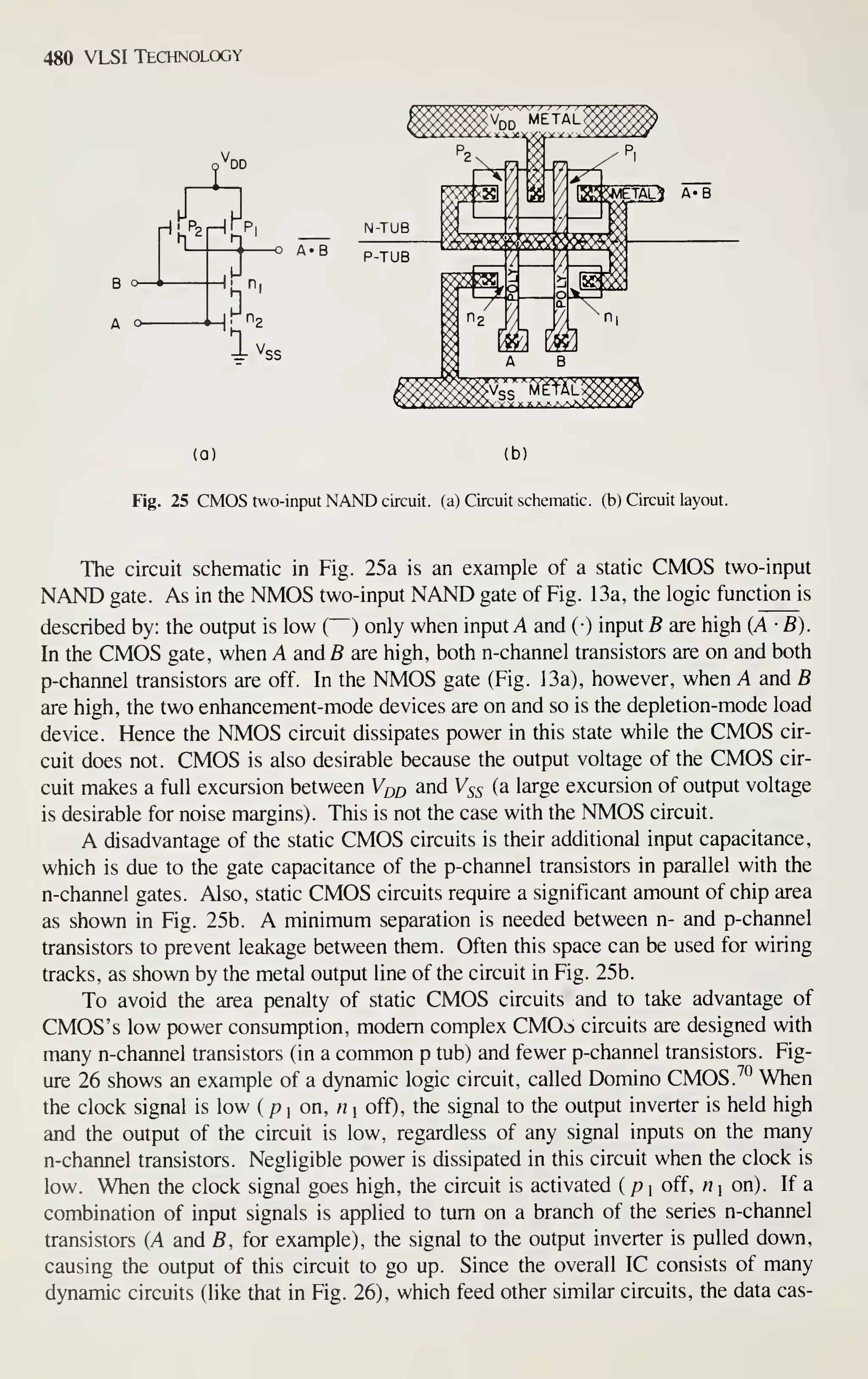

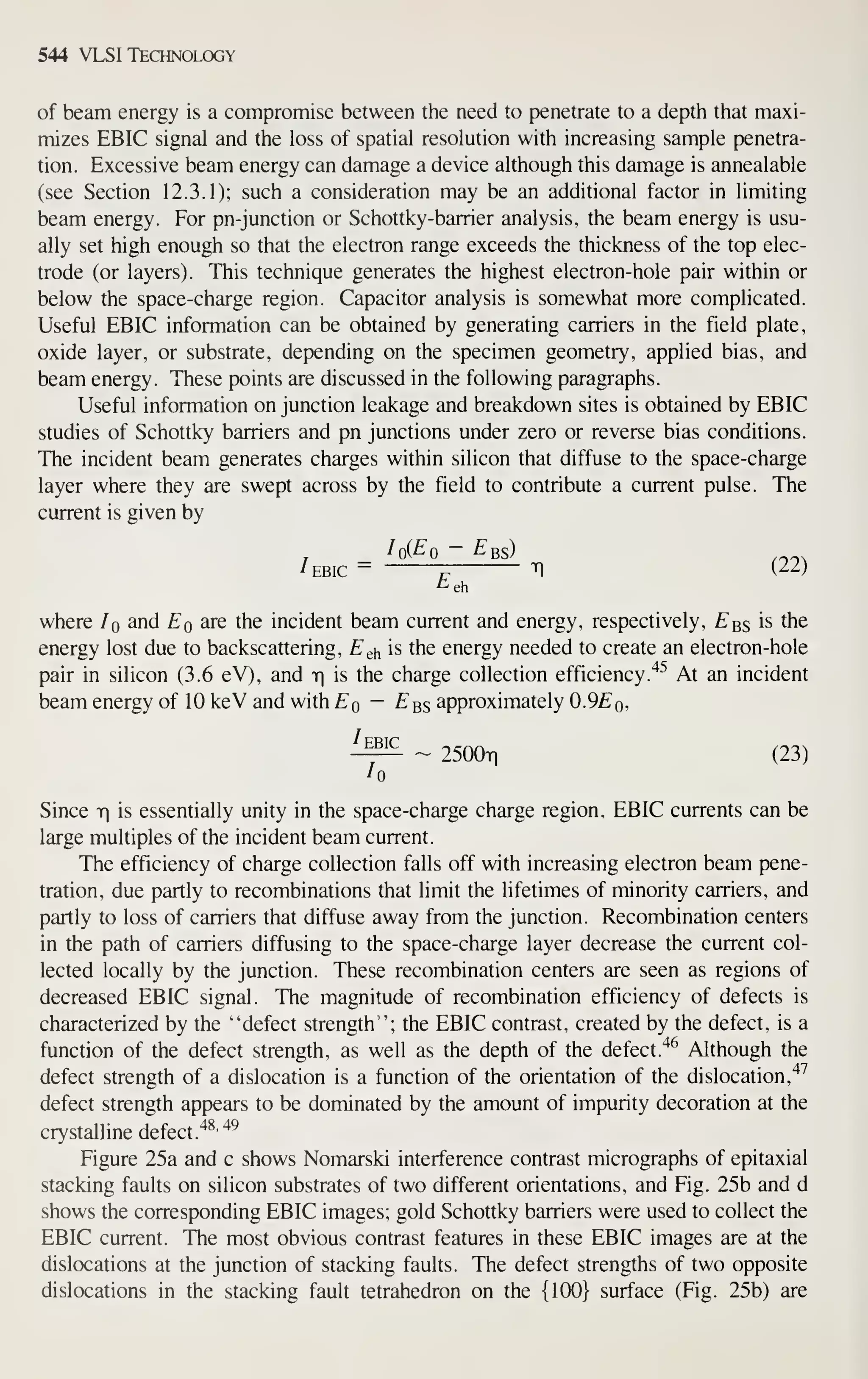

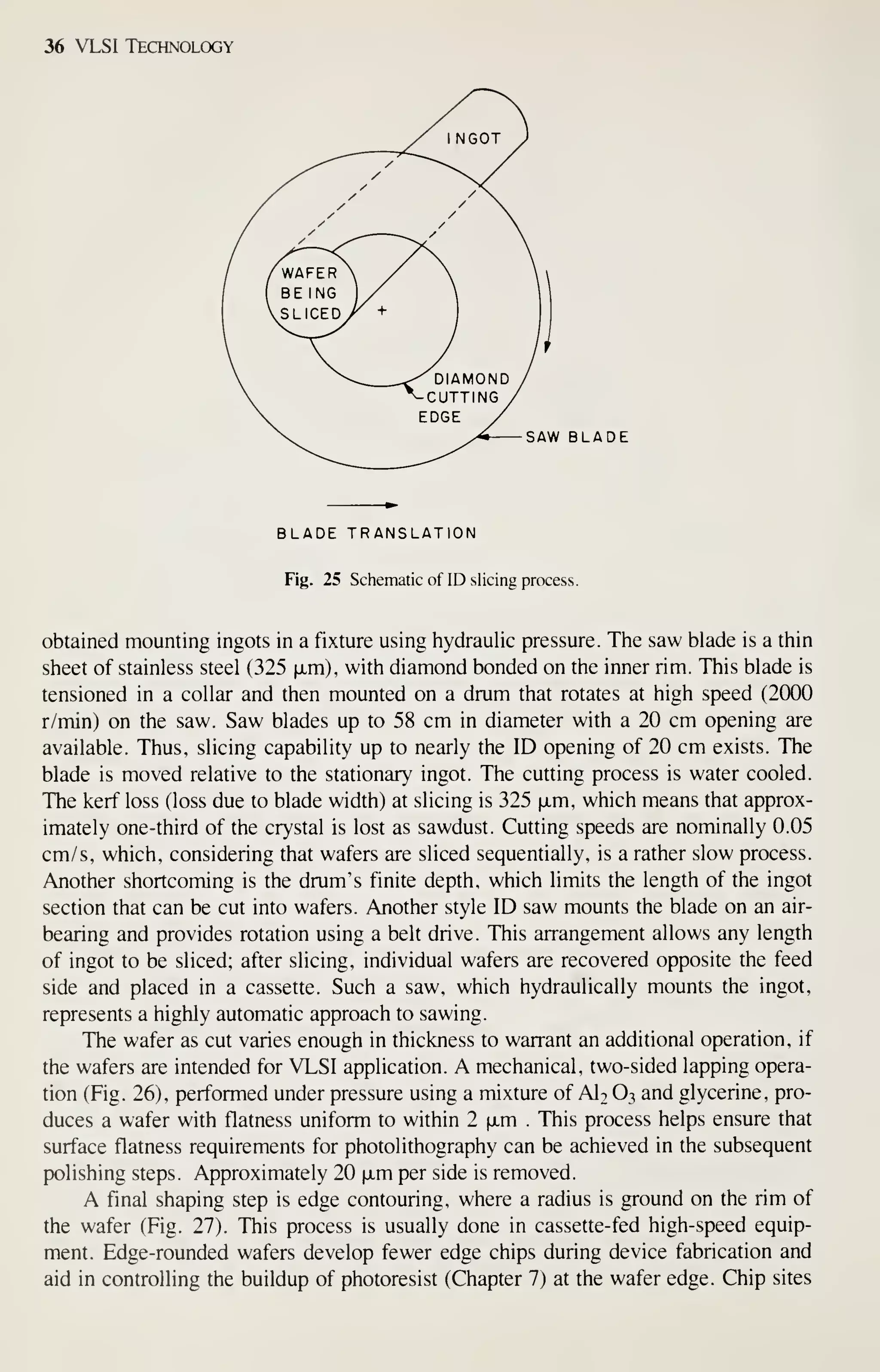

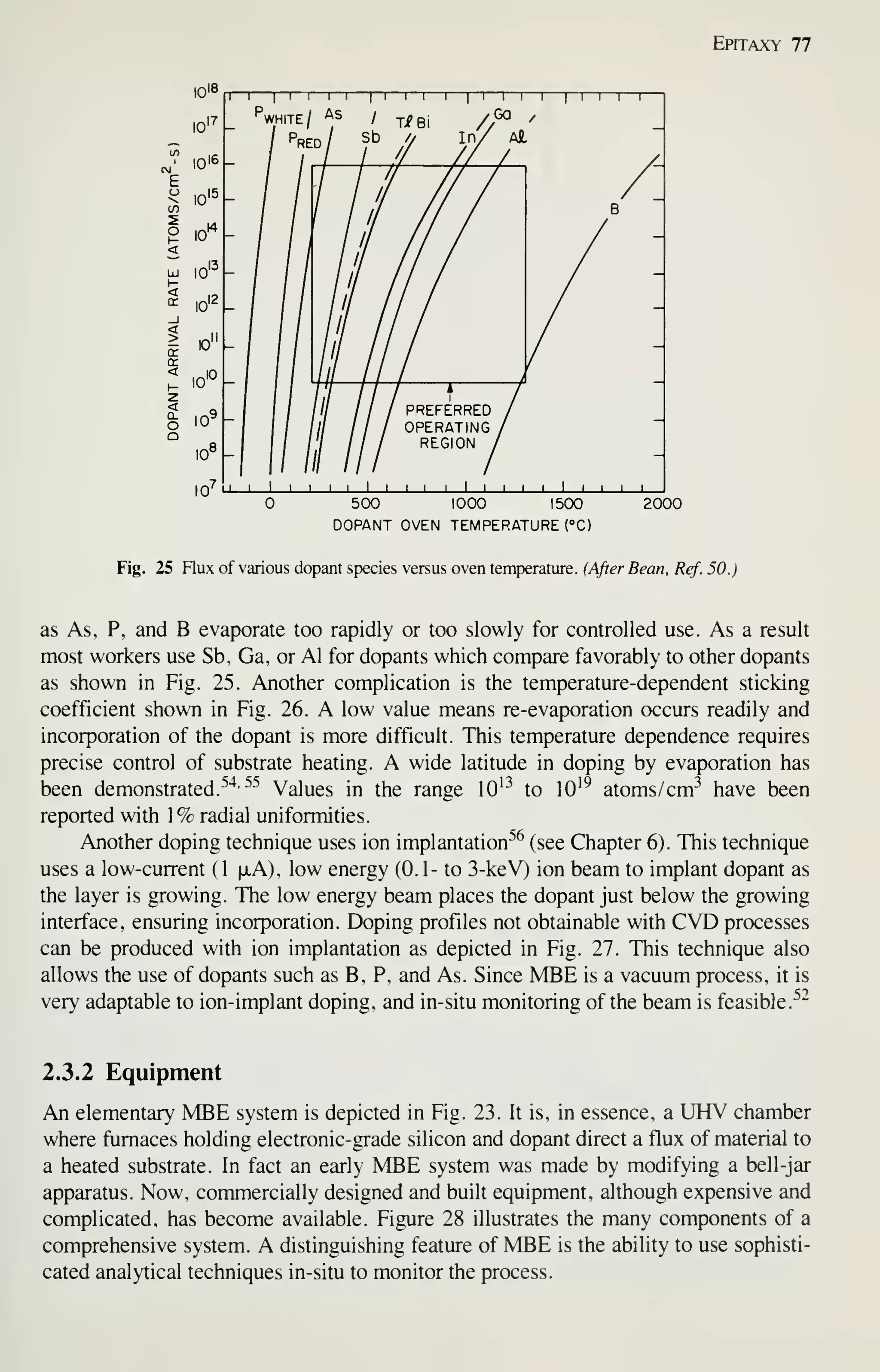

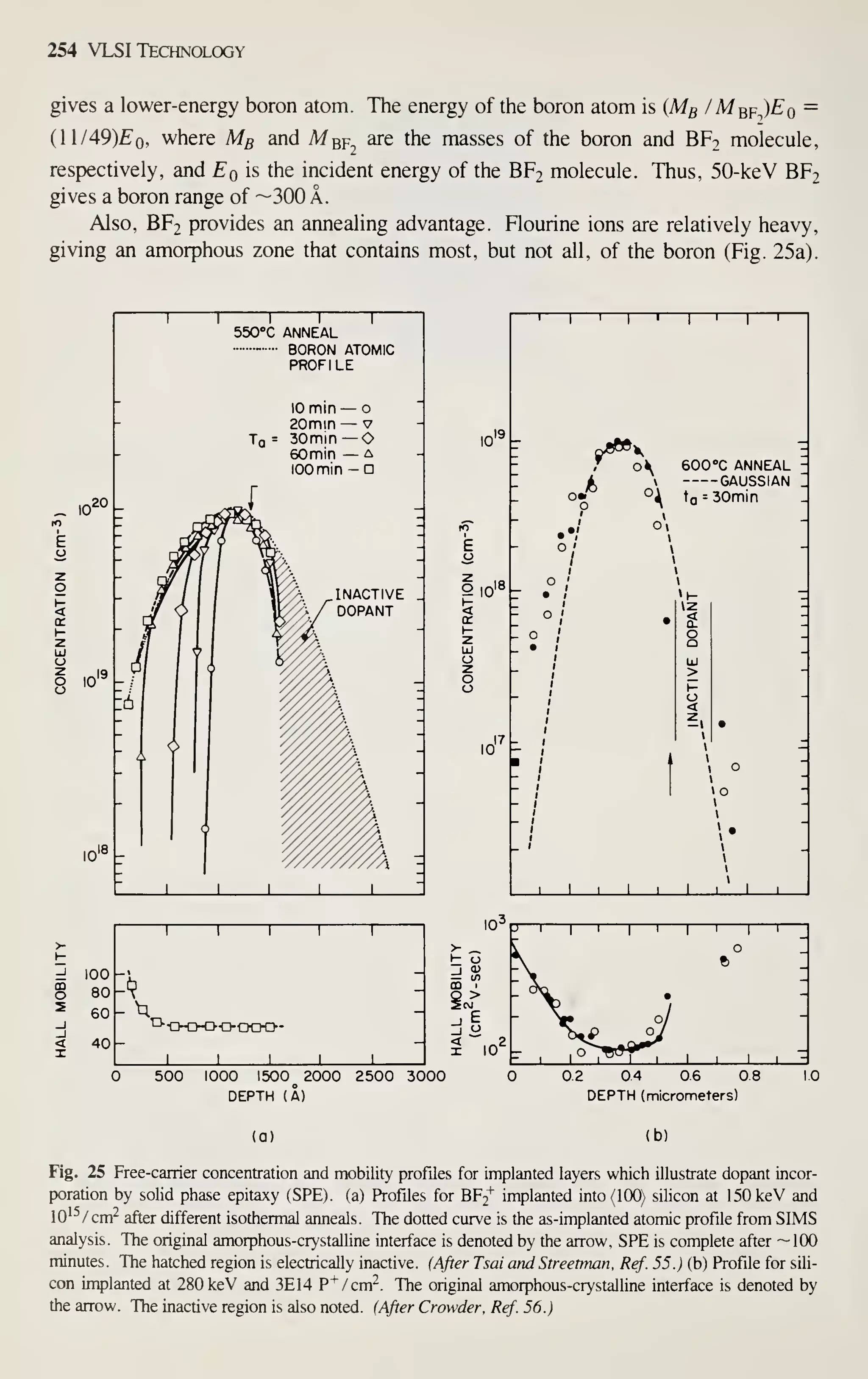

IC chip.'^ Note that IC complexity has advanced from small-scale integration (SSI) to

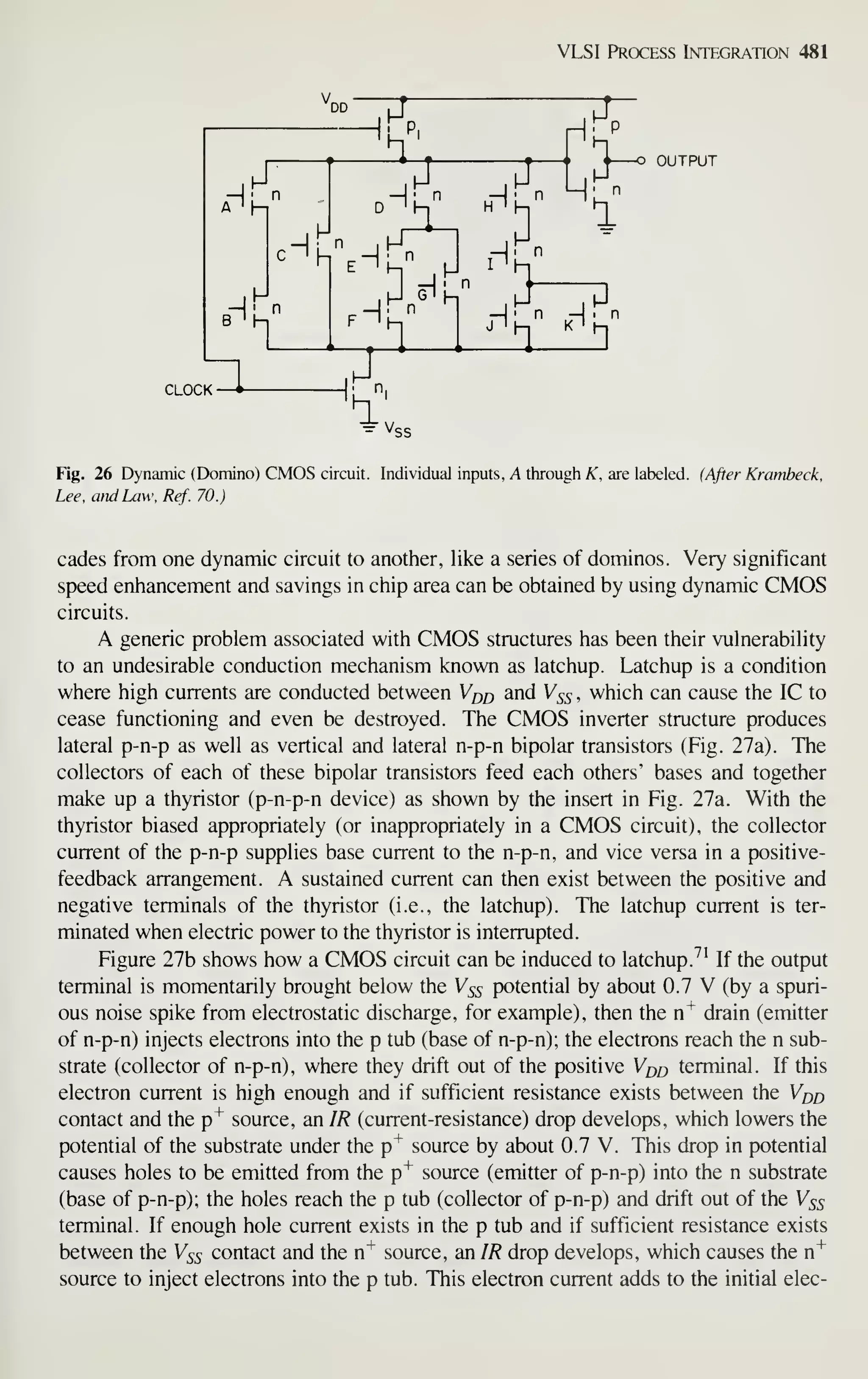

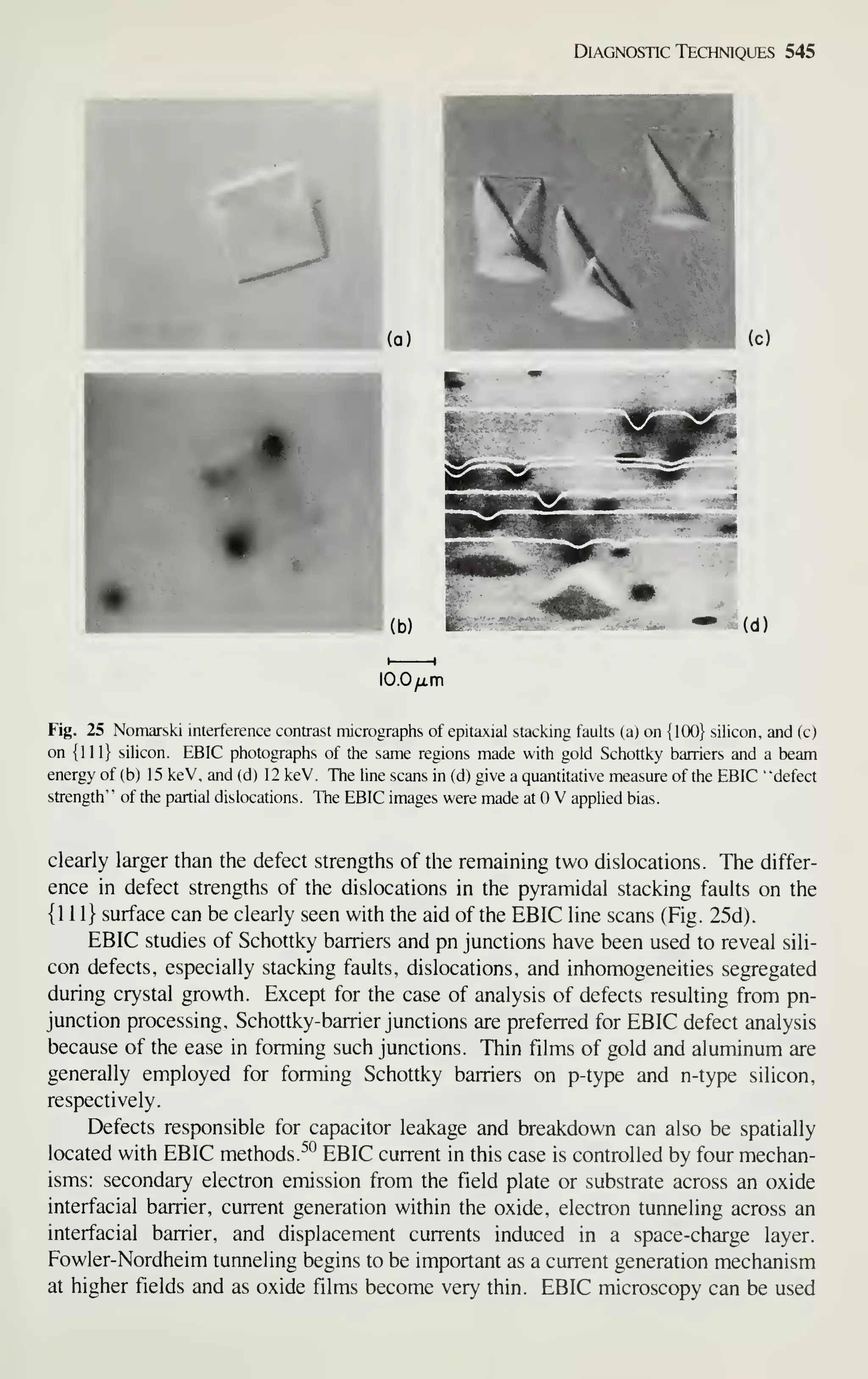

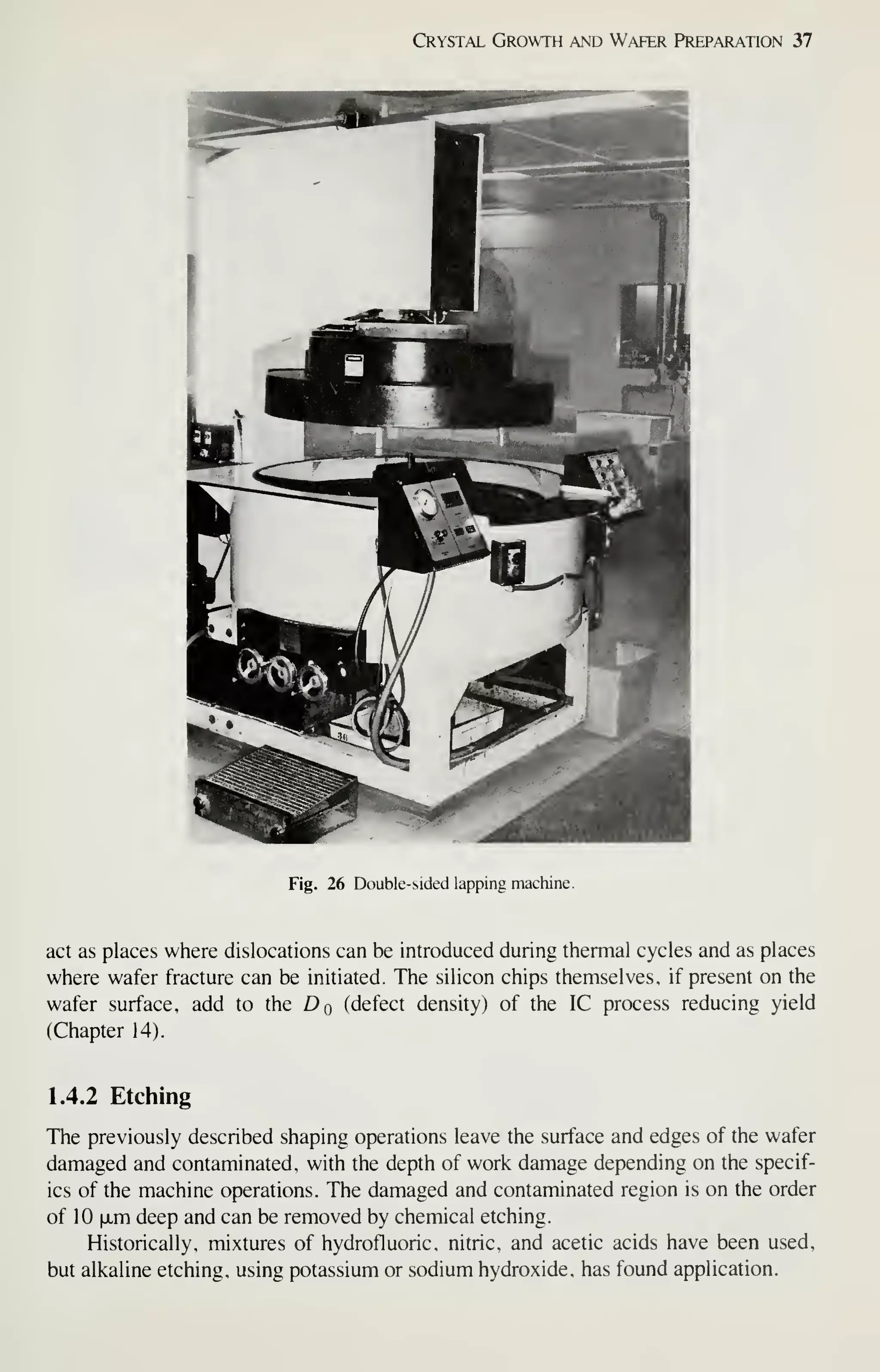

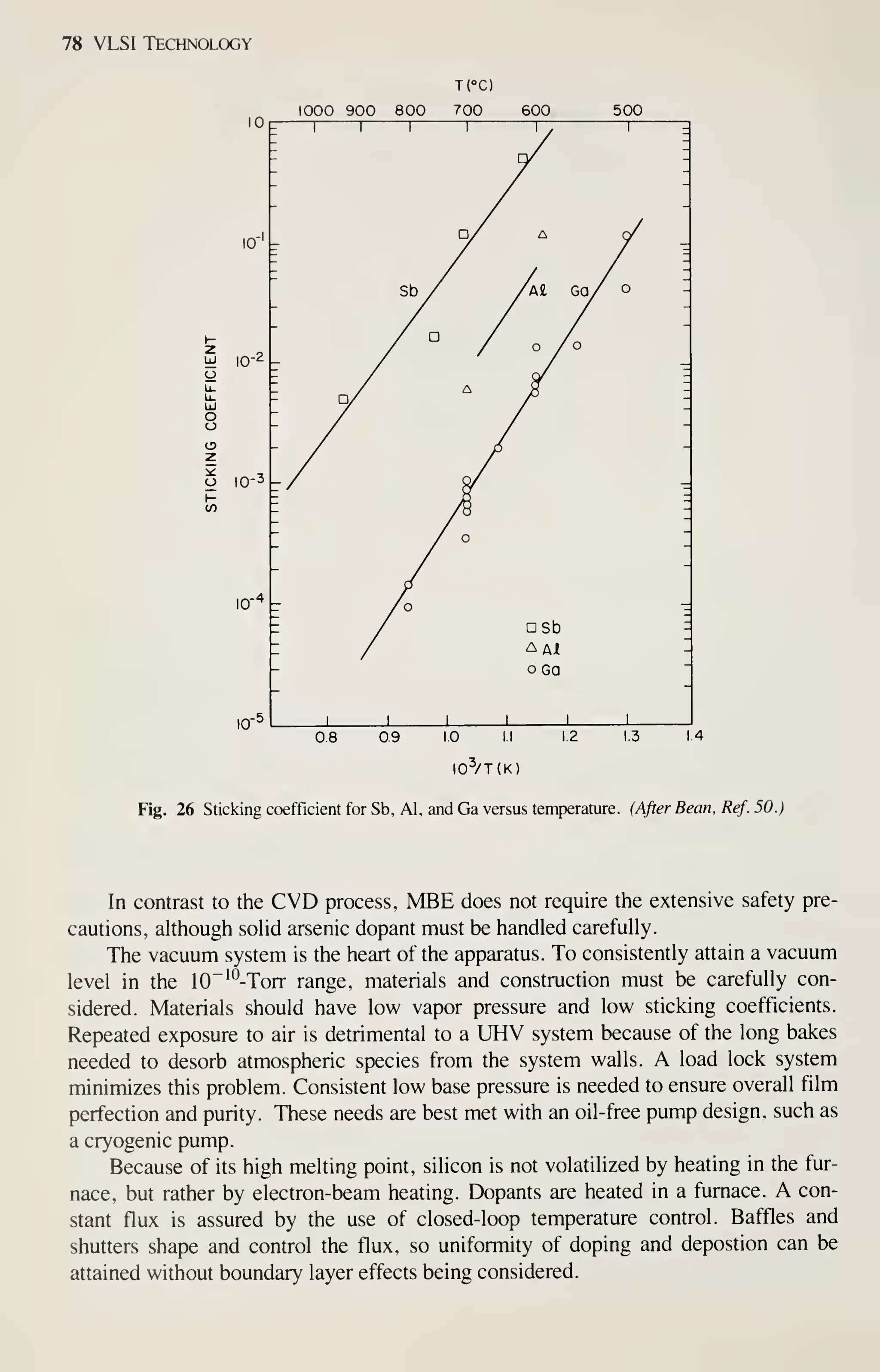

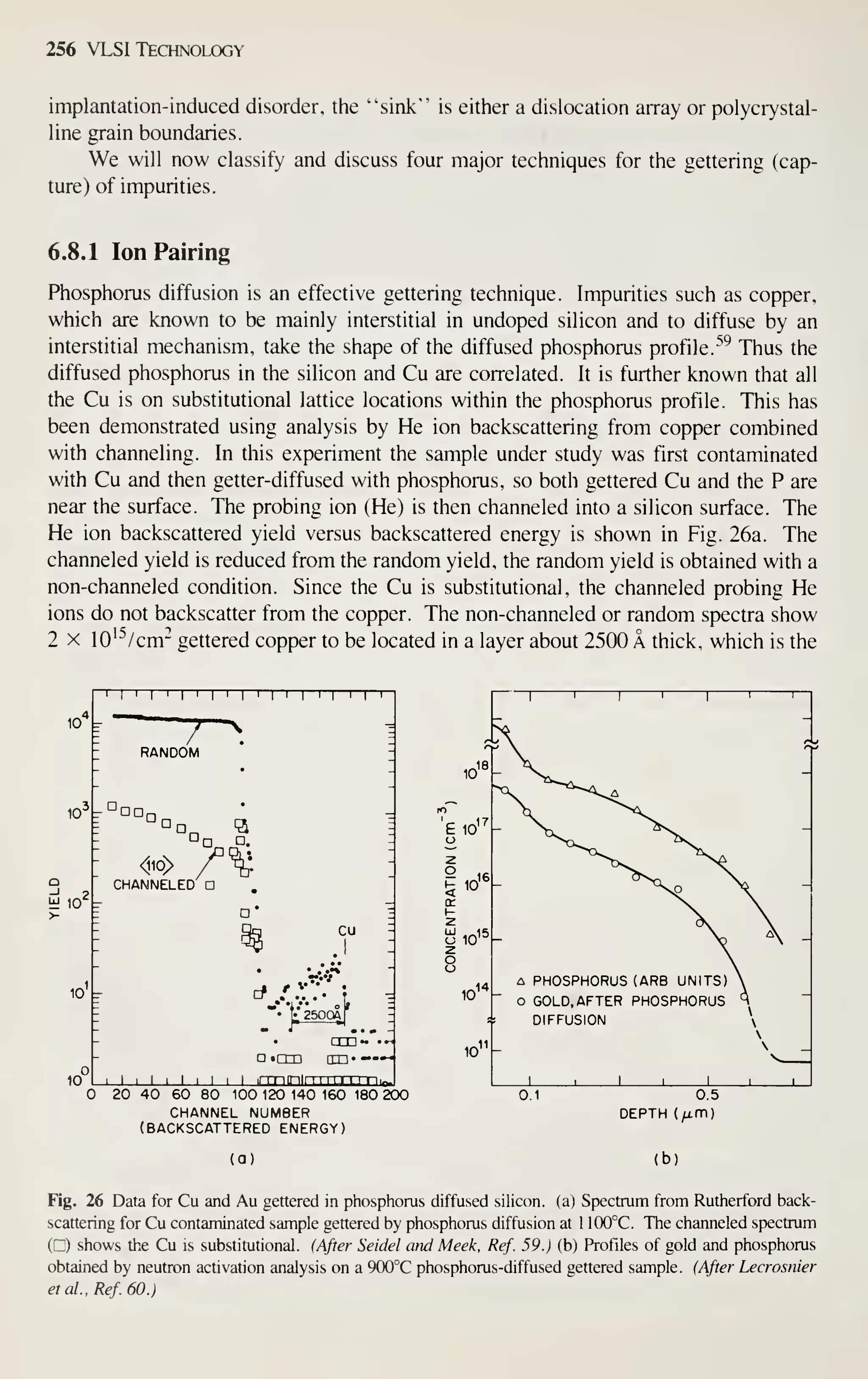

medium-scale integration (MSI), to large-scale integration (LSI), and finally to very-

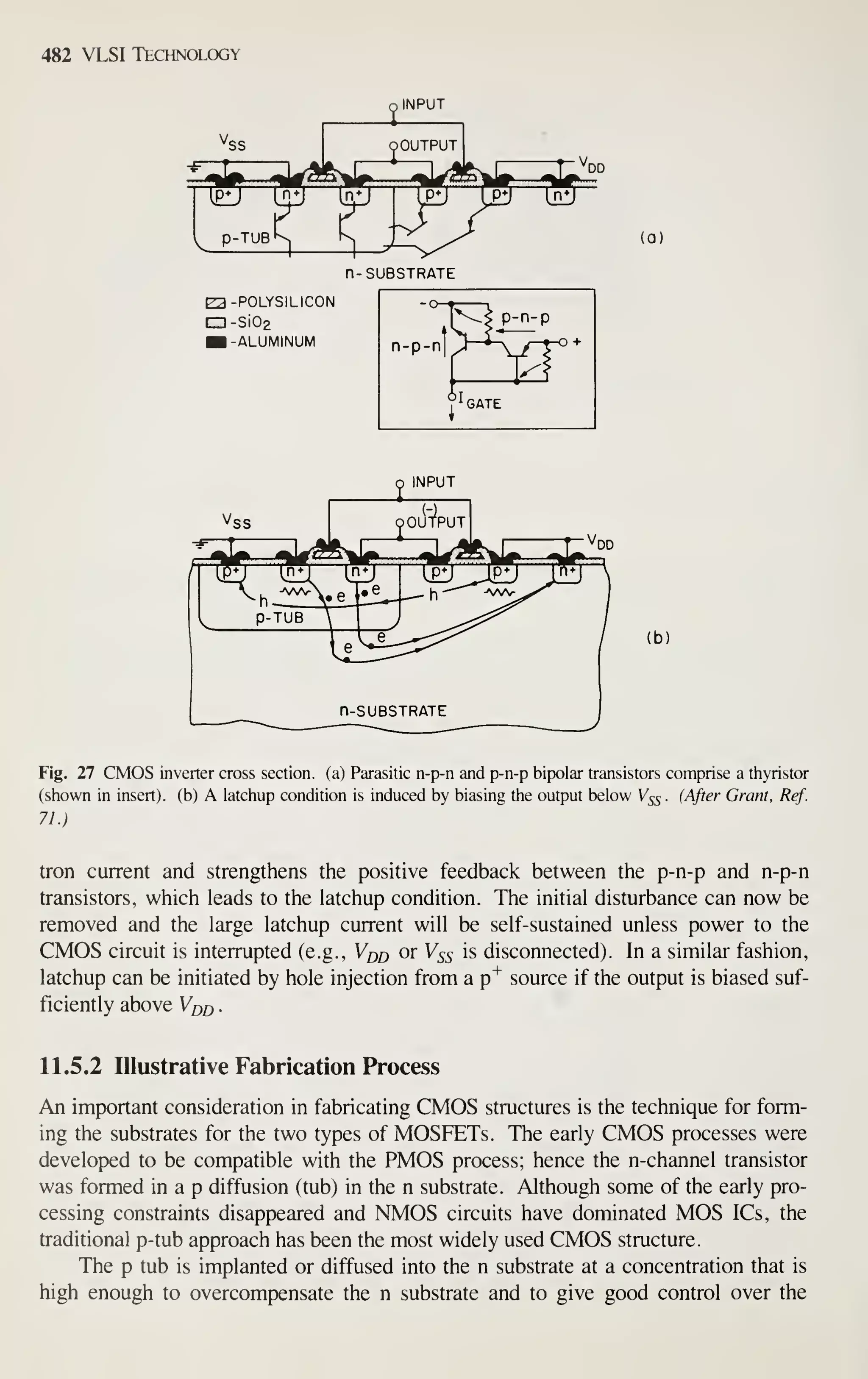

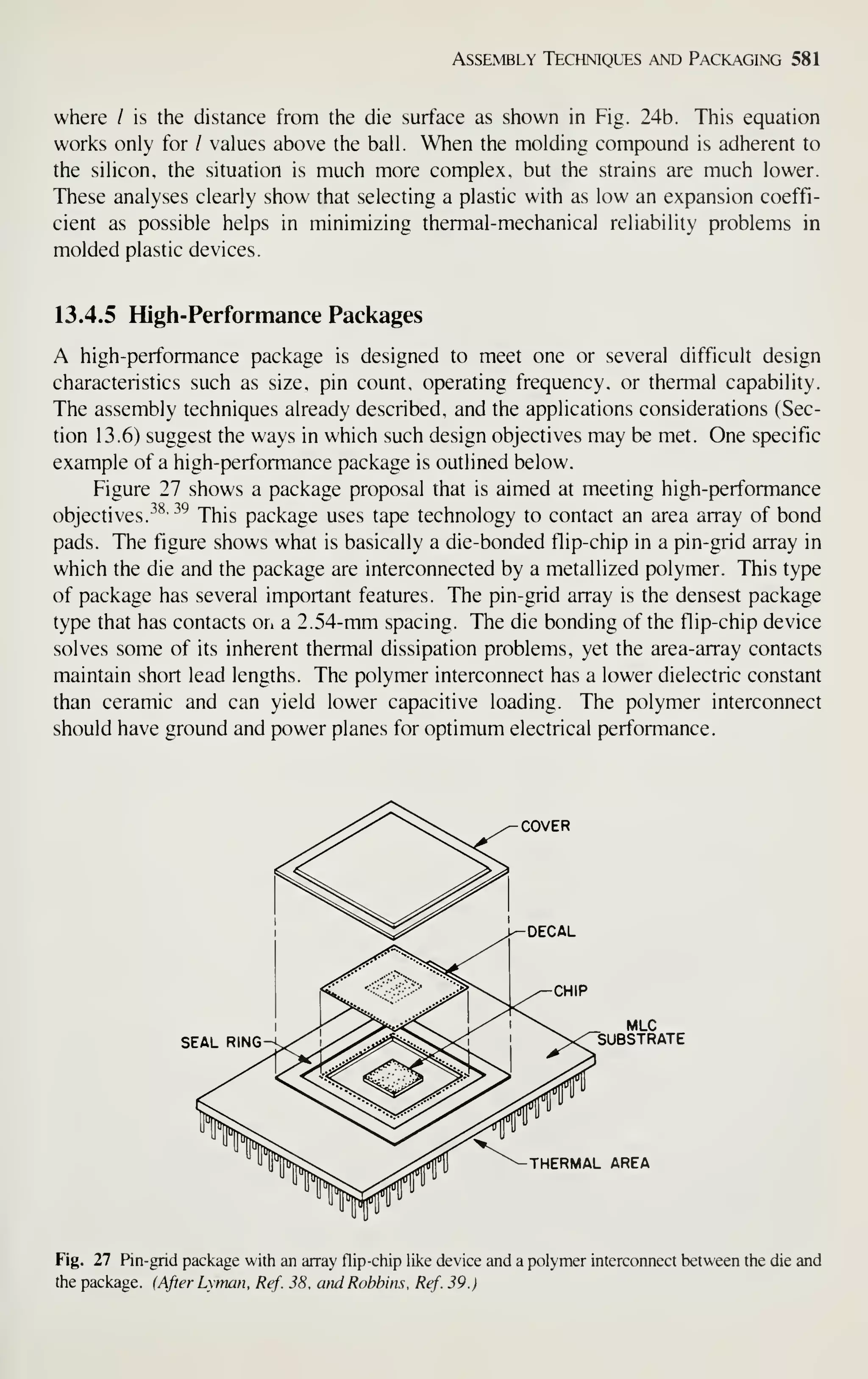

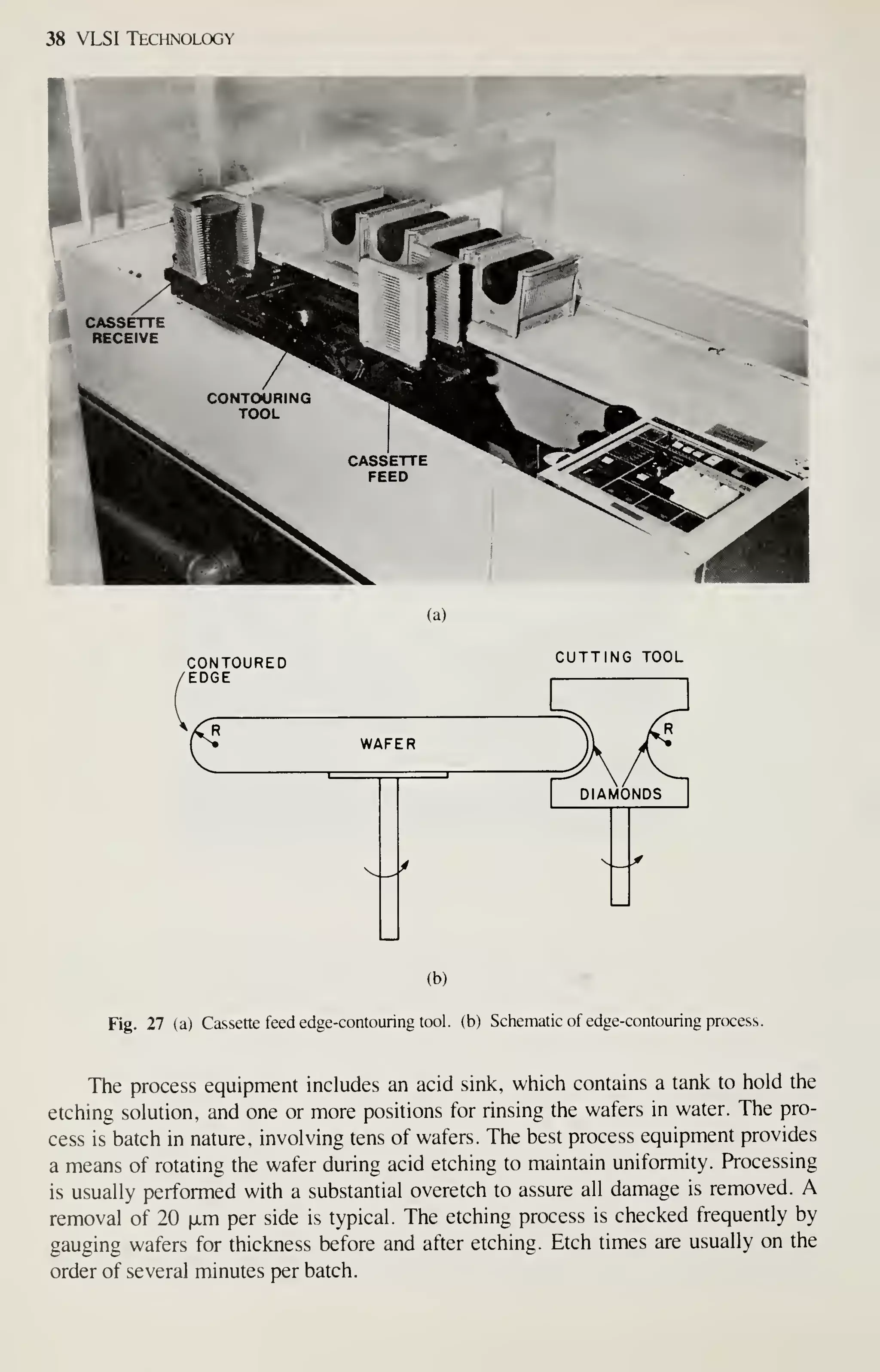

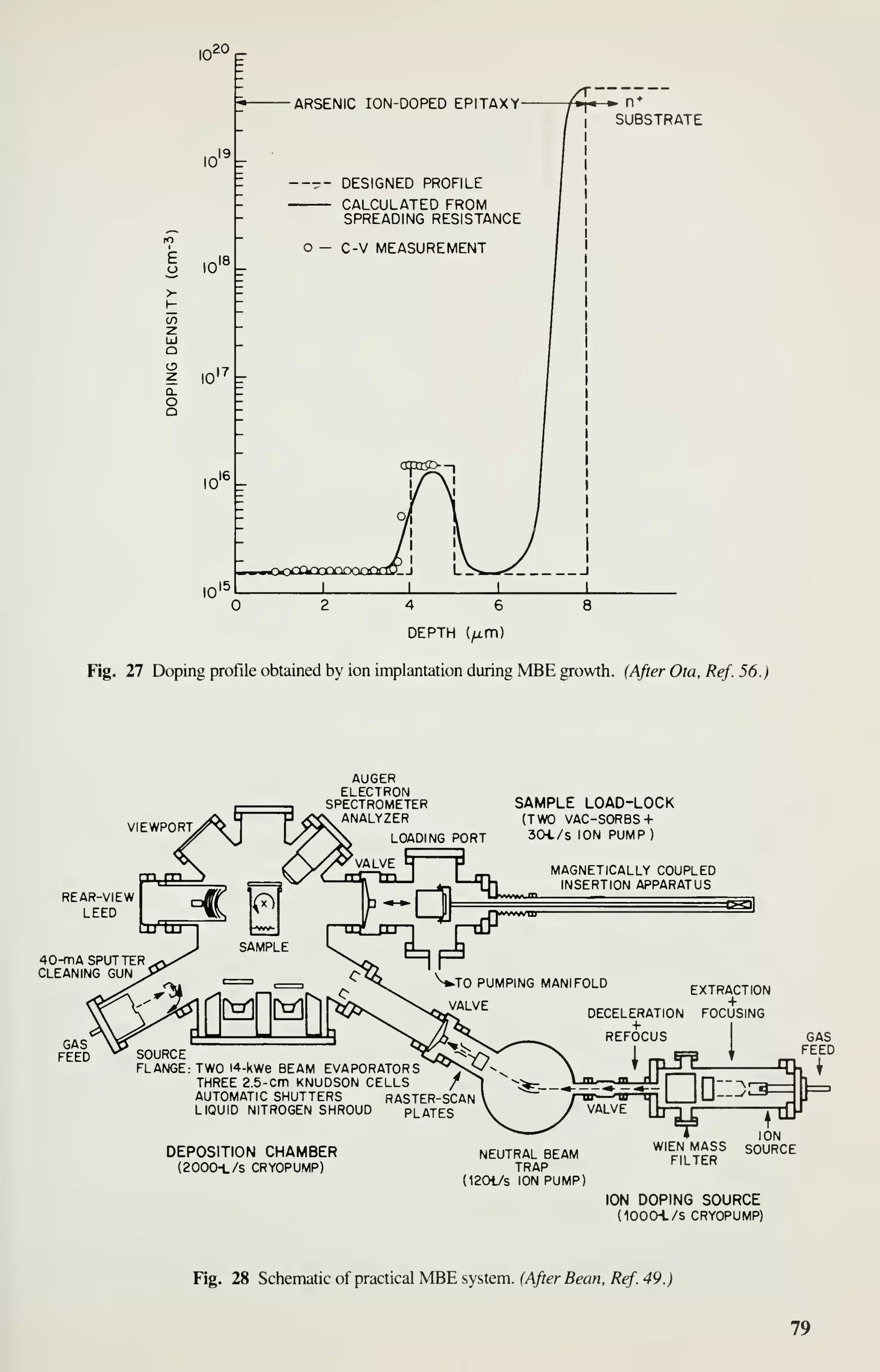

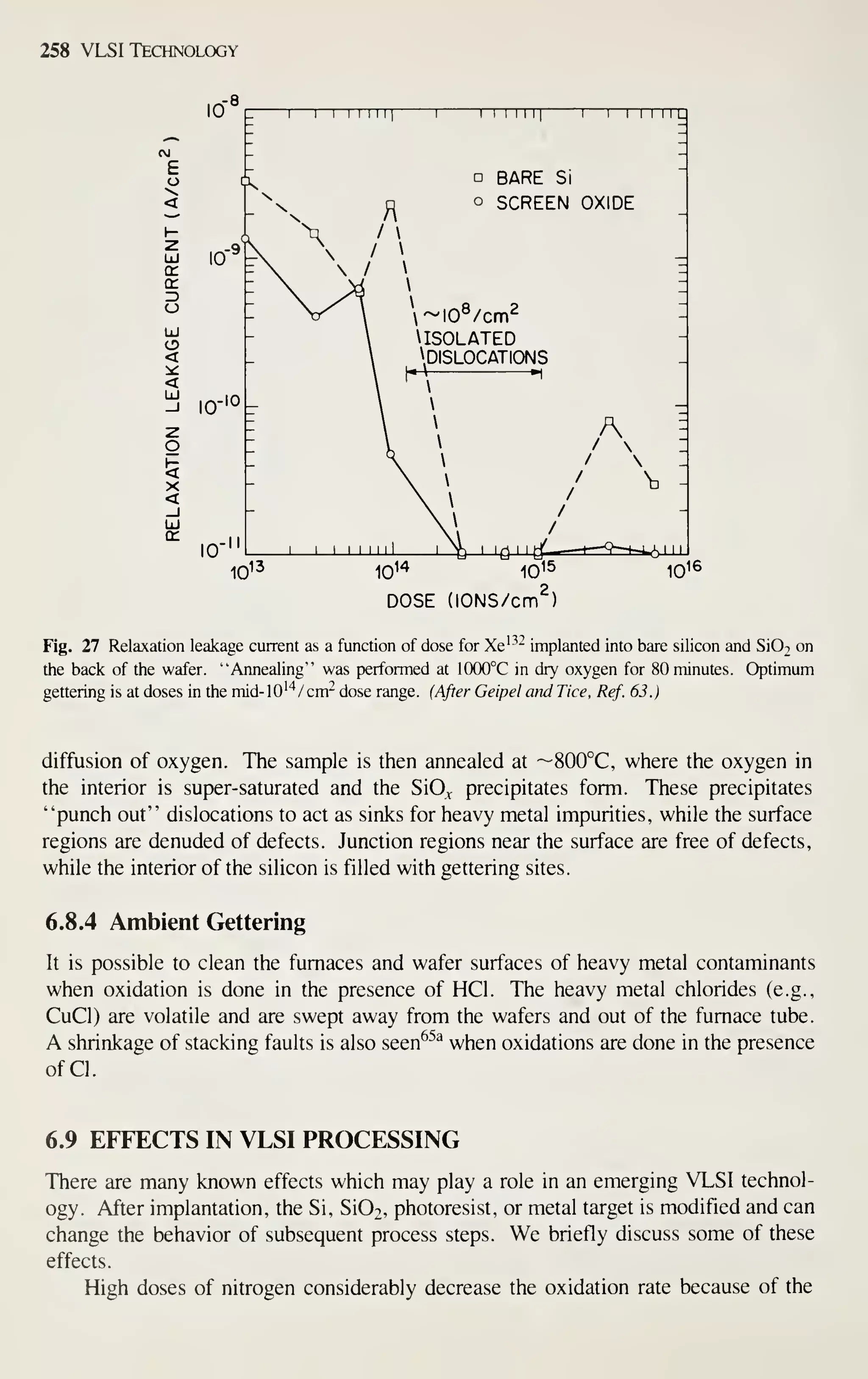

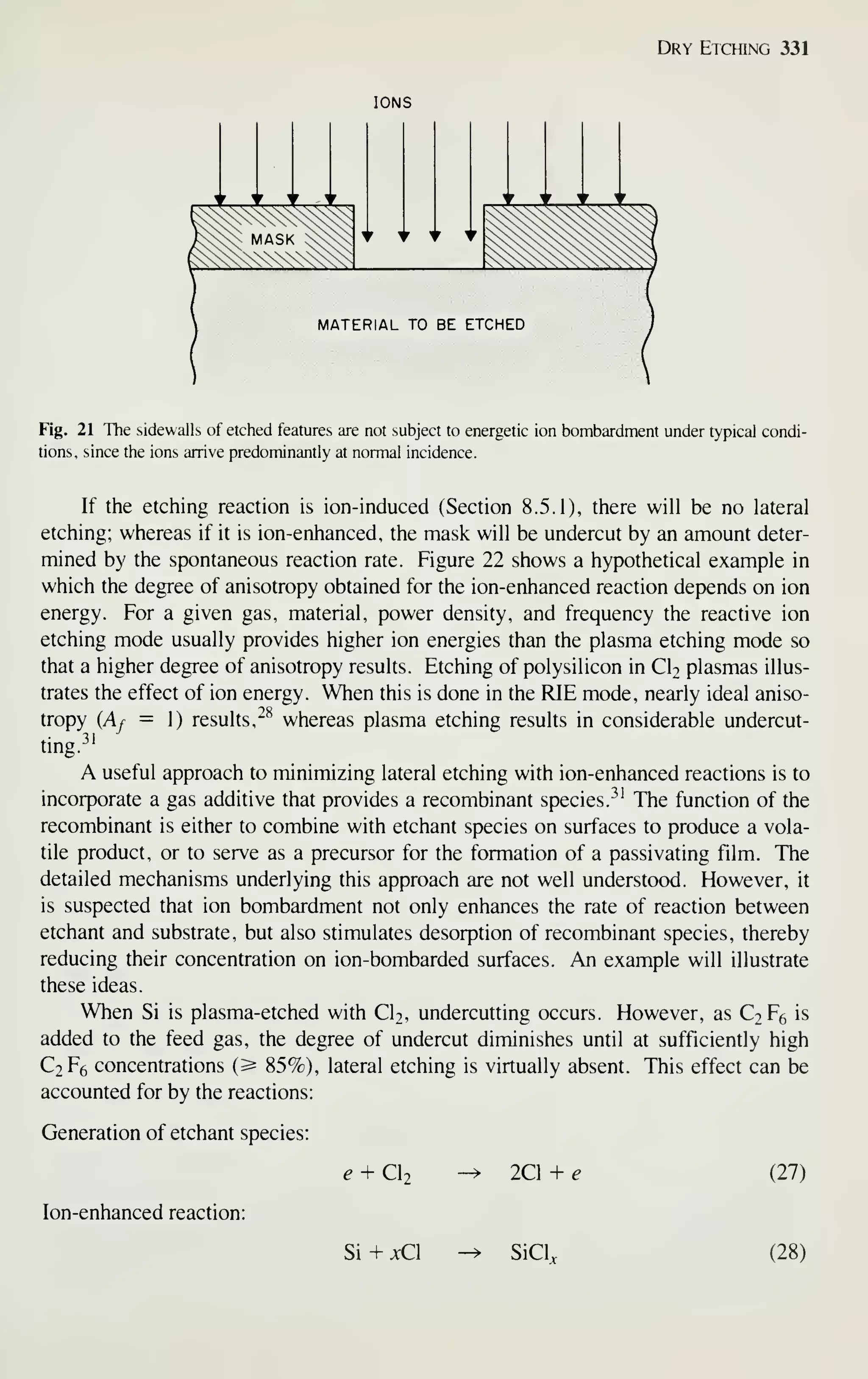

large-scale integration (VLSI), which has 10^ or more components per chip.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-21-2048.jpg)

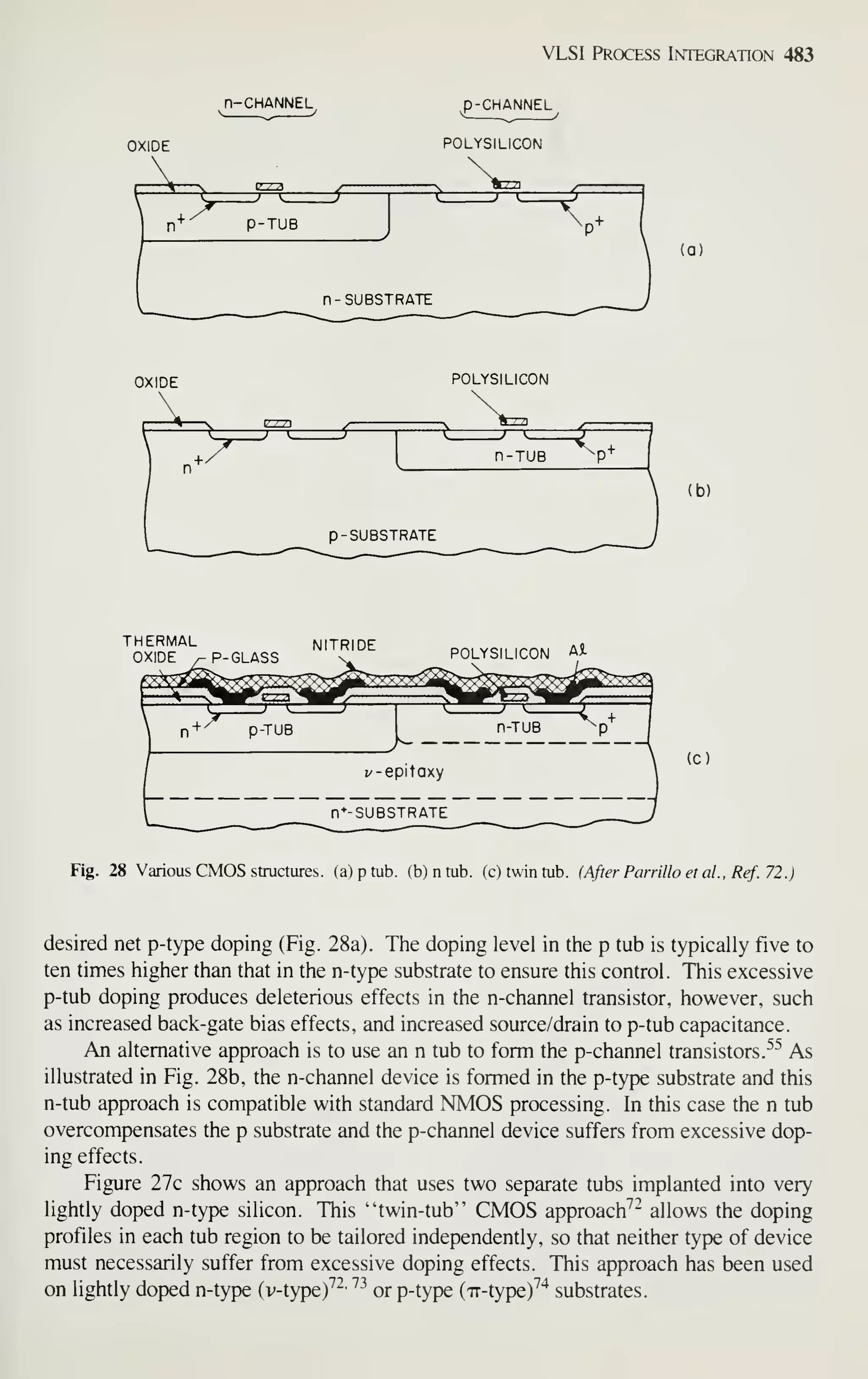

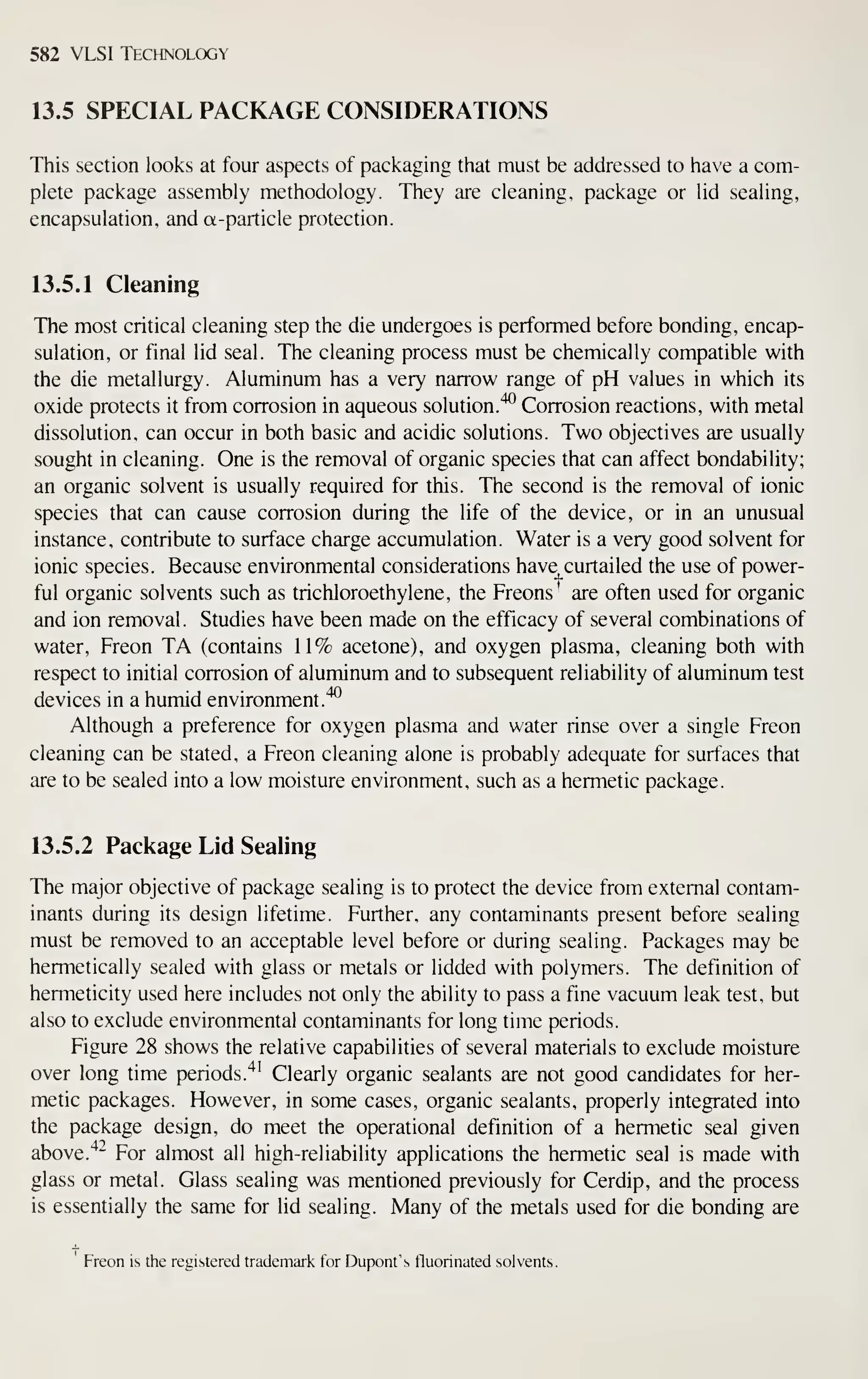

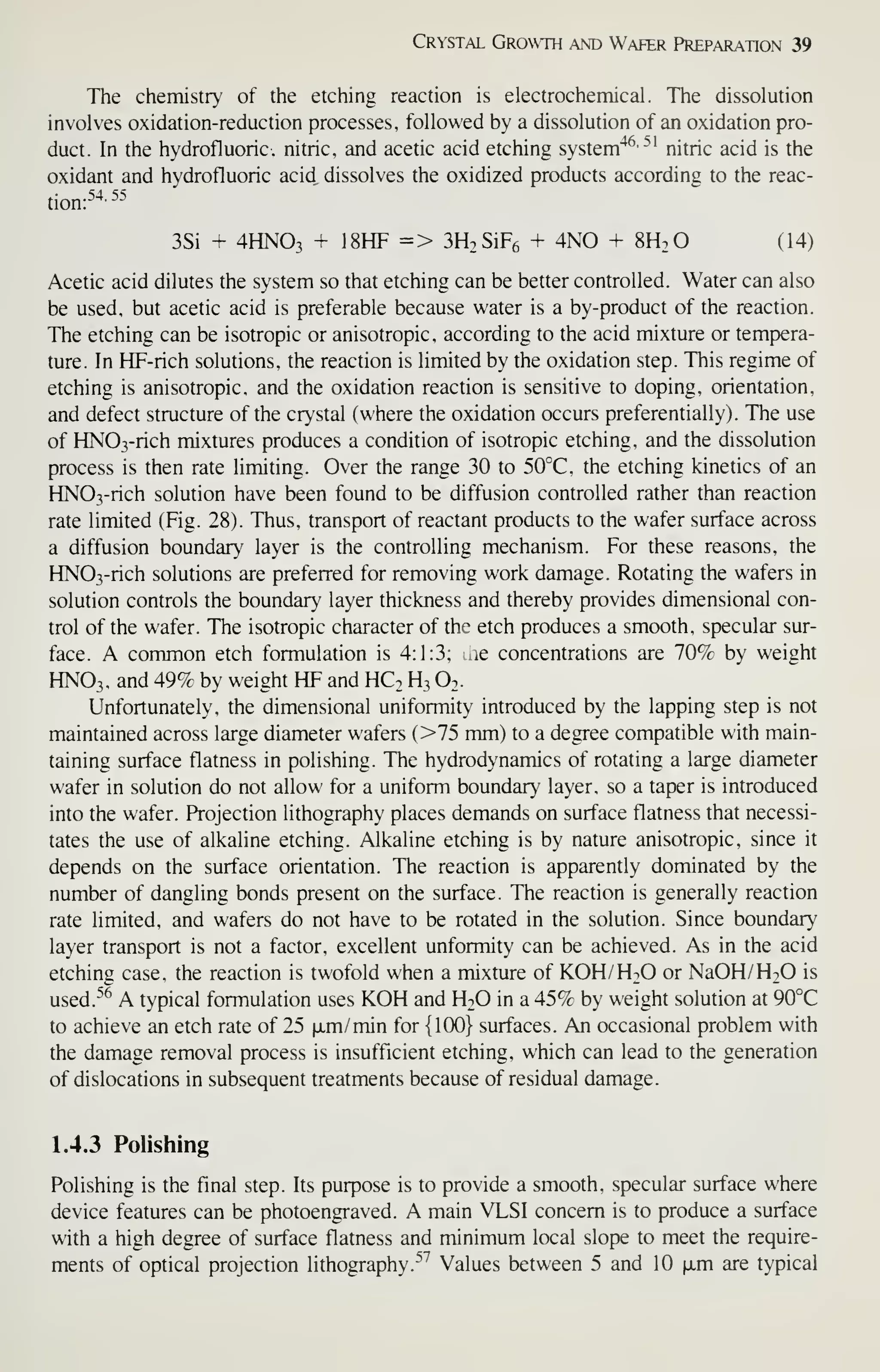

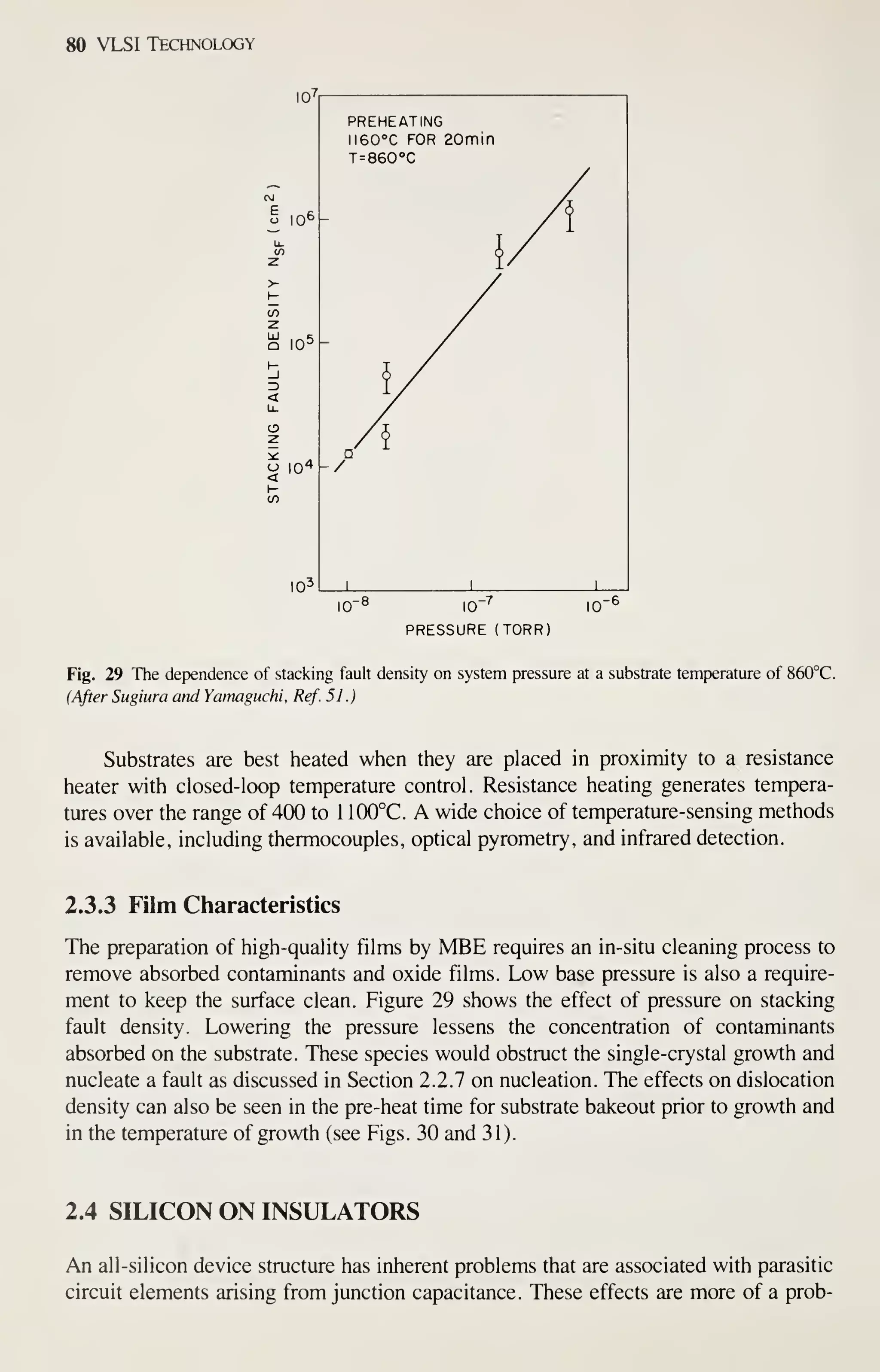

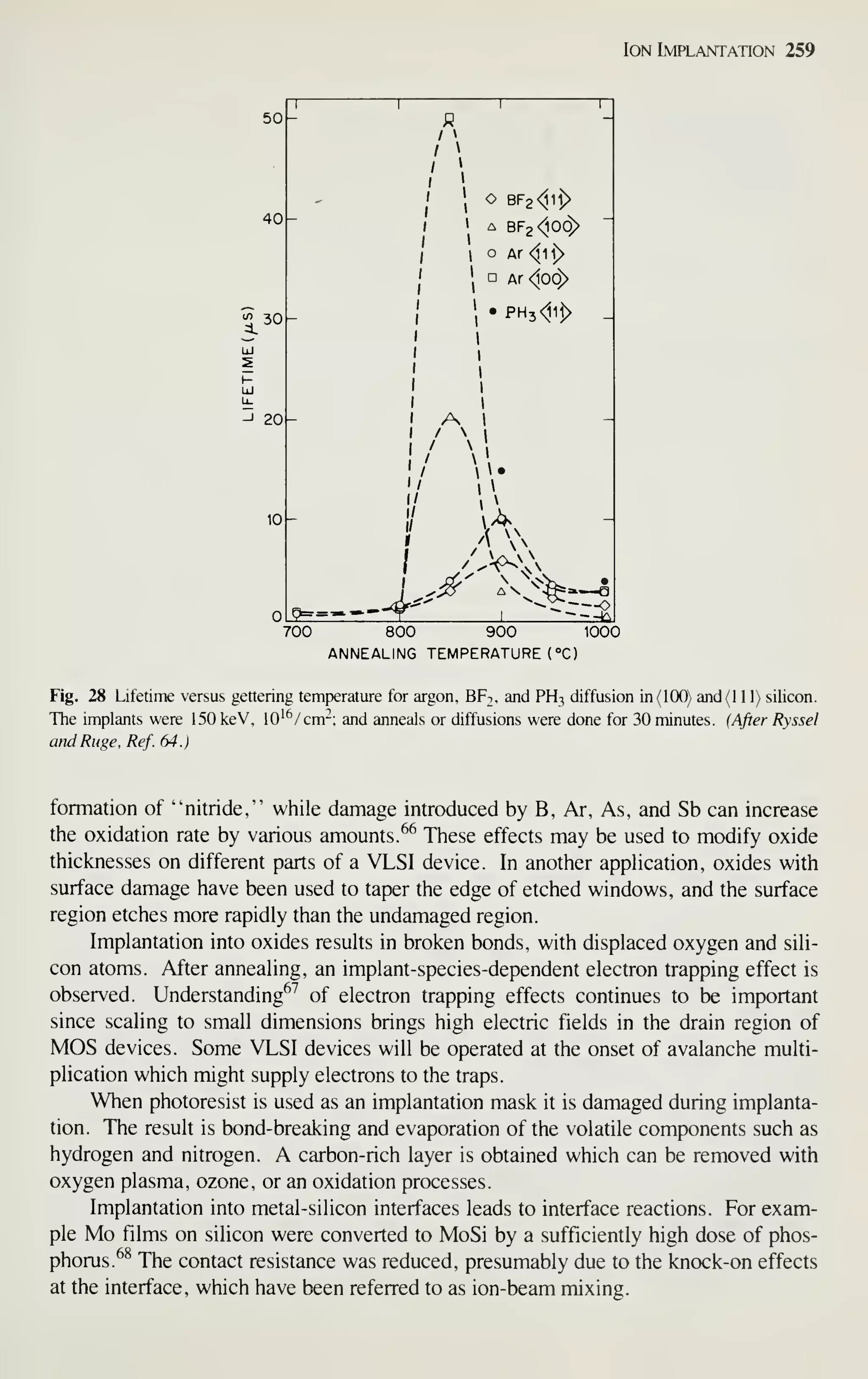

![2 VLSI Technology

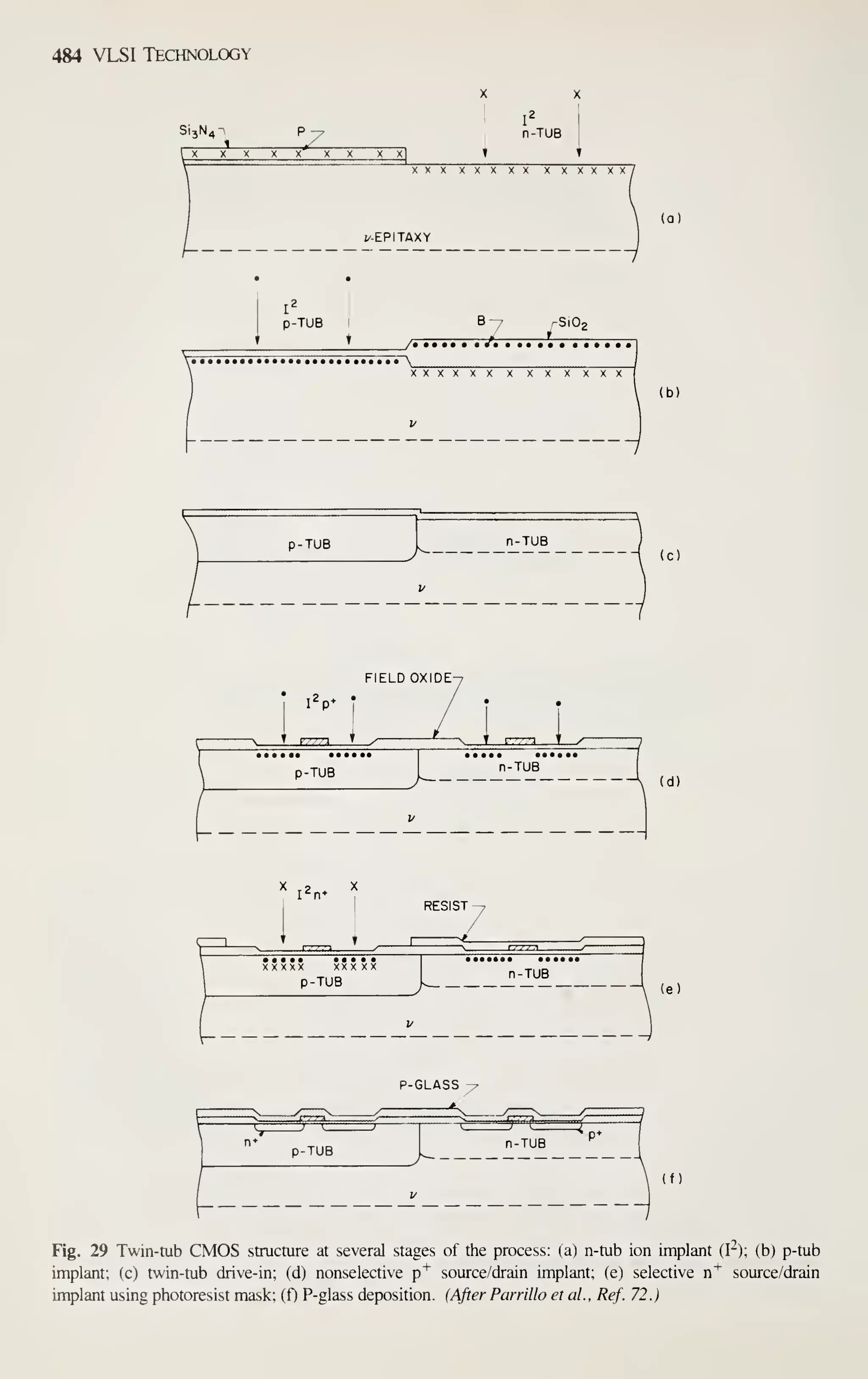

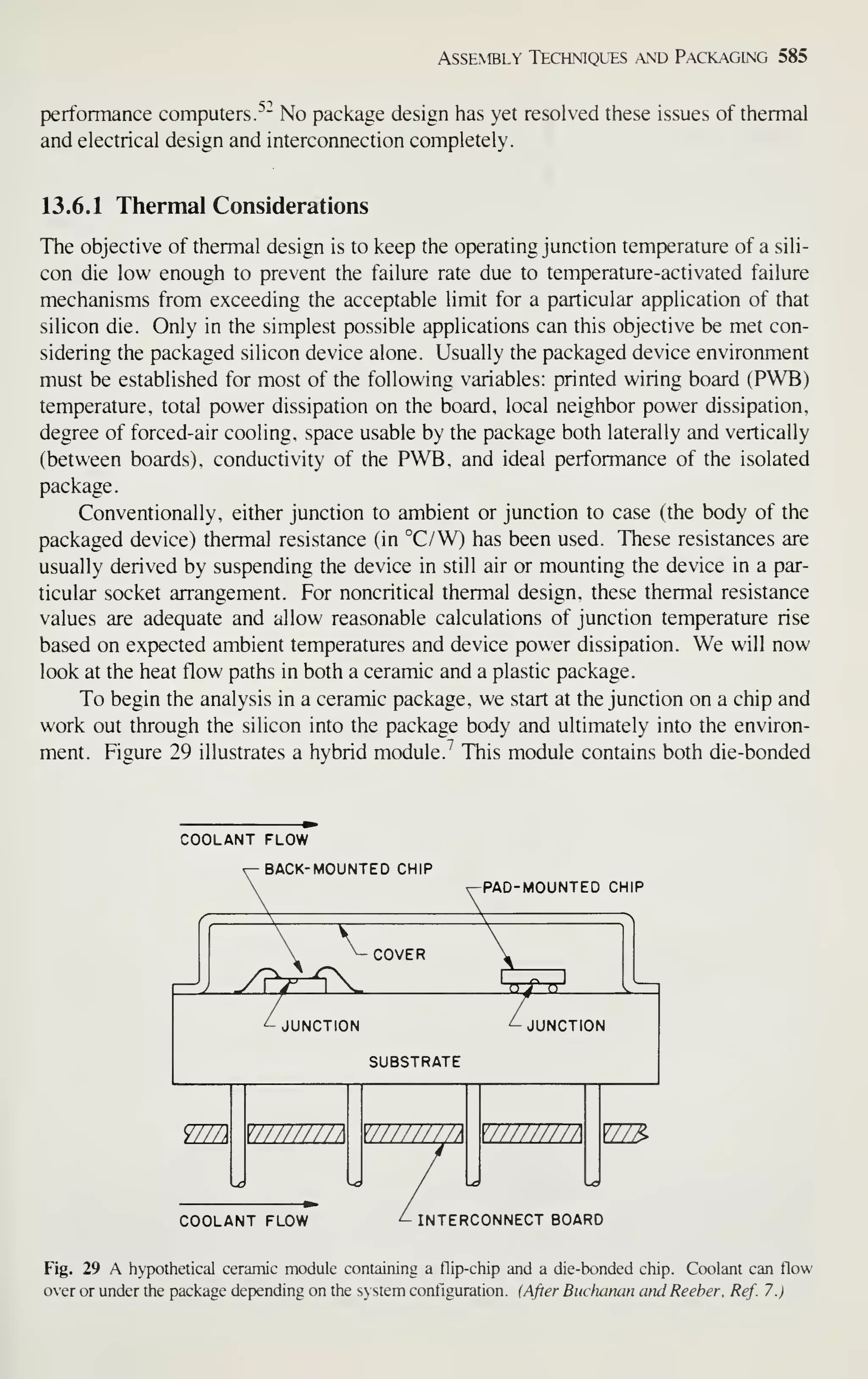

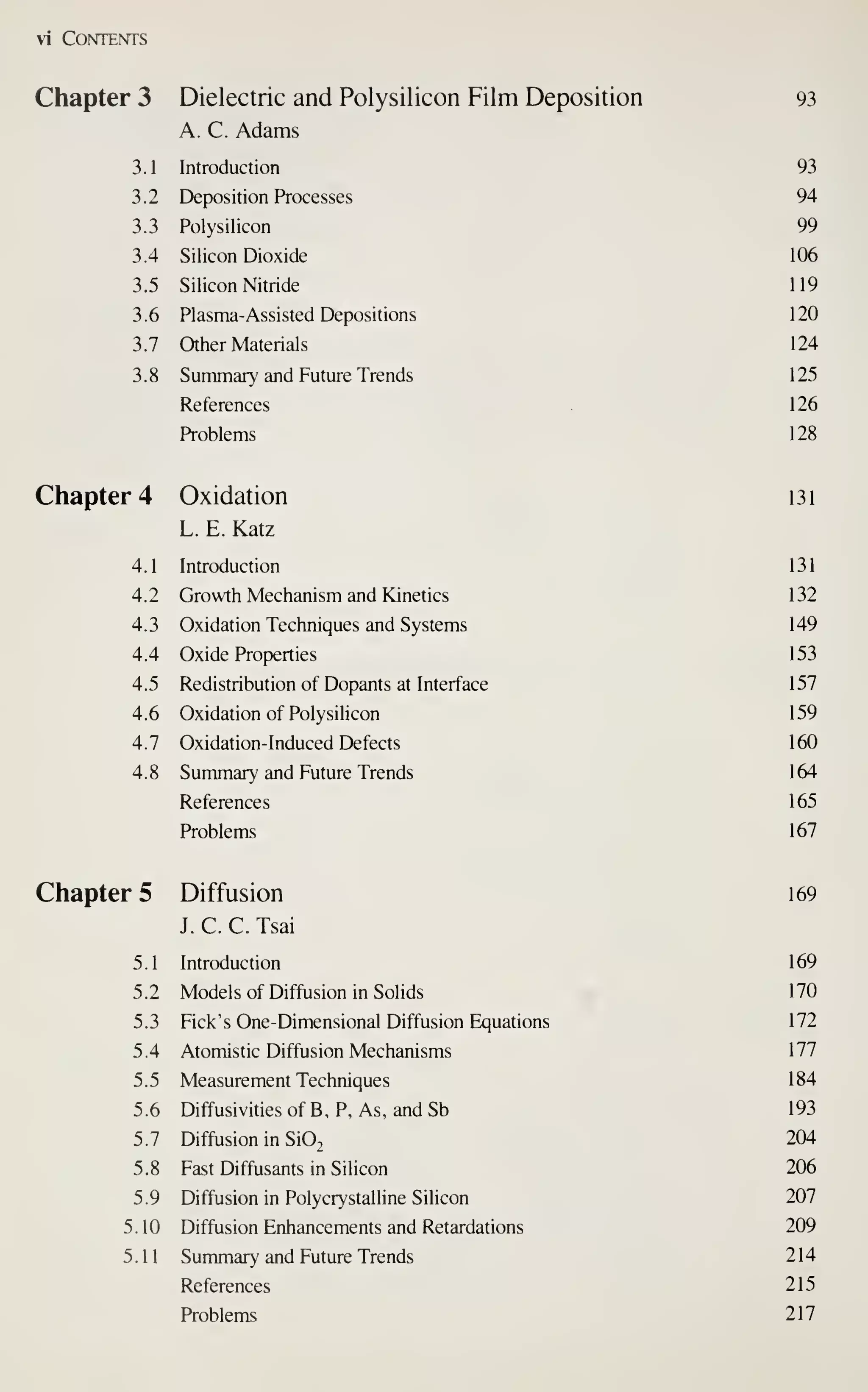

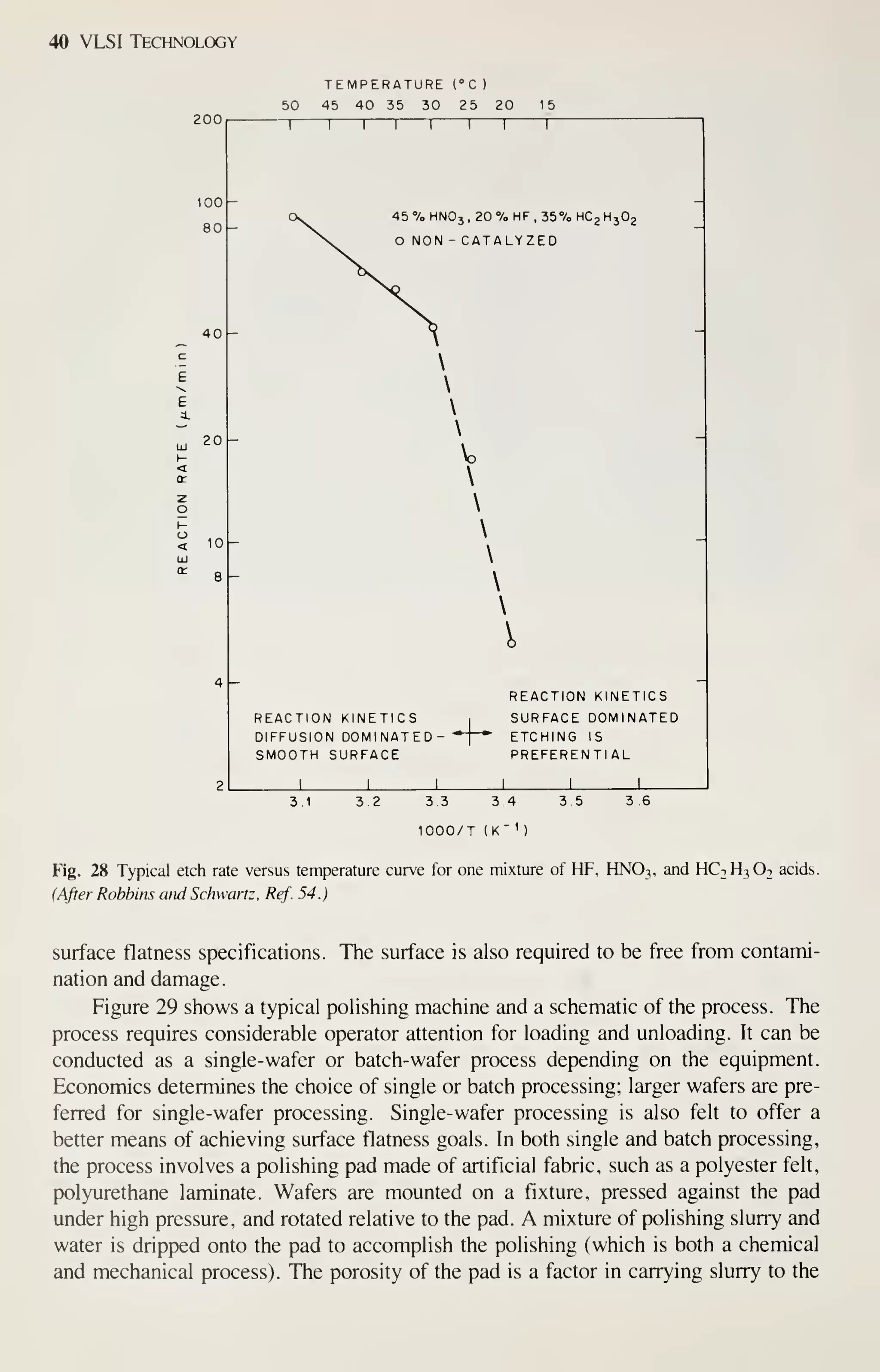

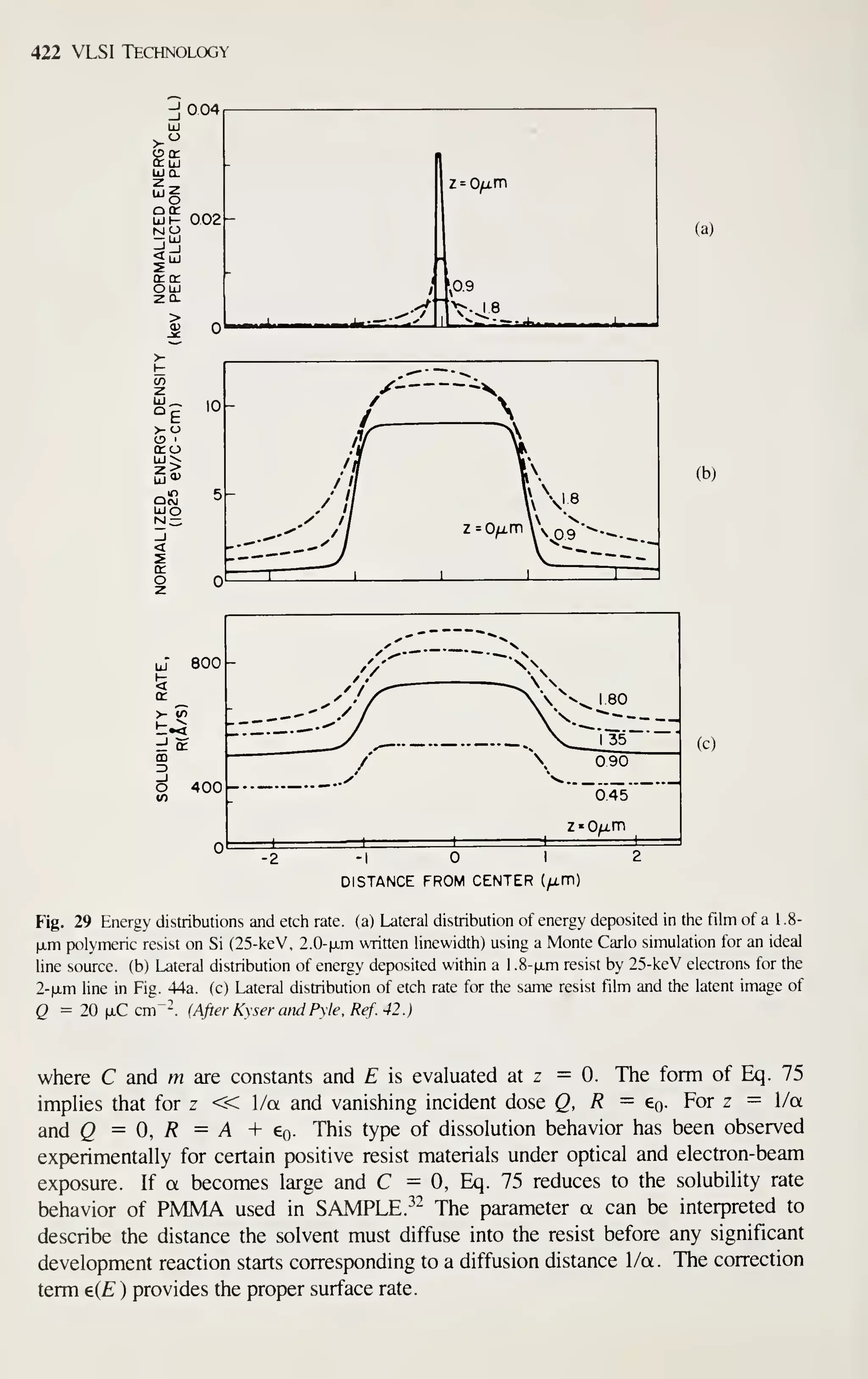

1000 p

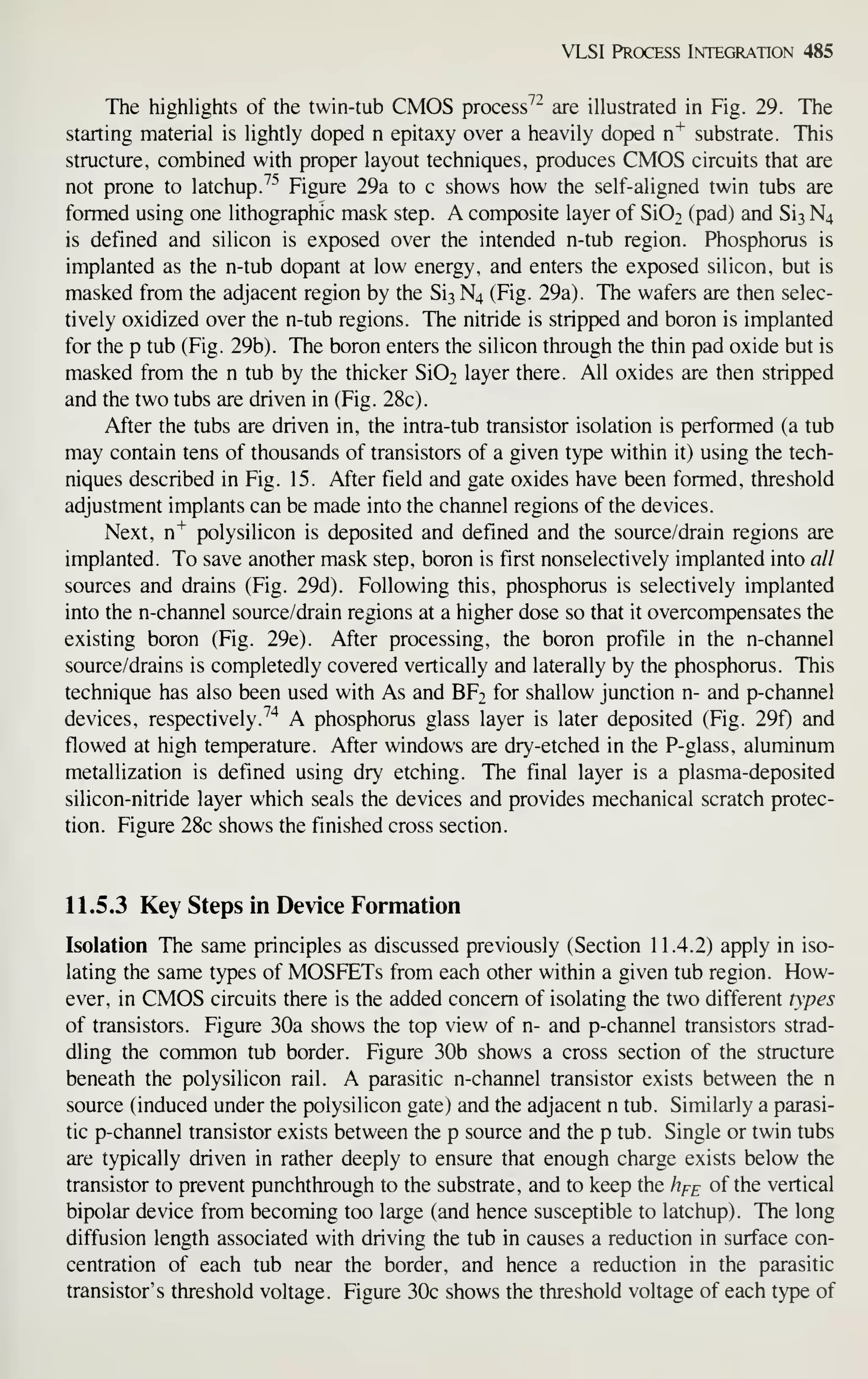

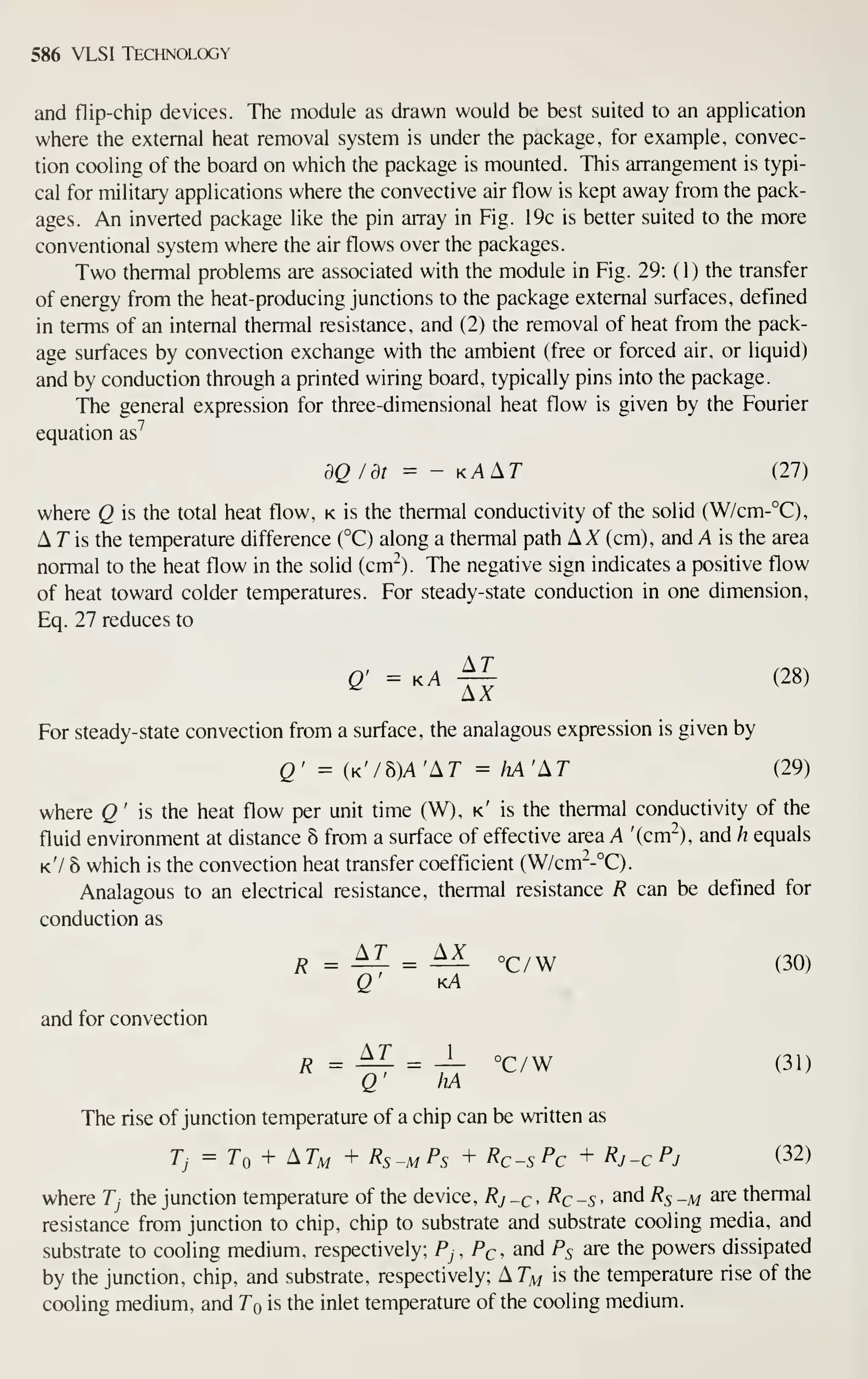

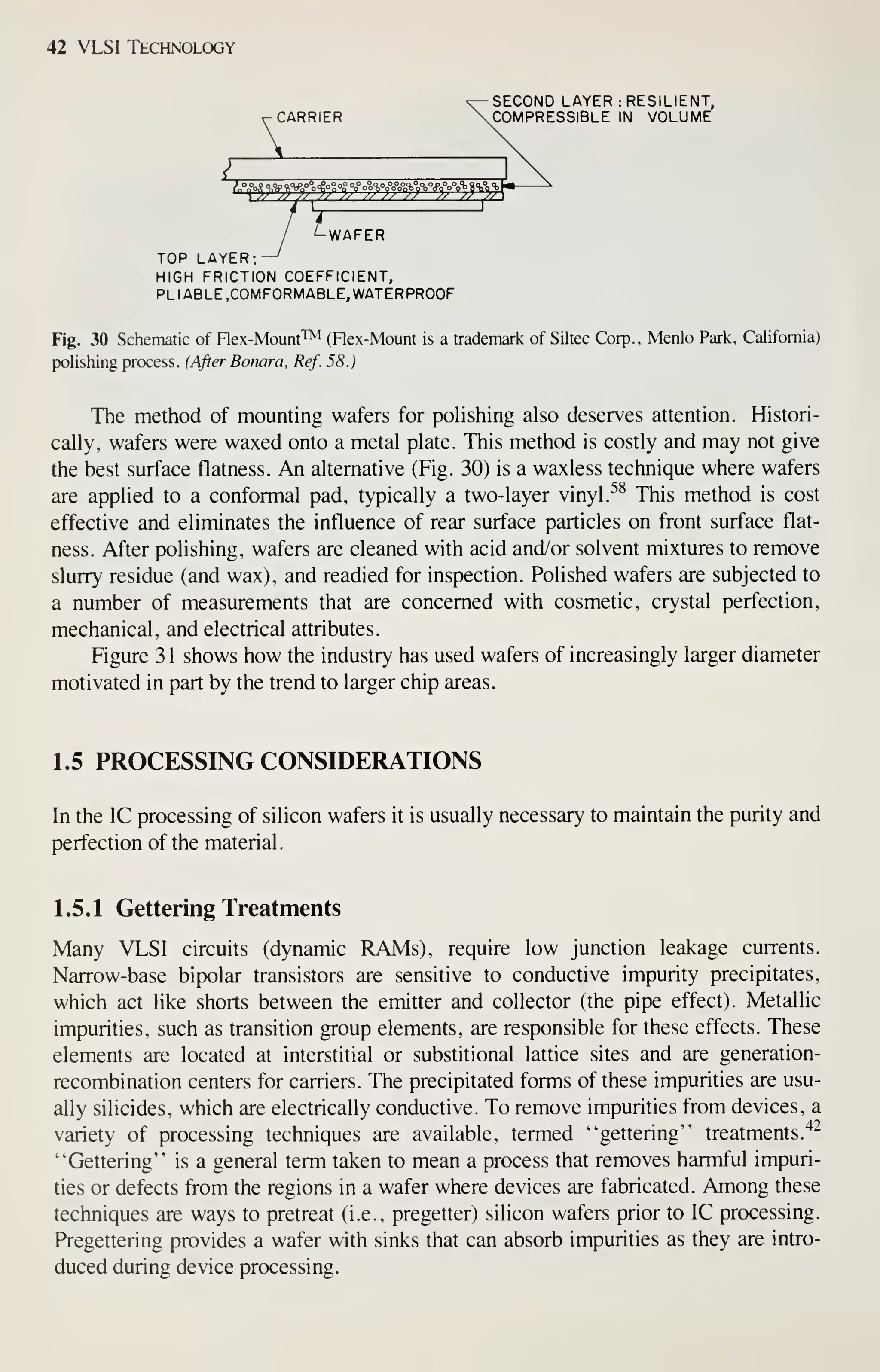

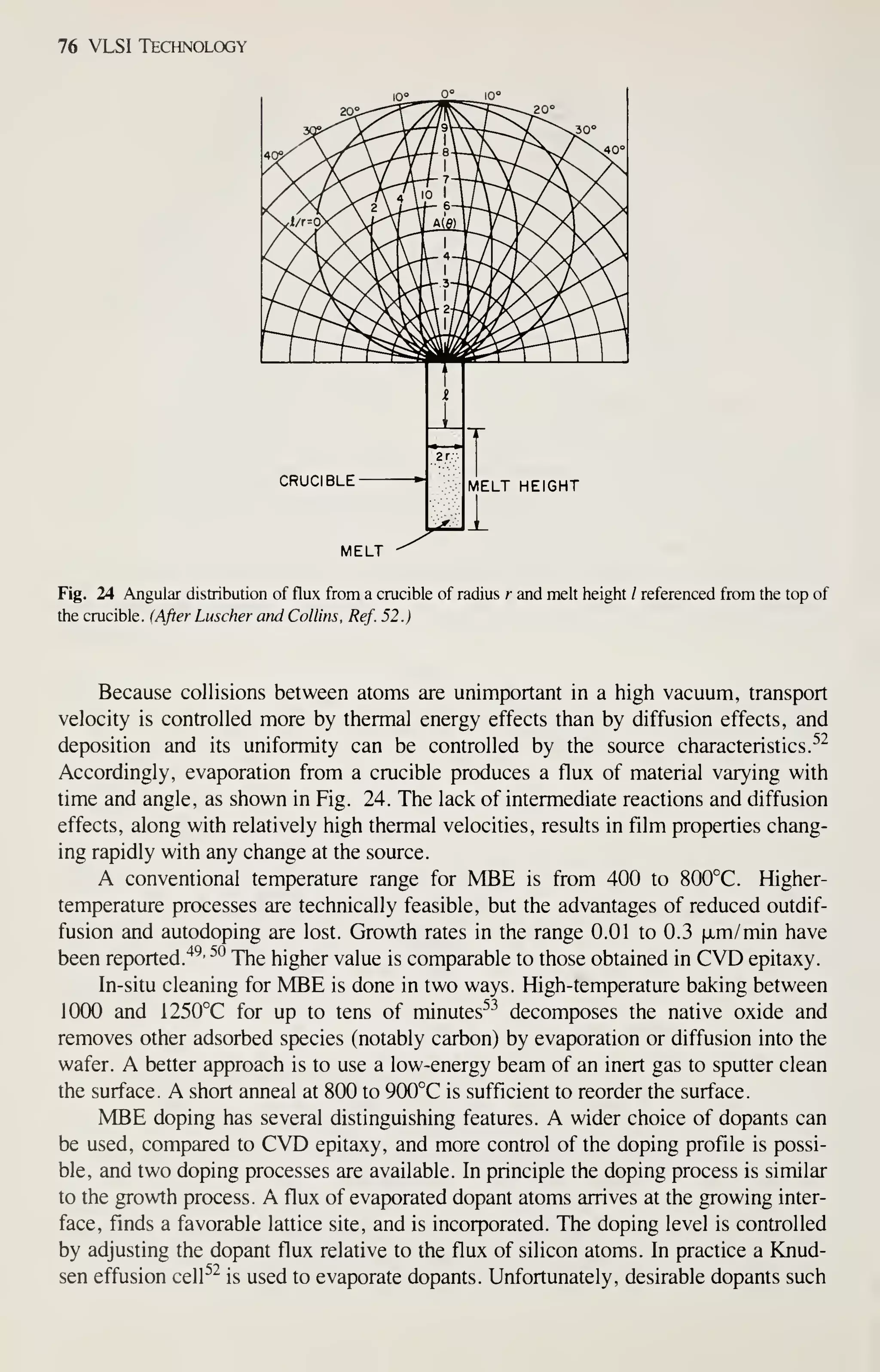

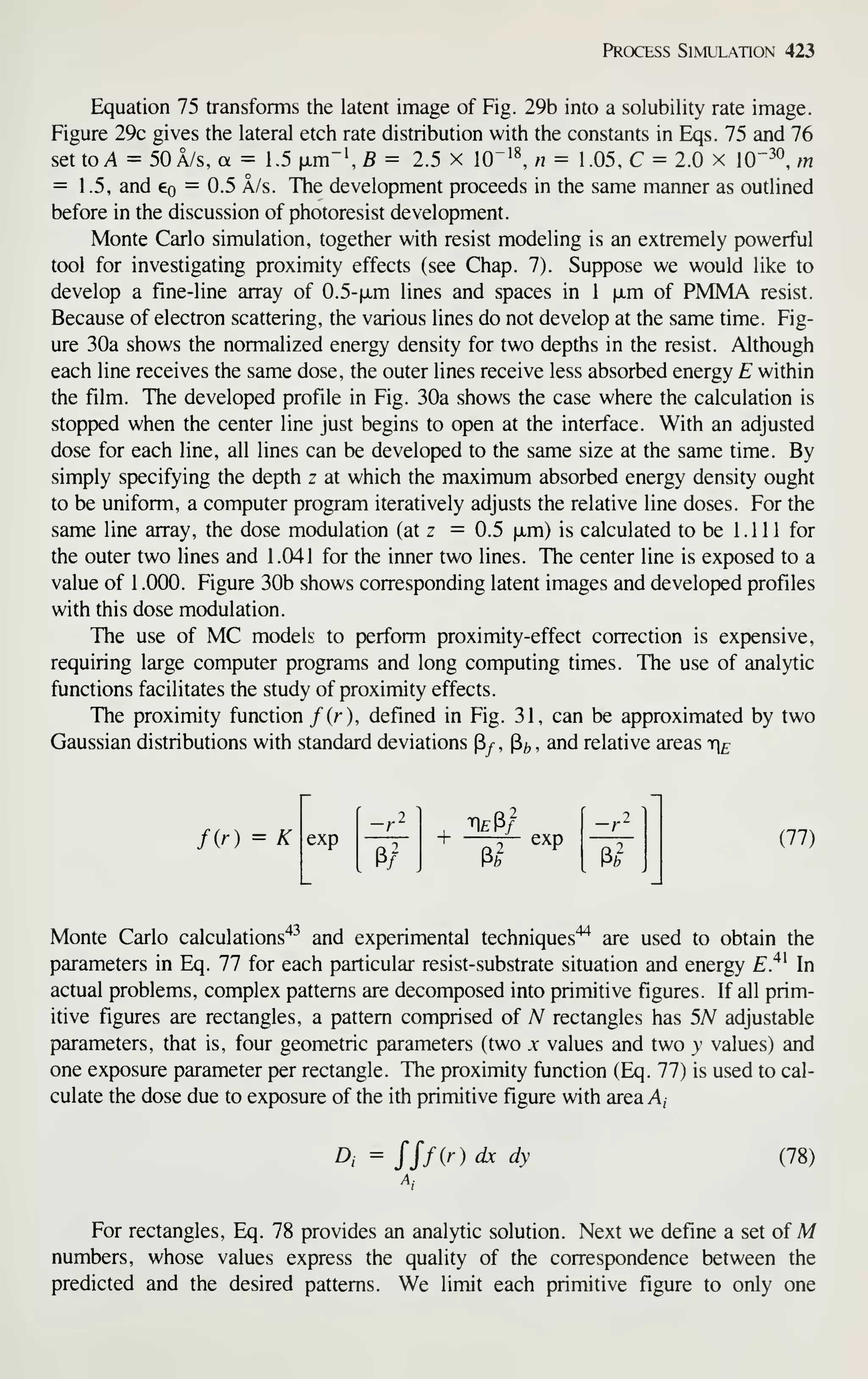

1930 1940 1950 1960 1970

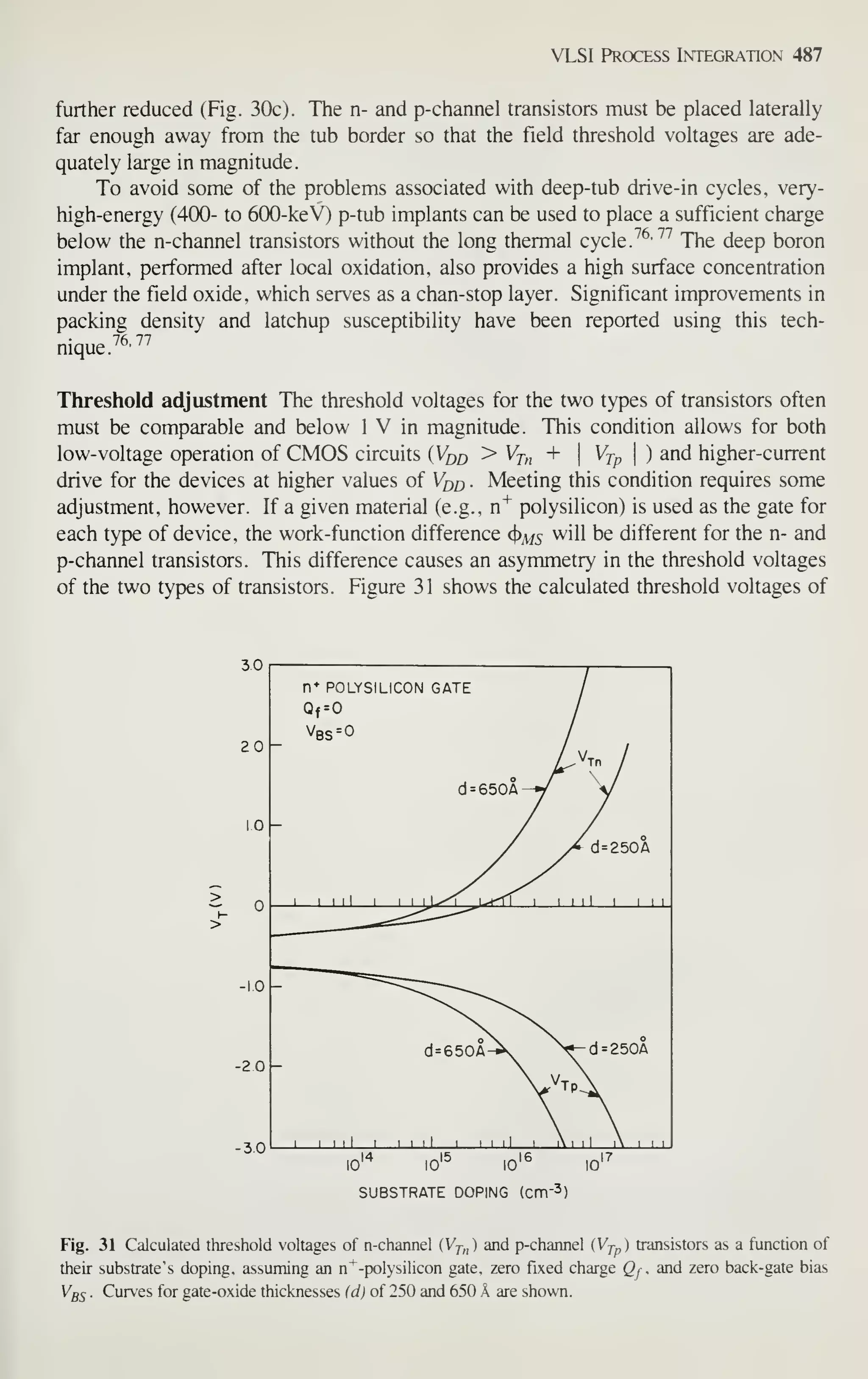

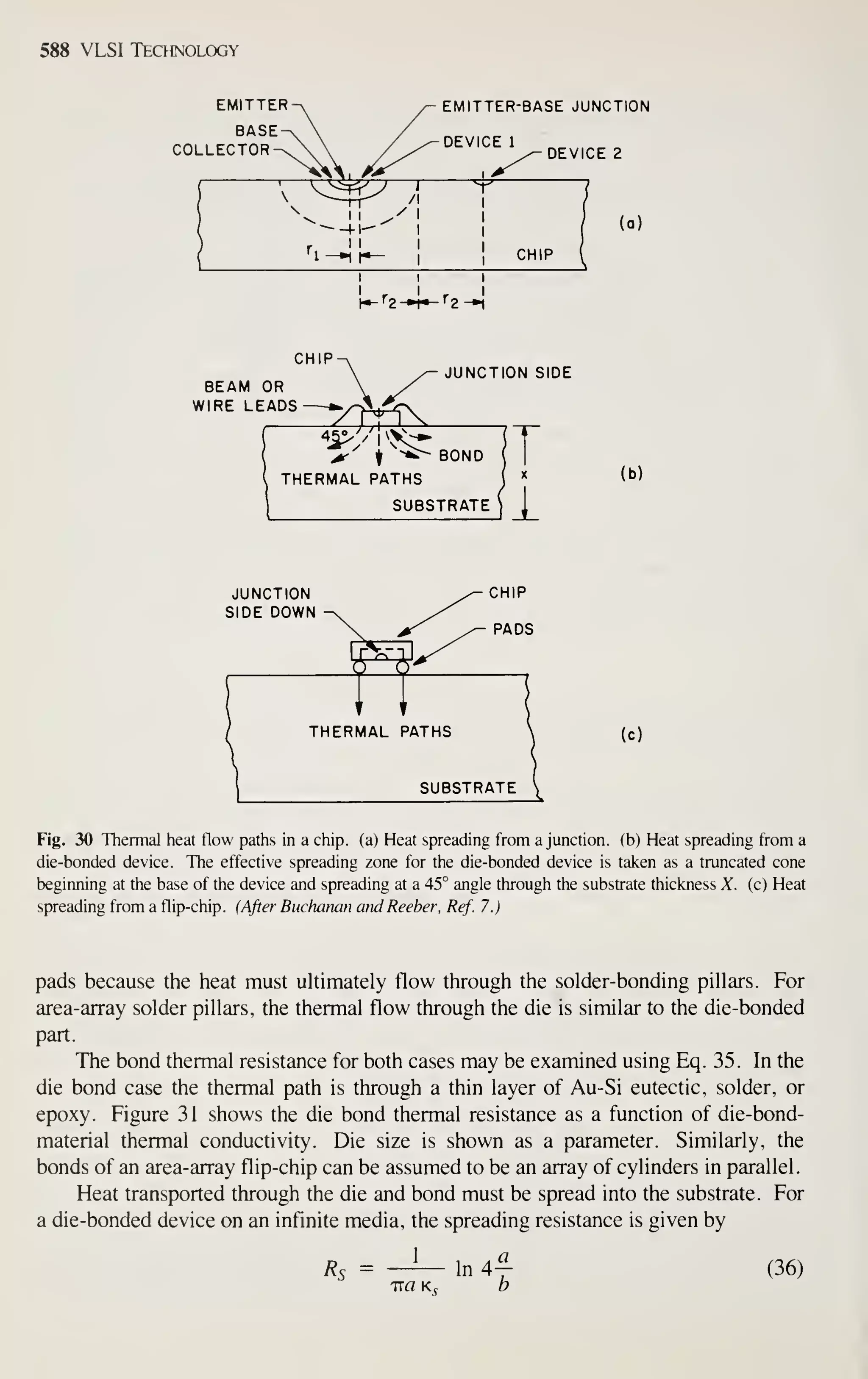

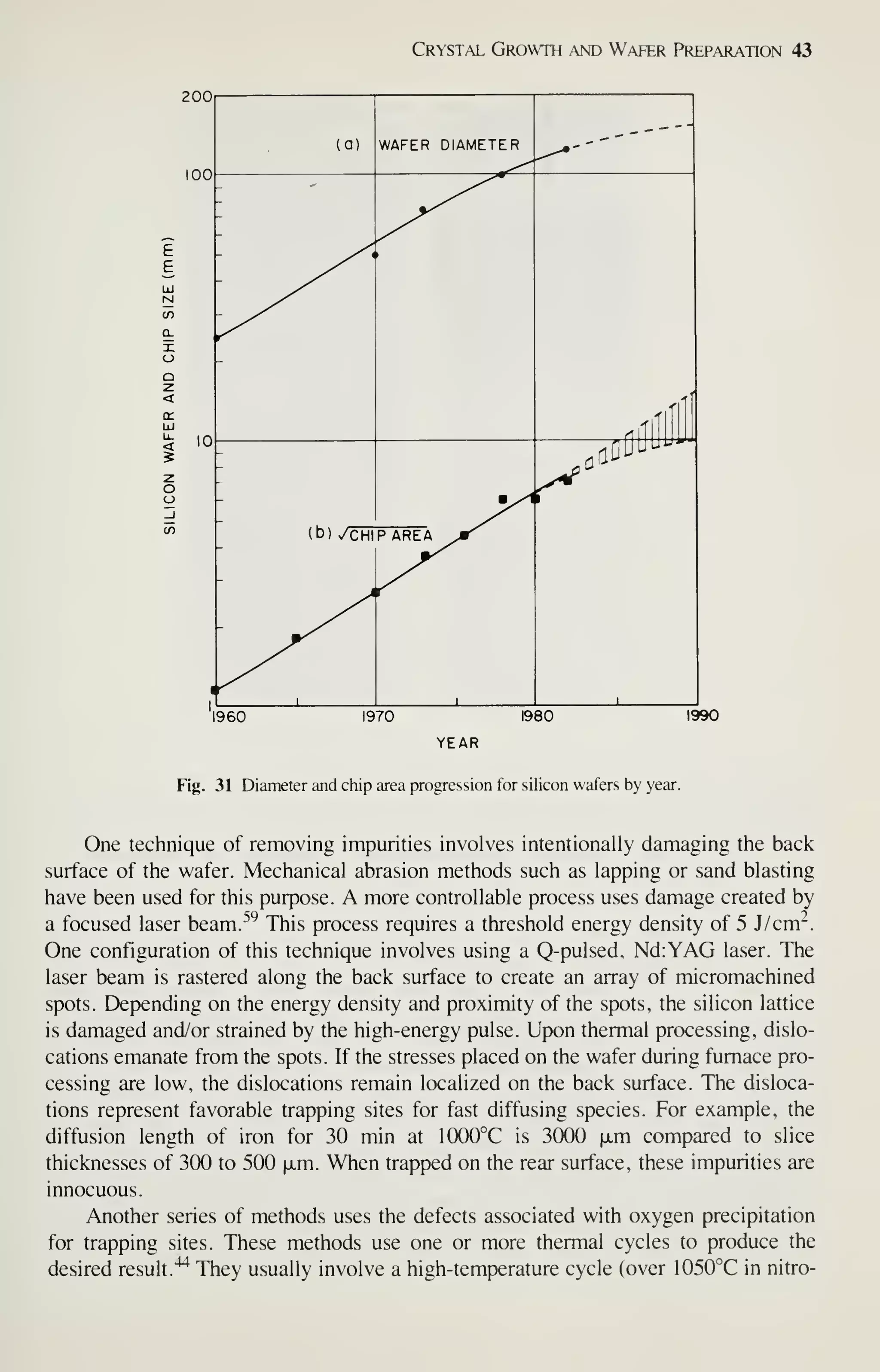

YEAR

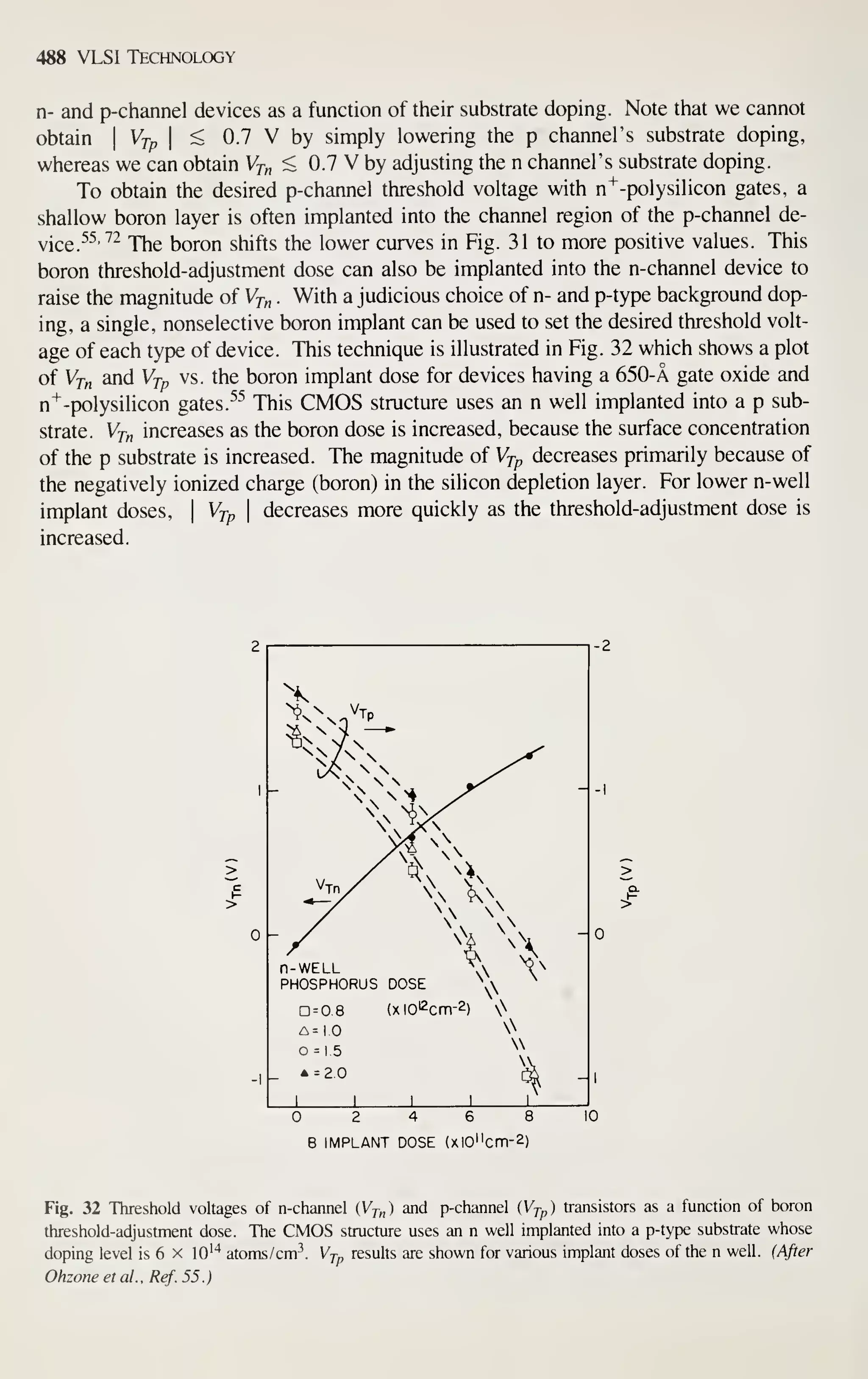

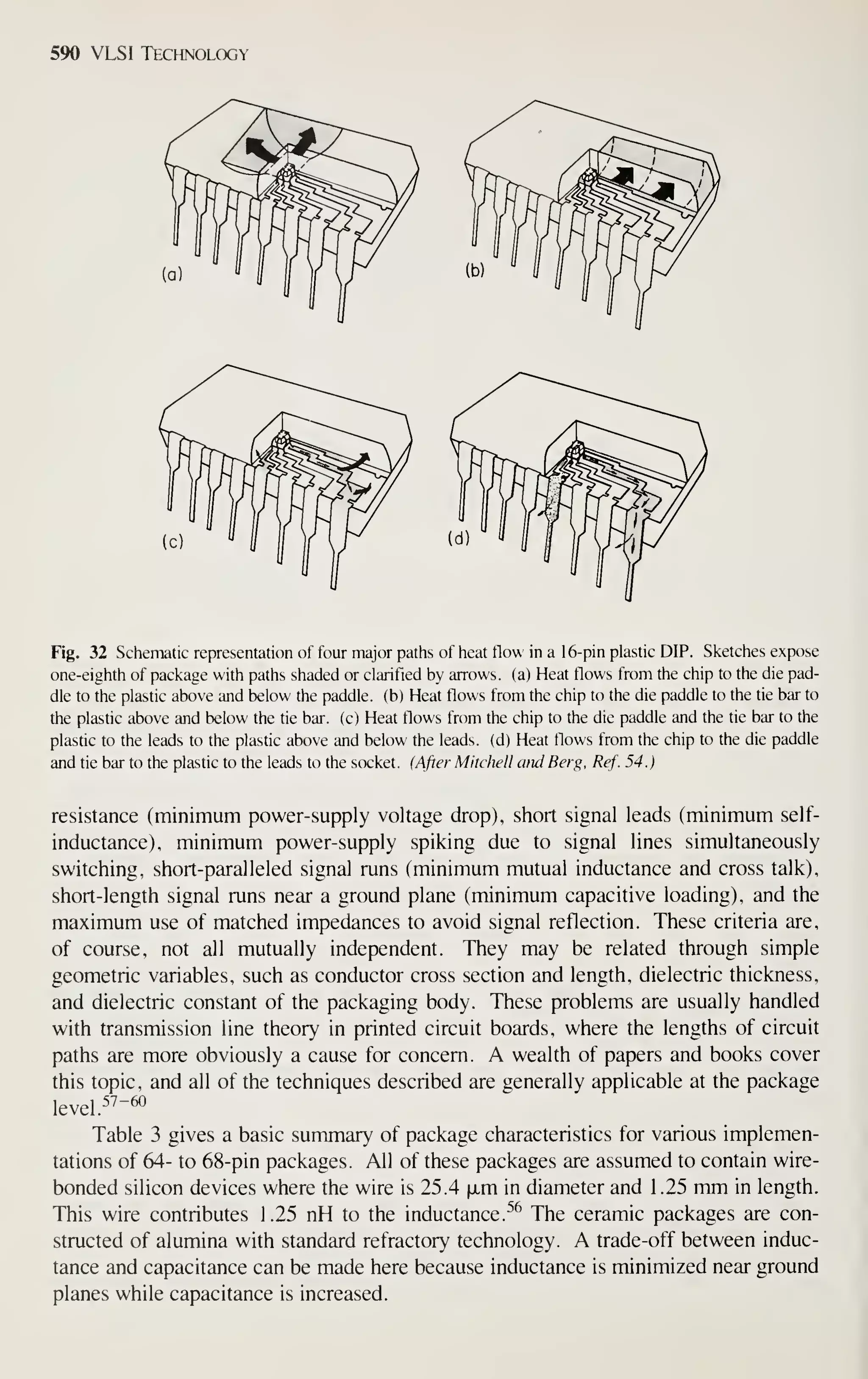

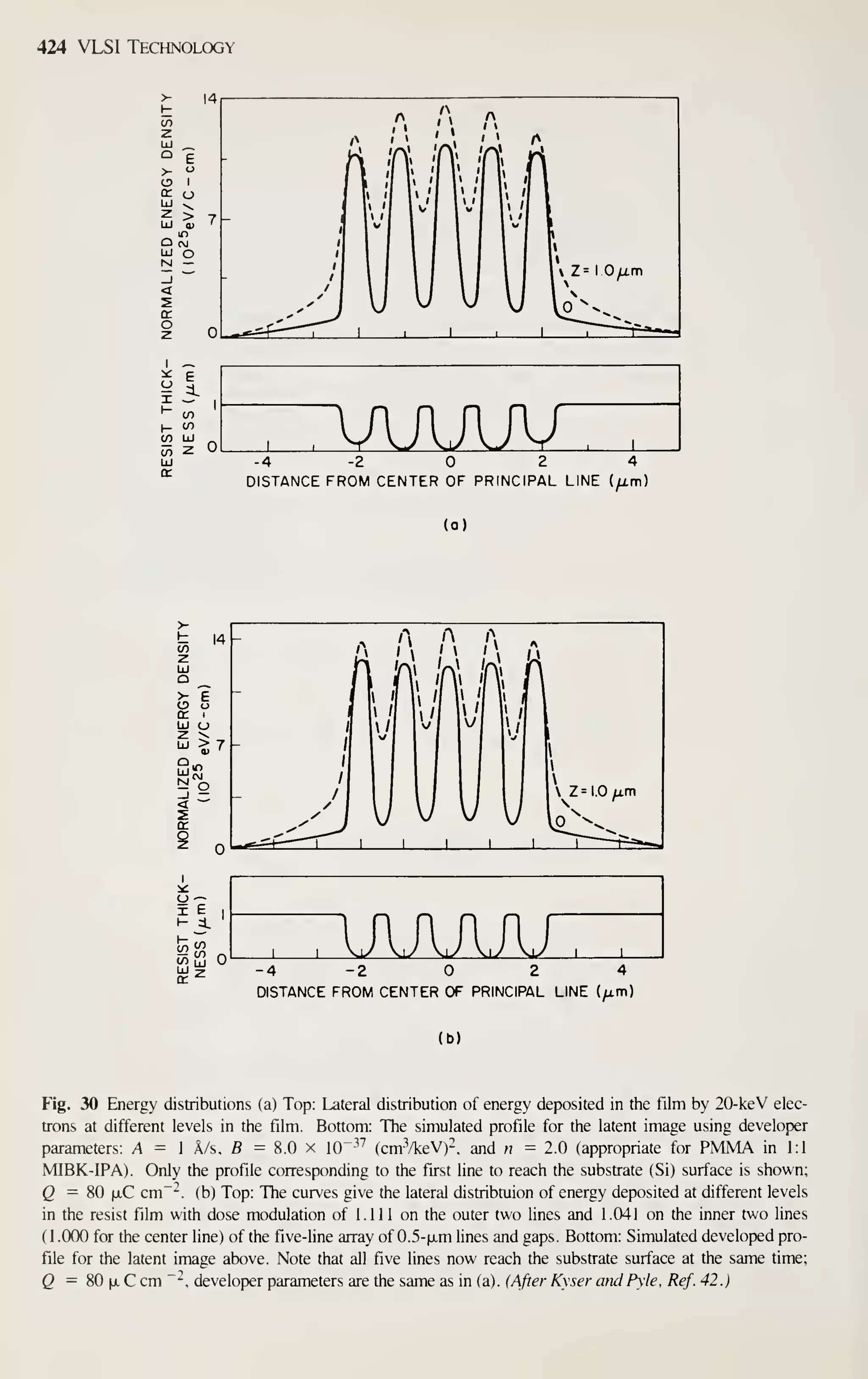

1980 1990

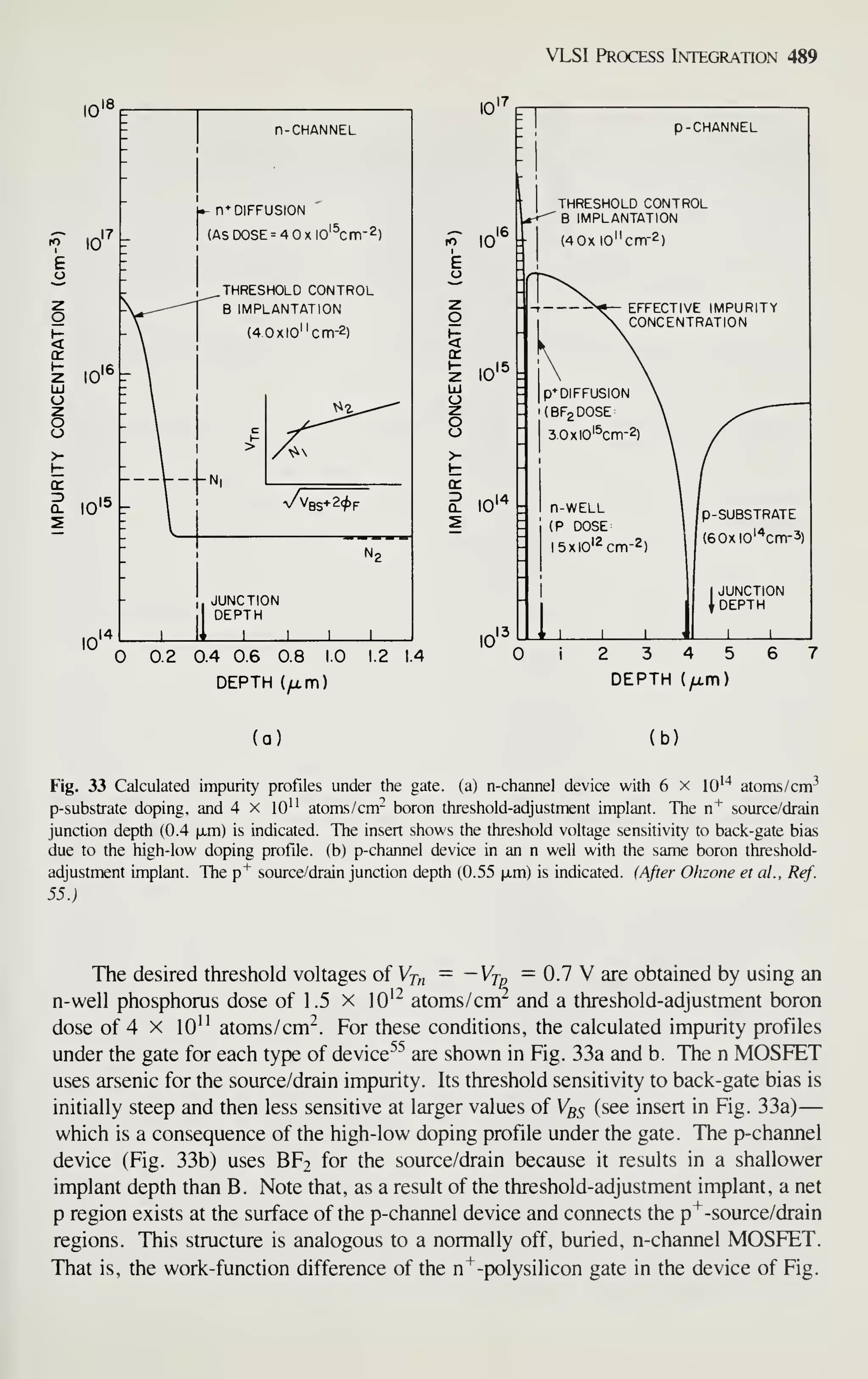

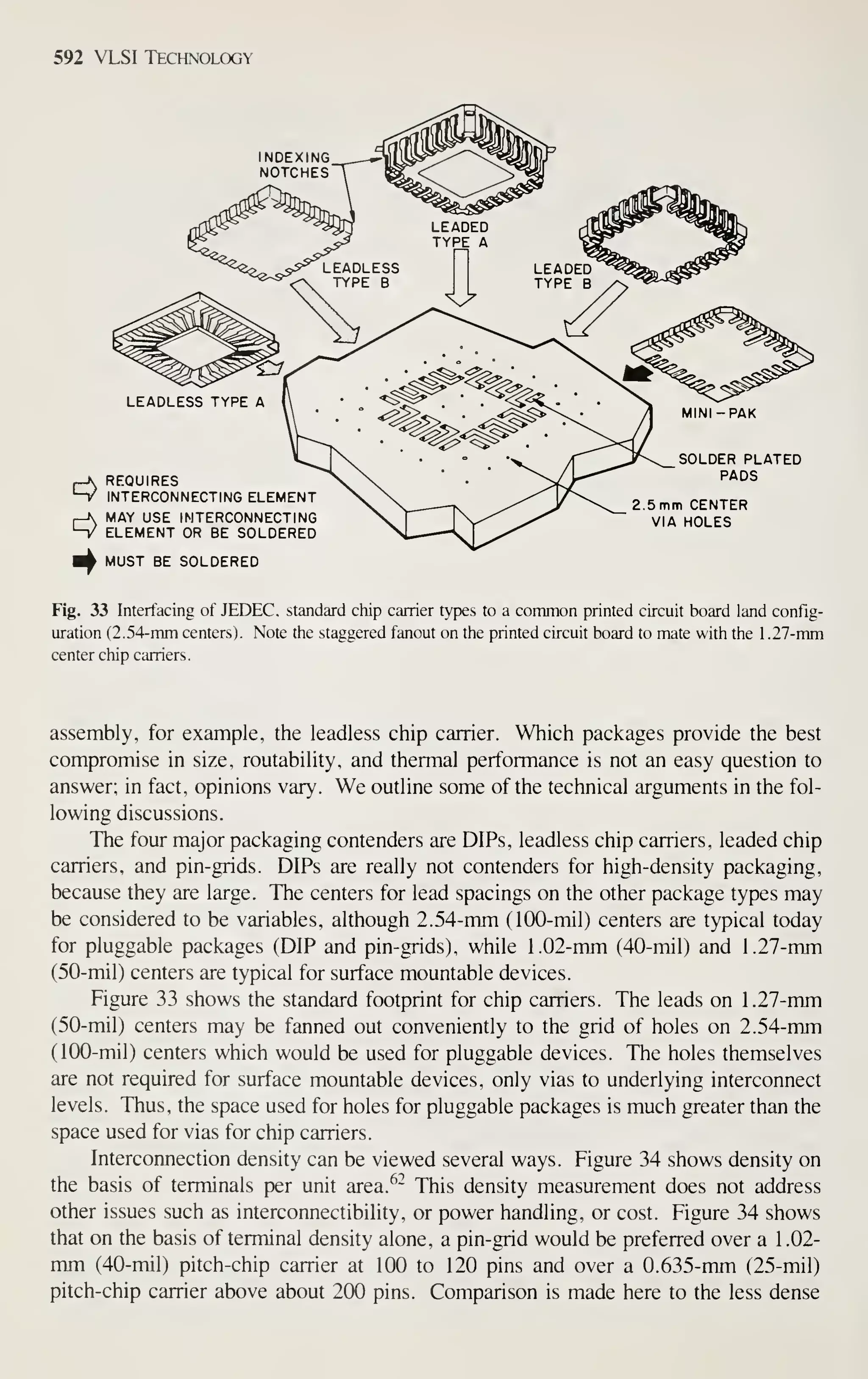

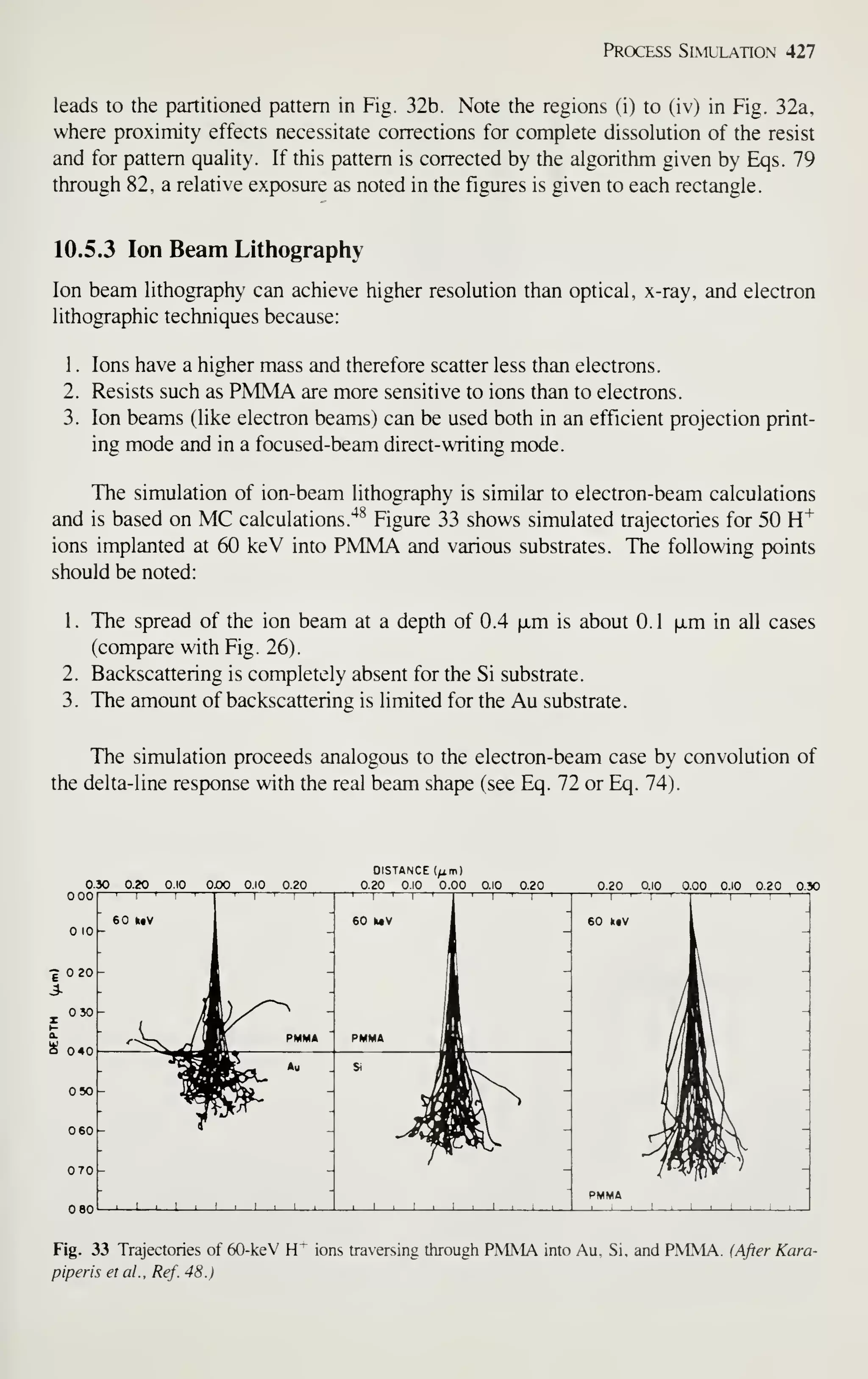

Fig. 1 (a) Factory sales of electronics in the United States for the 52 years between 1930 and 1981 and

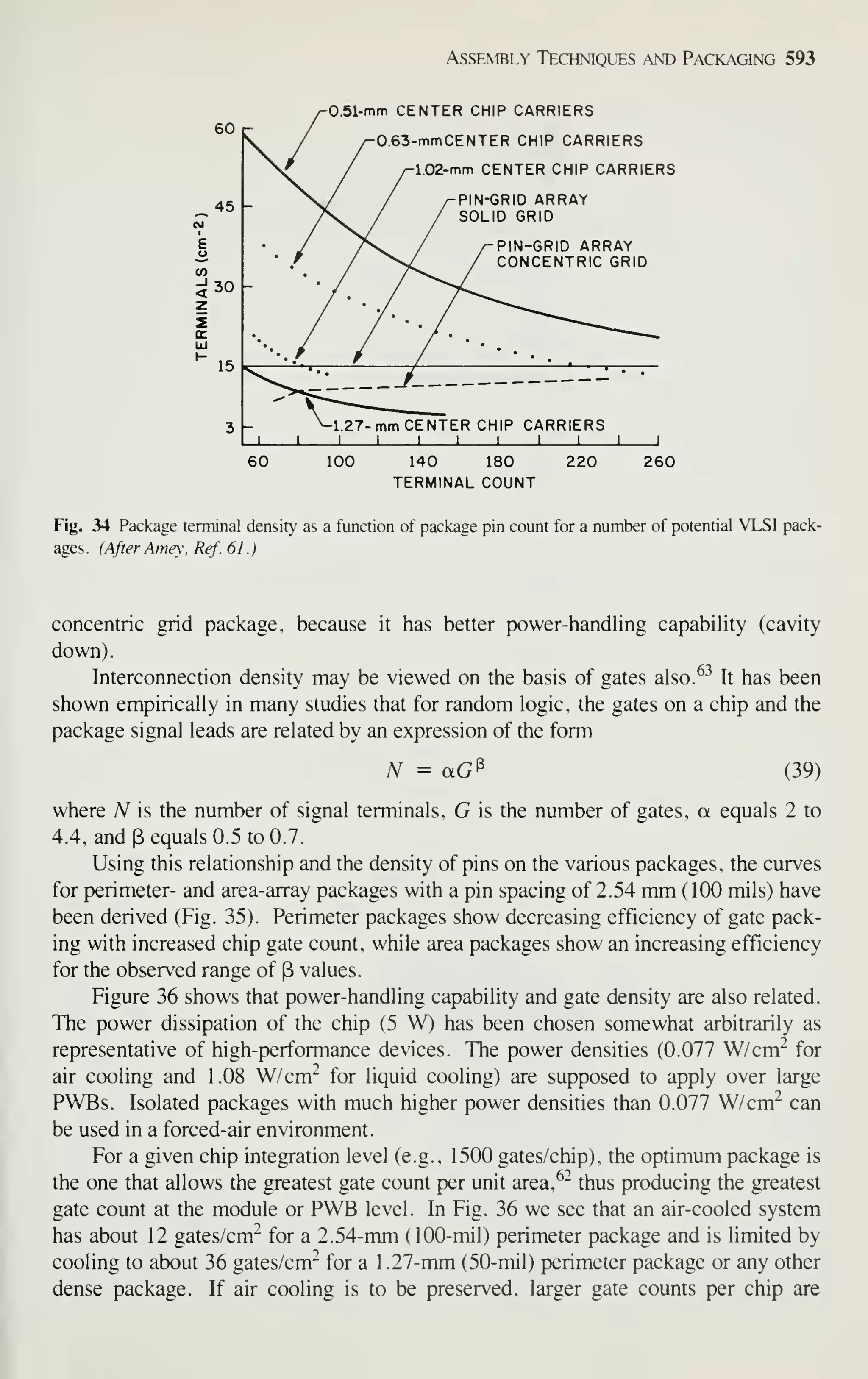

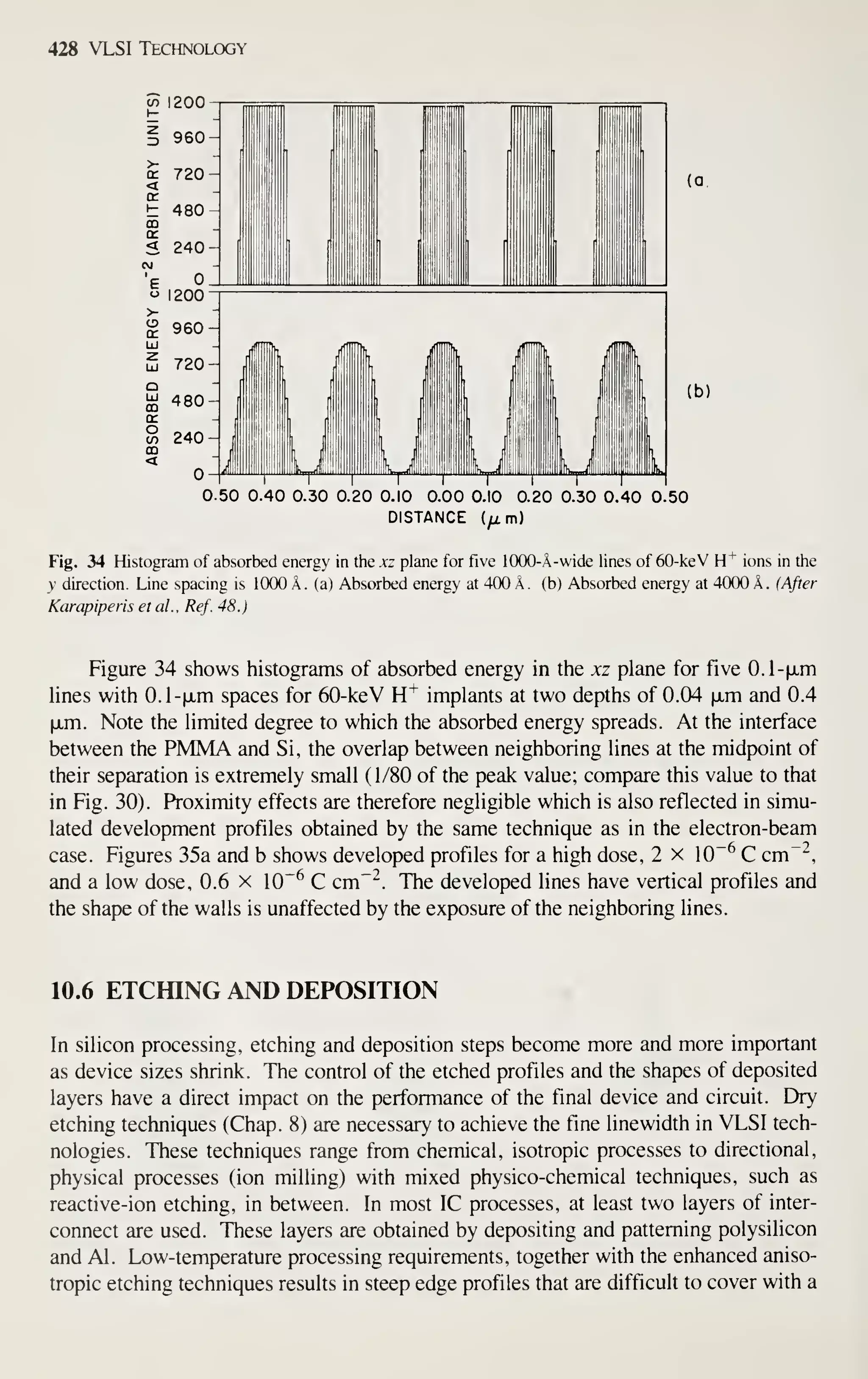

projected to 1990. (b) Integrated circuit market in the United States for the 20 years between 1962 and

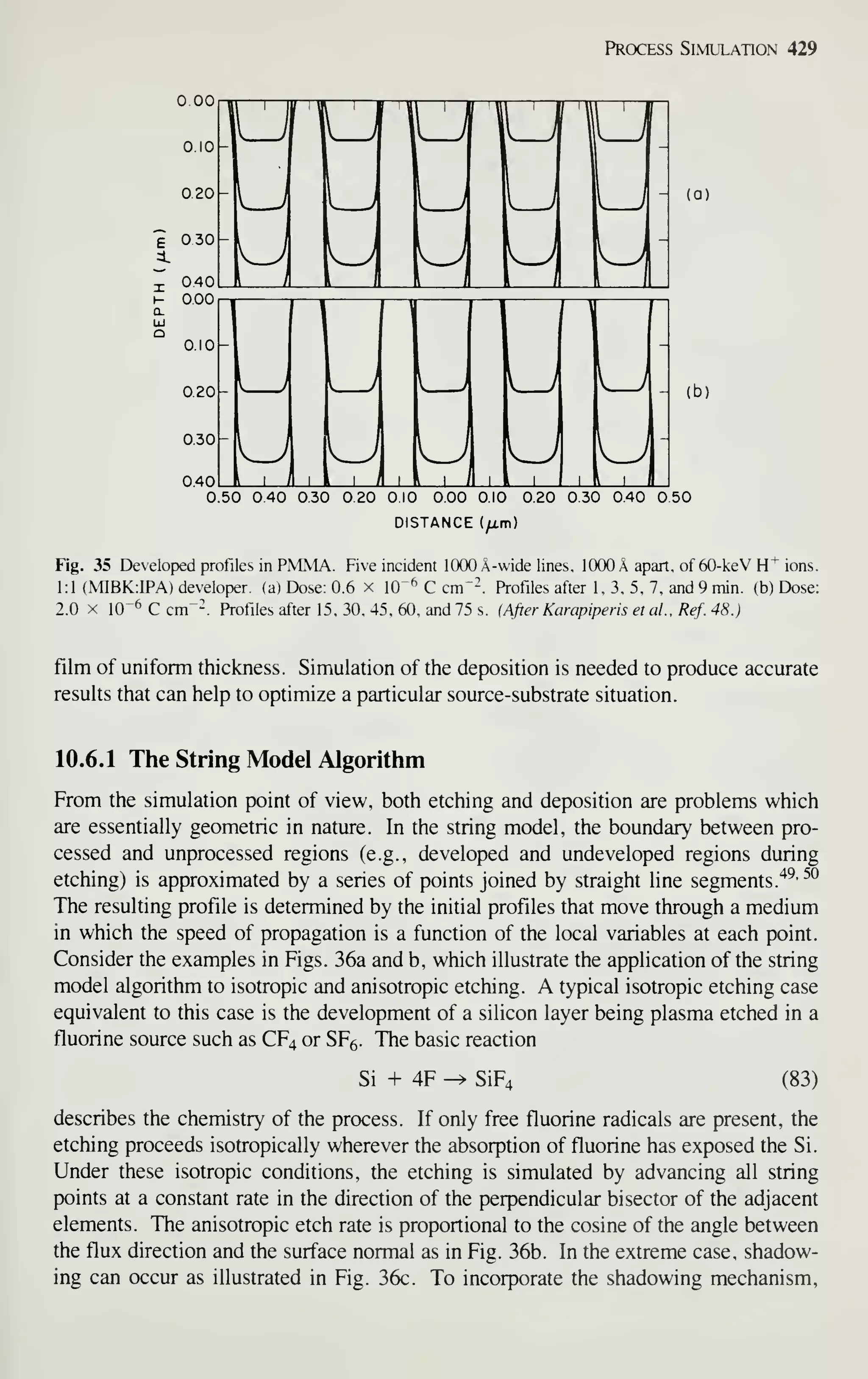

1981 and projected to 1990. (After Refs. 1 and2.)

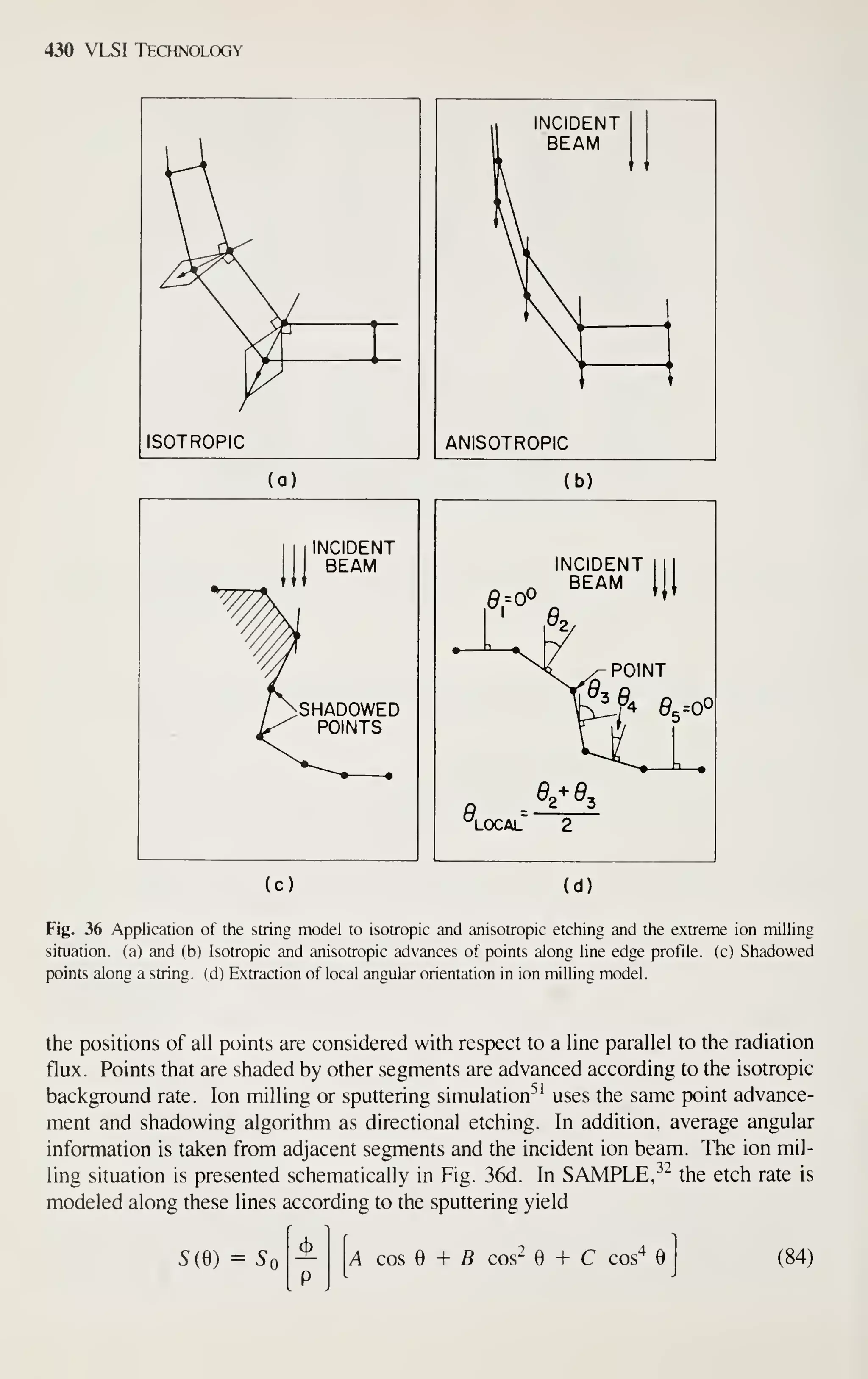

Although the rate of growth has slowed down in recent years because of difficulties in

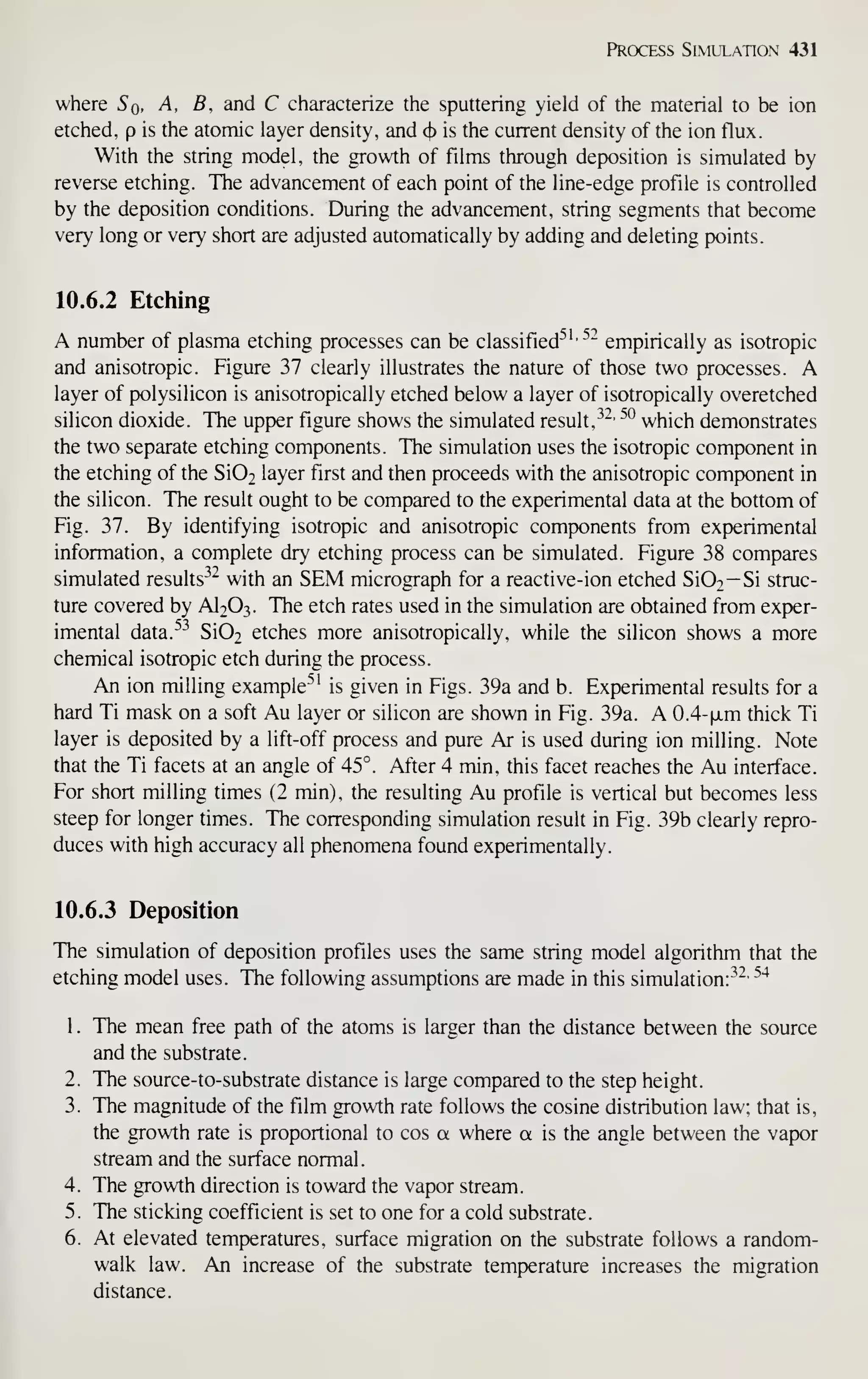

defining, designing, and processing complicated chips, a complexity of over 1 million

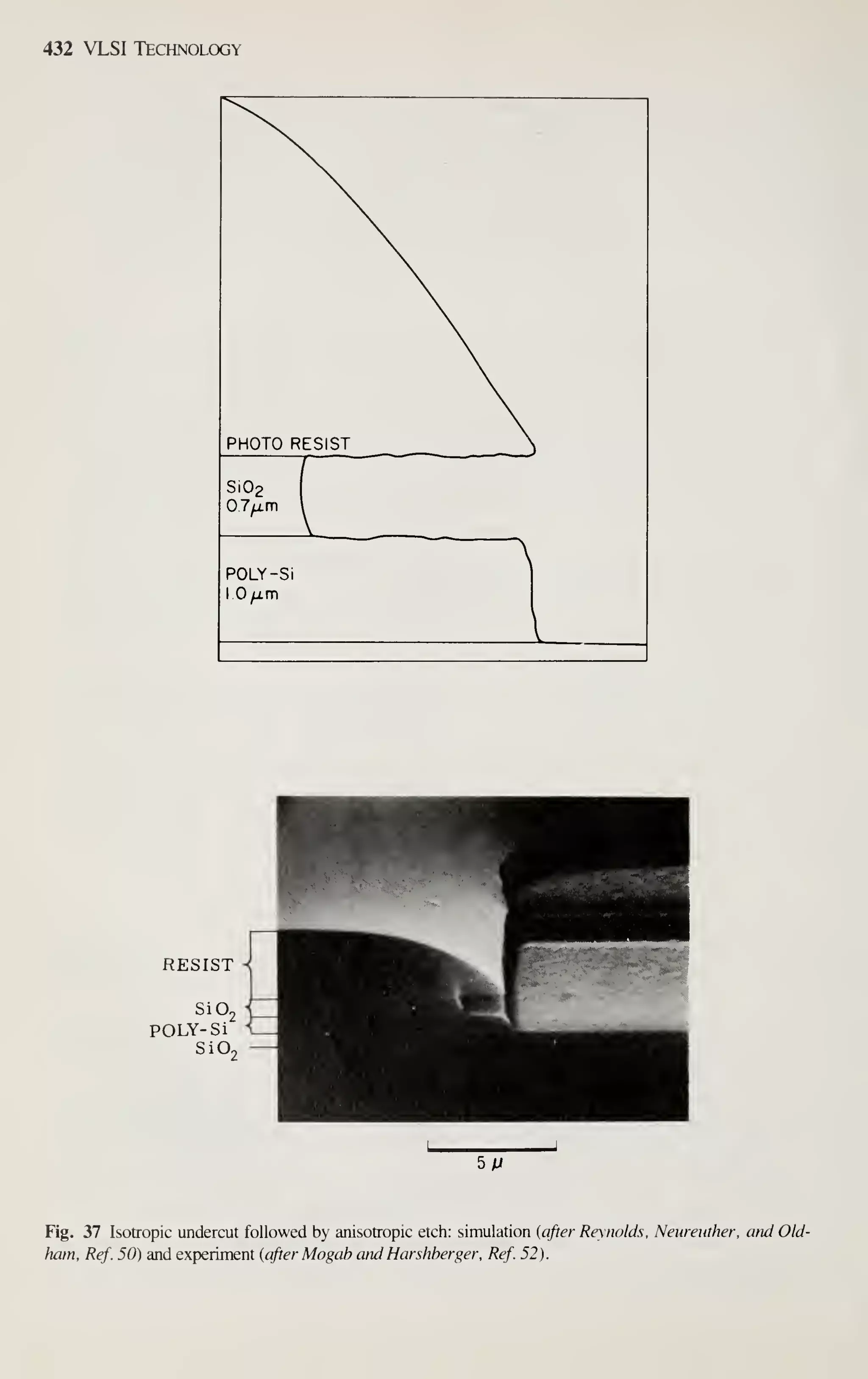

devices per chip will be available before 1990.

The most important factor in achieving such complexity is the continued reduc-

tion of the minimum device dimension [see Fig. 3, curve (b)]. Since 1960, the annual

rate of reduction has been 13%; at that rate, the minimum feature length will shrink

from its present length of 2 |xm to 0.5 fxm in 10 years.

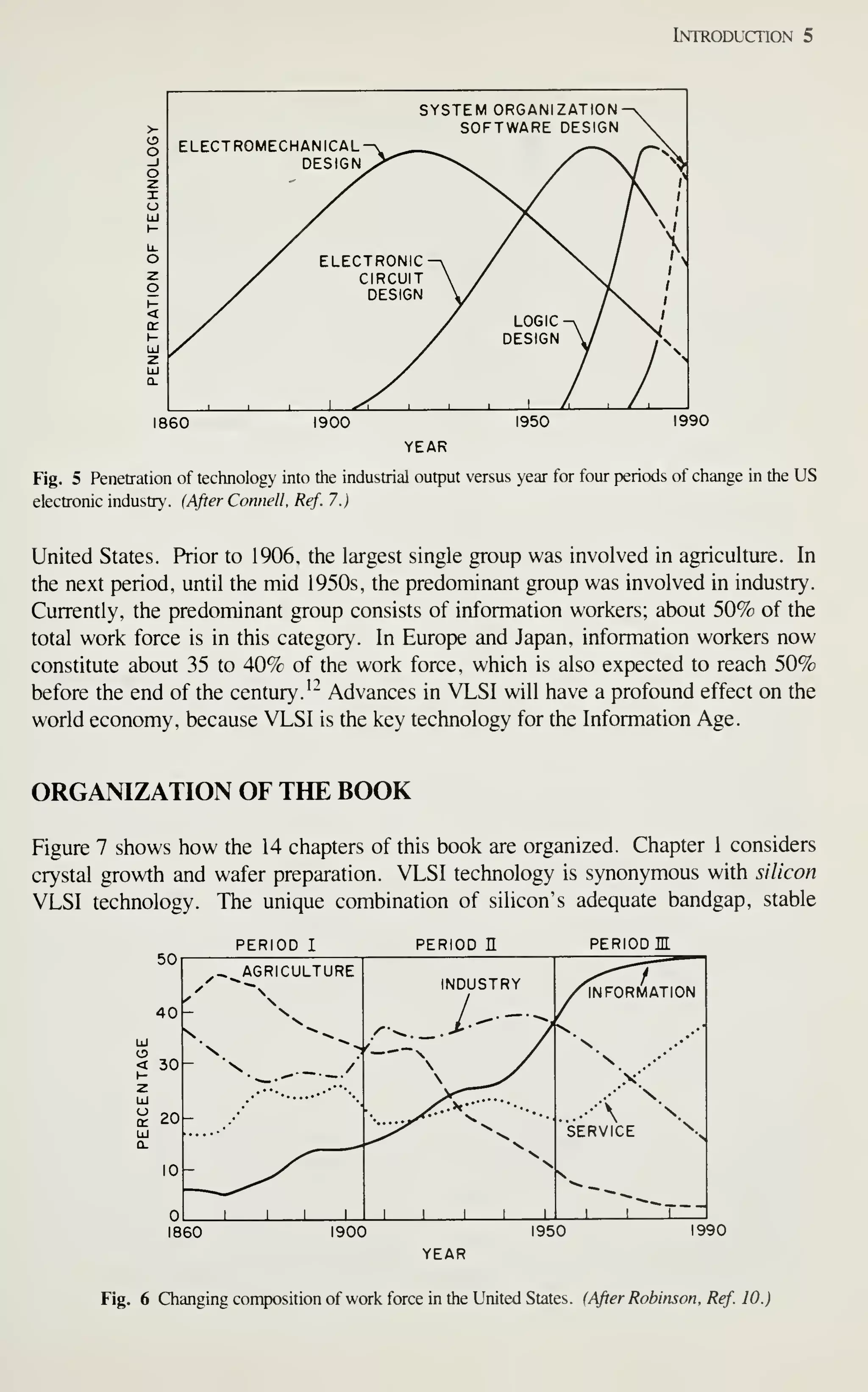

Device miniaturization results in reduced unit cost per function and in improved

performance. Figure 4, curve (a), gives an example of the cost reduction. The cost

per bit of memory chips has halved every 2 years for successive generations of

random-access memories.^ By 1990 the cost per bit is expected to be as low as ~ 1

millicent for a 1 -megabit memory chip. Similar cost reductions are expected for logic

ICs.

As device dimension decreases, the intrinsic switching time in MOSFETs

decreases linearly. (The intrinsic delay is given approximately by the channel length](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-22-2048.jpg)

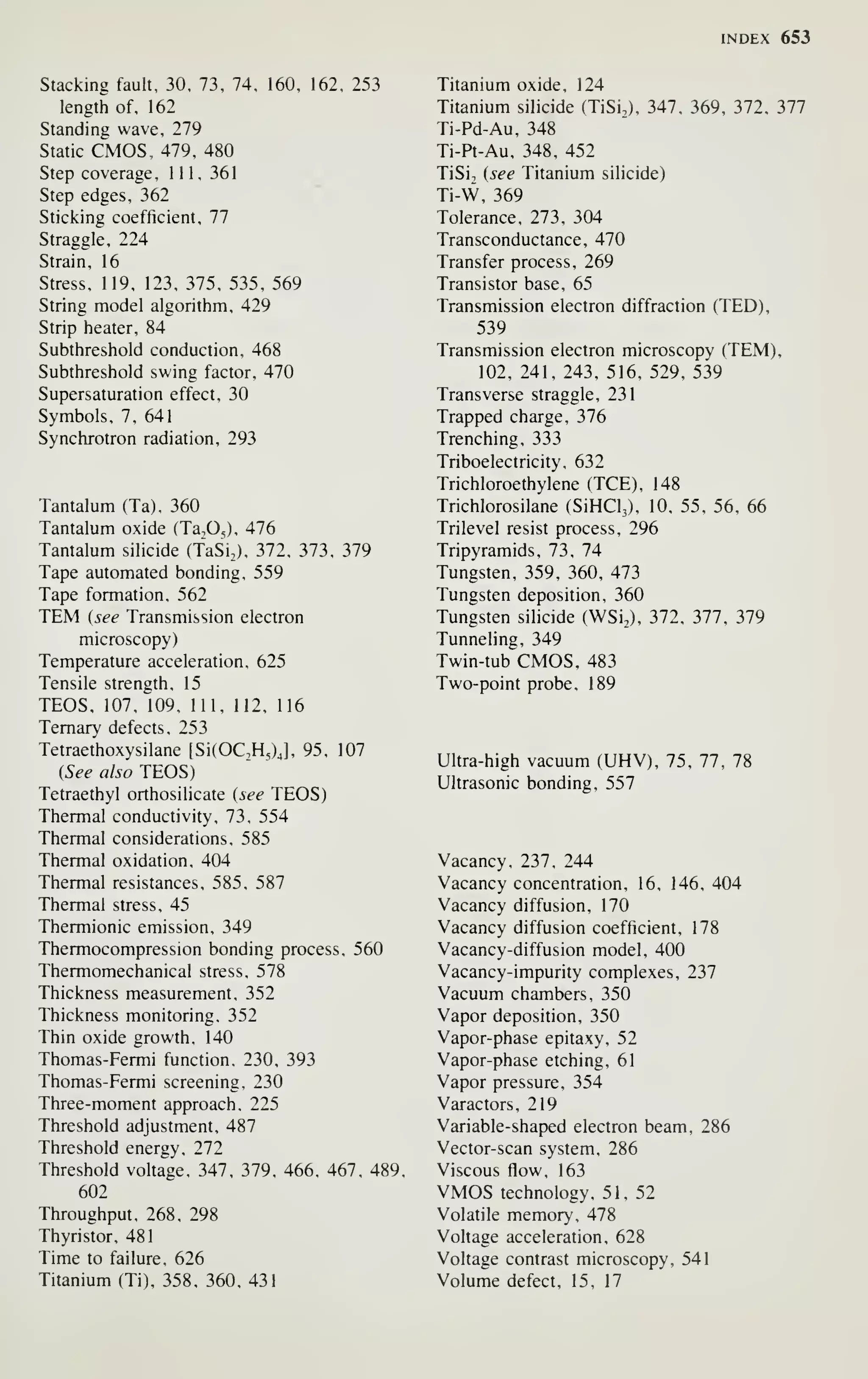

![Introduction 7

After completely processed wafers are tested, those chips that pass the tests are

ready to be packaged. Chapter 13 describes the assembly and packaging of VLSI

chips. Chapter 14 describes the yield at every step of the processing and the reliabil-

ity of the packaged ICs. As device dimensions approach 1 ixm, VLSI processing

becomes more automated, resulting in tighter control of all processing parameters. At

every step of production, from crystal growth to device packaging, numerous refine-

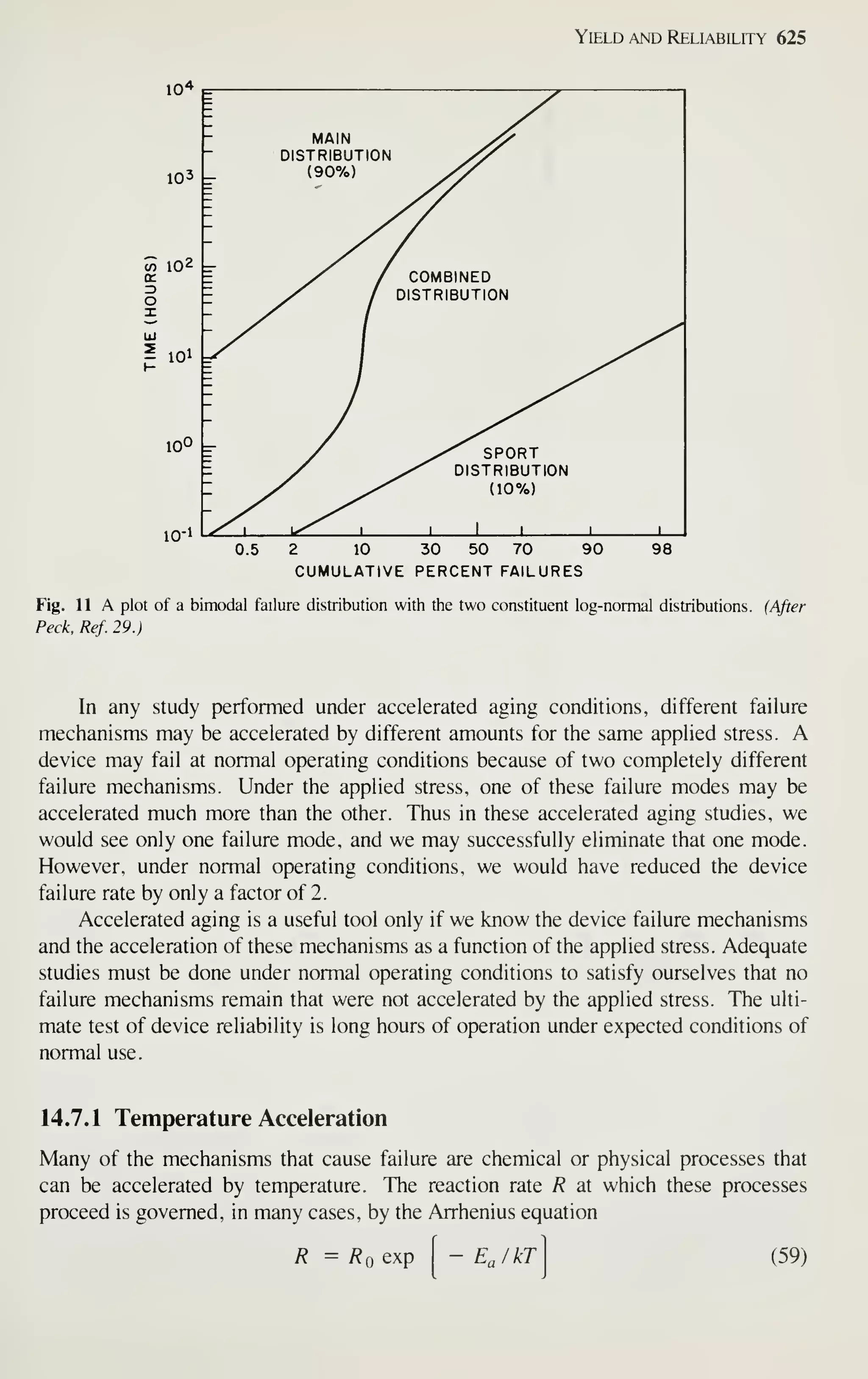

ments are being made to improve the yield and reliability.

To keep the notation simple in this book, we sometimes found it necessary to use

a simple symbol more than once, with different meanings. For example, in Chapter 1

S means 4-point probe spacing, in Chapter 7 it means resist sensitivity, while in

Chapter 14 it means slope of a failure plot. Within each chapter, however, a symbol

has only one meaning and is defined the first time it appears. Many symbols do have

the same or similar meanings consistently throughout this book; they are summarized

in Appendix B.

At present, VLSI technology is moving at a rapid pace. The number of VLSI

publications (i.e., papers with the acronym "VLSI" in the title or abstract) has grown

from virtually zero in 1975 to over 1000 in 1981 with an average annual growth rate

of over 300%! Note that many topics, such as lithography and process simulation, are

still under intensive study. Their ultimate capabilities are still not fully understood.

The material presented in this book is intended to serve as a foundation. The refer-

ences listed at the end of each chapter can supply more information.

REFERENCES

[1] Electronic Market Data Book 1982, Electronic Industries Association, Washington. D.C., 1982.

[2] "World Markets Forecast for 1982," Electronics, 55, No. 1, 121 (1982).

[3] "Ten-Year Worldwide Forecast for Electronic Equipment and Components," Electronic Business,

p. 92 (February 1981).

[4] G. Moore, "VLSI. What Does the Future Hold," Electron. Aust.,4,2, 14 (1980).

[5] R. N. Noyce, "Microelectronics," in T. Forester, Ed., The Microelectronics Revolution, MIT Press,

Cambridge, Mass., 1981, p. 29.

[6] R. W. Keyes. "Limitations of Small Devices and Large Systems," in N. G. Einspruch, Ed., VLSI

Electronics, Academic, New York, 1981, Vol. 1, p. 186.

[7] J. M. Connell, "Forecasting a New Generation of Electronic Components," Digest IEEE Spring

Compcon.. SI, 14(1981).

[8] W. Shockley, "The Path to the Conception of the Junction Transistor," IEEE Trans. Electron De-

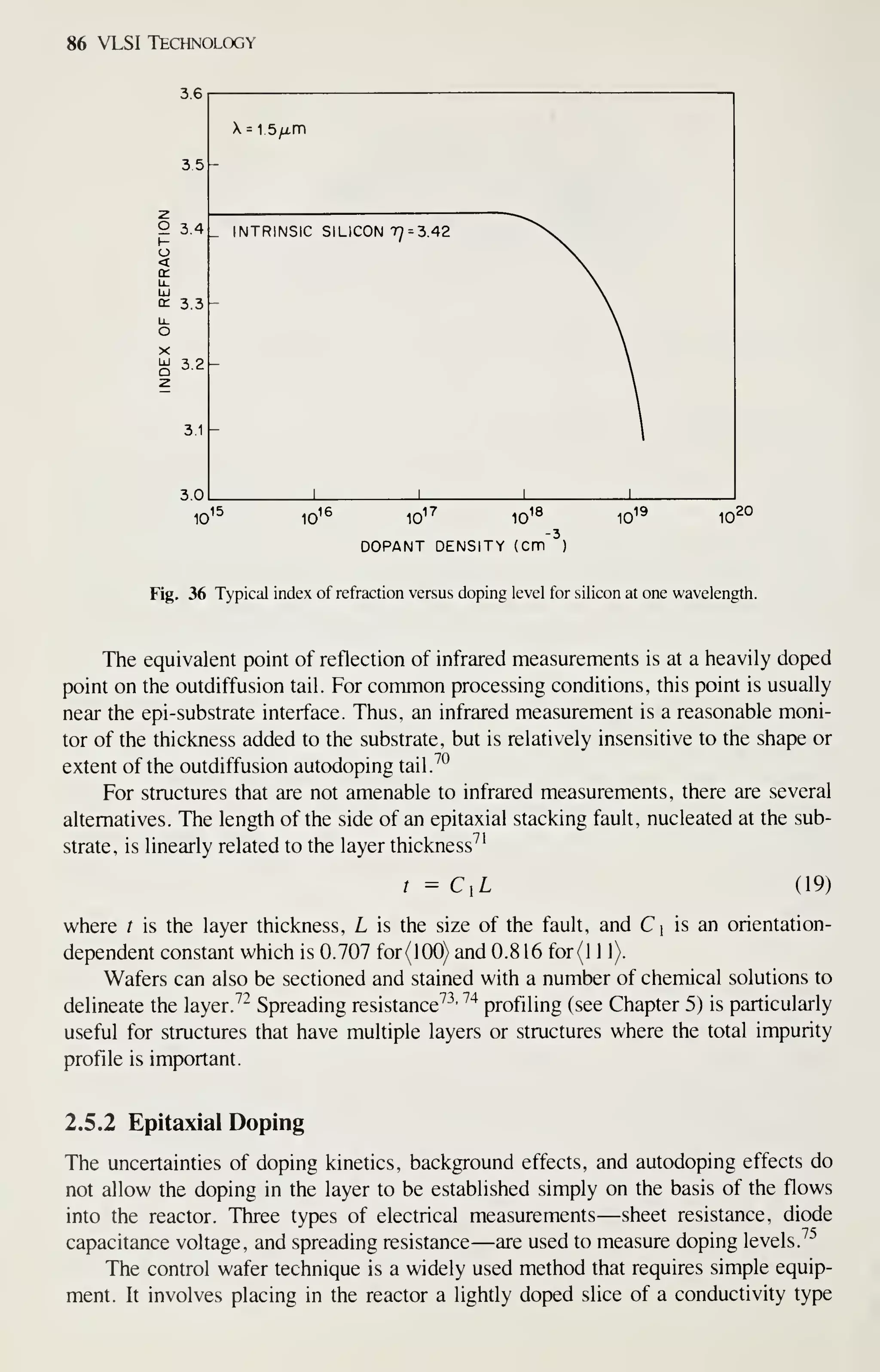

vices, ED-23, 591 {916).

[9] J. S. Kilby, "Invention of the Integrated Circuits. ""

IEEE Trans. Electron Devices, ED-23, 648

(1976).

[10] A. L. Robinson, "Electronics and Employment: Displacement Effects," in T. Forester, Ed., The

Microelectrons Revolution, MIT Press, Cambridge, Mass., 1981, p. 318.

[11] J. S. Mayo, "Technology Requirements of the Information Age," Bell Lab. Rec, 60, 55 (1982).

[12] D. Kimbel, Microelectronics, Productivity and Employment, Organization for Economic Coopera-

tional Development, Paris, 1981, p. 15.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-27-2048.jpg)

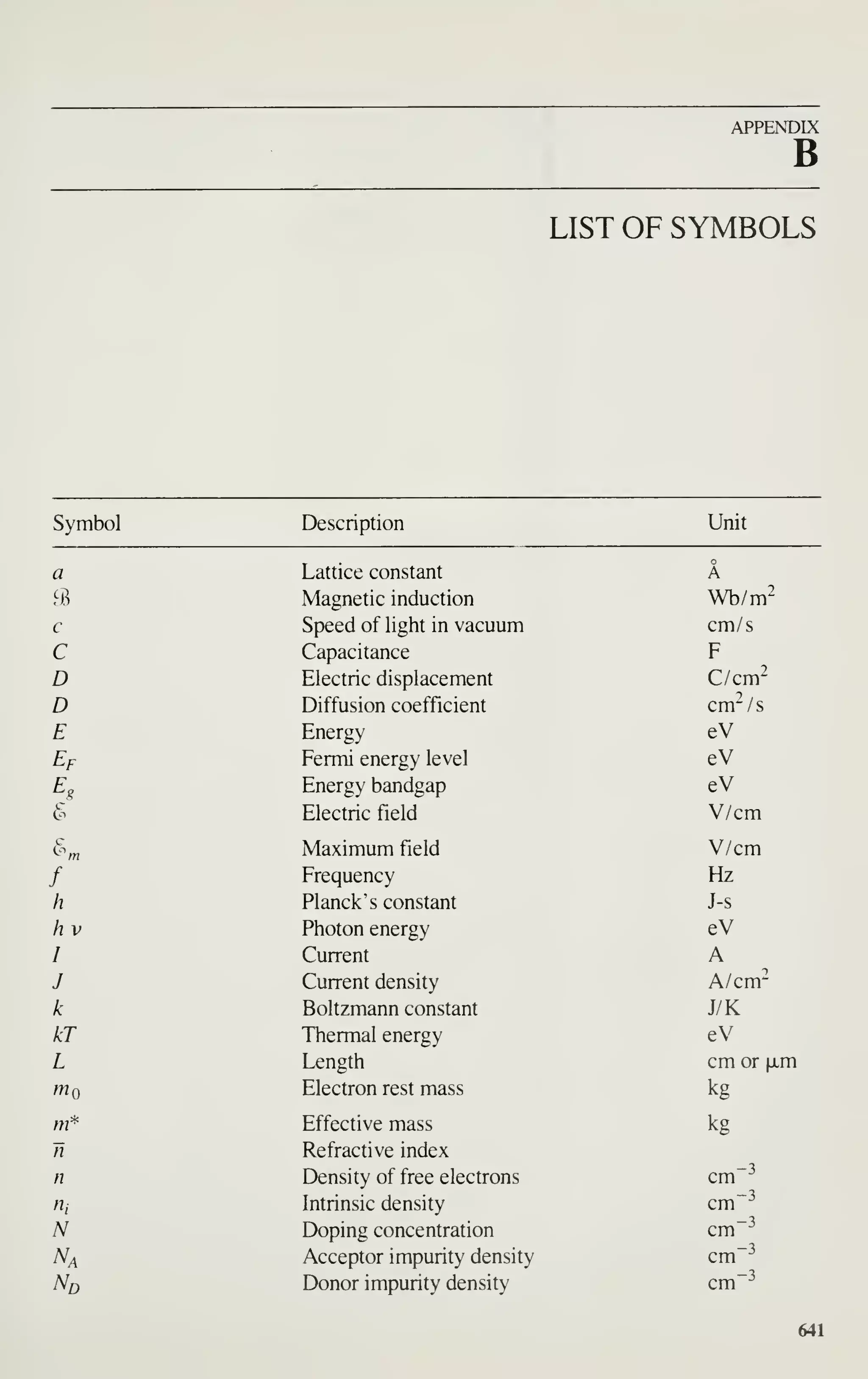

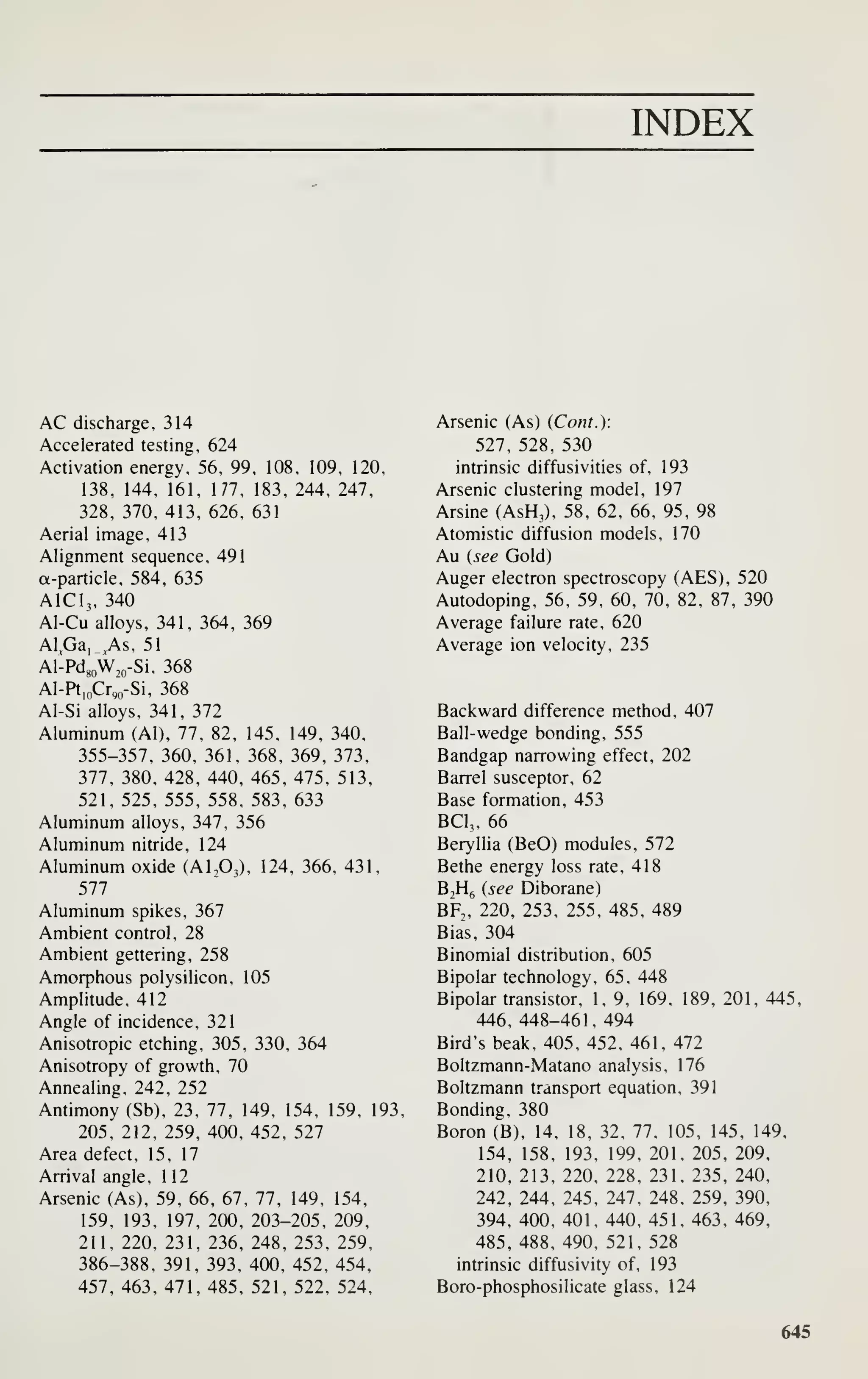

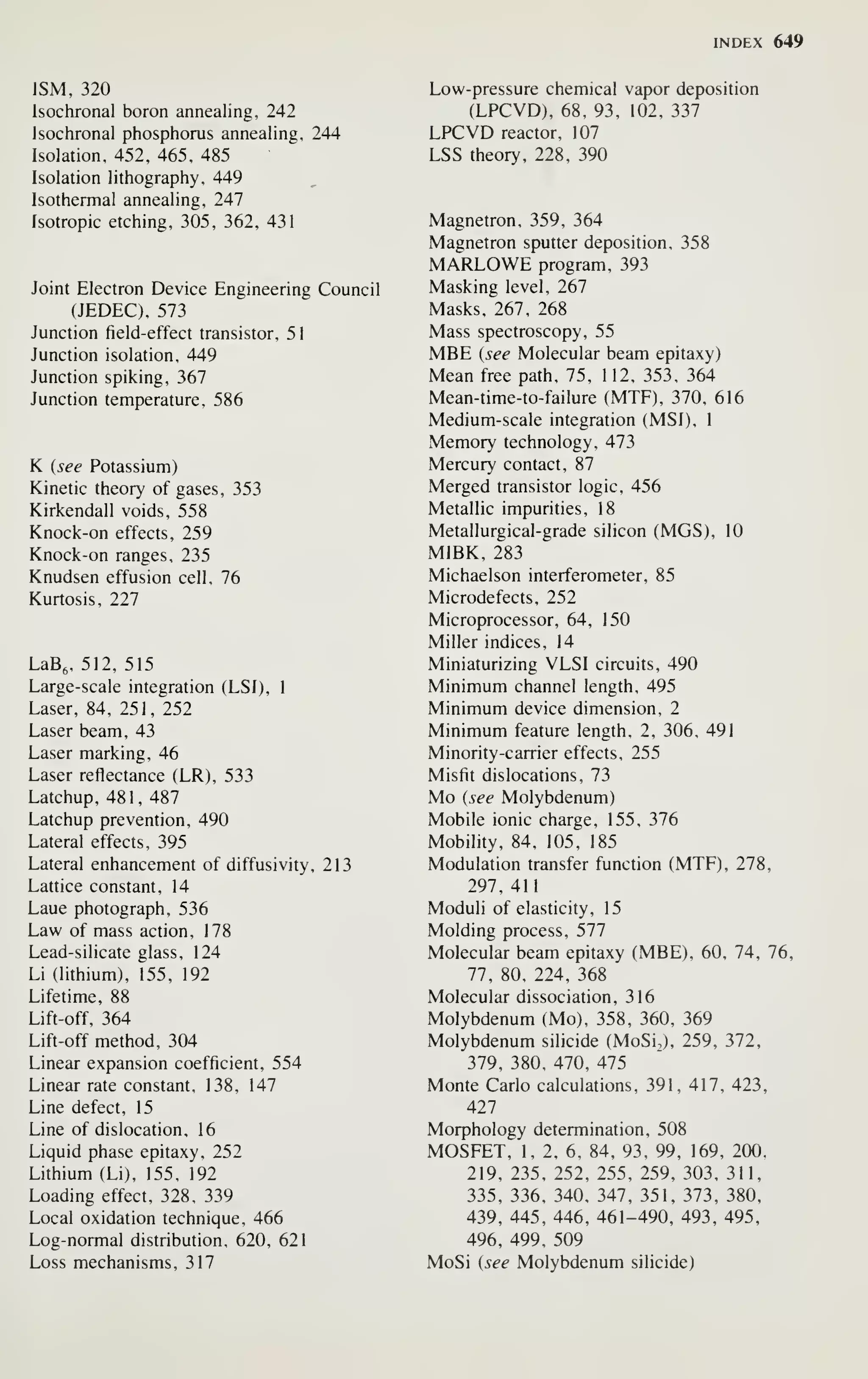

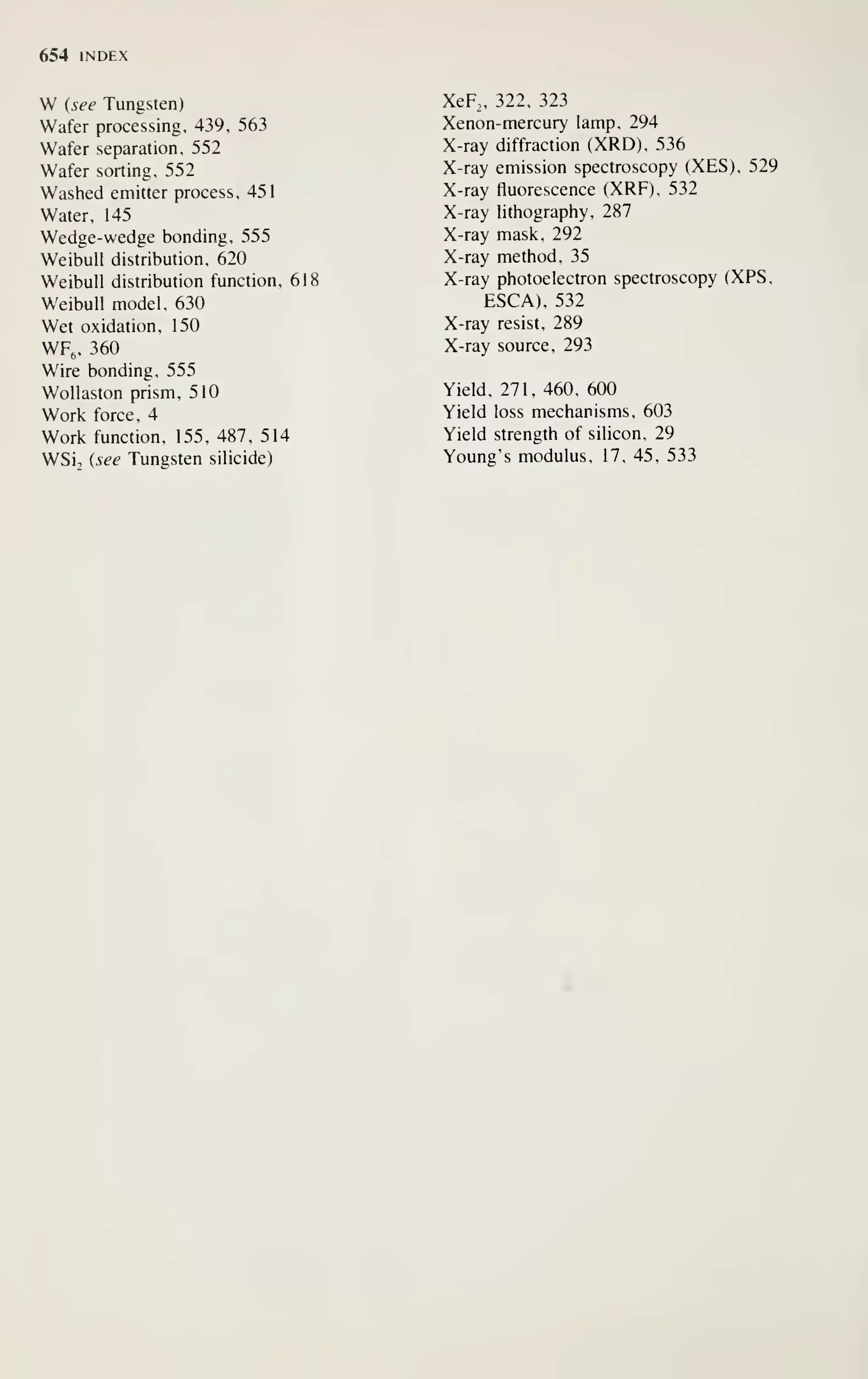

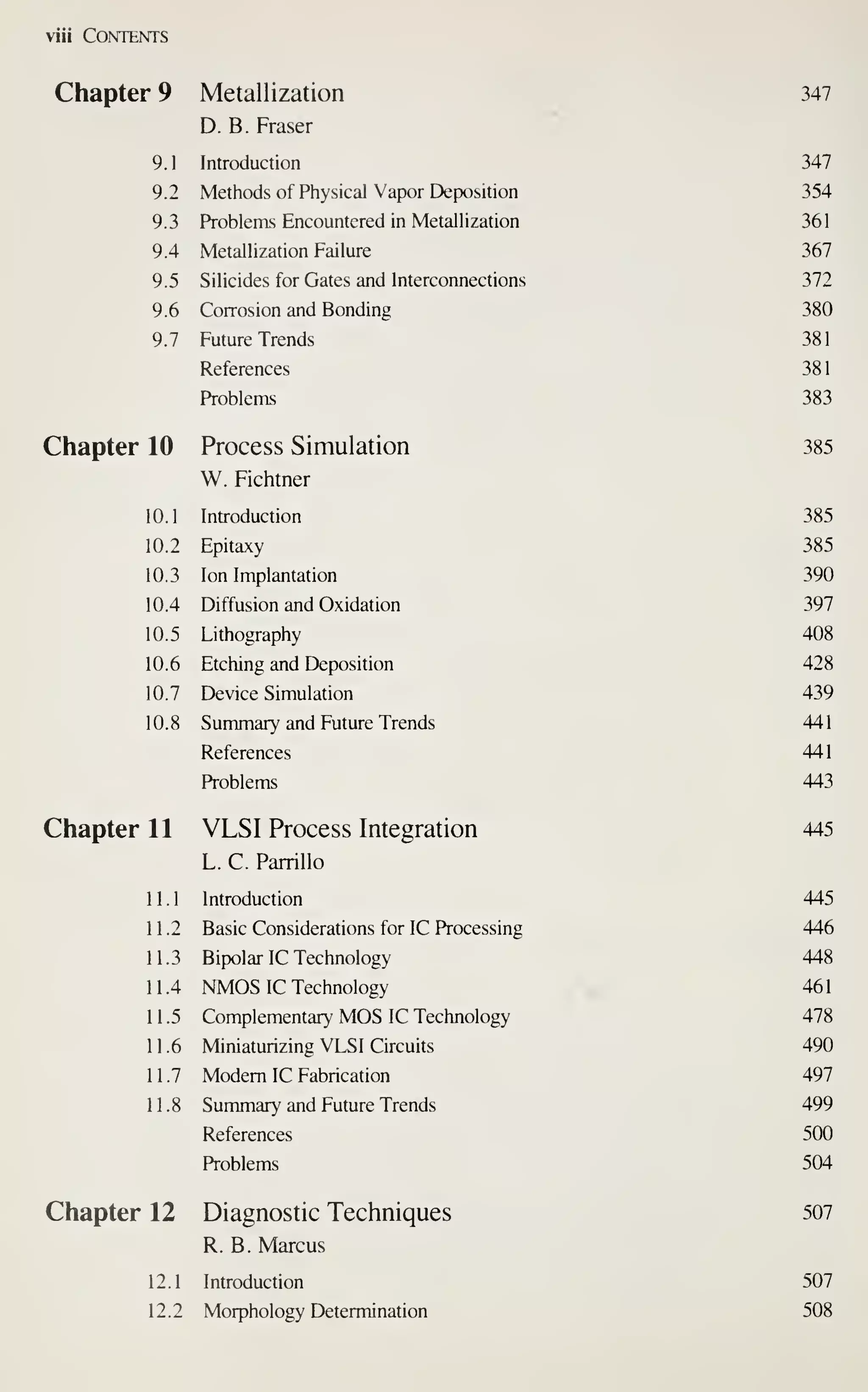

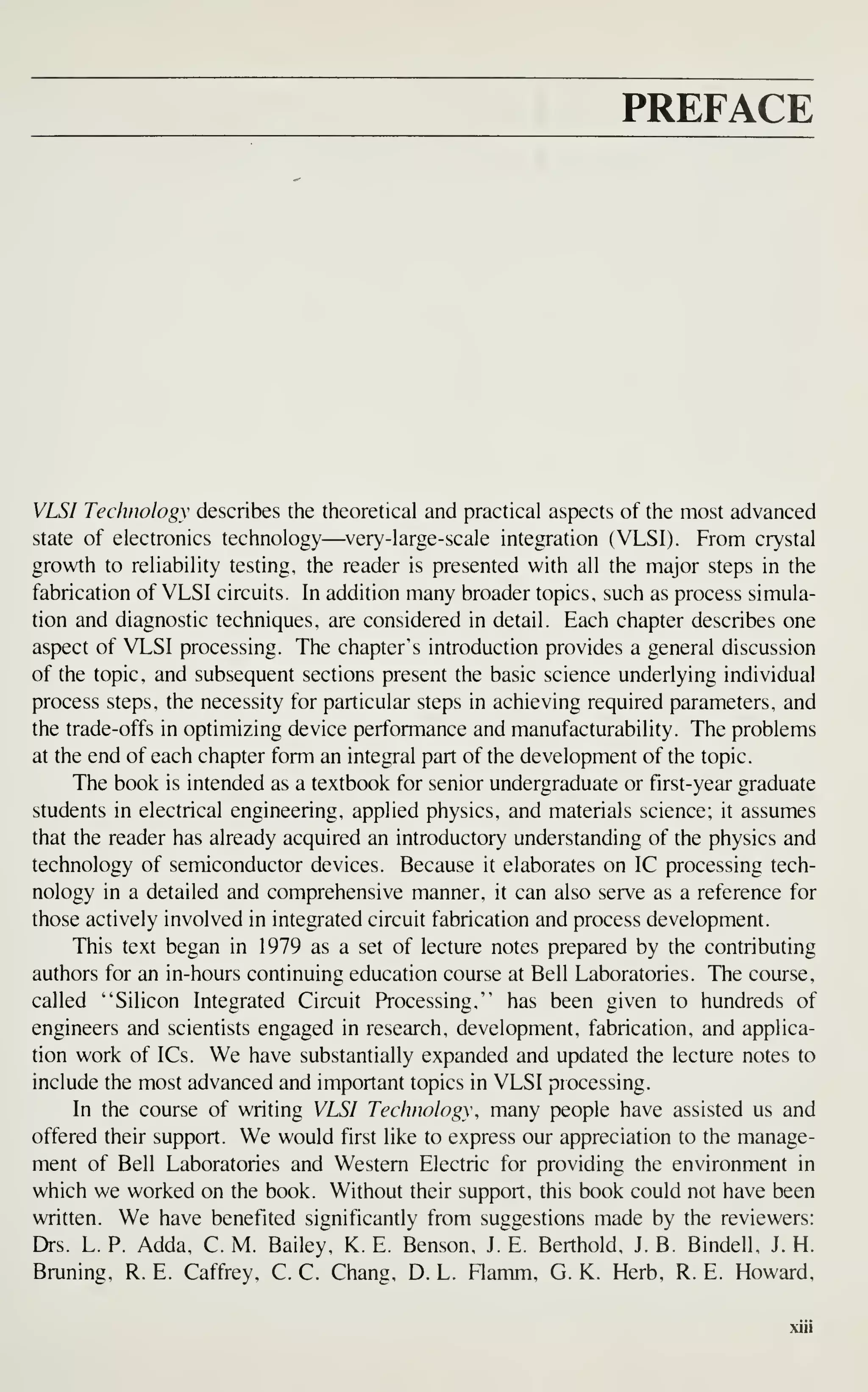

![CRYSTAL f

PLANE Ll

^

(100)

^[100] DIRECTION

Crystal Growth and Wafer Preparation 15

1 ^

(110) (111)

Fig. 6 Schematic representation of Miller indices in a cubic lattice system.

example, [111] denotes a specific direction, whereas (1 1 1) denotes the family of all

eight directions equivalent to [111]. A (100) notation denotes a particular lattice

plane, and {100} denotes all the planes crystallographically equivalent of (100).

The processing characteristics and some material properties of silicon wafers

depend on the orientation. The {111} planes have the highest density of atoms on the

surface, so crystals grow most easily on these planes. Mechanical properties such as

tensile strength are highest for (1 1 1) directions. The moduli of elasticity also show an

orientation dependence (Appendix A). Processing characteristics such as oxidation are

similarly orientation dependent. For example, {111} planes oxidize faster than {100}

planes, because they have more atoms per unit surface area available for the oxidation

reaction to occur. The choice of crystal orientation, therefore, is generally not left to

the discretion of the crystal grower, but is a device design consideration. Historically,

bipolar circuits have preferred (1 1 1) oriented material and MOS devices (100). There

are, of course, exceptions. Growth on other orientations such as (110) has been

demonstrated, but is more difficult to achieve routinely.^

A real crystal, as represented by a silicon wafer, differs from the mathematically

ideal crystal in several respects. It is finite, not infinite; thus, surface atoms are

incompletely bonded. The atoms are displaced from their ideal locations by thermal

agitation. Most importantly, real crystals have defects'^' " classified as follows: (1)

point defect, (2) line defect, (3) area or planar defect, and (4) volume defect. Defects

influence the optical, electrical, and mechanical properties of silicon.

Point defects Point defects take several forms as shown in Fig. 7. Any nonsilicon

atom incorporated into the lattice at either a substitutional or interstitial site is con-

sidered a point defect. This is true whether the atom is an intentional dopant or unin-

tentional impurity. Missing atoms create a vacancy in the lattice called a "Schottky

defect," which is also considered a point defect. A silicon atom in an interstitial lat-

tice site with an associated vacancy is called a "Frenkel defect." Vacancies and inter-

stitials have equilibrium concentrations that depend on temperature. From thermo-

dynamic principles the concentration as a function of temperature can be derived and

has the following relation:

N^ = A exp {-EJkT) (4)](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-35-2048.jpg)

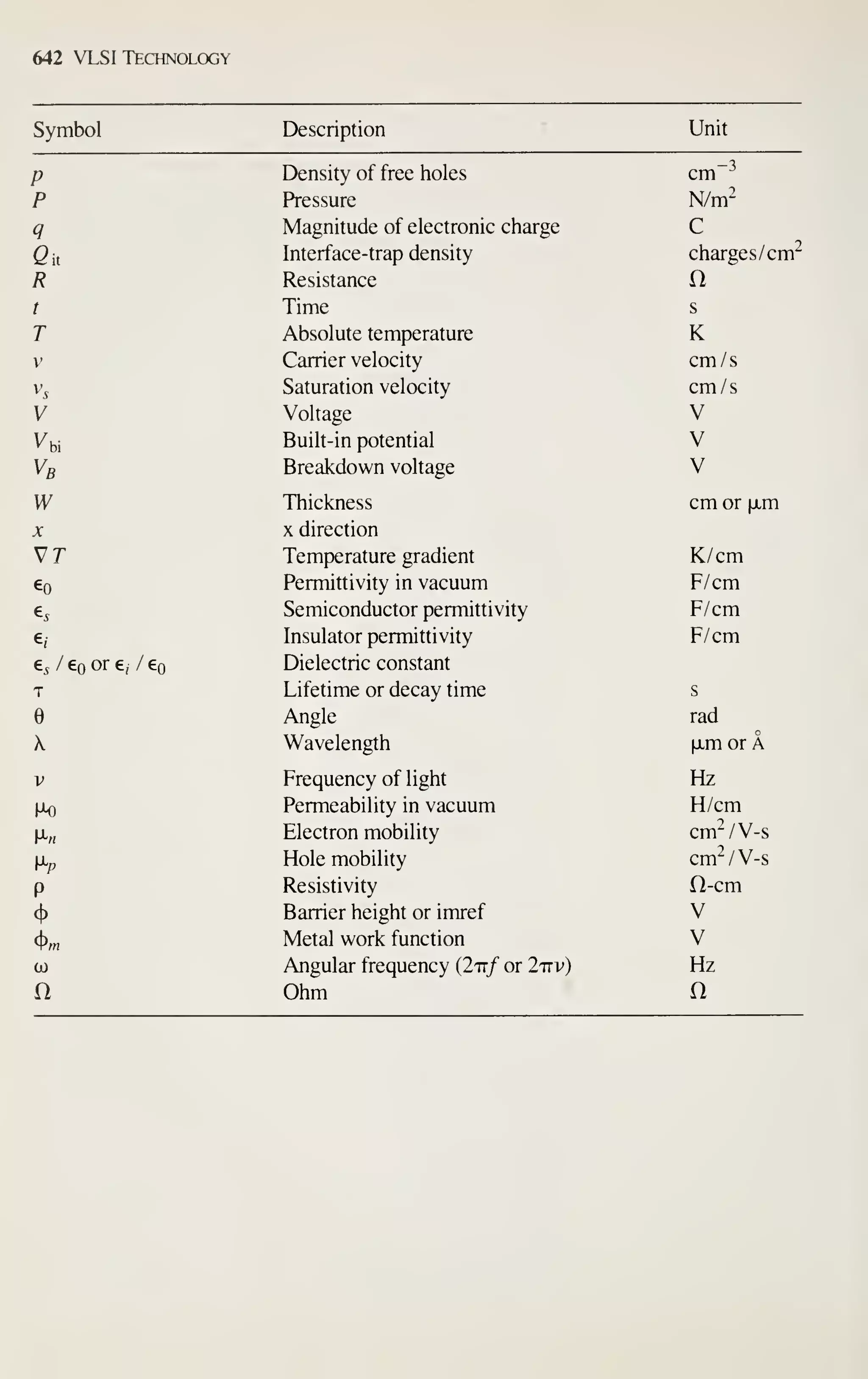

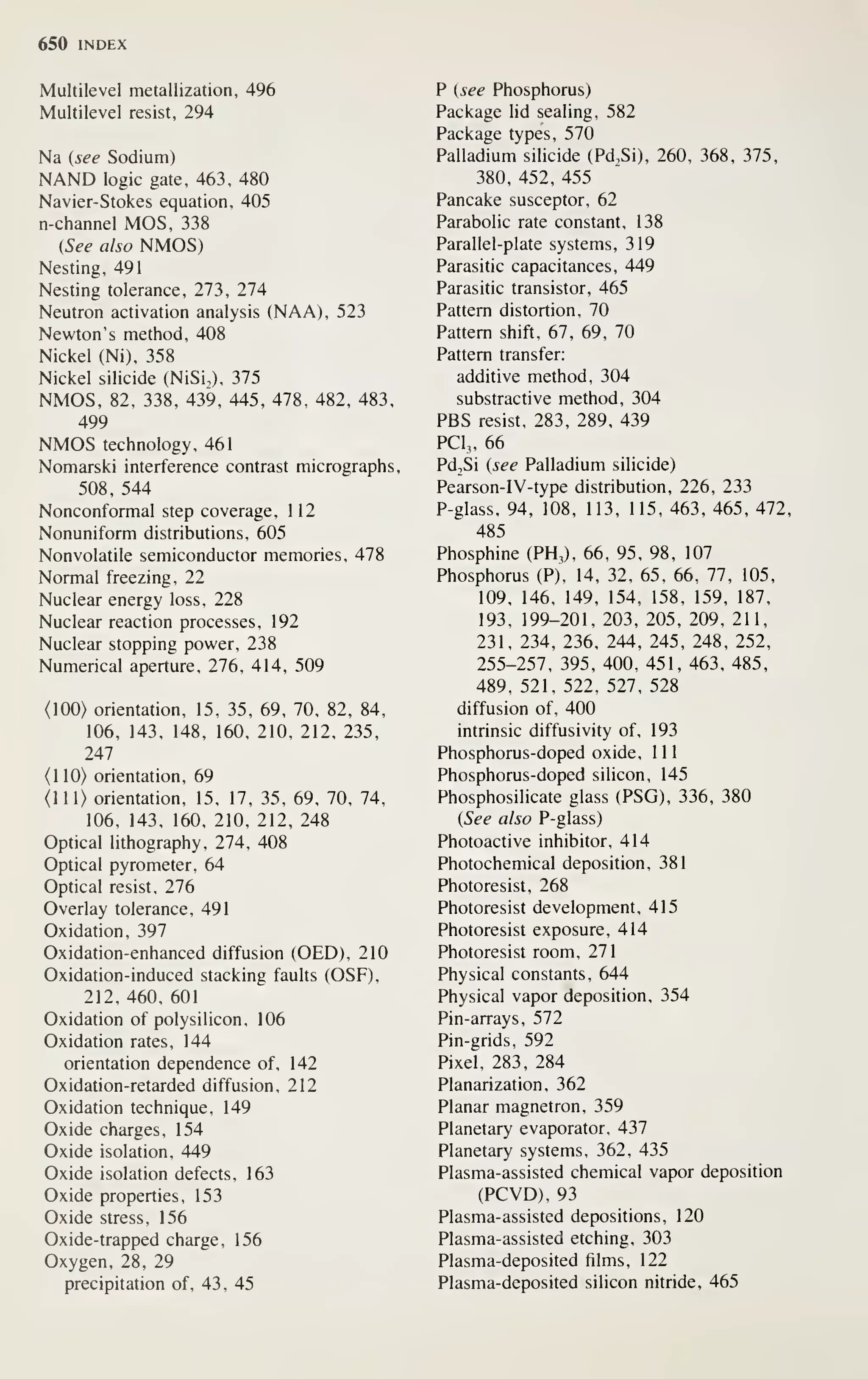

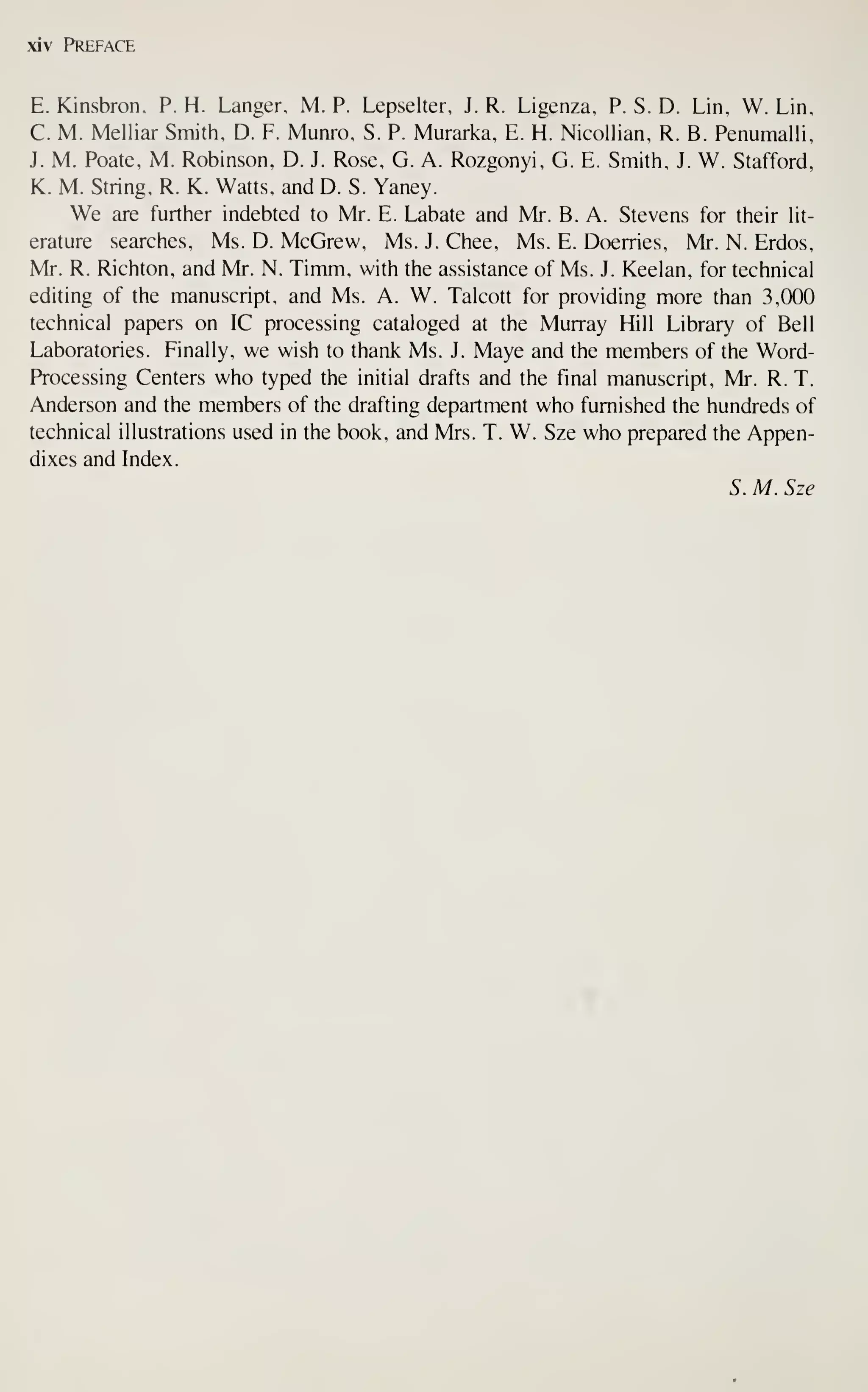

![Crystal Growth and Wafer Preparation 19

interface boundary layer (liquid)

SOLID (CRYSTAL)

GROWTH

AXIS

MP

o IMPURITY ATOMS

• SILICON ATOMS

DISTANCE

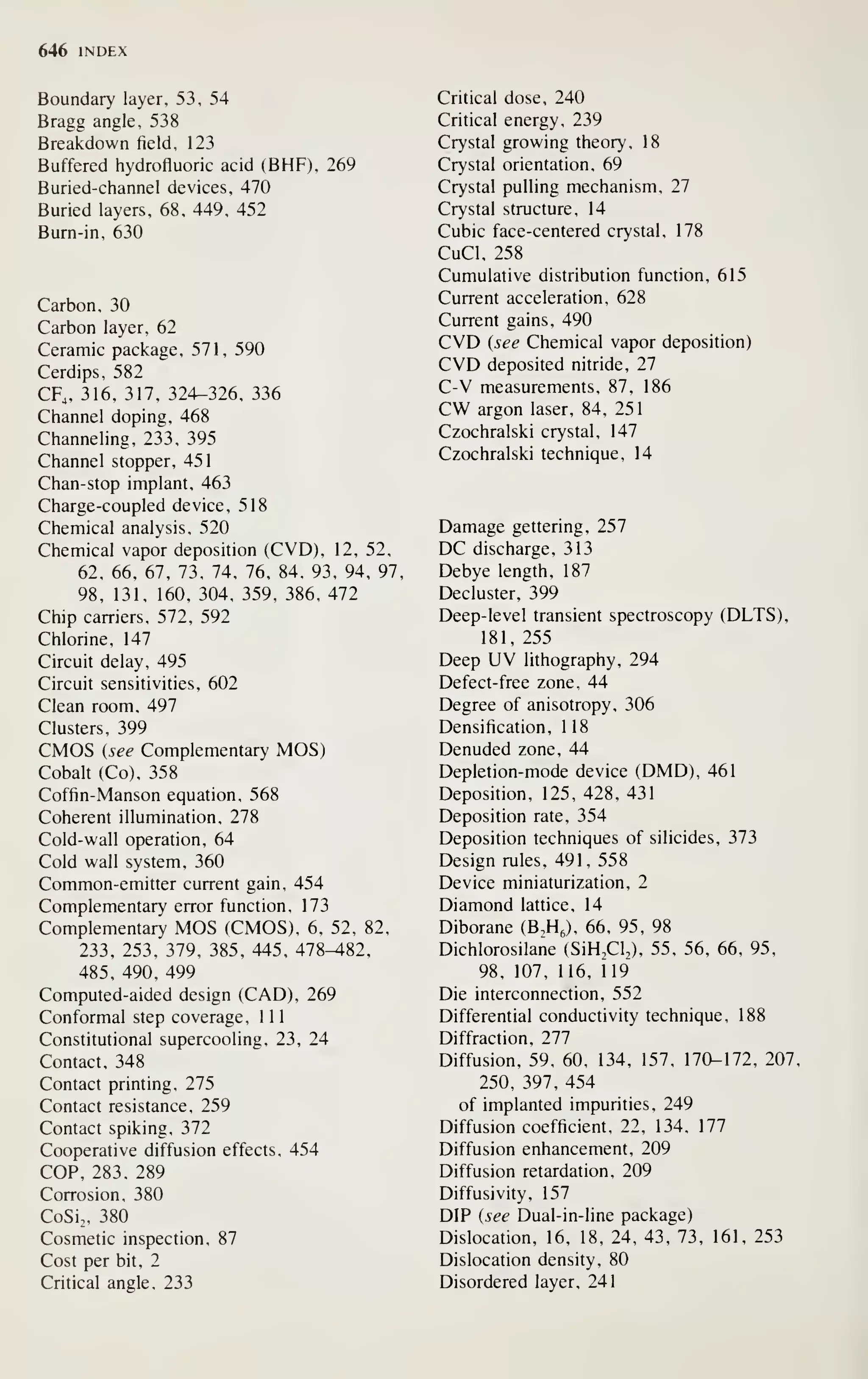

Fig. 10 Temperature gradients, solidification, and transport phenomena involved in Czochralski growth.

Positions 1 and 2 represent the location of isotherms associated with Eq. 6 and the crystal solidification at

the interface. Impurity atoms are transported across the boundary' layer and incorporated into the growing

crystal interface. M. P. is the melting point.

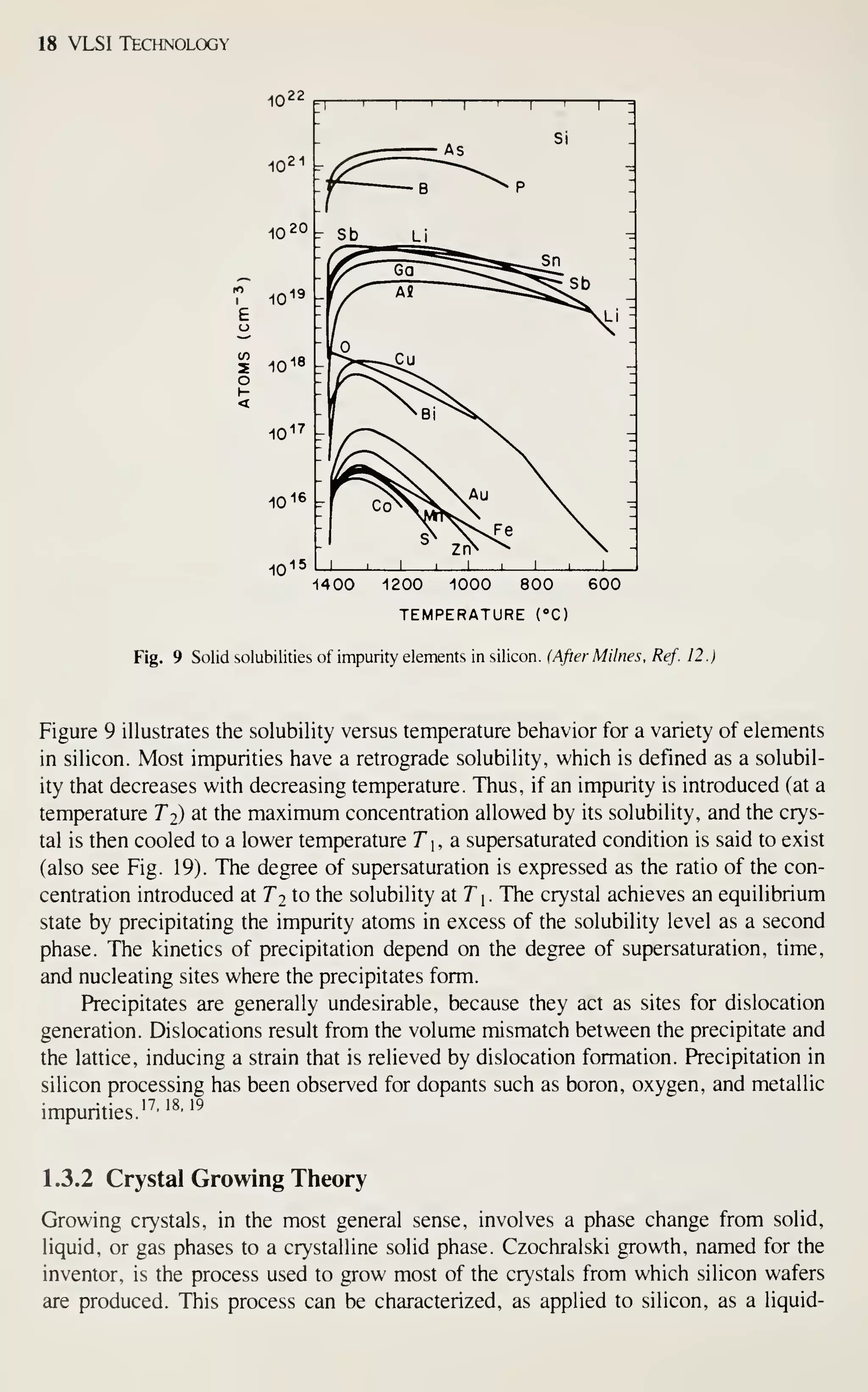

solid monocomponent growth system. This section discusses some elements of this

process as it relates to the understanding of the properties of the grown crystals. For a

more complete treatment of crystal growth, refer to the many excellent books devoted

to the subject.^-

-^•-'

The growth of a CZ crystal involves the solidification of atoms from a liquid

phase at an interface. The speed of growth is determined by the number of sites on the

face of the crystal and the specifics of heat transfer at the interface. Figure 10

schematically represents the transport process and temperature gradients involved.

Macroscopically, the heat transfer conditions about the interface can be modelled by

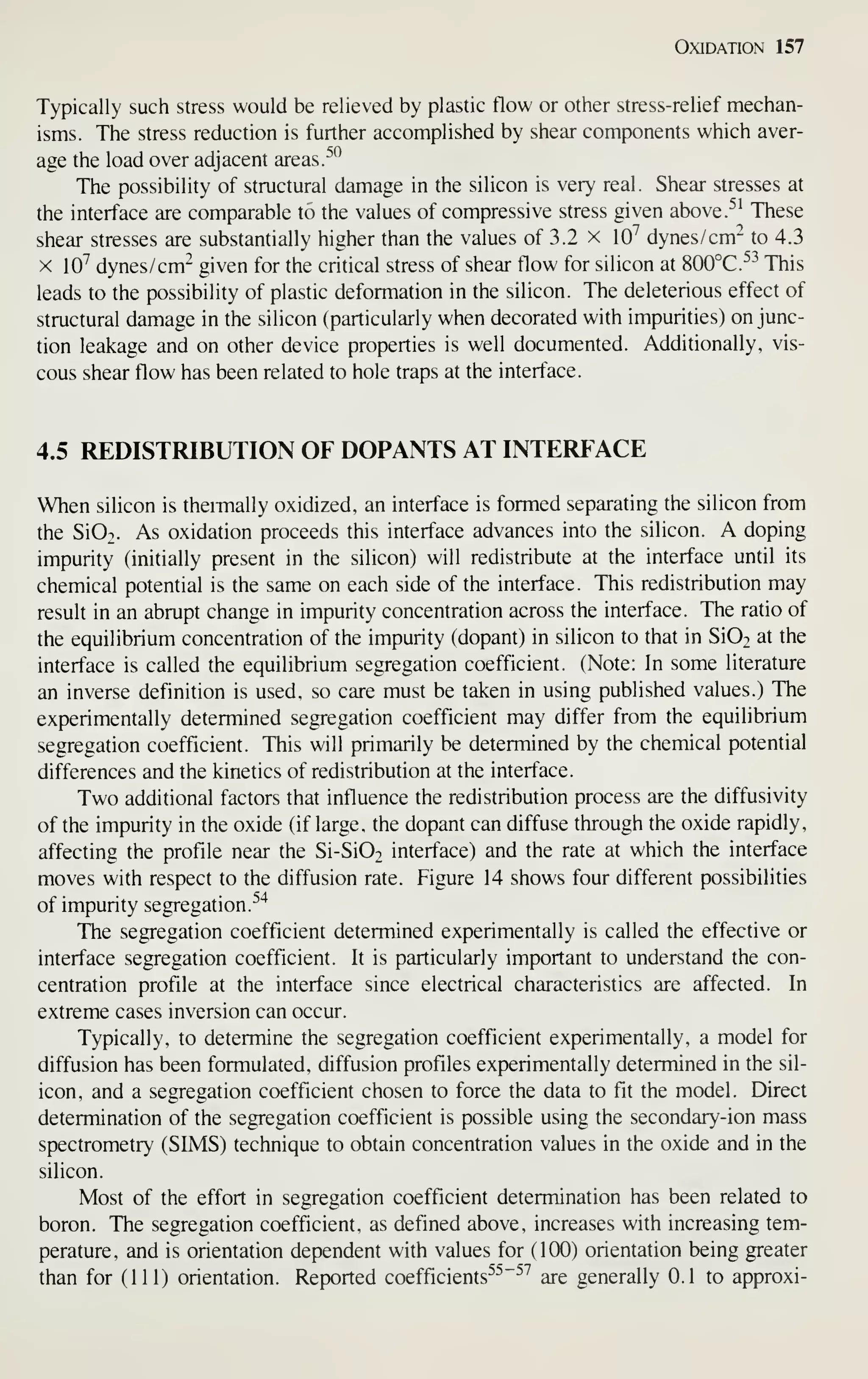

the following equation:^'

dm

dt

+ k,-— A

dX]

1

dT ,

dx-)

(6)

where L is the latent heat of fusion, dm/dt is the mass solidification rate, T is the

temperature, kj and k^ are the thermal conductivities of the liquid and solid, respec-

tively, dT/dx I and dT/dxi are the thermal gradients at points 1 and 2 (near the inter-

face in the liquid and solid, respectively), and A

and A 2 are the areas of the iso-

therms at positions 1 and 2, respectively.

From Eq. 6 the maximum pull rate of a crystal under the condition of zero ther-

mal gradient in the melt can be deduced: '' ^^

- A_ 4L

U dx

V, (7)

where V^.^ is the maximum pull rate (or pull speed) and d is the density of solid sili-

con. Figure 1 1 is an experimentally determined temperature variation along a crystal.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-39-2048.jpg)

![Crystal Growth and Wafer Preparation 25

SEED SHAFT,

LIFT AND

ROTATION

SENSOR FOR

DIAMETER CONTROL

VIEW

PURGE

VPORT "^ T

TUBE I

^ ^

INSULATION-

HEATER

SUSCEPTOR

TEMPERATURE

SENSOR

"SUPPER HOUSING

CONTROL SYSTEM

AND

POWER SUPPLY

] ISOLATION VALVE

AMBIENT GAS INLET

SEED SHAFT a CHUCK

FURNACE CHAMBER

MELT

CRUCIBLE

EXHAUST

VACUUM

PUMP

CRUCIBLE ROTATION

AND LIFT

Fig. 16 Schematic representation of a crystal grower.

100-mm diameter and 3.0-m length. The puller has four subsystems as follows (Fig.

16):

1. Furnace: crucible, susceptor and rotation mechanism, heating element and

power supply, and chamber.

2. Crystal-pulling mechanism: seed shaft or chain, rotation mechanism, and seed

chuck.

3. Ambient control: gas source, flow control, purge tube, and exhaust or vacuum

system.

4. Control system: microprocessor, sensors, and outputs.

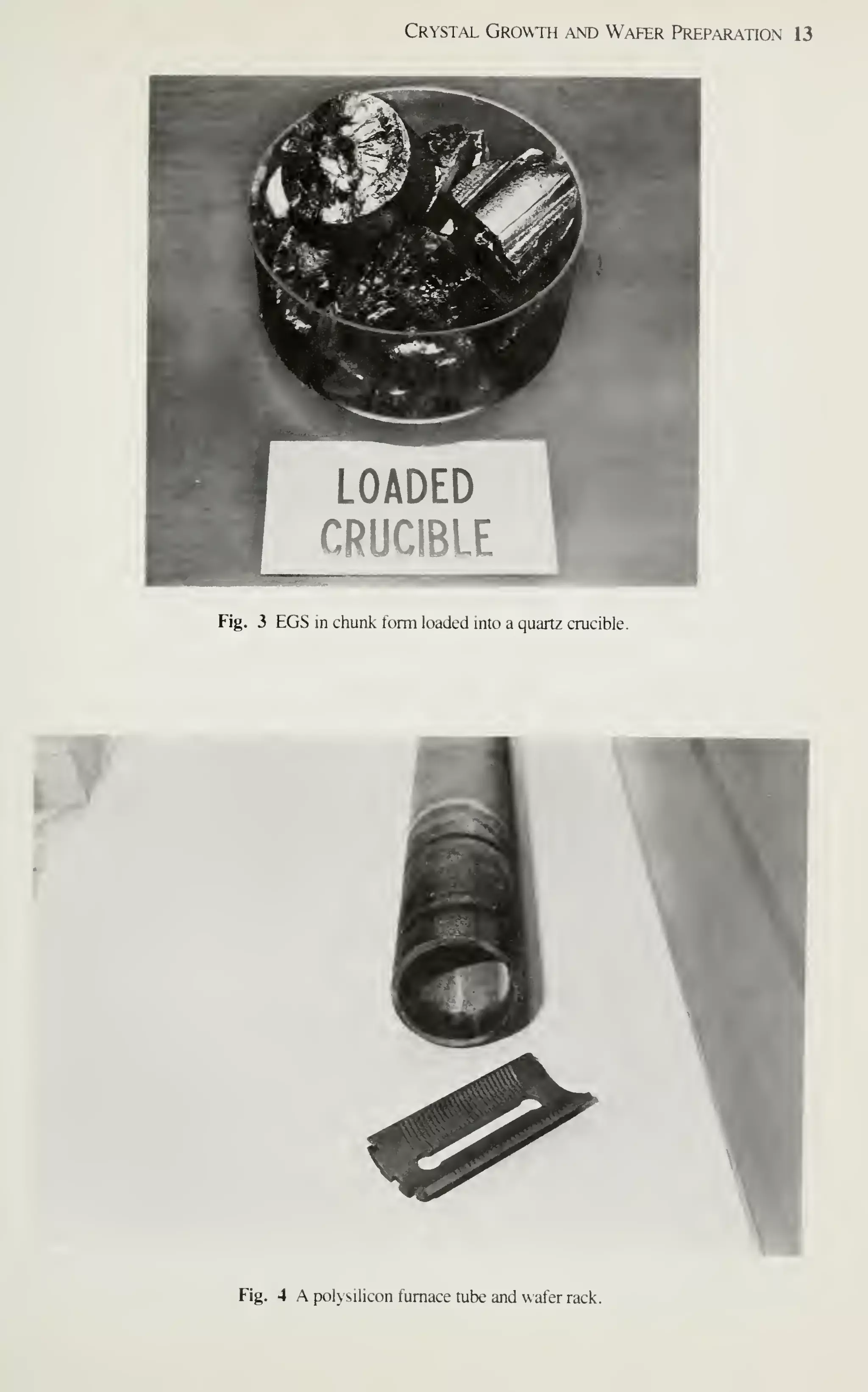

Furnace Perhaps the most important component of the growing system is the cruci-

ble (Fig. 3). Since it contains the melt, the crucible material should be chemically

unreactive with molten silicon. This is a major consideration, because the electrical

properties of silicon are sensitive to even ppb levels of impurities. Other desirable

characteristics for crucible material are a high melting point, thermal stability and

hardness. Additionally, the crucible should be inexpensive or reusable. Unfor-

tunately, molten silicon can dissolve virtually all commonly used high-temperature](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-45-2048.jpg)

![Crystal Growth and Wafer Preparation 47

Large diameter wafers (>150 mm) are feasible and 200-mm wafers have been

produced. Practical implementation is awaiting the need for further productivity

improvements and improved circuit fabrication capability, particularly in the litho-

graphic area. Ingots of larger diameters will be grown in big pullers. The slower cool-

ing rates experienced by these such materials may alter the properties of the material,

particularly the point-defect kinetics. This topic provides an area for continued

research, because properties of the material are related to defects formed in device

processing, and thus related to IC yield.

REFERENCES

[1] C. L. Yaws, R. Lutwack, L. Dickens, and G. Hsiu, "Semiconductor Industry Silicon: Physical and

Thermodynamic Properties," Solid State TechnoL. 24, 87 ( 1981).

[2] J. C. Bailar, Editor, Comprehensive Inorganic Chemistry, 1, Pergamon Press, New York, 1973.

[3] W. Shockley, "The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors," Bell

Syst. Tech. J., 28, 435 {949).

[4] L. D. Grossman and J. A. Baker, "Polysilicon Technology," Semiconductor Silicon 1977. Electro-

chem. Soc., Pennington, New Jersey, 1977, p. 18.

[5] Am. Soc. Test. Mater., ASTM Standard, F574, Part 43.

[6] W. Dietze, L. P. Hunt, and D. H. Sawyer, "The Preparation and Properties of CVD-Silicon Tubes

and Boats for Semiconductor Device Technology," J. Electrochem. Soc, 121 , 1112 (1974).

[7] S. N. Rea, "Gzochralski Silicon Pull Rate Limits," 7. Cryst. Growth, 54, 267 ( 1981).

[8] R. A. Laudise, The Growth of Single Crystals, Prentice Hall, Englewood Cliffs, New Jersey, 1970.

[9] L. D. Dyer, "Dislocation-Free Gzochralski Growth of (110) Silicon Crystals," J. Cryst. Growth, 47,

533(1979).

[10] K. V. Ravi, Imperfections and Impurities in Semiconductor Silicon. Wiley, New York, 198 1

.

[11] R. K. Watts, Point Defects in Crystals, Wiley and Sons, New York, 1977.

[12] A. G. Milnes, Deep Levels in Semiconductors. Wiley, New York, 1973.

[13] J. Friedel, Dislocations, Pergamon Press, New York, 1964.

[ 14] A. J. R. deKock and W. M. van de Wijgert. "The Effect of Doping on the Formation of Swirl Defects

in Dislocation-Free Gzochralski-Grown Silicon," J. Cryst. Growth, 49, 718 (1980).

[15] S. M. Hu, "Temperature Distribution and Stresses in Gircular Wafers in a Row during Radiative Cool-

ing," J. Appl. Phys., 40, 4413 ( 1969).

[16] K. G. Moerschel, C. W. Pearce, and R. E. Reusser, "A Study of the Effects of Oxygen Content, Ini-

tial Bow and Furnace Processing on Warpage of Three-Inch Diameter Silicon Wafers," Semiconductor

Silicon 1977, Electrochem. Soc, Pennington, New Jersey, 1977, p. 170.

[17] S. Kishino, Y. Matsushita, and M. Kanamori. "Carbon and Oxygen Role for Thermally Induced

IVIicrodefect Formation in Silicon," Appl. Phys. Lett.. 35, 213 ( 1979).

[18] A. Armigliato. D. Nobili. P. Ostoja, M. Servidori, and S. Solmi, "Solubility and Precipitation of

Boron in Silicon," Semiconductor Silicon 1977, Electrochem. Soc, Pennington, New Jersey, 1977,

p. 638.

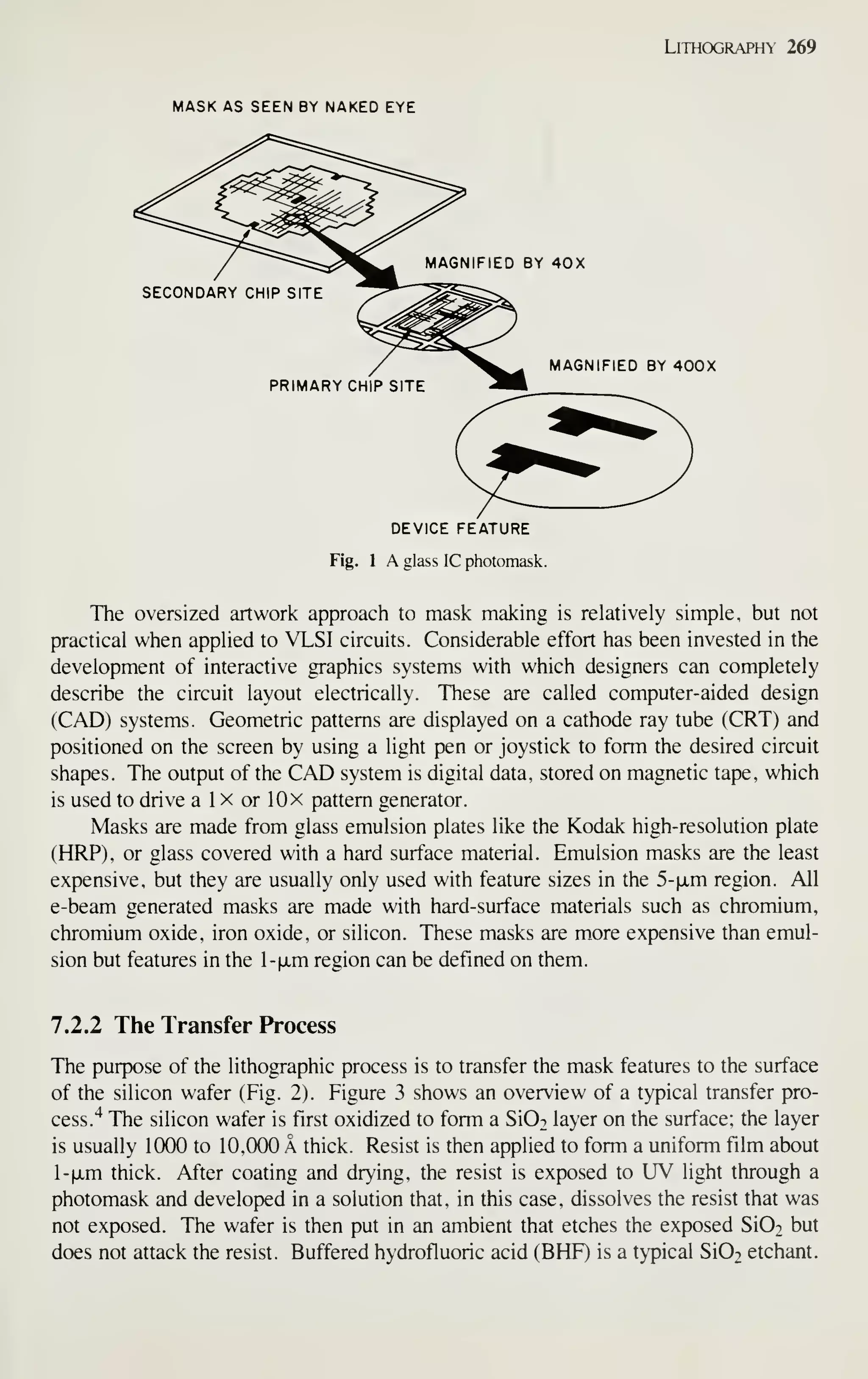

[19] W. T. Stacy, D. F. Allison, and T. C. Wu, "The Role of Metallic Impurities in the Formation of Haze

Defects," Semiconductor Silicon 1981 , Electrochem. Soc, Pennington, New Jersey, 1981, p. 344.

[20] B. R. Pamplion, Crystal Growth, Pergamon Press. New York, 1983.

[21] W. R. Runyan, Silicon Semiconductor Technology, McGraw-Hill, New York, 1965.

[22] T. G. Digges, Jr. and R. Shima, "The Effect of Growth Rate, Diameter and Impurity Concentration

on Structure." J. Cryst. Growth, 50, 865 (1980).

[23] S. M. J. G. Van Run, "A Critical Pulling Rate for Remelt Suppression in Silicon Crystal Growth," J.

Cryst. Growth, 53, 441 (98).

[24] H. Kolker, "The Behavior of Nonrotational Striations in Silicon," J. Cryst. Growth, 50, 852 (1980).](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-67-2048.jpg)

![48 VLSI Technology

[25] J. Chikawa and S. Yoshikawa, "Swirl Defects in Silicon Single Crystals," Solid State TechnoL, 23,

65(1980).

[26] J. A. Burton, R. C. Prim, and P. Slichter.y. Chem. Phys.. 21, 1987 (1953).

[27] J. R. Carruthers, A. F. Win, and R. E. Reusser, "Czochralski Growth of Large Diameter Silicon Cry-

stals - Convection and Segregation," Semiconductor Silicon 1977, Electrochem. Soc., Pennington,

New Jersey, 1977, p. 61

.

[28] K. M. Kim, "Interface Morphological Instability in Czochralski Silicon Crystal Growth from Heavily

Sb-Doped Melt," 7. Electrochem. Soc, 126, 875 ( 1979).

[29] K. E. Benson, ,V. Lin, and E. P. Martin, "Fundamental Aspects of Czochralski Silicon-Crystal

Growth for VLSI," Semiconductor Silicon 1981, Electrochem. Soc., Pennington, New Jersey, 1981,

p. 33.

[30] M. H. Liepold, T. P. O'Donnell, and M. A. Hagan, "Materials of Construction for Silicon Crystal

Growth," J. Crysi. Growth, 40, 366 (1980).

[31] F. A. Voltmer and F. A. Padovani, "The Carbon-Silicon Phase Diagram for Dilute Carbon Concentra-

tion," Semiconductor Silicon 1973, Electrochem. Soc., Pennington, New Jersey, 1973, p. 75.

[32] H. Hirata and K. Hoshikawa, "The Dissolution Rate of Silica in Molten Silicon," Jpn. J. Appl. Phys.,

19, 1573(1980).

[33] B. Bathey, H. E. Bates, and M. Cretella, "Effect of Carbon on the Dissolution of Fused Silica in

Liquid Silicon," J. Electrochem. Soc, 128, 771 (1980).

[34] M. Watanabe, T. Usami, H. Muroaka, S. Matsuo, Y. Imanishi, and H. Nagashima, "Oxygen-Free

Silicon Single Crystal from Silicon-Nitride Crucible," Semiconductor Silicon 1981, Electrochem.

Soc., Pennington, New Jersey, 1981, p. 126.

[35] H. M. Liaw, "Oxygen and Carbon in Czochralski-Grown Silicon," Semicon. Int., 2,1( 1979).

[36] T. Carlberg, T. B. King, and A. F. Witt, "Dynamic Oxygen Equilibrium in Silicon Melts during Cry-

stal Growth," 7. f/mrof/zt'm. 5oc., 127, 189(1981).

[37] T. Suzuki, N. Isawa, Y. Okubo, and K. Hoshi, "CZ Silicon Growth in a Transverse Magnetic Field,"

Semiconductor Silicon 1981 , Electrochem. Soc., Pennington, New Jersey, 1981, p. 90.

[38] J. R. Patel, "Oxygen in Silicon," Semiconductor Silicon 1977. Electrochem. Soc., Pennington, New

Jersey, 1977, p. 521.

[39] Am. Soc. Test. Mater., ASTM Standard, F121-76, Part 43.

[40] J. Doerschel and F. G. Kirscht, "Differences in Plastic Deformation Behavior of CZ and FZ Grown

Silicon Crystals," Phys. Status SolidiA, 64, K85 (1981).

[41] K. Sumino et al., "The Origin of the Difference in the Mechanical Strengths of Czochralski Silicon,"

Jpn. J. Appl. Phys., 19, L49 (1980).

[42] C. W. Pearce, L. E. Katz, and T. E. Seidel, "Considerations Regarding Gettering in Integrated Cir-

cuits," Semiconductor Silicon 1981 , Electrochem. Soc., Pennington, New Jersey. 1981, p. 705.

[43] T. Nozaki, "Concentration and Behavior of Carbon in Semiconductor Silicon," J. Electrochem. Soc,

117, 1566(1970).

[44] Y. Matsushita, S. Kishino, and M. Kanamori, "A Study of Thermally Induced Microdefects in

Czochralski-Grown Silicon Crystals: Dependence on Annealing Temperature and Starting Material,"

Jpn. J. Appl. Phys., 19, LlOl (1980).

[45] D. G. Schimmel, "A Comparison of Chemical Etches for Revealing (100) Silicon Crystal Defects," J.

Electrochem. Soc, 123, 734 (1976).

[46] A. C. Bonora, "Silicon Wafer Process Technology: Slicing, Etching, Polishing," Semiconductor Sili-

con 1977, Electrochem. Soc., Pennington, New Jersey, 1977, p. 154.

[47] Am. Soc. Test. Mater., ASTM Standard, F84, Part 43.

[48] Am. Soc. Test. Mater., ASTM Standard, F723, Part 43.

[49] W. R. Thurber, R. L. Mattis, and Y. M. Liu, "Resistivity Dopant Density Relationship for Silicon,"

Semiconductor Characterization Techniques, Electrochem. Soc., Pennington, New Jersey, 1978,

p. 81.

[50] S. E. Bradshaw and J. Goorissin, "Silicon for Electronic Devices," J. Cryst. Growth, 48, 514

(1980).

[51] R. B. Hening, "Silicon Wafer Technology - State of the Art 1976," Solid State Technol., 19, 37

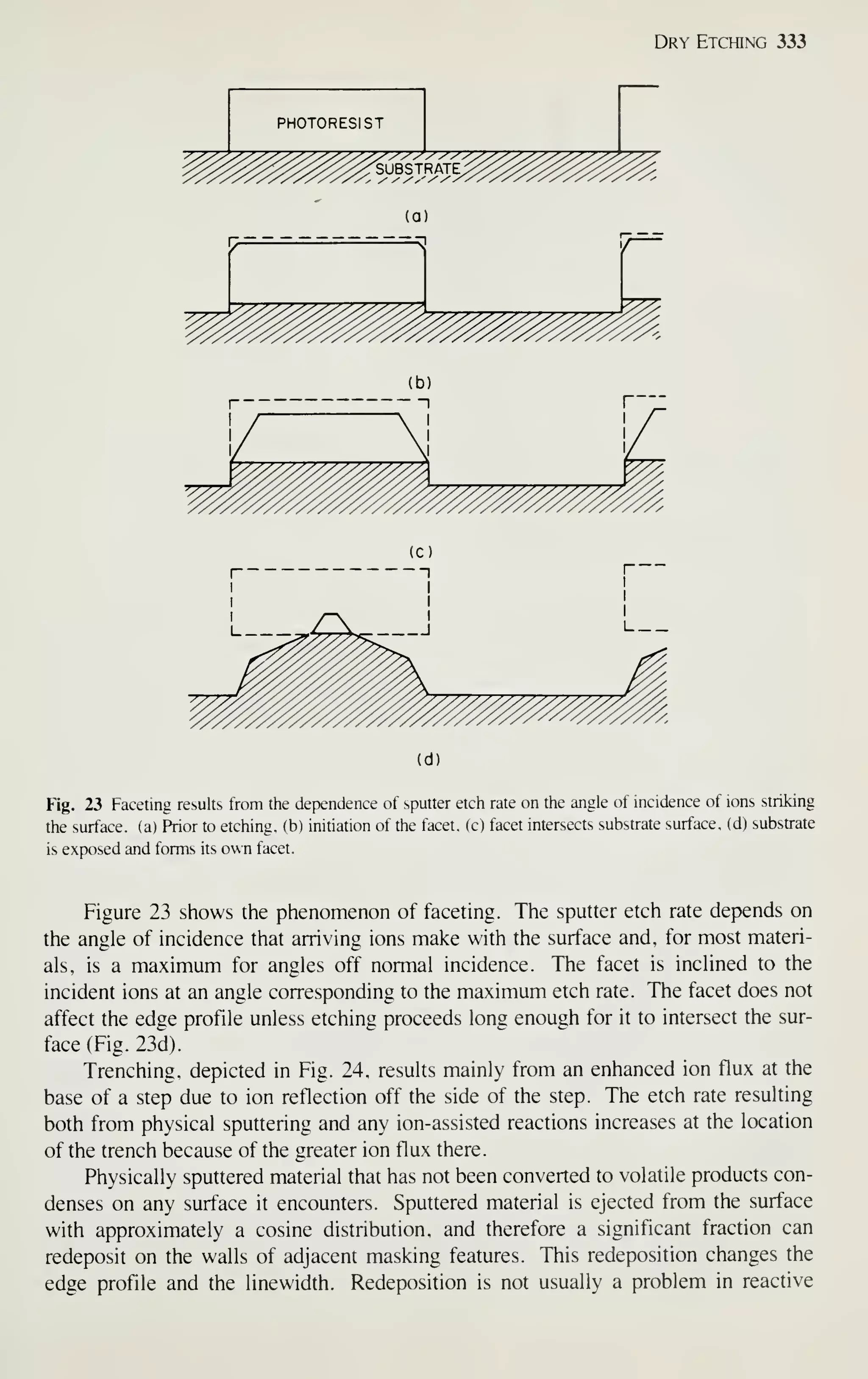

(1976).](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-68-2048.jpg)

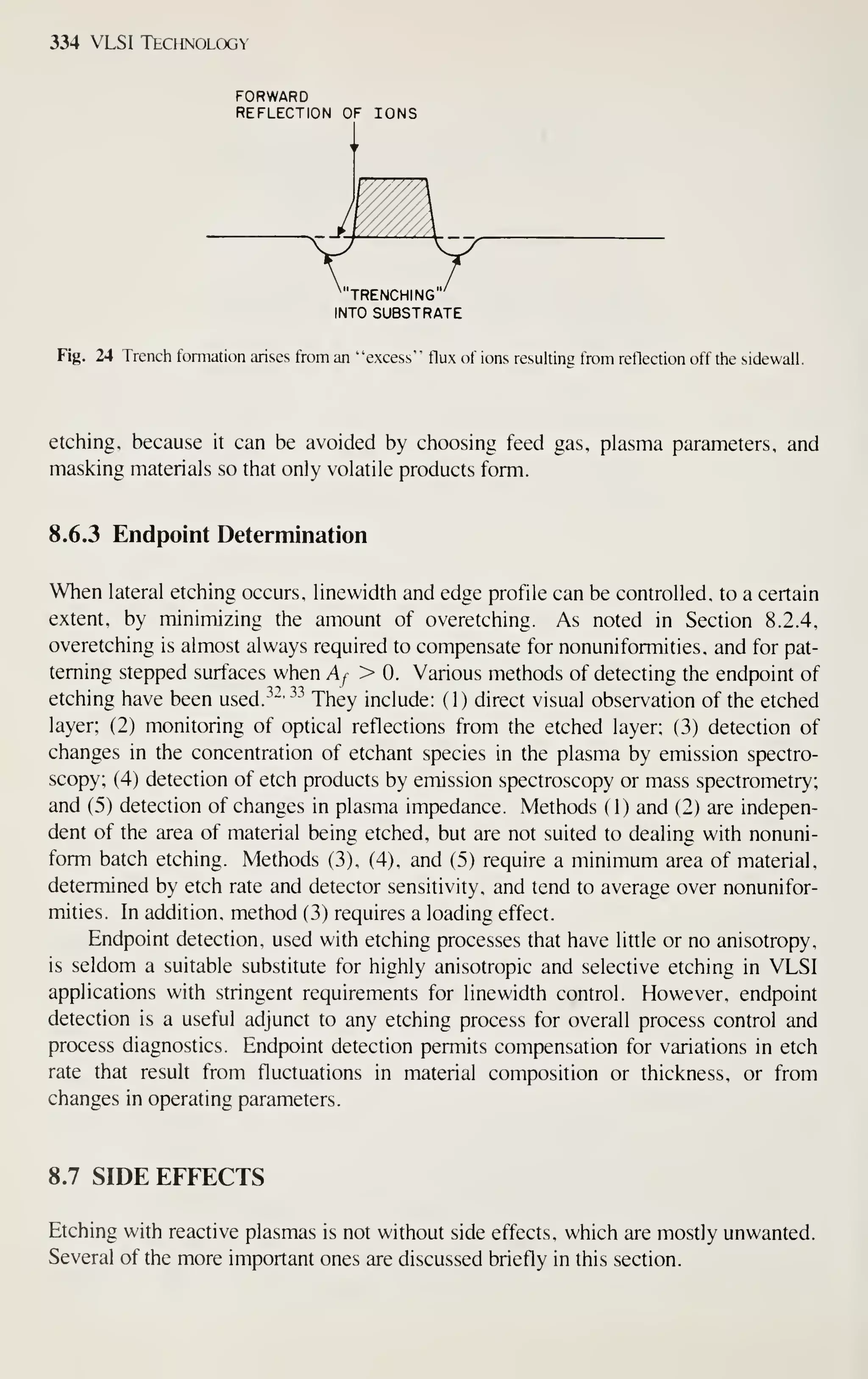

![Crystal Growth and Wafer Preparation 49

[52] Semiconductor Equipment and Materials Institute (SEMI), Mountain View, California.

[53] The American Society for Testing and Materials (ASTM), Committee F-1 on Electronics, Philadel-

phia, Pennsylvania.

[54] H. Robbins and B. Schwartz, "Chemical Etching of Silicon," J. Electrochem. Soc, 106, 505 (1959);

107, 108(1960); 108, 365 (196ir; and 123, 1909(1976).

[55] W. Kern, "The Chemical Etching of Semiconductors," RCA Rev., 39, 278 (1978).

[56] I. Barycka, H, Teterycz, and Z. Znamirowski, "Sodium Hydroxide Solution Shows Selective Etching

of Boron-Doped Silicon," J. Electrochem. Soc. 126, 345 (1979).

[57] W. A. Baylies, "A Review of Flatness Effects in Microlithographic Technology," Solid State Tech-

noi.lA. 132(1981).

[58] A. C. Bonara, "Flex-Mount Polishing of Silicon Wafers," Solid State Technol.. 20, 55 ( 1977).

[59] C. W. Pearce and V. J. Zaleckas, "A New Approach to Lattice Damage Gettering," J. Electrochem.

Soc, 126, 1436(1979).

[60] K. Yamamoto, S. Kishino, Y. Matsushita, and T. Lizuka, "Lifetime Improvement in Czochralski-

Grown Silicon Wafers by the Use of aTwo Step Annealing," .4/7/?/. Phys. Lett., 36, 195 (1980).

[61] L. E. Katz, C. W. Pearce, and P. F. Schmidt, "Neutron Activation Study of a Gettering Treament for

CZSilkon Substrates," J. Electrochem. Soc, 128,620(1981).

[62] M. Ogino, T. Usami, and M. Watanabe, "Microdefects Due to Oxygen Precipitates and Their Appli-

cation to CMOS LSI and CCD Sensor," Electrochem. Soc. Extended Abstracts, 80-2, Abs. 435

(1980).

[63] B. Leroy and C. Plougoven, "Warpage of Silicon Wafers," J. Electrochem. Soc, 127, 961 (1980).

[64] P. F. Schmidt and C. W. Pearce, "A Neutron Activation Analysis Sttjdy of the Sources of Transistion

Group Metal Contamination in the Silicon Device Manufacturing Process," J. Electrochem. Soc,

128,630(1981).

PROBLEMS

1 Iron is an impurity in quartz crucibles. Using a concentration value of 2 x lO'^ /cnr' in the crucible,

assume 300 cm-' of the crucible is dissolved into a 6500-g melt, all at the beginning of the cycle. Calculate

the seed (0% solidified) and tang end (90% solidified) iron concentration in the ingot.

2 Using the equation governing crystal growth (Eq. 6), derive an expression relating growth rate inversely

to crystal diameter. Assume no temp)erature gradient in the melt. Since the heat flow down the crystal is

small, assume heat flow from the crystal is predominantly from radiation.

3 Calculate the number of gallons of HF and HNO3 acid needed to remove the work damage from 5000

wafers of 100-mm diameter.

4 The seed crystal used in CZ growing is usually "necked down" to a small diameter (3 mm) as a means to

initiate dislocation-free growth. Using the yield strength of silicon, calculate the maximum mass of silicon

that could be supported by such a seed. Convert this to a length for 100- and 1 25-mm-diameter crystals.

5 Large growers, such as that pictured in the chapter, require 120 kWh to convert a kilogram of polysilicon

into a crystal. Account for this energy in terms of the energy needed to melt the silicon, the radiation loss

fiom the melt surface, and conduction down the crystal. Is all the energy accounted for? Assume that a 10-

kg charge of polysilicon is used to grow a 10-cm-diameter crystal from a 25-cm-diameter crucible at a rate of

0.0025 cm/s.

6 Solar cells have been suggested as an alternative energy source. Conduct the following feasibility calcula-

tion: How much polysilicon would be required to supply all the United States' electrical needs from 100-

mm-diameter Czochralski-grown silicon wafers, and how much land area would this require? Compare the

silicon used to current consumption. Use the following data:

1

.

The average U.S. weekly power consumption is 42 x lO' kWh.

2. Assume that each gram of silicon in the finished cell required 5 g of polysilicon.

3. The average solar energy falling on the earth's surface is 1340 W/m"; assume 50 h of daylight per

week.

4. The cell will convert 8% of all incident energy to electrical power.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-69-2048.jpg)

![68 VLSI Technology

As in oxidation, diffusion, and LPCVD processes, wafers are cleaned before the

expitaxy process begins. All organic and metallic residues on the wafers must be

removed.^^ Particles are removed by using ultrasonic agitation in the cleaning baths,

by brush scrubbing with water, or by high-pressure water jets. Clean wafers must be

handled carefully to prevent recontamination, especially by particles. To prevent par-

ticle contamination, the entire reactor or load station is usually installed in a clean

room. A second method is to use a clean-air hood at the loading station.

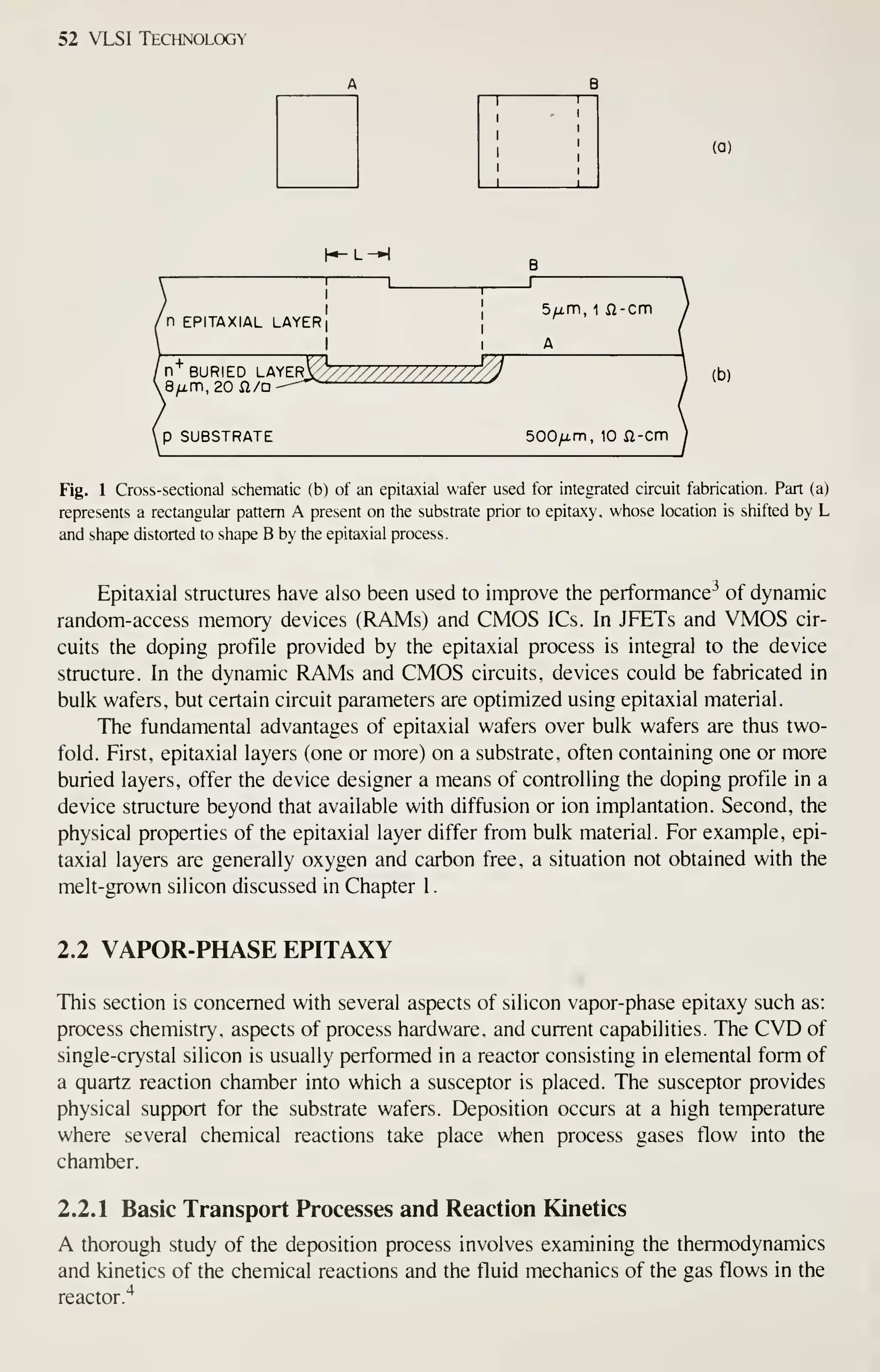

2.2.5 Buried Layers

To fabricate bipolar ICs, usually one or more diffusions are applied to the substrate to

create the necessary isolation, collector, emitter, or base functions (Fig. 1). These dif-

fusions are applied to the substrate prior to epitaxy using the lithographic, oxidation,

diffusion, or ion-implantation processes discussed in other chapters. The diffusions

are called buried layers or diffusions under film. The presence of a buried layer com-

plicates the epitaxial process because of its effect on autodoping (vertical and lateral),

defects, pattern shifting, and pattern distortion.

The pre-epitaxial process leaves a step of 500 to 1000 A around the perimeter of

the buried layer that marks its location (A of Fig. 1). Subsequent masking levels must

be properly aligned with the buried layer pattern. Unfortunately, the deposition pro-

cess shifts the pattern (B of Fig. lb). Lithographic masks must compensate for the

amount of the shift (L of Fig. lb). A separate but related effect is pattern distortion or

washout, which alters the shape of the feature in the layer. Figure la also illustrates

the nature of pattern distortion. The pattern in the epitaxial layer is thus misplaced and

15 -

o 10

•

o

DATA

INTERPOLATED

EPITAXIAL THICKNESS ( f^m)

-

15

-

13

-

^1

-

9

- 7

-

M/^''^

-

1 1 1

5 -

30 60

SURFACE ORIENTATION

[minutes of arc off <100>]

Fig. 17 Pattern shift for a (100) orientation with various amounts of misorientation. (A.fxer Drum and Clark,

Ref. 37.)](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-88-2048.jpg)

![Epitaxy 69

misshaped relative to its original configuration in the substrate. These effects place

limitations on the design of high-density circuits, and are a complicated function of

substrate orientation, growth rate and temperature, and silicon source.

^^

The crystal orientation has a profound effect on pattern shift.

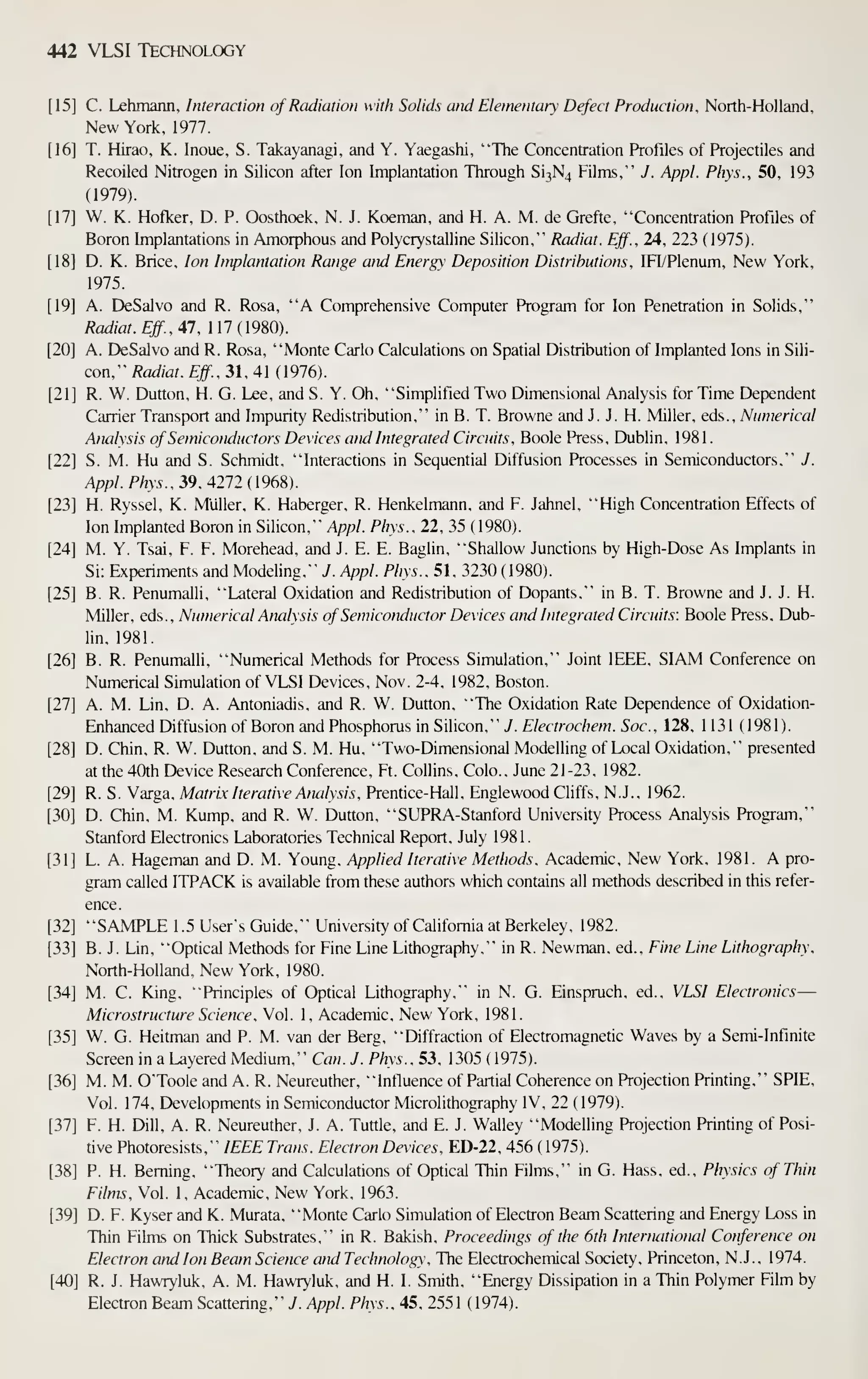

-^^

Since the layer

does not grow normal to the substrate but rather by additions to microsteps (Fig. 9),

the macrostep marking the diffusion is shifted. As a result the microscopic growth

processes are altered by the orientation of the wafer. Current practice is to misorient

(1 1 1) wafers by 2 to 5° towards the nearest (1 10) direction and to orient (100) wafers

exactly on the orientation. Figure 17 illustrates the (100) case; note that the pattern

shift changes with epitaxial thickness. As shown in Fig. 18, pattern shift is indepen-

dent of reactor design, ^^^

but does show a pronounced dependence on growth rate and

VERTICAL GEOMETRY

ORIENTATION <111>

DEPOSITION RATE

o 1 0|im/min

5/j.m/min

/im/min

m /min

1000 1100 1200

3-

2-

1

-

0_

HORIZONTAL GEOMETRY

1000 1100 1200

3-

2-

cn 1 _

CYLINDRICAL GEOMETRY

1000 1100 1200

TRUE TEMPERATURE (°C)

- (a)

(b)

- (C)

Fig. 18 Pattern shift as a function of reactor [(a) vertical, (b) horizontal, and (c) cylindrical (or barrel)],

temperature, and growth rate. (After Lee etal., Ref. 38.)](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-89-2048.jpg)

![Epitaxy 81

106

105 -

103 —

10'

"1 I I I I

r I

I I

1

r

J I u

—

o

o-

_l I L.

10 20

PREHEAT TIME OF SUBSTRATE (min)

Fig. 30 The dependence of film quality on predeposition heating time. (After Sugiura and Yamaguchi, Ref.

53.)

CVl 10

E

GROWTH TEMPERATURE (°C)

6 800 700

'

1 1

1

1

600

ti- 10-

en

z

t 10^ I-

en

2

LlI

Q

Z

H 10^ -

<

o

o

_l

en

10'

E= 3.5 ev

^ll

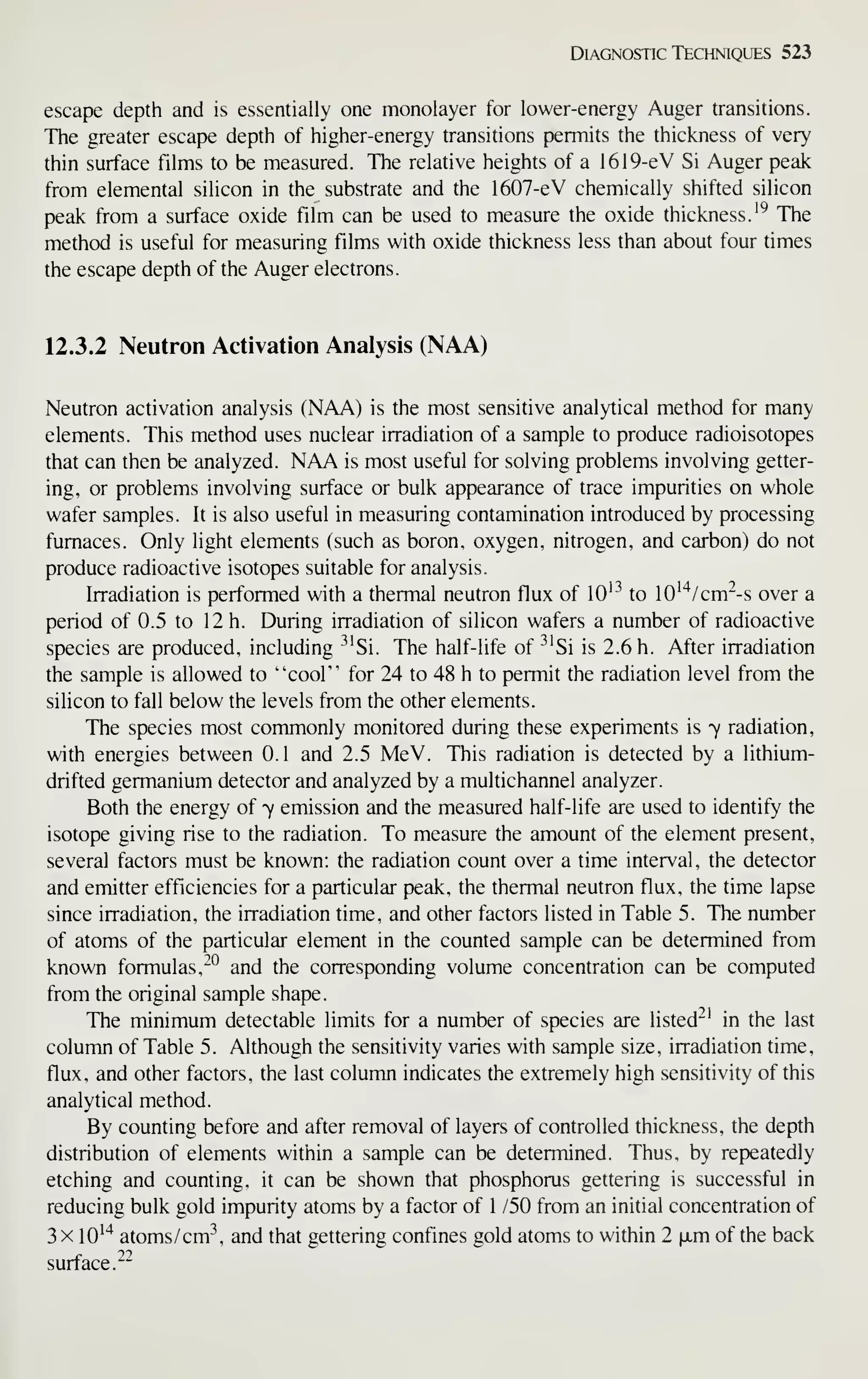

'

I I I I I I I I I I I I I I 1 I I I I ] I 1

0.9 1.0 1.1

10^ /T(K)

Fig. 31 The dependence of film perfection on growth temperature. (After Sugiura and Yamaguchi, Ref.

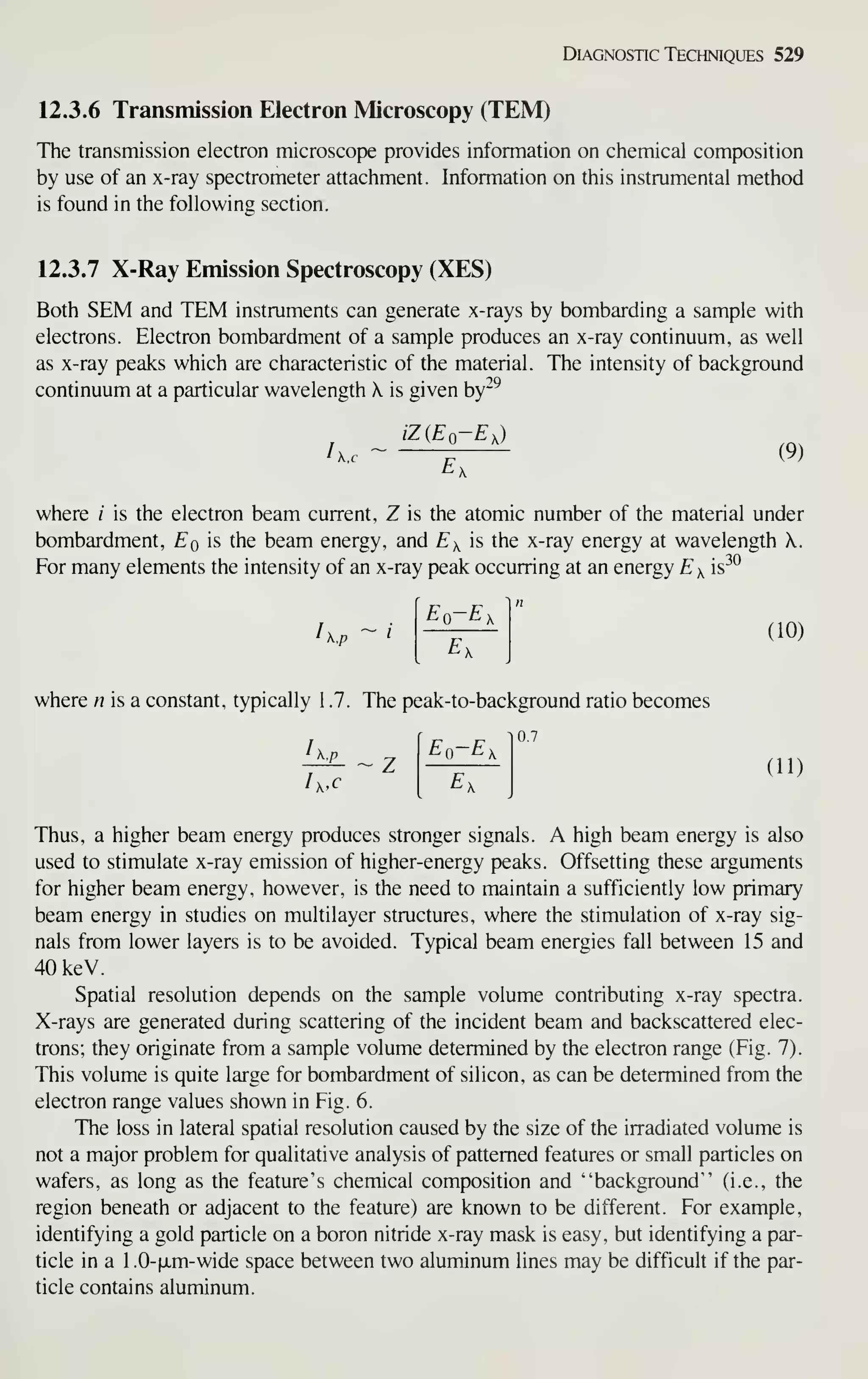

53.)](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-101-2048.jpg)

![88 VLSI Technology

2.5.4 Lifetime

The lifetime of minority carriers is generally not a consideration in structures intended

for IC fabrication, but could be of interest in some devices such as dynamic RAMs.

Several measurements involving the transient response of diodes or MOS capacitors

are applicable to epitaxial layers.

^^'^-^

However, the diffusion length of carriers is

often many times that of the layer thickness. This complicates the interpretation of the

measurement results.

2.6 SUMMARY AND FUTURE TRENDS

Epitaxy as a process will remain integral to circuit manufacture. It offers doping pro-

files and material properties not obtainable otherwise. Homoepitaxial silicon struc-

tures will remain popular design choic in the foreseeable future. The advantages of

SOI technologies are compelling for h h-density and high-speed circuits. In particu-

lar, if silicon-on-Si02 can be perfected, it will offer the advantages of SOS without

the problems. Lateral-seeded SOI will undoubtedly receive considerable research

attention. MBE would be advantageous in fully ion-implanted VLSI circuits in which

the total thermal cycle is minimized so that the doping capabilities of MBE can be

exploited.

Although presently available equipment is adequate for most needs, several

aspects of the epitaxial process could be improved. In keeping with automation else-

where in the fabrication process, an autoloading epitaxial reactor remains a desirable

objective. This equipment could take the form of a cassette-fed machine processing a

single wafer at a time. Conceptually, a uniwafer reaction chamber could be optim-

ized for temperature and gas flows to produce wafers having exceptional uniformity.

The throughput of epitaxial reactors is less than that of LPCVD processes (Chapter 3)

by a factor of 5 to 10. However, monocrystalline silicon cannot be grown in LPCVD

equipment. One difficulty is the low growth rates in the usual LPCVD temperature

ranges (Fig. 8). An alternative reactor design, ^"^

termed the rotary disc, is similar in

load configuration to LPCVD equipment, and offers high capacity and efficiency.

Large-scale use of MBE will require equipment with throughputs comparable to

present-day epitaxial reactors.

Although epitaxial processes are well characterized and understood, the trend to

thinner layers for bipolar and unipolar ICs will result in incremental process improve-

ments and the continued study of autodoping effects. Additionally, contamination,

responsible for precipitates in epitaxial layers, needs to be reduced commensurate

with the requirements of VLSI devices. Contamination-free epitaxy will be a

worthwhile process improvement.

REFERENCES

[1] H. C. Theuerer et al., "Epitaxial Diffused Transistors," Proc. IRE. 48, 1642 (1960).

[2] F. E. Holmes and C. A. T. Salama, "VMOS—A New MOS Integrated Circuit Technology," Solid

State Electron . , 1 7 , 79 1 ( 1 974)

.

[3] D. S. Yaney and C. W. Pearce, "The Use of Thin Epitaxial Layers for MOS VLSI," Proceedings of

the 1981 International Electron Device Meeting , IEEE, 1981, p. 236.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-108-2048.jpg)

![Epitaxy 91

[58] M. S. Abrahams and C. J. Buiocchi, "Cross-Sectional Electron Microscopy of Silicon on Sapphire,"

Appl. Phys. Lett.. 27, 325 (1975).

H. Schlotter, "Interface Properties of Sapphire and Spinel." J. Vac. Sci. Technol.. 13, 29 (1976).

Y. Kobayaski. T. Suzuki, and M. Tamura. "Improvement of Crystalline Quality of SOS with Laser

hradiation Techniques." y/?«. J. Appl. Phys.. 20. L249 ( 1981).

G. A. Sai-Halar. F. F. Fang. T. O. Sedgwick, and A. Segmuller. "Stress-Relieved Regrowth of Sili-

con on Sapphire by Laser Annealing." Appl. Phys. Lett.. 36. 419 (1980).

K. Shibata. T. Inoue. and T. Takigawa. "Grain Growth of Polycr}'stalline Silicon Films on SiOi by

CW Scanning Electron Beam Annealing." Appl. Phys. Lett.. 39. 645 (1981).

D. K. Biegelsen, N. M. Johnson, D. J. Bartelink, and M. D. Moyer, "Laser-Induced Crystallization

of Silicon Islands on Amorphous Substrates: Multilayer Structures," Appl. Phys. Lett., 38, 150

(1981).

R. A. Lemons and M. A. Bosch, "Periodic Motion of the Crystallization Front during Beam Anneal-

mg of Si Films," Appl. Phys. Lett.. 39, 343 ( 1981).

B-Y. Tsuar, J. C. C. Fan, M. W. Geis, D. J. Silversmith, and R. W. Mountain, "Improved Tech-

niques for Growth of Large Area Single Crystal Si Sheets over Si02 Using Lateral Epitaxy by Seeded

Solidification," /V'P/- Phys. Lett.. 39, 561 ( 1981).

T. I. Kamins and P. A. Pianetta, "MOSFETs in Laser-Recrystallized Polysilicon on Quartz," IEEE

Electron. Dex'ice Lett., EDL-1, 214 (1980).

B-Y. Tsuar, M. W. Geis. J. C. C. Fan. D. J. Silversmith, and R. W. Mountain, "N-Channel Deep-

Depletion Metal-Oxide Semiconductor Transistors Fabricated in Zone-Melting-Recrystallized Polycry-

stalline Si Films m SiO. ," Appl. Phys. Lett.. 39, 909 ( 1981 ).

P. H. Langer and C. W. Pearce, "Epitaxial Resistivity," J. Test. Eval.. 1, 305 (1973).

Am. Soc. Test. Mater.. ASTM Standard, F95, Part 43.

K. Sato, Y. Ishikawa, and K. Sugawara, "Infrared Interference Spectra Observed in Silicon Epitaxial

Wafers." Solid State Electron.. 9. 771 (1966).

Am. Soc. Test. Mater.. ASTM Standard. F143. Part 43.

Am. Soc. Test. Mater.. ASTM Standard. Fl 10. Part 43.

National Bureau of Standards. Special Publication 400-10. "Spreading Resistance Symposium,"

December 1974.

Y. Isda. H. Abe. and M. Kondo. "Impurity Profile Measurements of Thin Epitaxial Wafers by Mul-

tilayer Spreading Resistance Analysis." i. Electrochem.Soc. 124. 1118(1977).

D. L. Rehrig and C. W. Pearce, "Production Mercury Probe Capacitance-Voltage Testing," Sem-

icond.Int..2. 151 (1980)

Am. Soc. Test. Mater.. ASTM Standard. F374. Part 43.

M. G. Buehler, "Peripheral and Diffused Layer Effects on Doping Profiles," IEEE Trans. Electron

Devices.ED-l9, nil (1912).

J. A. Copeland, "Diode Edge Effect on Doping-Profile Measurements," IEEE Trans. Electron Dev-

ices , ED-ll , 404 (1910)

.

P. J. Severin and G. J. Poodt. "Capacitance-Voltage Measurements with a Mercury-Silicon Diode,"

J. Electrochem. Soc. 1 19. 1384 ( 1972).

I. Amron, "Errors in Dopant Concentration Profiles Determined by Differential Capacitance Measure-

ments." Electrochem. Technol.. 5, 94 ( 1967).

D. G. Schimmel, "A Comparison of Chemical Etches for Revealing (100) Silicon Crystal Defects," J.

Electrochem. Soc. 123. 734(1976).

P. G. Wilson. "Recombination in P-I-N Diodes," Solid State Electron., 10, 145 (1967).

K. H. Zaininger and F. P. Herman, "The C-V Technique as an Analytical Tool," Solid State Tech-

nol.. 13,46(1970).

[84] V. S. Ban and E. P. Miller, "A New Reactor for Silicon Epitaxy," Proceedings of the 7th Interna-

tional Conference on Chemical Vapor Deposition 1979, Electrochem. Soc., 1979, p. 102.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-111-2048.jpg)

![126 VLSI Technology

VLSI devices with very small dimensions require precise lithography, pattern

transfer with anisotropic etching, and very shallow junctions. These conditions

impose new requirements on the film deposition process. The major requirements are

low processing temperatures to prevent movement of the shallow junctions, confor-

mal step coverage over the anisotropically etched features, low process-induced

defects (mainly particles generated during wafer handling and loading), and high

wafer throughput to reduce cost. These requirements are met by hot-wall, low-

pressure depositions (chemical or plasma). The reactors for this type of deposition are

easily scaled to accommodate 125- or 150-mm wafers. In contrast, atmospheric-

pressure depositions and physical-deposition techniques are much more difficult to

scale and do not have the high throughput or the low defect densities. Consequently

these techniques are being replaced by LPCVD and plasma-assisted depositions as

critical device dimensions decrease and wafer size increases.

Low-temperature depositions will continue to increase in importance, because the

maximum processing temperature for devices with shallow junctions is about 900 to

950°C. Depositions at very low temperatures, 30 to 200°C, have been investigated

and they will probably find applications in new device technologies. These low-

temperature techniques include plasma-assisted depositions of organosilicon com-

pxDunds and photo-induced depositions of silicon dioxide and silicon nitride. The

photo-induced reactions occur at about 100°C and introduce almost no radiation dam-

age in devices.

REFERENCES

[1] W. Kern and V. S. Ban, "Chemical Vapor Deposition of Inorganic Thin Films," in J. L. Vossen and

W. Kern, Eds., Thin Film Processes. Academic, New York, 1978. pp. 257-331.

[2] W. Kern and G. L. Schnable, "Low-Pressure Chemical Vapor Deposition for Very Large- Scale

Integration Processing—A Review," IEEE Trans. Electron Devices. ED-26, 647 ( 1979).

[3] E. C. Douglas, "Advanced Process Technology for VLSI Circuits," Sold State Technol., 24, 65 (May

1981).

[4] J. L. Vossen and W. Kern, "Thin-Film Formation," Phys. Today, 33, 26 (May 1980).

[5] M. L. Hammond, "Introduction to Chemical Vapor Deposition," Solid State Technol., 22, 61

(December 1979).

[6] M. L. Hammond, "Safety in Chemical Vapor Deposition," Solid State Technol., 23, 104 (December

1980).

[7] R. S. Rosier, "Low Pressure CVD Production Processes for Poly, Nitride, and Oxide," Solid State

Technol., 20, 63 (April 1977).

[8] W. A. Brown and T. I. Kamins, "An Analysis of LPCVD System Parameters for Polysilicon, Silicon

Nitride and Silicon Dioxide Deposition," Solid State Technol., 22, 51 (July 1979).

[9] R. J. Gieske, J. J. McMullen, and L. F. Donaghey, "Low Pressure Chemical Vapor Deposition of

Polysilicon," in L. F. Donaghey, P. Rai-Choudhury, and R. N. Tauber, Eds., Chemical Vapor

Deposition—Sixth International Conference, Electrochemical Society, Princeton, N.J., 1977, pp.

183-194.

[10] M. L. Hitchman, "Kinetics and Mechanism of Low Pressure CVD of Polysilicon," in T. O.

Sedgwick and H. Lydtin, Eds., Chemical Vapor Deposition —Seventh International Conference. Elec-

trochemical Society, Princeton, N.J., 1979, pp. 59-76.

[11] W. A. Bryant, "The Kinetics of the Deposition of Silicon by Silane Pyrolysis at Low Temperatures

and Atmospheric Pressure," Thin Solid Films, 60, 19 (1979).](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-146-2048.jpg)

![Dielectric and Polysilicon Film Deposition 127

12] C. H. J. Van Den Brekel and L. J. M. Bollen. "Low Pressure Deposition of Polycrystalline Silicon

from Silane." y. Cnst. Growth. 54. 310 (1981).

13] F. C. Eversteyn and B. H. Put. "'Influence of ASH3. PH3. and B^H^, on the Growth Rate and Resis-

tivity of Polycrystalline Silicon Films Deposited from a SiH;

—

Ht Mixture," J. Electrochem. Soc,

120.106(1973).

14] T. I. Kamins, M. M. Mandurah. and K. C. Saraswat, "Structure and Stability of Low Pressure Chem-

ically Vapor-Deposited Silicon Films," 7. Electrochem. Soc, 125. 927 ( 1978).

15] T. I. Kamins. "Structure and Properties of LPCVD Silicon Films." J. Electrochem. Soc, 127. 686

(1980).

16] Y. Wada and S. Nishimatsu. "Grain Growth Mechanism of Heavily Phosphorus-Implanted Polycrys-

talline Silicon," 7. f/mroc/Tew. Soc. 125. 1499(1978).

17] T. 1. Kamins. "Resistivity of LPCVD Polycrystalline-Silicon Films," J. Electrochem. Soc, 126, 833

(1979).

18] M. M. Mandurah, K. C. Saraswat, and T. 1. Kamins, "Phosphorus Doping of Low Pressure Chemi-

cally Vapor-Deposited Silicon Films," J. Electrochem. Soc, 126, 1019 (1979).

19] M. M. Mandurah, K. C. Saraswat, C. R. Helms, and T. I. Kamins, "Dopant Segregation in Polycrys-

talline Silicon," J. Appl. Phys.. 51 , 5755 ( 1980).

20] T. I. Kamins, J. Manoliu, and R. N. Tucker, "Diffusion of Impurities in Polycrystalline Silicon," J.

Appl. Phys.. 43.^3 (1912).

21] D. J. Coe, "The Lateral Diffusion of Boron in Polycrystalline Silicon and its Influence on the Fabrica-

tion of Sub-Micron MOSTS," Solid State Electron., 20, 985 (1977).

22] T. 1. Kamins, "Hall Mobility in Chemically Deposited Polycrystalline Silicon," J. Appl. Phys., 42,

4357(1971).

23] S. Horiuchi, "Electrical Characteristics of Boron Diffused Polycrystalline Silicon Layers," Solid State

Electron., 18,659(1975).

24] G. Yaron, "Characterization of Phosphorus Implanted Low Pressure Chemical Vapor Deposited

Polycrystalline Silicon," Solid State Electron., 22, 1017 (1979).

25] M. Kuisl and W. Langheinrich, "Preparation and Properties of Phosphorus-Doped Polycrystalline Sil-

icon Films," in J. M. Blocher, Jr., H. E. Hintermann, and L. H. Hall, Eds., Chemical Vapor

Deposition —Fifth International Conference, Electrochemical Society. Princeton, N.J., 1975, pp.

380-389.

26] T. I. Kamins. "Oxidation of Phosphorus-Doped Low Pressure and Atmospheric Pressure CVD

Polycrystalline-Silicon Films." J. Electrochem. Soc, 126. 838 ( 1979).

27] B. G. Bagley, D. E. Aspnes, A. C. Adams, and C. J. Mogab, "Optical Prop)erties of Low-Pressure

Chemically Vapor Deposited Silicon Over the Energy Range 3.0-6.0 eV," Appl. Phys. Lett., 38, 56

(1981).

28] Ch. Kuhl, H. Schlotterer, and F. Schwidefsky, "Optical Investigation of Different Silicon Films," J.

Electrochem. Soc. 121, 1496(1974).

29] M. Hirose, M. Taniguchi, and Y. Osaka, "Electronic Properties of Chemically Deposited Polycrystal-

line Silicon," 7. Appl. Phys., 50, 377 (1979).

30] W. Kern and R. S. Rosier, "Advances in Deposition Processes for Passivation Films," J. Vac Sci.

Technol., 14, 1082(1977).

31] R. E. Logar, M. T. Wauk, and R. S. Rosier, "Low Pressure Deposition of Phosphorus-Doped Silicon

Dioxide at 400°C in a Hot Wall Furnace," in L. F. Donaghey. P. Rai-Choudhury, and R. N. Tauber,

Eds., Chemical Vapor Deposition—Sixth International Conference, Electrochemical Society, Prince-

ton, N.J. , 1977, pp. 195-202.

32] H. Huppertz and W. L. Engl, "Modeling of Low-Pressure Deposition of SIOt by Decomposition of

TEOS," IEEE Trans. Electron Devices, ED-26, 658 ( 1979).

33] A. C. Adams and C. D. Capio, "The Deposition of Silicon Dioxide Films at Reduced Pressure," J.

Electrochem. Soc, 126, 1042(1979).

34] K. Watanabe, T. Tanigaki, and S. Wakayama, "The Properties of LPCVD SiOj Film Deposited by

SiH^Cl, and N^O Mixtures," J. Electrochem. Soc, 128, 2630 (1981).

35] M. Maeda and H. Nakamura, "Deposition Kinetics of Si02 Film," J. Appl. Phys., 52, 6651 (1981).](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-147-2048.jpg)

![128 VLSI Technology

[36] M. Shibata, T. Yashimi, and K. Sugawara, "Deposition Rate and Phosphorus Concentration of Phos-

phosilicate Glass Films in Relation to PH3/SiH4+PH3 Mole Fraction." J. Electrochem. Soc, 122,

157(1975).

[37] P. J. Tobin, J. B. Price, and L. M. Campbell, "Gas Phase Composition in the Low Pressure Chemical

Vapor Deposition of Silicon Dioxide." J. Electrochem. Soc. 127. 2222 (1980).

[38] A. C. Adams and C. D. Capio. "Planarization of Phosphorus-Doped Silicon Dioxide," J. Electro-

chem. Soc, 128,423(1981).

[39] W. A. Pliskin, "Comparison of Properties of Dielectric Films Deposited by Various Methods." J.

Vac. Sci. Techiol., 14, 1064 (1977).

[40] A. C. Adams and S. P. Murarka, "Measuring the Phosphorus Concentration in Deposited Phosphosili-

cate Fihns," J. Electrochem. Soc, 126, 334 (1979).

[41] K. Chow and L. G. Garrison, "Phosphorus Concentration of Chemical Vapor Deposited Phosphosili-

cate Glass," J. Electrochem. Soc, 124, 1133 (1977).

[42] A. C. Adams, D. P. Schinke, and C. D. Capio, "An Evaluation of the Prism Coupler for Measuring

the Thickness and the Refractive Index of Dielectric Films on Silicon Substrates," J. Electrochem.

Soc, 126, 1539(1979).

[43] N. Nagasima, "Structure Analysis of Silicon Dioxide Films Formed by Oxidation of Silane," J. Appl.

P/m.. 43, 3378(1972).

[44] J. A. Appels, E. Kooi, M. M. Paffen, J. J. H. Schatorje, and W. H. C. G. Verkuylen, "Local Oxida-

tion of Silicon and its Application in Semiconductor Device Technology," Philips Res. Rep.. 25, 118

(1970).

[45] P. S. Peercy, H. J. Stein, B. L. Doyle, and S. T. Picraux, "Hydrogen Concentration Profiles and

Chemical Bonding in Silicon Nitride," J. Electron. Mat.. 8, 1 1 (1979).

[46] J. V. Dalton and J. Drobek. "Structure and Sodium Migration in Silicon Nitride Films," J. Electro-

chem. Soc 115,865(1968).

[47] J. R. Hollahan and R. S. Rosier, "Plasma Deposition of Inorganic Thin Films," in J. L. Vossen and

W. Kern, Eds., Thin Film Processes. Academic, New York, 1978, pp. 335-360.

[48] M. J. Rand, "Plasma-Promoted Deposition of Thin Inorganic Films," J. Vac Sci. Technol.. 16, 420

(1979).

[49] H. Dun, P. Pan, F. R. White, and R. W. Douse, "Mechanisms of Plasma-Enhanced Silicon Nitride

Deposition Using SiH4/N2 Mixture," J. Electrochem. Soc, 128, 1555 (1981).

[50] A. C. Adams, F. B. Alexander, C. D. Capio, andT. E. Smith, "Characterization of Plasma-Deposited

Silicon Dioxide," J. Electrochem. Soc, 128, 1545 (1981).

[51] W. A. Lanford and M. J. Rand, "The Hydrogen Content of Plasma-Deposited Silicon Nitride," J.

Appl. Phys.. 49. 2414 (I9m.

[52] A. K. Sinha and T. E. Smith, "Electrical Prof)erties of Si-N Films Deposited on Silicon from Reactive

Plasma," J. Appl. Phys., 49, 2756 (1978).

[53] M. J. Rand and J. F. Roberts, "Silicon Oxynitride Films from the NO—NH3 —SiHj Reaction," J.

Electrochem . 5oc. , 1 20, 446 ( 1 973)

.

[54] A. K. Gaind and E. W. Heam, "Physiochemical Properties of Chemical Vapor-Deposited Silicon

Oxynitride from a SiH4—C02—NH3—H2 System," y. Electrochem. Soc, 125. 139(1978).

PROBLEMS

1 Find the empirical formula for plasma silicon nitride containing 25 at. % H and having a Si/N ratio of 1 . 1

.

Find the empirical formula for LPCVD silicon nitride containing 5 at. % H and having a Si/N ratio of 0.75.

2 If plasma-deposited Si02 contains 3 x 10^' H/cm^, find the at. % H and the empirical formula.

3 If the average chlorine concentration within the first 1000 A of a deposited Si02 is 1 x lO'^ Cl/cm^, what

is the at. % CI in this region?

4 Derive the relationship between wt. % B, at. % B, and mol % B2O3 for boron-doped Si02.

5 A polysilicon deposition uses 30 % silane in nitrogen at 625°C and 53.3 Pa (0.4 Torr). The total gas flow

is 500 std. cm^/min. The volume of the LPCVD reactor is 20 L, its length is 150 cm, and a cross-sectional](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-148-2048.jpg)

![134 VLSI Technology

and

C* = Hpc (5)

where Co is the equiUbrium concentration in the oxide at the outer surface, C* is the

equihbrium bulk concentration in the oxide, p^ is the partial pressure in the gas adja-

cent to the oxide surface, pc is the partial pressure in the bulk of the gas, and H is

Henry's law constant. Using Henry's law along with the ideal gas law ^ allows us to

rewrite Cq and Cc

Cg = -r^ (6a)

kT

Ps_

kT

Ps

Cs = ^ (6b)

Combining Eqs. 3 to 6 gives

F, - h{C* - Co) (7)

where h is the gas-phase mass-transfer coefficient in terms of concentration in the

solid, given by h = Hq / HkT. When the concentration of the oxidant in the oxide at

the oxide-gas interface Co is less than the equilibrium bulk oxide concentration, F is

positive. Oxidation is a nonequilibrium process with the driving force being the devi-

ation of concentration from equilibrium.^ Henry's law is valid only in the absence of

dissociation effects at the gas-oxide interface. This implication is that the species

moving through the oxide is molecular.

The flux of this oxidizing species across the oxide is taken to follow Pick's law

^2= -D ^ (8)

da

at any point d in the oxide layer. D is the diffusion coefficient and dC / dd is the con-

centration gradient of the oxidizing species in the oxide. Following the steady-state

assumption, F2 must be the same at any point within the oxide (i.e., dFj/dd =0)

resulting in

^(Co - Q)

F2 = -^-^, (9)

do

where C, is the oxidizing species concentration in the oxide adjacent to the oxide-

silicon interface and do is the oxide thickness.

Assuming that the flux corresponding to the Si-Si02 interface reaction is propor-

tional to C,

F3 = k,Ci (10)

where k^ is the rate constant of chemical surface reaction for silicon oxidation.

After setting F] = Fj = Ft,, as dictated by steady-state conditions, and solving

simultaneous equations, we obtain the following expressions for C, and Co:](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-154-2048.jpg)

![162 VLSI Technology

TEMPERATURE (°C)

1200 1150 1100

"T

0.64 0.66 0.68 0.70

lO'/T (K-l)

0.72 0.74

Fig. 16 Growth of oxidation-induced stacking faults versus temperature; for 3 h of dry oxidation. (After

Hu.Ref.62.)

responsible for stacking fault growth. Equation 23 is a proposed model^' in which the

oxidation rate is the controlling parameter in oxidation stacking fault length.

dt

K,

dT,

dt

K, (23)

where / is the stacking fault length, Tq^ is the oxide thickness, t is the time, n is the

power dependence, .^i is related to the growth mechanism and defect generation at

the Si-Si02 interface, and K2 is related to the retrogrowth mechanism. Applying this

equation to experimental data gives values for n, K], and Kj- A 0.4th power depen-

dence is observed. ^^ This less-than-linear dependence of oxidation stacking fault

growth rate on the oxidation rate means that smaller stacking faults will result for a

higher oxidation rate at the same temperature for the same oxide thickness. This, of

course, is the case with high-pressure oxidation where the oxidation rate is increased.

Figure 17 shows an experimental result for a 950 to 1 100°C temperature range at both

1- and 6.4-atm pressure.^ The above results confirm the proposed model. Additional

results^^ at 700°C and 20-atm pressure show complete stacking fault suppression for

all thicknesses studies (up to 5 [xm). Preexisting stacking faults tend to grow during](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-182-2048.jpg)

![Oxidation 165

REFERENCES

[1] M. M. Alalia. "Semiconductor Surfaces and Films; the Si-SiOi System."' Properties of Elemental and

Co/npound Semiconductors. H. Gatos, Ed.. Interscience. New York. 1960. Vol. 5. pp. 163 — 181.

P. J. Jorgensen. "Effect of an Electric Field on Silicon Oxidation." J. Chem Phys.. 37, 874 (1962).

J. R. Ligenza and W. G. Spitzer. "The Mechanisms for Silicon Oxidation in Steam and Oxygen." J.

Phys. Chem. Solids. 14. 131 (1960).

B. E. Deal and A. S. Grove. "General Relationship for the Thermal Oxidation of Silicon." J. Appl.

Phys.. ^6. 3170 (1965).

A. S. Grove. Physics cmd Technology of Semiconductor Devices. Wiley. New York. 1967, Chapter 2.

E. H. .NicoUian and J. R. Breuws. MOS Physics and Technology. Wiley. New York. 1982.

U. R. Evans. "The Relationship Between Tarnishing and Corrosion." Trans. Electrochem. Soc, 46.

247(1924).

P. S. Flint. "The Rates of Oxidation of Silicon." Abstract 94. The Electrochem. Soc. Extettded Abs..

Spring Meeting. Los Angeles. .May 6- 10. 1962.

R. H. Doremus. "Oxidation of Silicon by Water and Oxygen and Diffusion in Fused Silica." J. Pins.

Chem.. m.113 (1916).

J. Blanc, "A Revised Model for the Oxidation of Si by Oxygen." Appl. Phys. Lett.. 33. 424 ( 1978).

T. G. Mills and F. A. Kroger. "Electrical Conduction at Eleated Temp, in Thermally Grown SiO-.

Films." J. Electrochetn. Soc. 120. 1582(1973).

W. A. Tiller. "On the Kinetics of the Thermal Oxidation of Silicon. I. A Theoretical Perspective." J.

Electrochem. Soc. 127. 619 (1980).

W. A. Tiller, "On the Kinetics of the Thermal Oxidation of Silicon. II. Some Theoretical Evalua-

tions," J. Electrochem. Soc, 127, 625 ( 1980).

W. A. Tiller. "On the Kinetics of the Thermal Oxidation of Silicon. III. Coupling With Other Key

Phenomena." J. Electrochem. Soc. 128. 689 ( 1981 ).

R. B. Fair, "Oxidation. Impurity Diffusion, and Defect Growth in Silicon—An Overiev. ." J. Elec-

trochem. Soc. 128. 1361 (1981).

S. M. Hu. "Formation of Stacking Faults and Enhanced Diffusion in the Oxidation of Silicon." J.

Appl. Pins.. 45. 1561 {1914).

F. N. Schuettmann. K. L. Chiang, and W. A. Brown, "Variation of Silicon Dioxide Growth Rate

with Pre-Oxidation Clean," Abstract 276, The Electrochem. Soc. Extended Abs.. Spring Meeting,

Seattle, Washington, May 1978.

E. A. Irene, "Silicon Oxidation Studies: Some Aspects of the Initial Oxidation Regime,"" J. Electro-

chem. Soc, 125, 1708(1978).

E. A. Taft, "The Optical Constants of Silicon and Dr} Oxygen Oxides,"" J. Electrochem. Soc. 125.

968(1978).

C. Hashimoto. S. .Muramoto. N. Shiomo. and O. Nakajima. "A Method of Forming Thin and Highly

Reliable Gate Oxides. ""y.£/mTOf/!£'w.5of.. 127. 129(1980).

A. C. Adams. T. E. Smith, and C. C. Chang. "The Growth and Characterization of Very Thin Silicon

Dioxide Films."" 7. Electrochem. Soc. 127. 1787 ( 1980).

M. Hirayama. H. .Miyoshi. N. Tsubouchi. and H. Abe. "High Pressure Oxidation for Thin Gate Insu-

lator Process."" IEEE Trans. Electron Devices. ED-29. 503 (1982).

J. R. Ligenza. "Effect of Cr>'stal Orientation on Oxidation Rates in High Pressure Steam."" Phys.

Chem.. 65.2011 i96).

W. A. Pliskin. "Separation of the Linear and Parabolic Terms in the Steam Oxidation of Si."" IBM J.

Res.Dev.. 10. 198(1966).

B. E. Deal, "Thermal Oxidation Kinetics of Silicon in PTogenic HiO and 5% HCI/H^O Mixtures,"

J. Electrochem. Soc. 125. 576 ( 1978).

E. A. Irene, "The Effects of Trace Amounts of Water of the Thermal Oxidation of Si in Oxygen,"" J.

Electrochem. Soc, 121, 1613 (1974).

M. M. Atalla and E. Tannenbaum. "Impurity Redistribution and Junction Formation in Silicon by

Thermal Oxidation."" BellSxst. Tech. J.. 39. 933 (1960).](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-185-2048.jpg)

![Oxidation 167

[56] R. B. Fair and J. C. C. Tsai, "Theory and Direct Measurement of Boron Segregation in SiO-i during

Dry. Near Dry and Wet O2 Oxidation." J. Electrochem. Soc. 125. 2050 (1978).

[57] S. P. Murarka. "Diffusion and Segregation of Ion-Implanted Boron in Silicon in Dr>' Oxygen

Ambients." Phys. Rev. B. 12. 2502 ( 1975).

[58] T. I. Kamins. "Oxidation of Phosphorous-Doped Low Pressure and Atmospheric Pressure CVD

PolycrN'Stalline-Silicon Films." J. Electrochem. Soc. 126. 838 ( 1979).

[59] H. Sunami, "Thermal Oxidation of Phosphorus-Doped Polycrvstalline Silicon in Wet Oxygen." J.

Electrochem. Soc. 125. 892 (1978).

[60] E. A. Irene, E. Tiemey, and D. W. Dong. "Silicon Oxidation Studies: Morphological Aspects of the

Oxidation of Polycrystalline Silicon." J. Electrochem. Soc, 127, 705 (1980).

[61] A. Lin, R. W. Dutton, D. A. Antoniades, and W. A. Tiller. "The Growth of Oxidation Stacking

Faults and the Point Defect Generation at Si-SiOi Interface during Thermal Oxidation of Silicon." J.

Electrochem. Soc. 128. 1121 (1981).

[62] S. M. Hu. "Anomalous Temperature Effect of Oxidation Stacking Faults in Silicon." Appl. Phys.

Lett.. 1, 165 (1915).

[63] H. Shiraki. "Stacking Fault Generation. Suppression and Grown-In Defect Elimination in Dislocation

Free Silicon Wafers by HCl Oxidation." Jpn. J. Appl. Phys.. 15. 1 ( 1976).

[64] N. Tsubouchi. H. Miyoshi. and H. Abe. "Suppression of Oxidation-Induced Stacking Fault Forma-

tion in Silicon by High Pressure Steam Oxidation." J. Appl. Phys., 17, 223 (1978).

[65] L. E. Katz and L. C. Kimerling. "Defect Formation During High Pressure. Low Temperature Steam

Oxidation of Silicon." J. Electrochem. Soc, 125. 1680 ( 1978).

[66] D. Kahng. T. A. Shankoff. T. T. Sheng. and S. E. Haszko. "A Method for Area Saving Planar Isola-

tion O.xides Using Oxidation Protected Sidewalls." J. Electrochem. Soc, 127. 2468 (1980).

4.9 PROBLEMS

1 Show from the densities and molecular weights of Si and SIOt that a layer of silicon of thickness 0.45 dQ

is consumed when a SiOn layer of thickness cIq is formed. Use densitv' values of 2.27 gm/cm-^ for Si02 and

2.33 gm/cm- for Si.

2 Show that in Eq. 14. d^ + Ado = B(t + i) reduces to d^ = Bt for long times and to dQ = B I A {t + t)

for short times.

3 (a) Show that in Eq. 14. c/q + .4^0 ~ ^(' + "J"' can be used graphically to obtain an equation describing

the oxidation rate.

(b) Generate such a plot for the 1 100°C oxidation data of Fig. 5. Use t = and ( 100) orientation to

obtain rate constants. Compare your results to those of Fig. 3.

4 Using Eq. 14 and Table 1 . how long will it take to grow 2.0 fxm of SIOt at 920°C and 25-atm steam pres-

sure?

5 Define a set of conditions to minimize the chance of inverting the surface of an n-type substrate (contain-

ing a boron diffusion) when oxidizing the wafer.

6 List possible ways of growing an initial oxide on a substrate without forming oxidation-induced stacking

faults.

7 Solve Eq. 14 for oxide thickness as/ (r. t. A, B).

8 Make use of the equation derived in Problem 7. and the data in Tables 1 and 2, to generate oxide thick-

ness versus time curves for wet and dry oxidations at 1 100°C. Assume t = 0.

9 Generate a model showing possible interface reaction and point-defect fluxes at the interface.

10 Devise a processing scheme to generate selectively a planar recessed oxide in silicon. Show how you

might prevent lateral oxidation during the oxide growth.](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-187-2048.jpg)

![170 VLSI Technology

defects, vacancies and interstitial atoms, and impurity atoms. The continuum theory

describes the diffusion phenomenon from the solution of Pick's diffusion equation

with appropriate diffusivities. (This chapter uses the terms "diffusivity" and "diffu-

sion coefficient" interchangeably.) The diffusivities of a dopant element can be deter-

mined from experimental measurements, such as the surface concentration, junction

depth, or the concentration profiles, and the solutions of Pick's diffusion equation.

When impurity concentrations are low, the measured diffusion profiles are well

behaved and agree with Pick's diffusion equation with a constant diffusivity which

can be calculated readily. In these cases the detailed atomic movements do not have

to be known. When impurity concentrations are high, the diffusion profiles deviate

from the predictions of the simple diffusion theory, and the impurity diffusion is

affected by other factors, which are not considered in Pick's simple diffusion laws.

Since the diffusion profile measurements reveal concentration-dependent diffusion

effects, we apply Pick's diffusion equation with concentration-dependent diffusivities

to the high-concentration diffusions. The concentration-dependent diffusivities are

determined by a Boltzmann-Matano analysis'^ or other formulations of profile

analysis.

Various atomistic diffusion models based on defect-impurity interactions have

been proposed to explain the experimental results from concentration-dependent dif-

fusivities and other anomalous diffusions. The atomistic diffusion theory is still

undergoing active development. Theoretical and experimental results on the diffusion

of Group III and V elements in silicon have been incorporated into various process

models. Chapter 11 discusses the process models in detail. Because process model-

ing is still developing we have to be aware of the model's limitations.

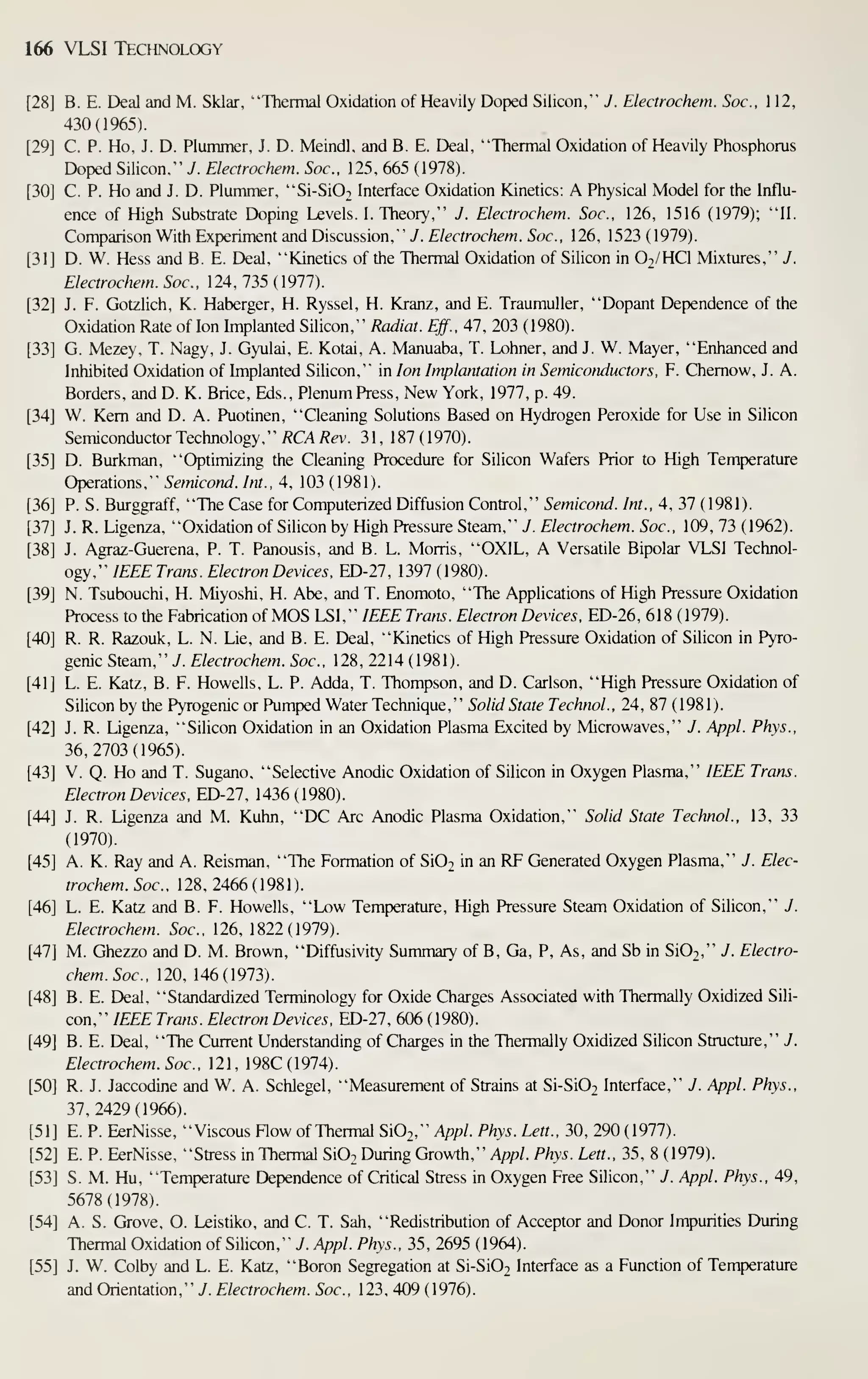

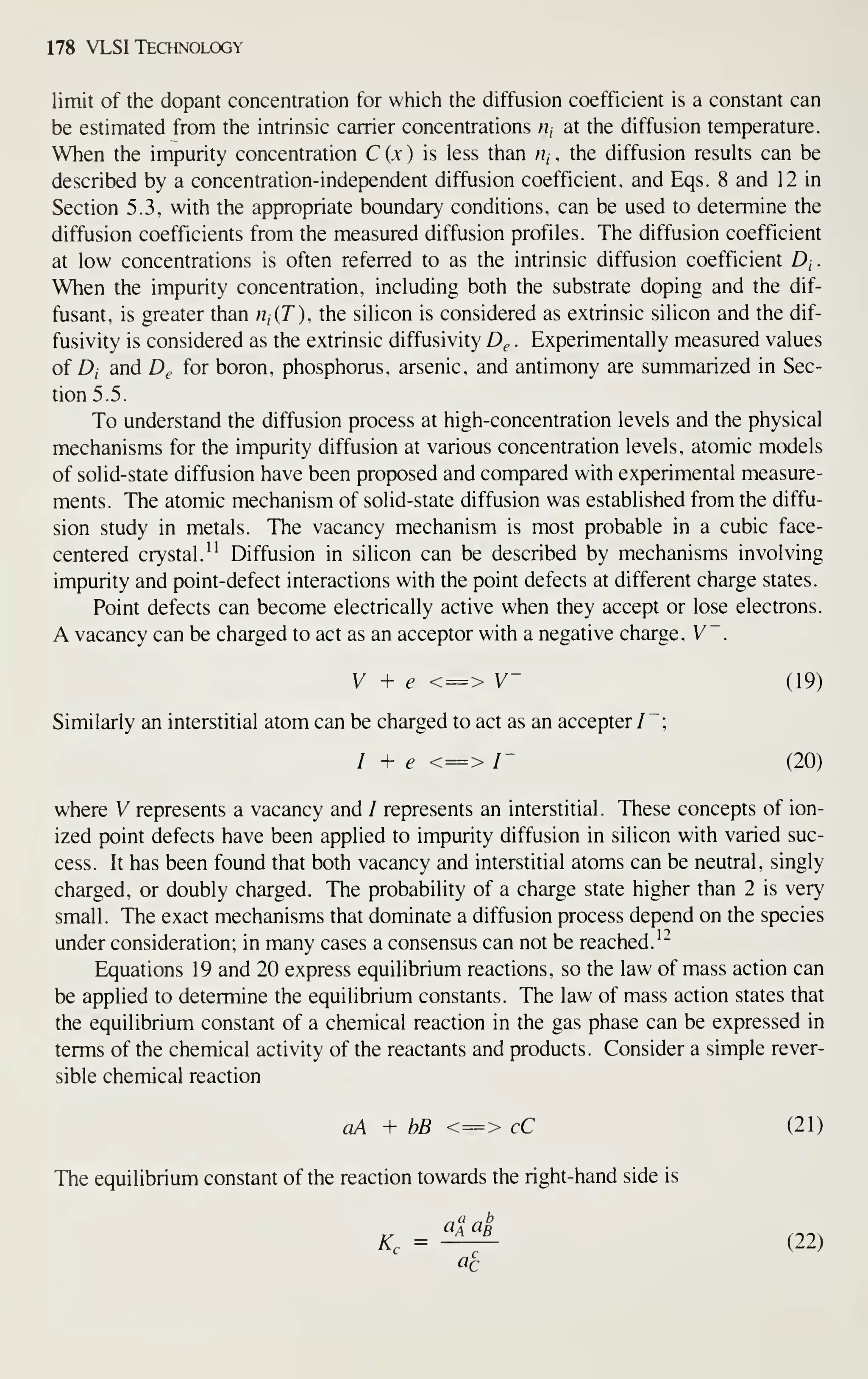

5.2 MODELS OF DIFFUSION IN SOLIDS

At high temperatures point defects, such as vacancies and interstitial atoms, are gen-

erated in a single-crystal solid. When a concentration gradient of the host or impurity

atoms exists, the point defects affect atom movement (diffusion). Diffusion in a solid

can be visualized as atomic movement of the diffusant in the crystal lattice by vacan-

cies or self-interstitials. Pigure 1 shows some common atomic diffusion models" in a

solid, using a simplified two-dimensional crystal structure with lattice constant a.

The circles represent the host atoms occupying the low-temperature lattice positions.

The solid circles represent either host or impurity atoms. At elevated temperatures

the lattice atoms vibrate around the equilibrium lattice sites. Occasionally a host

atom acquires sufficient energy to leave the lattice site, becoming an interstitial atom

and creating a vacancy. When a neighboring atom (either the host or the impurity

atom) migrates to the vacancy site, the mechanism is called diffusion by a vacancy

(Pig. la). If the migrating atom is a host atom the diffusion is referred to as self-

diffusion; if it is an impurity atom the diffusion is impurity diffusion. [Self-diffusion

experiments are usually conducted by introducing radioactive isotopes of the host

atom (Pig. la).]](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-190-2048.jpg)

![Diffusion 175

Redistribution diffusion In bipolar linear ICs, redistribution diffusion from a

predeposition diffused layer is an important step. The redistribution diffusion in a

nonoxidizing ambient has been studied extensively. In VLSI technology, no inten-

tional rediffusion is applied in order to keep the diffusion depth shallow. From an ion

implanted source, however, some redistribution diffusion can occur while thermally

annealing the ion implanted region for electrical activation at temperatures greater

than 1000°C. The solution to Pick's equation, Eq. 4, with an initial ion implanted

Gaussian distribution has been obtained.^

The equation for redistribution diffusion in an oxidizing ambient involves a mov-

ing boundary problem and is more difficult to solve. No analytical solutions have

been found. A mathematical formulation of diffusion in an oxidizing ambient from a

given initial profile has been obtained;'' however, the solution involves expressions

that require numerical integration. Segregation of impurity atoms during oxidation

between the growing oxide and silicon was discussed in Chapter 4. Since redistribu-

tion diffusion is not important in VLSI technology, we will not discuss it in this

chapter.

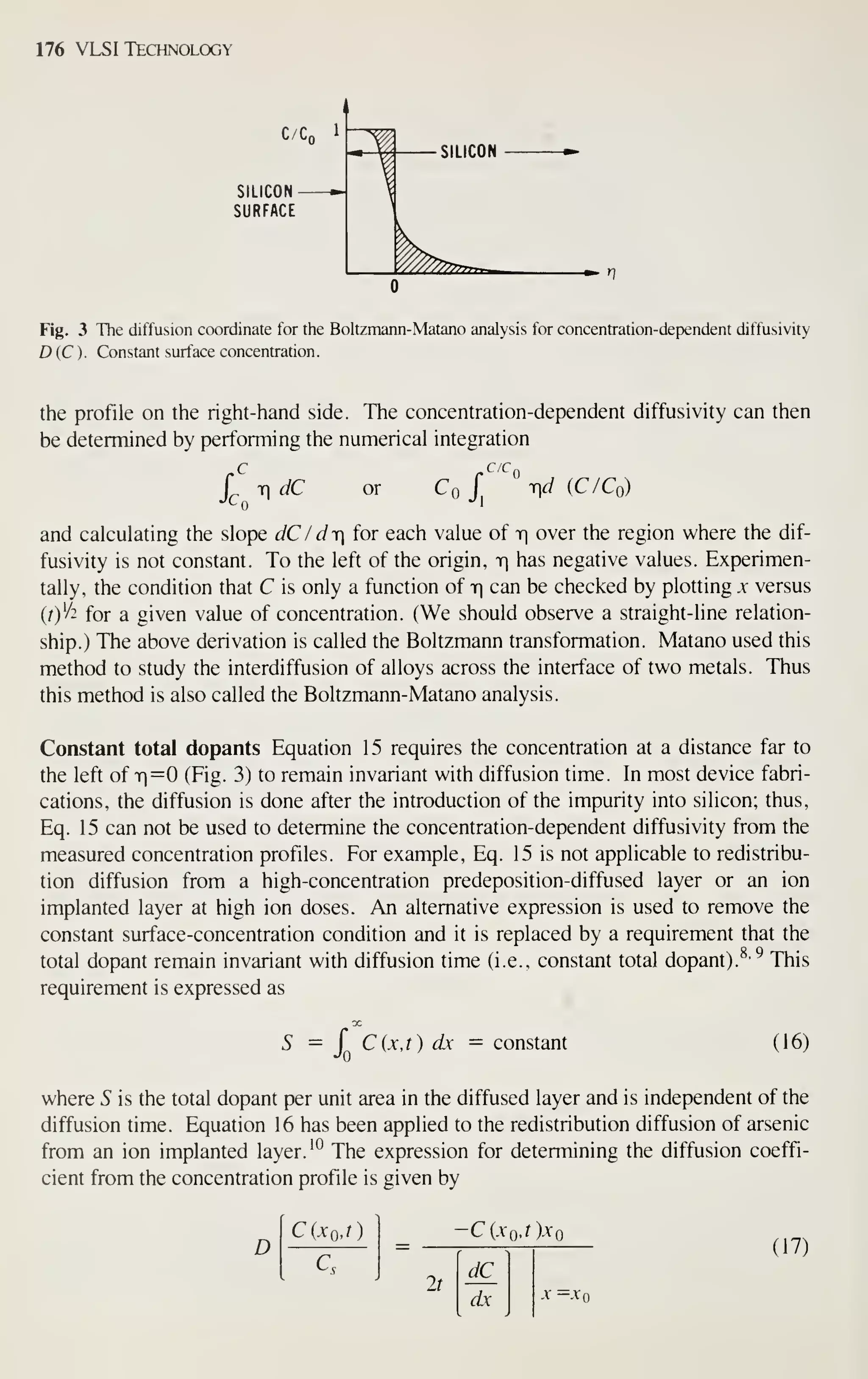

5.3.2 Concentration-Dependent Diffusivities

At high concentrations, when the diffusion conditions are close to the constant surface

concentration case or to the constant total dopant case, the measured impurity profiles

deviate from Eqs. 8 and 12, respectively. In these high-concentration regions, the

impurity profile can often be represented by concentration-dependent diffusivities.

Equation 3 is used to determine the concentration-dependent diffusivities from the

experimentally measured concentration profiles. This section considers diffusion

under two conditions: constant surface concentration and a constant total dopant.

Constant surface concentration The one-dimensional diffusion equation with a

concentration-dependent diffusion coefficient was given in Eq. 3. If D is only a func-

tion of the concentration C and the surface concentration is maintained at a constant

value, Eq. 3 can be transformed into an ordinary differential equation"^ with a new

variable iq, where

m =

^ (14)

Thus, both D and C depend on x implicitly. After a change of variable to t], Eq. 15

can be obtained from Eq. 3:

-V2/^ T] dC

D(C) = -^ (15)

dT

Equation 15 refers to an infinite system. To determine the concentration-dependent

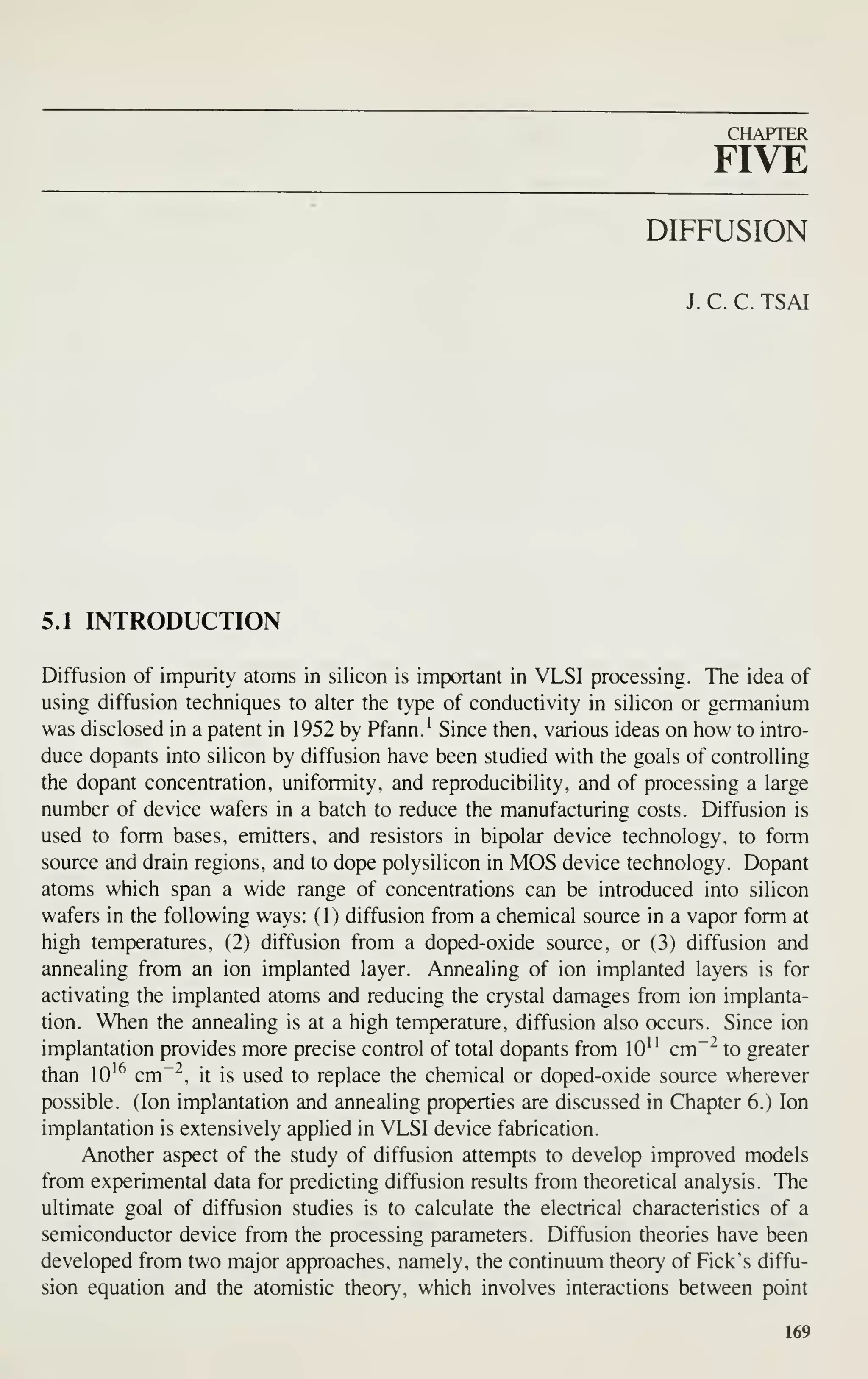

diffusivity from Eq. 15, we first plot the measured diffusion profile as concentration

(or normalized concentration) versus r (see Fig. 3). We choose the origin of the

abscissa so that the area under the profile on the left-hand side equals the area under](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-195-2048.jpg)

![Diffusion 179

where K^, is the equihbrium constant, a^ is the cheniical activity of element A, % is

the chemical activity of element B, qq is the chemical activity of the product C, and

a.h, and c represent the mole concentration of elements A, fi, and C of the reaction

shown in Eq. 21. For a dilute solution (a near ideal solution), the activities can be

replaced by the concentrations^ of the reactants and products according to Rault's law,

and Eq. 22 becomes

K^

CY

(23)

where [A] is the concentration of element A, {E is the concentration of element fi,

and [C] is the concentration of element C.

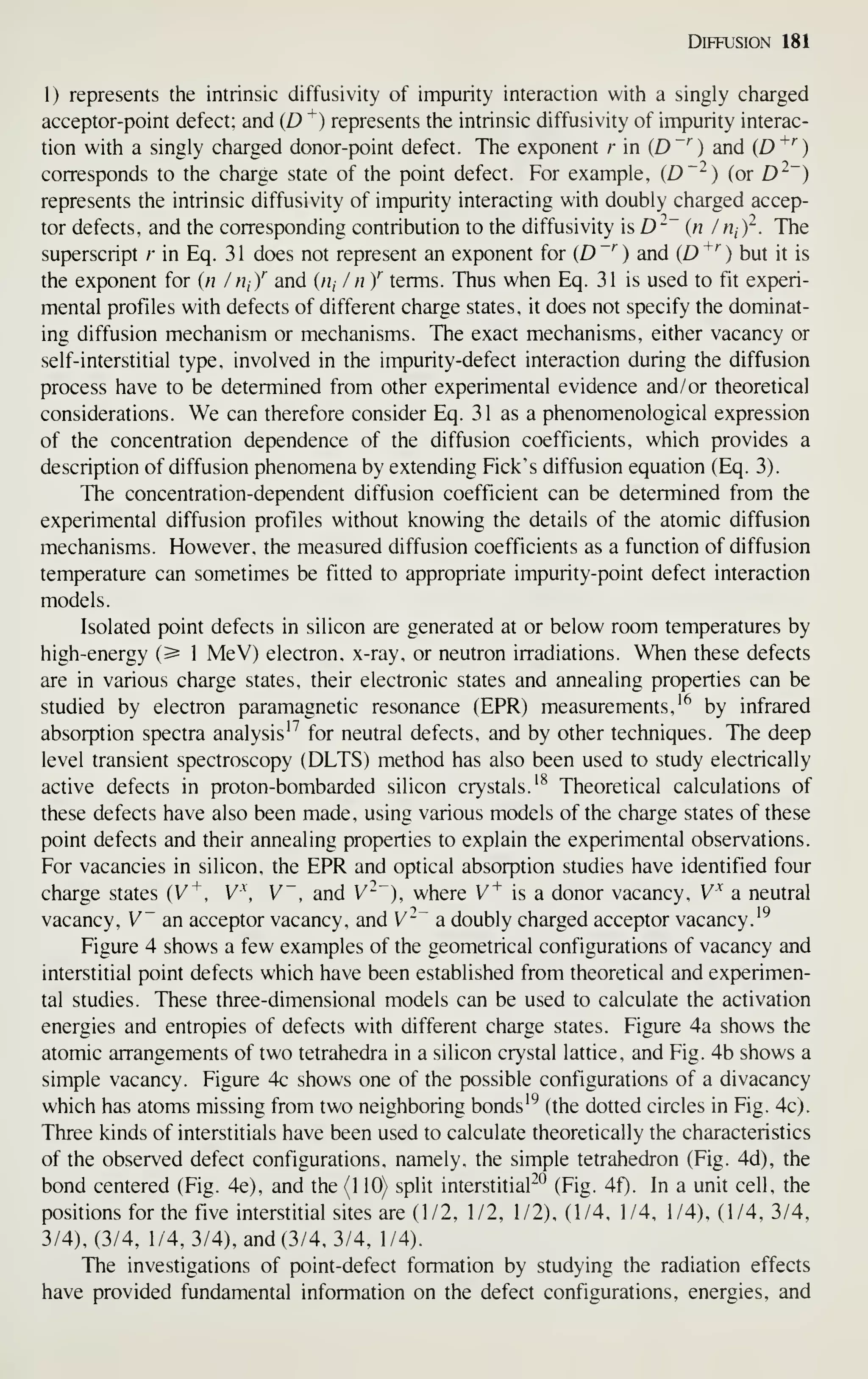

The law of mass action has been applied to dilute solid solutions where point

defects in a solid are considered as dilute solid solutions of defects in the crystal lat-

tice. The law of mass action is applicable to a dilute solid solution when the reactions

are in thermal equilibrium and sometimes applicable when the reactions are in quasi-

thermal equilibrium.

Vacancy and interstitial concentrations can be determined from statistical ther-

modynamics. They are expressed in terms of entropies of formation AS and forma-

tion energies A//. For a neutral monovacancy in silicon, the concentration Cy can be

expressed as

20

C^, =5.5 X 10-^ exp

'as^5

k

exp

kT

(24)

where XSy is the entropy of formation of a neutral monovacancy, A//v is the forma-

tion energy of a neutral monovacancy (expressed in eV). The superscript x represents

a neutral charge state of the defect. The subscript V denotes a vacancy defect.

For silicon. A/Zy is estimated to be greater than or equal to 2.5 eV and AS'v is

estimated to equal 1.1^. Thus the intrinsic concentration of monovacancy at the dif-

fusion temperatures of interest is rather low for silicon.

For an extrinsic silicon, the acceptor-type vacancy concentration can be

expressed as'^

1 + T^ exp

Cv" =

Ey - E,

kT

1 + ^/2 exp

Ev - Ef

QiV-)

Ey ~ Ej

kT

Ey - Ef

kT

kT

Q(V-)

(25)](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-199-2048.jpg)

![180 VLSI TECHN0LCX3Y

for (Ey — Ef)'»kT and {By — Ei)y>kT. Cy is the acceptor vacancy concentration

in the extrinsic siHcon, C, (V") is the acceptor vacancy concentration in the intrinsic

sihcon, Ey is the acceptor vacancy energy level (in eV), £, is the intrinsic Fermi level

(in eV), and Ef is the Fermi level of the extrinsic silicon (in eV). Thus,

C,

exp

C,{V-)

But for the nondegenerate case, we obtain

n = /I, exp

for n-type silicon, and Eq. 26 becomes

Cy-

Ei

kT

Ef - Ei

(26)

kT

(27)

If the impurity diffusion is dominated by the acceptor monovacancy mechanism, the

diffusion coefficient is approximately proportional to the acceptor monovacancy con-

centration. Thus, we have

-^ = ^ (28)

D, n,

where D is the diffusion coefficient in extrinsic silicon, and D, is the diffusion coeffi-

cient in intrinsic silicon.

The intrinsic carrier concentration /i, can be calculated using the following empir-

ical formula:

'*

where

n] = 1.5 X 10-^3 j2>

expt(-1.21 + ^Eg)/kT]

•/2

^Eo = -7.1 X 10"

T

(29)

(30)

and an assumed fg = 1.21 eV.

Equation 28 states that the interaction of the impurity atoms with charged accep-

tor vacancies leads to a dependence of the diffusion coefficient on the Fermi level at

the diffusion temperature. Since vacancies and interstitials can have various charge

states, Eq. 28 can be generalized to include all possible combinations of impurity-

point defect interactions.'^

D = D' + % iD-') + t (E>^')

n,

(31)

where D x for neutral defects, (D "''

), and (D ^^ ) refer to the intrinsic impurity dif-

fusivities associated with the particular charge states, r, of the point defects that affect

the impurity diffusion and r is an integer 1, 2, 3, . .

.

, m. For example, D^ represents

the intrinsic diffusivity of impurity interaction with a neutral-point defect; (D "), (r =](https://image.slidesharecdn.com/simonm-220913174129-44ec6f82/75/Simon-M-Sze-editor-Very-Large-Scale-Integration-VLSI-Technology-McGraw-Hill-Inc-US-1983-pdf-200-2048.jpg)

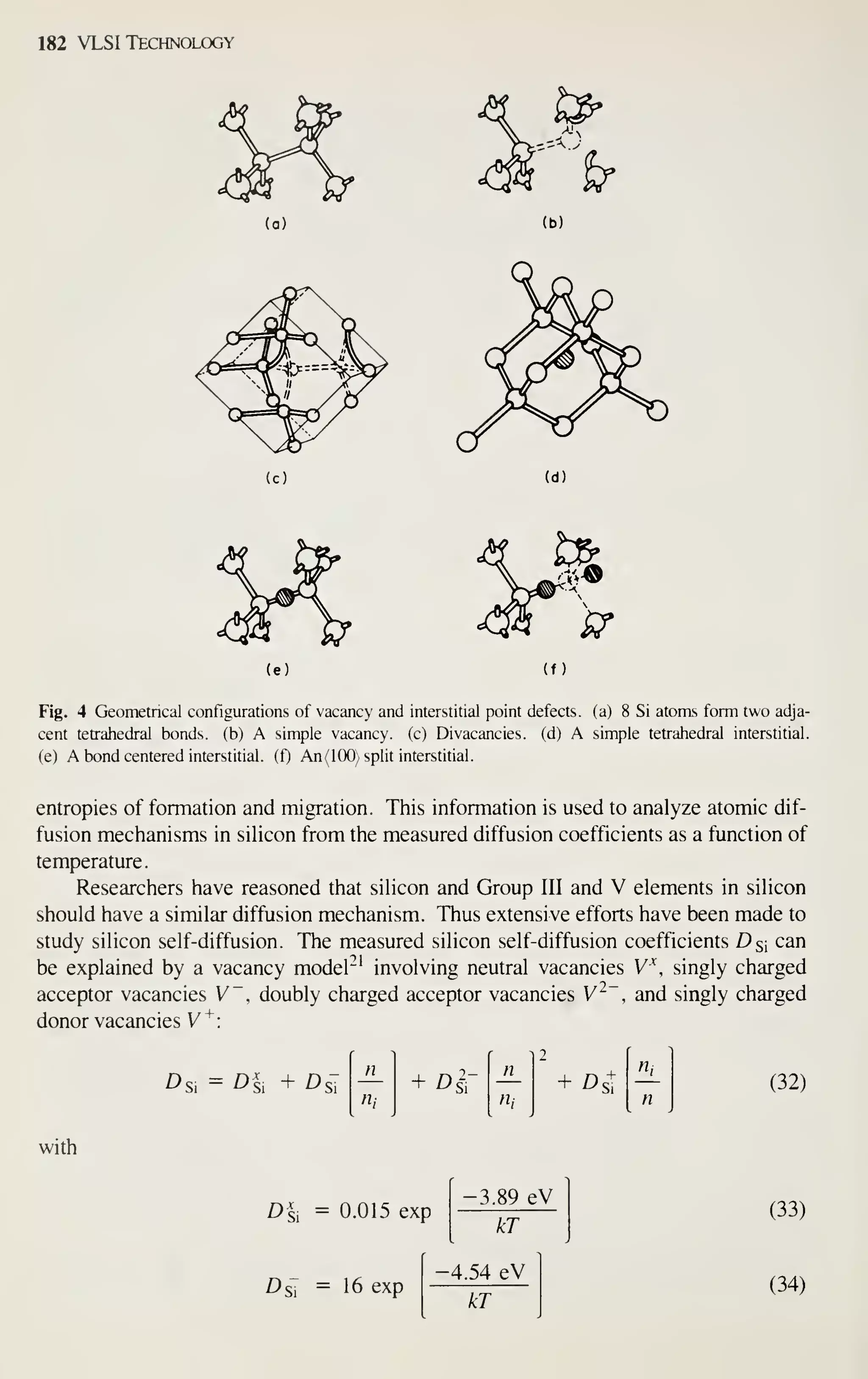

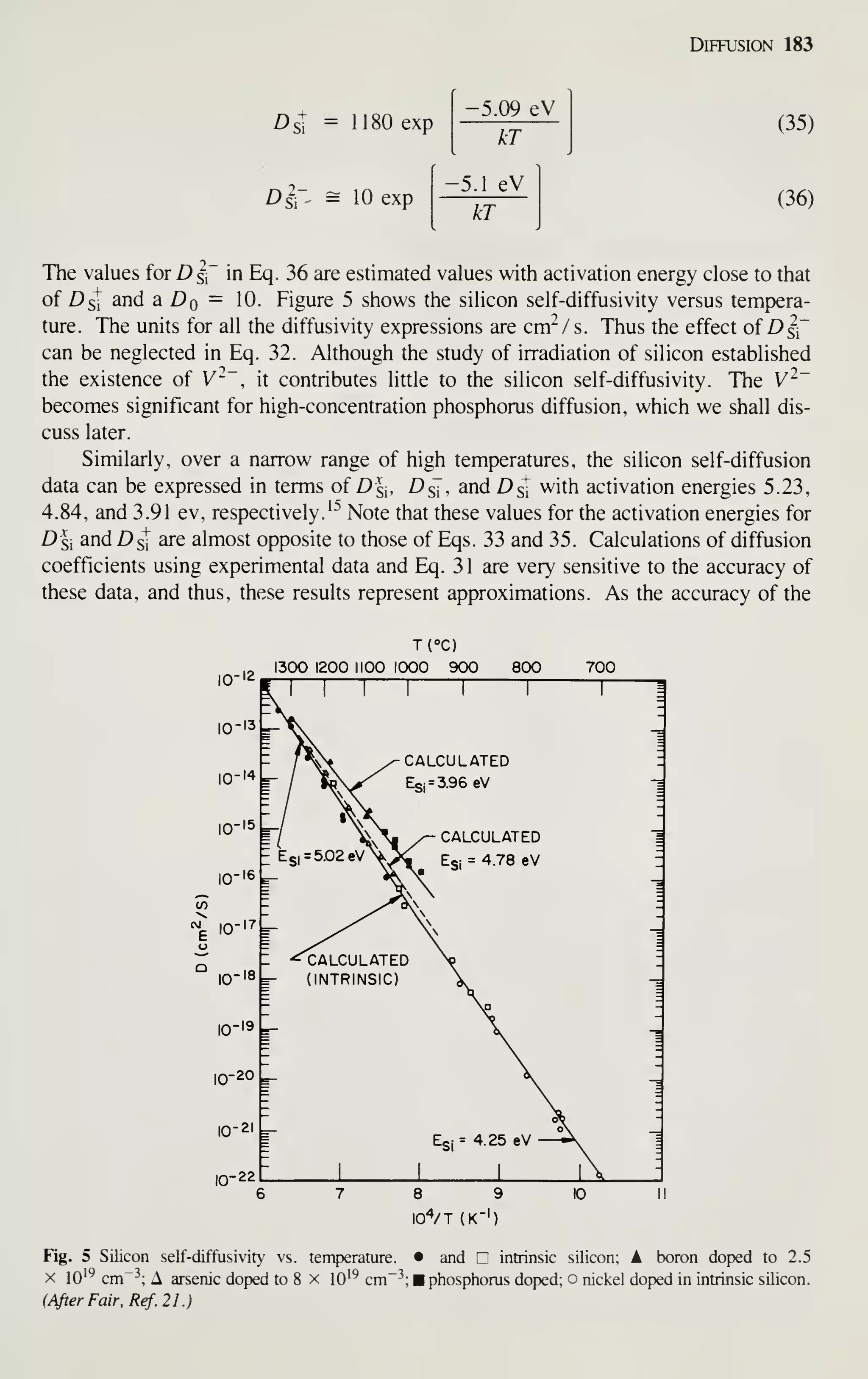

![Diffusion 185

Table 1 Correction factor C.F. for the measurement

of sheet resistances with the four-point probe-^

Circle Square

Rectangle

d/s diam d/s a/d^ 1 a/d = 2 a/d = 3 a /d^4

1.0 0.9988 0.9994

1.25 1.2467 1.2248

1.5 1.4788 1.4893 1.4893

1.75 1.7196 1.7238 1.7238

2.0 1.9475 1 .9475 1 .9475

2.5 2.3532 2.3541 2.3541

3.0 2.2662 2.4575 2.7000 2.7005 2.7005

4.0 2.9289 3.1137 3.2246 3.2248 3.2248

5.0 3.3625 3.5098 3.5749 3.5750 3.5750

7.5 3.9273 4.0095 4.0361 4.0362 4.0362

10.0 4.1716 4.2209 4.2357 4.2357 4.2357

15.0 4.3646 4.3882 4.3947 4.3947 4.3947

20.0 4.4364 4.4516 4.4553 4.4553 4.4553

40.0 4.5076 4.5120 4.5129 4.5129 4.5129

oc 4.5324 4.5324 4.5325 4.5325 4.5324

measuring the voltages for current flowing in two directions, and then averaging the

two readings. This average reading removes some of the effect of contact resistance.

If the voltage differences are large, however, probe points and the cleanliness of the

sample surface should be checked. To ensure that the readings are correct, the sheet

resistances at two or three current levels can be measured. These measurements show

whether the measured sheet resistances are constant over the range of measured

currents. For high-resistivity silicon, annealing the sample in N2 at 150°C for a few

minutes improves the accuracy of readings. Always try to use as low current as possi-

ble to avoid ohmic heating or to avoid reaching the punchthrough voltage.

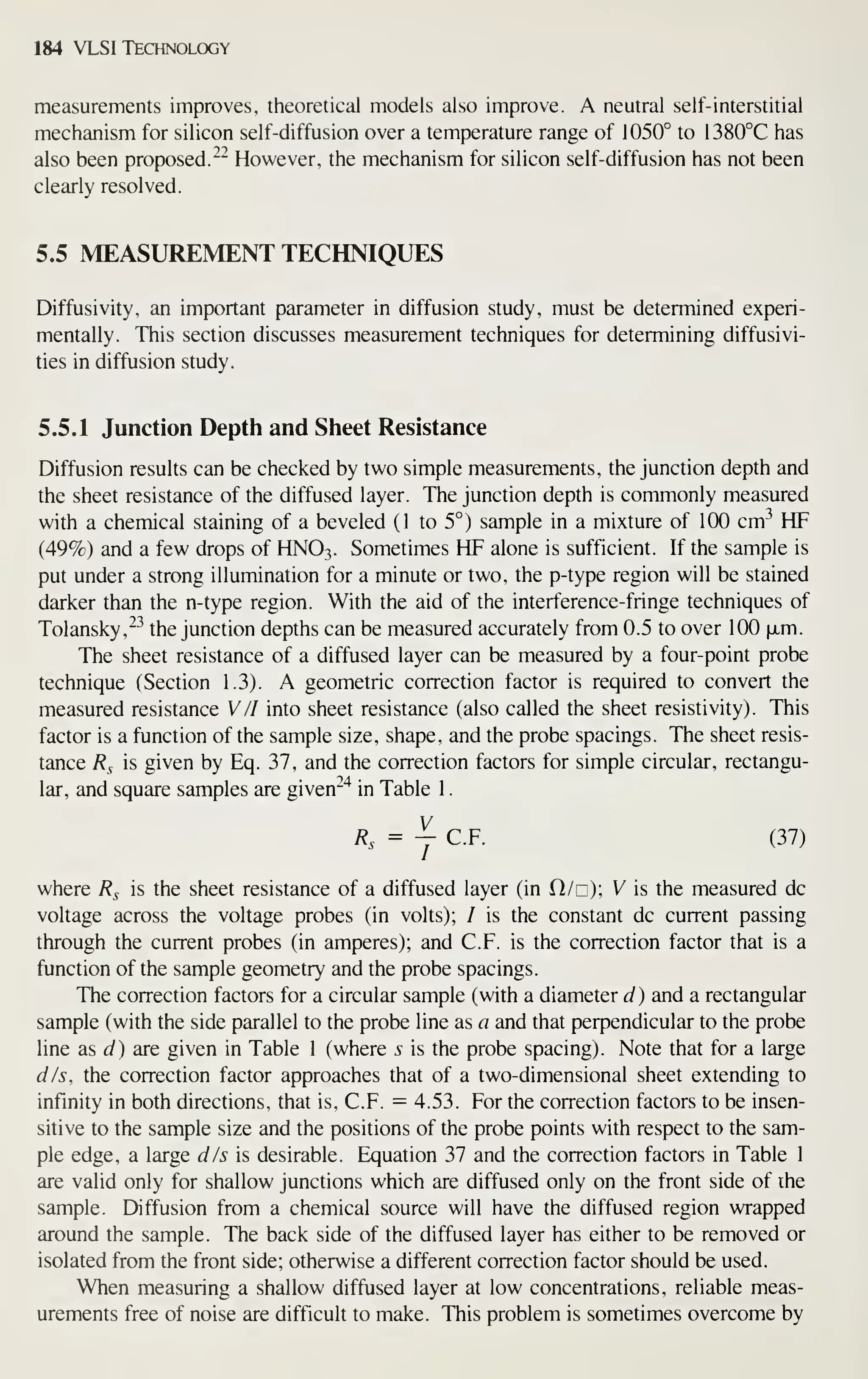

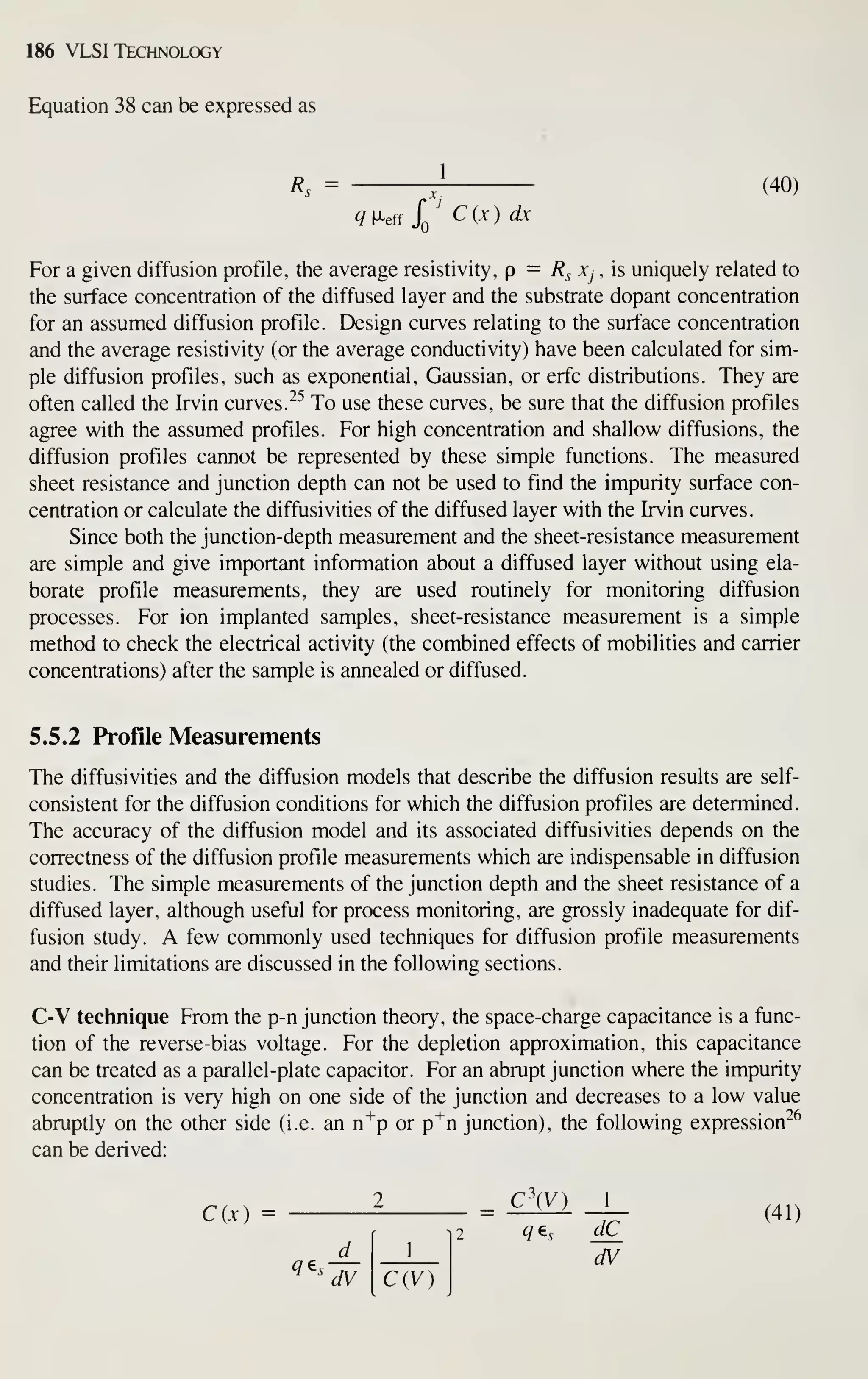

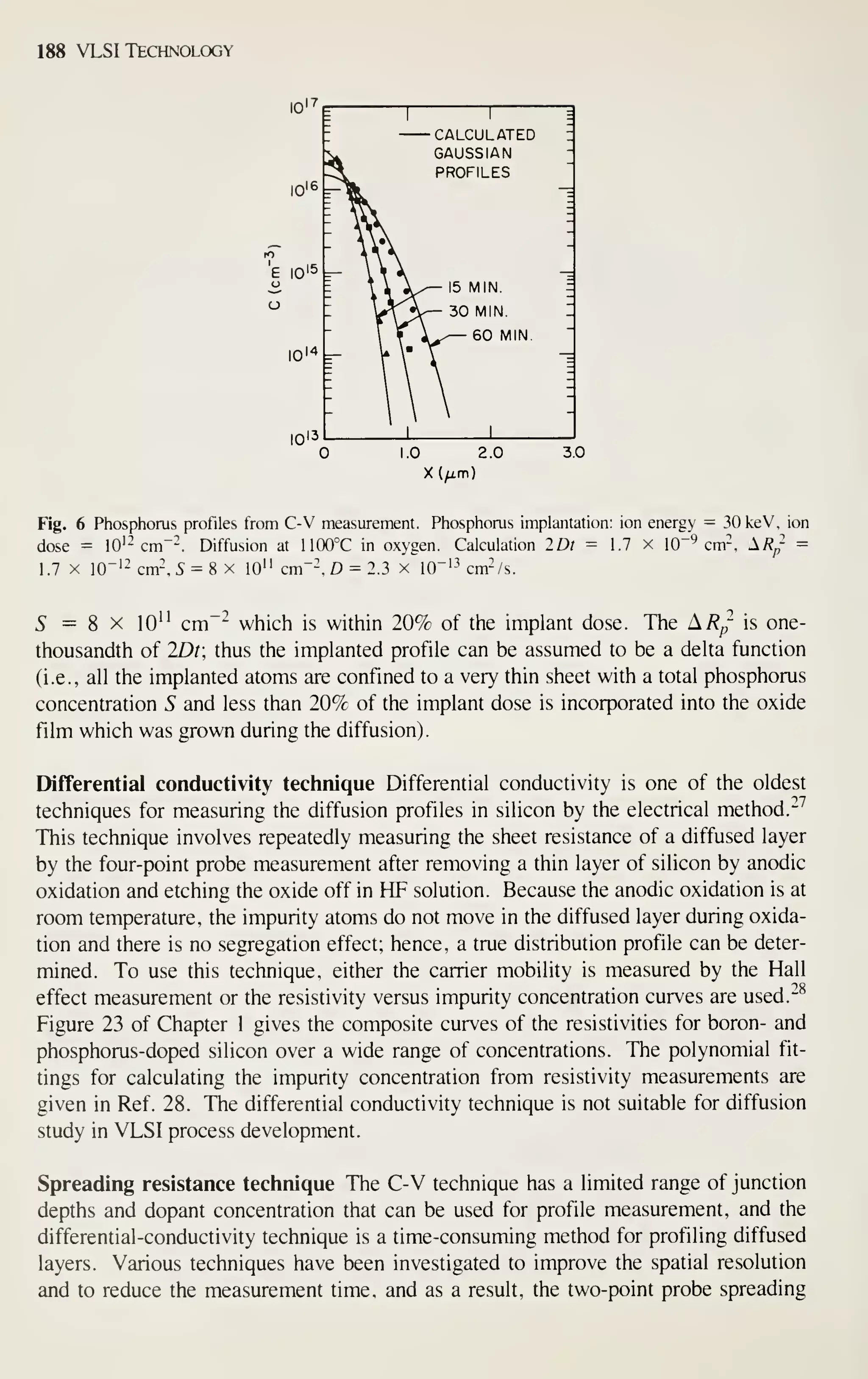

For a diffused layer, an average sheet resistance R^ is related to the junction

depth Xj , the carrier mobility ji, and the impurity distribution C (x ) by the following

expression:

Rs =

-r-^ (38)

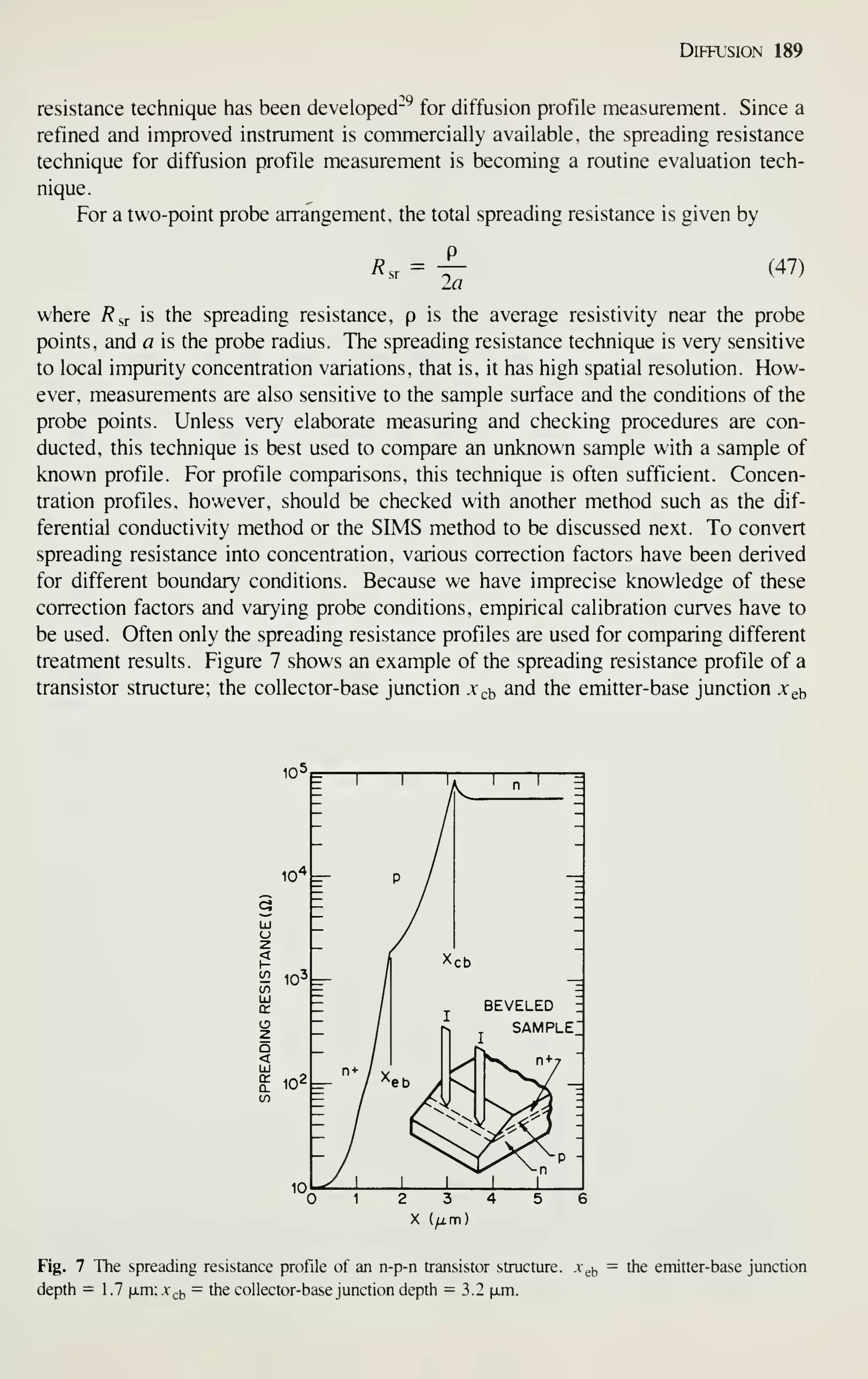

^ X' M-CU) dx

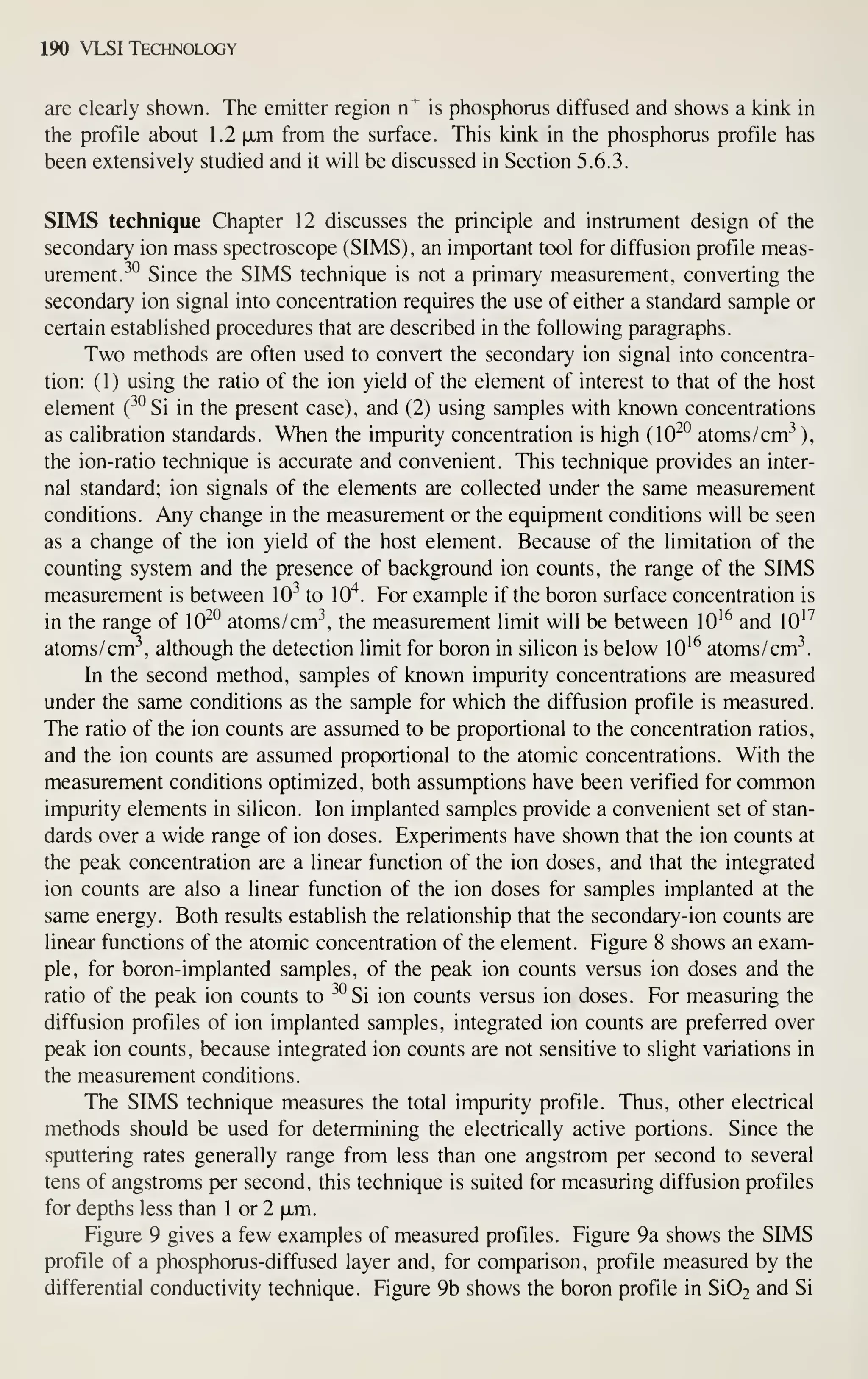

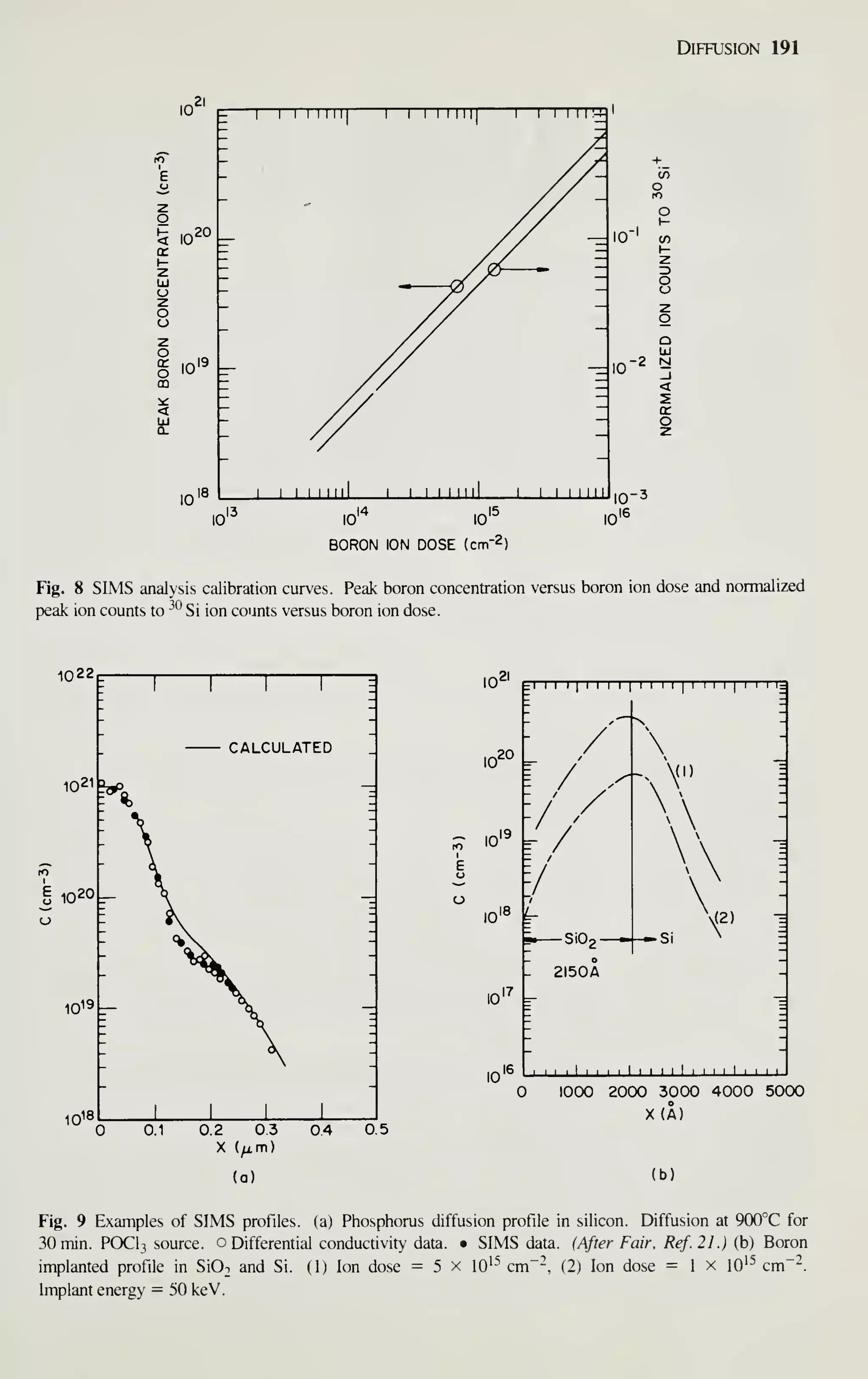

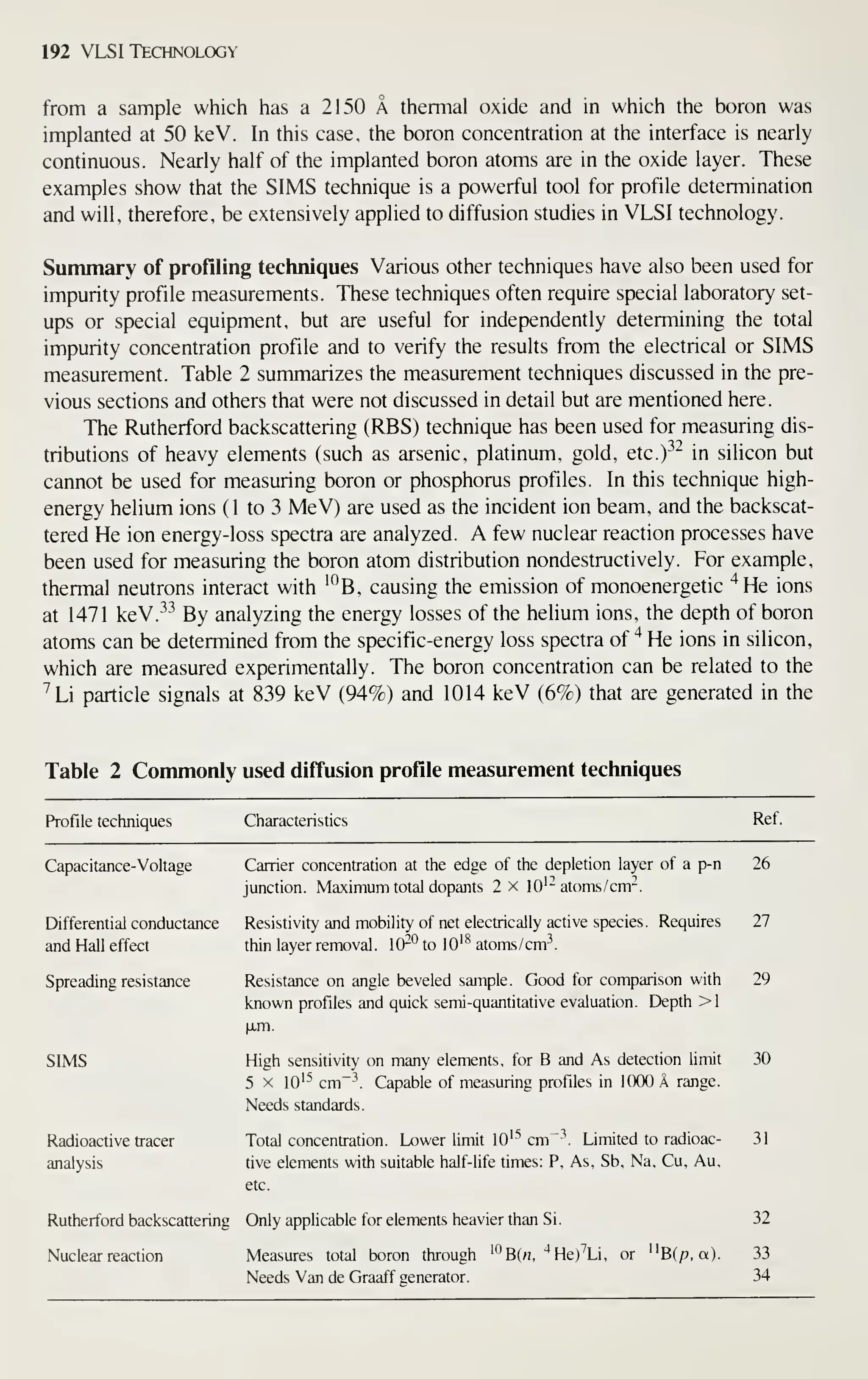

The depletion of charge carriers near Xj can be neglected in the above calculation. In