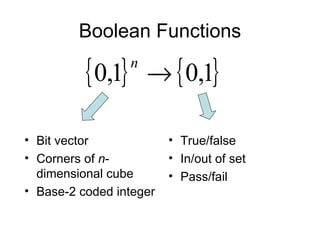

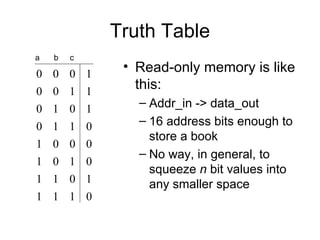

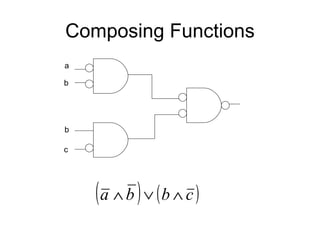

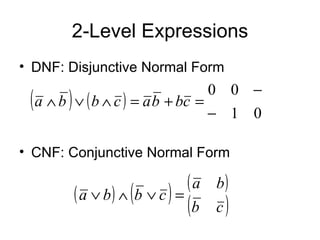

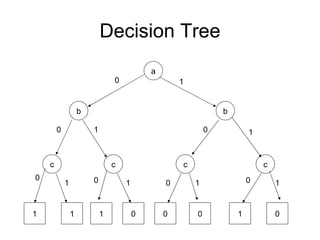

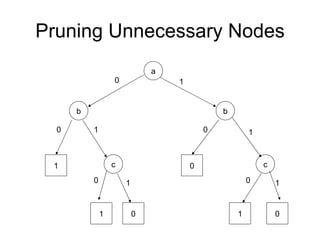

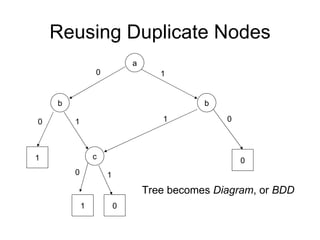

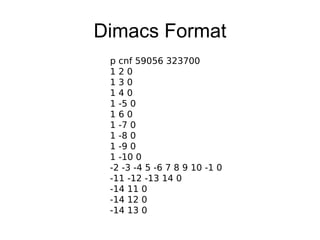

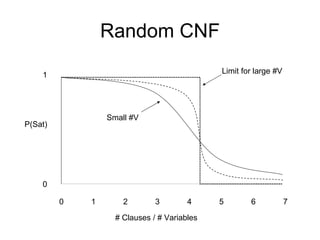

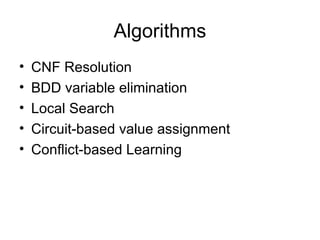

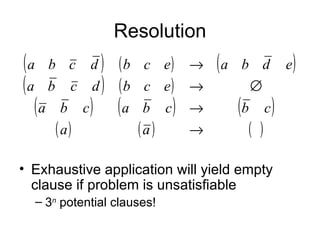

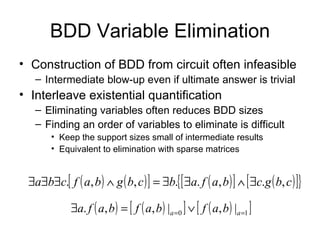

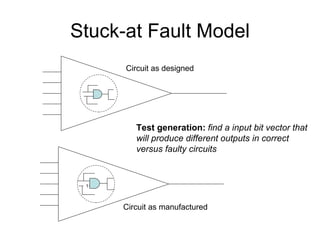

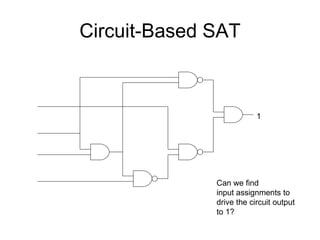

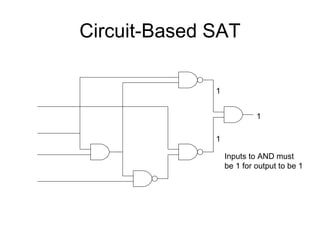

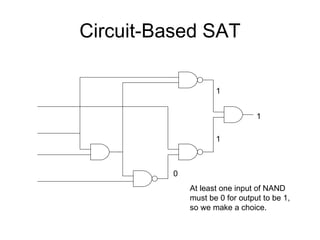

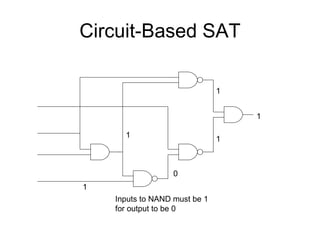

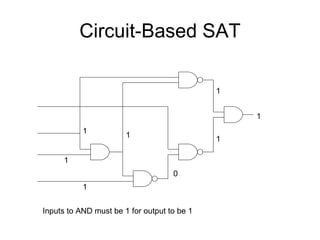

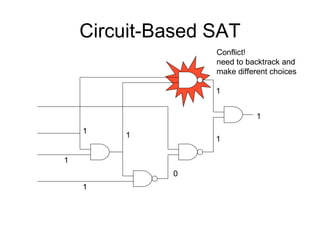

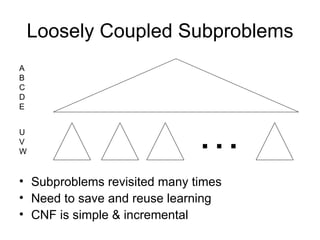

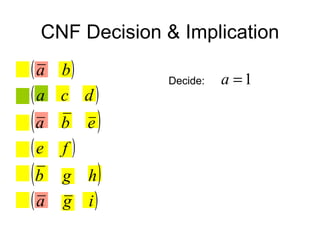

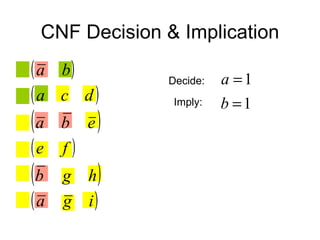

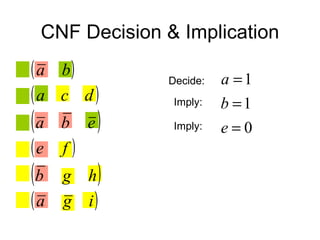

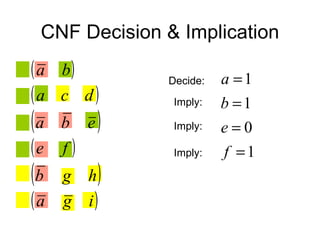

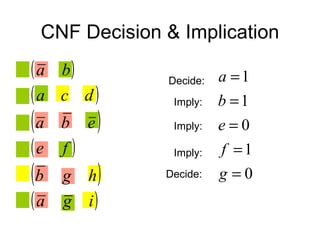

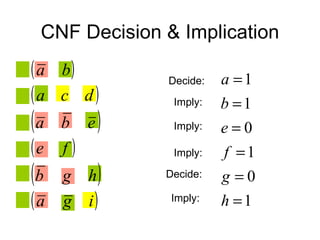

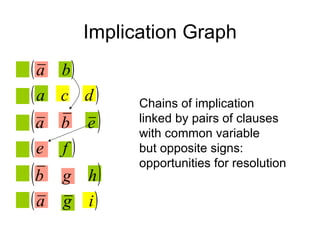

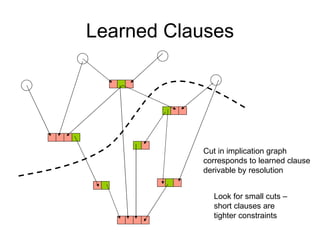

The document discusses applications and algorithms for satisfiability problems in Boolean logic and functions. It covers topics such as truth tables, composing functions, optimization, decision trees, binary decision diagrams, satisfiability communities and conferences, SAT file formats, and algorithms like resolution, variable elimination, local search, and circuit-based value assignment.

![Satisfiability: Applications and Algorithms Jim Kukula [email_address]](https://image.slidesharecdn.com/satisfiability-091117142247-phpapp01/75/Satisfiability-1-2048.jpg)