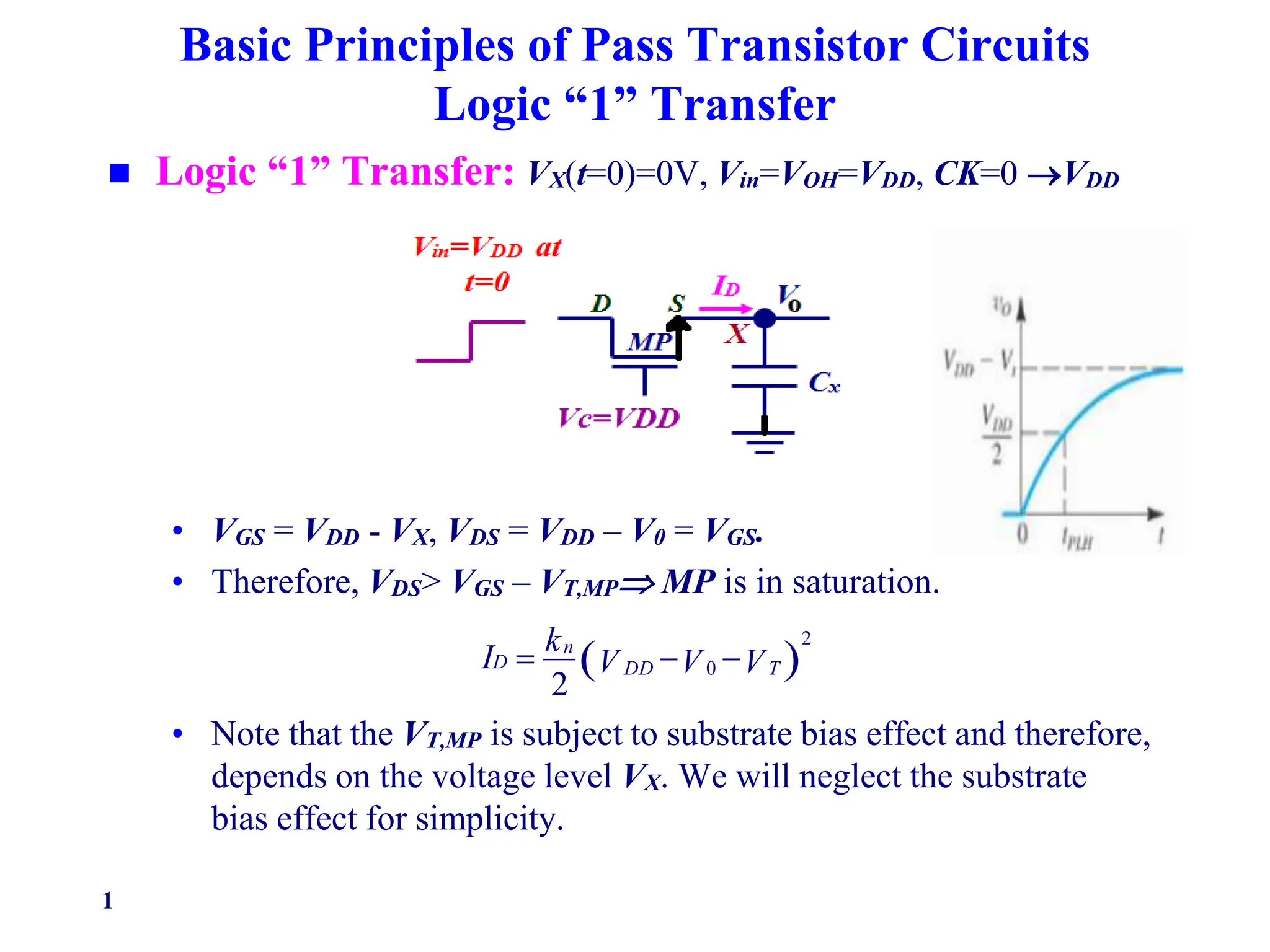

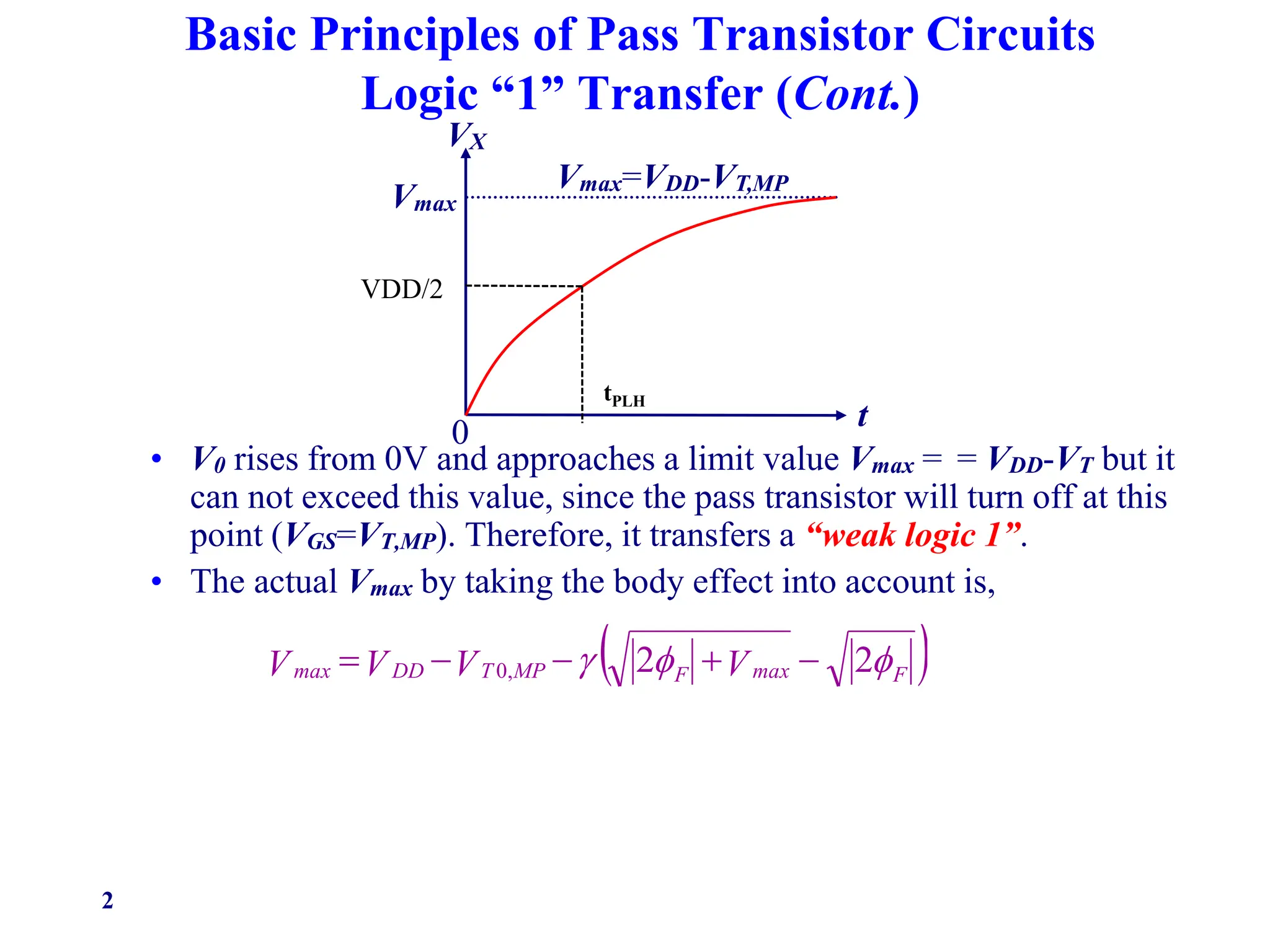

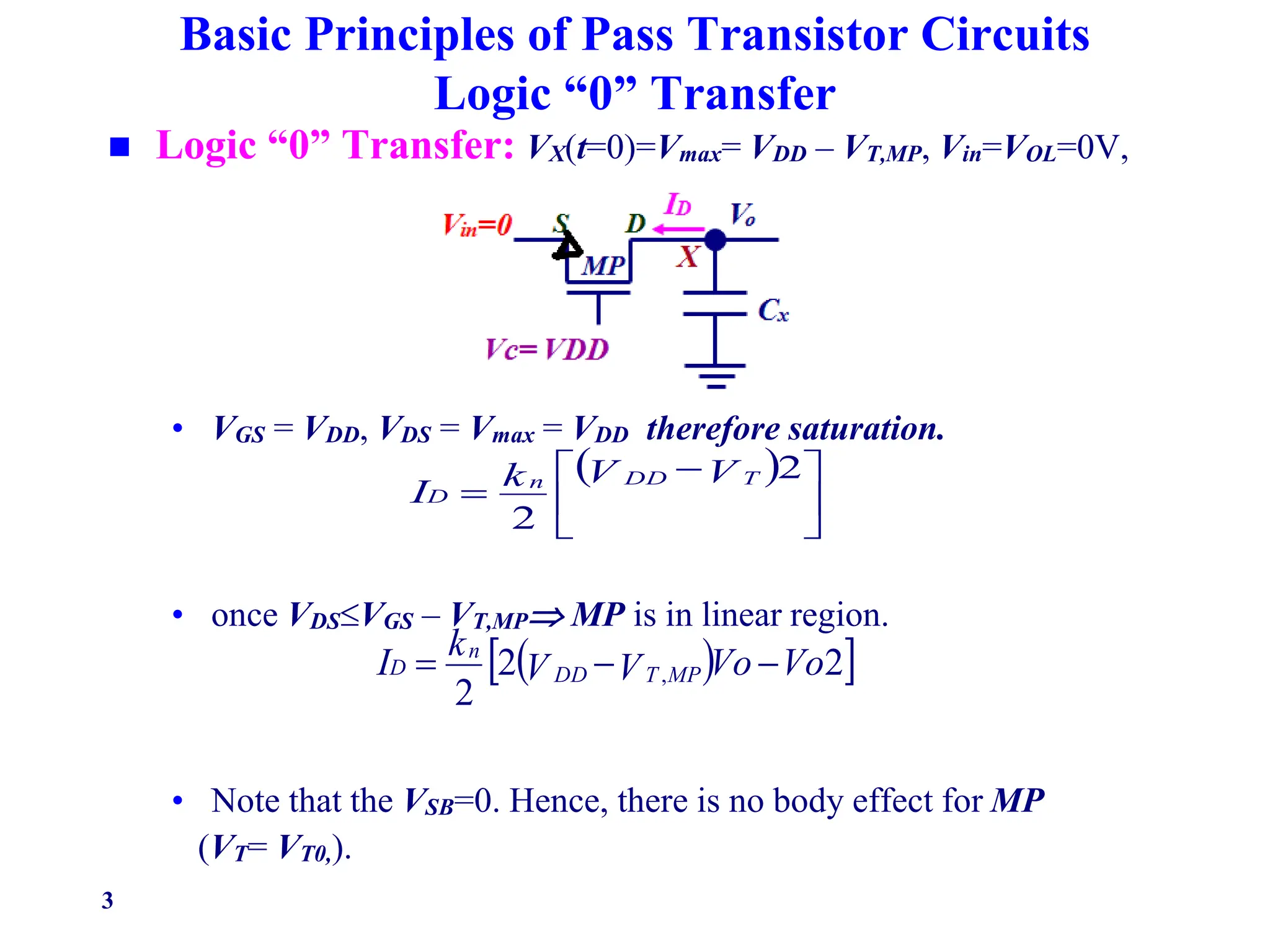

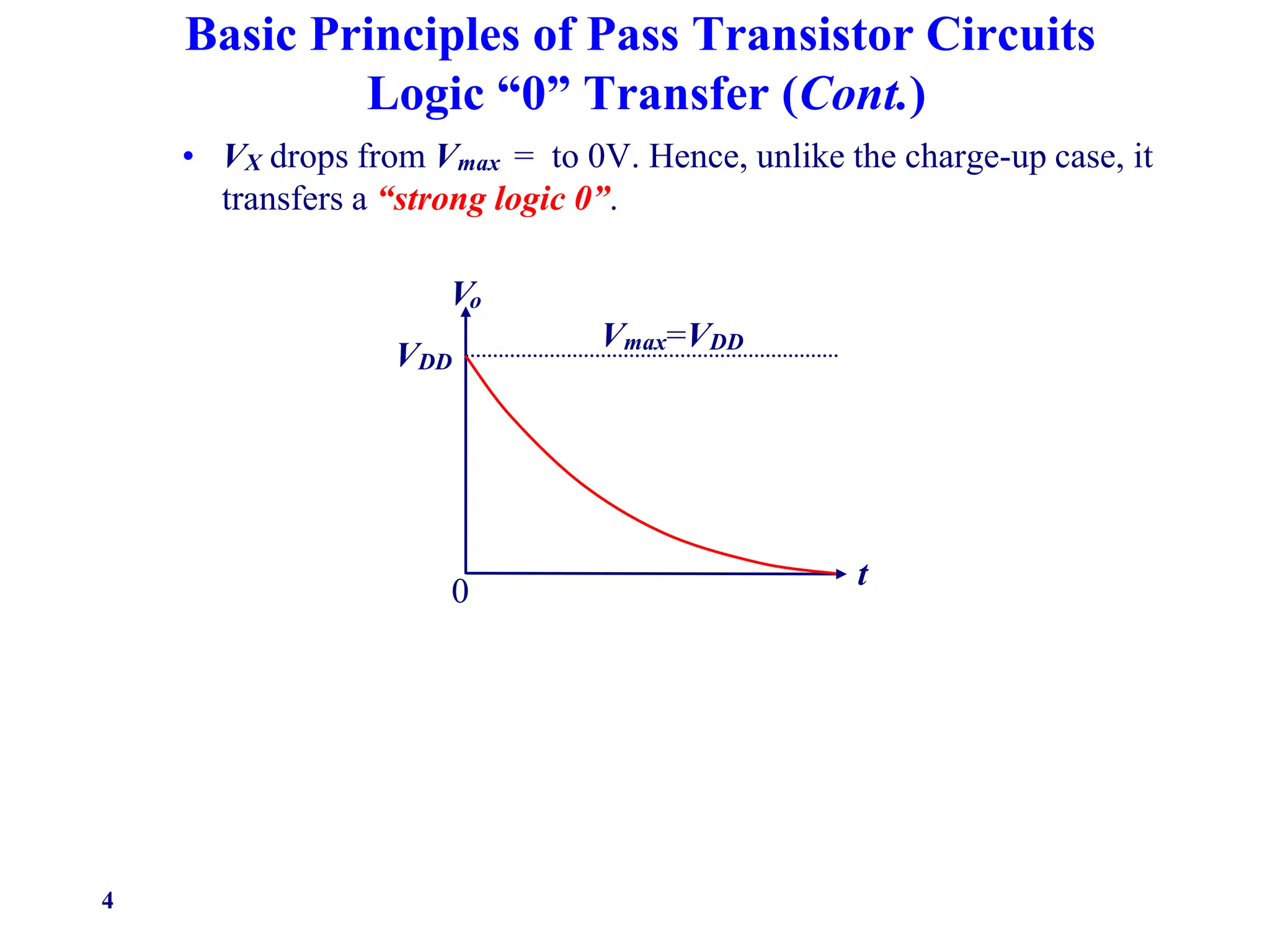

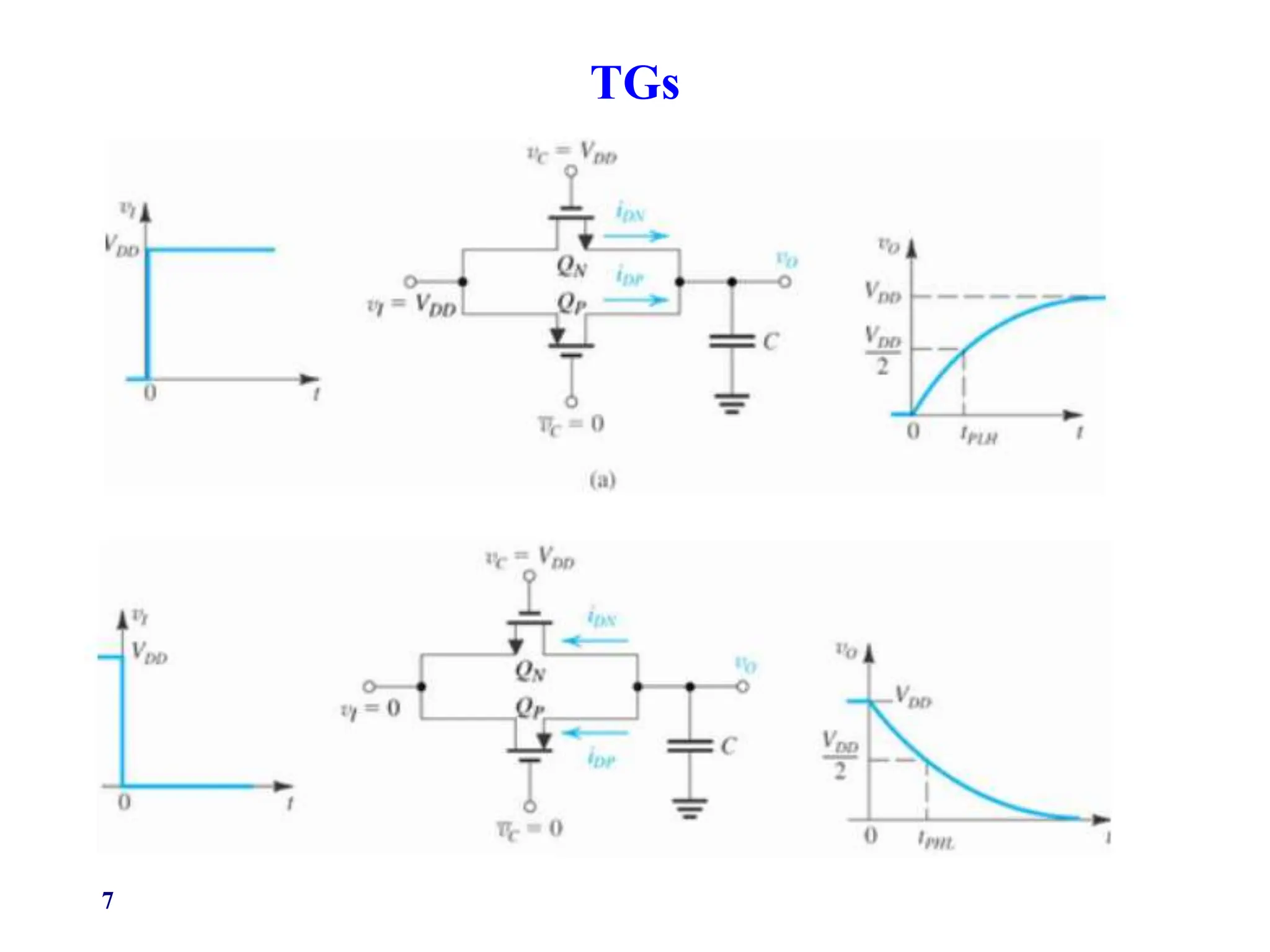

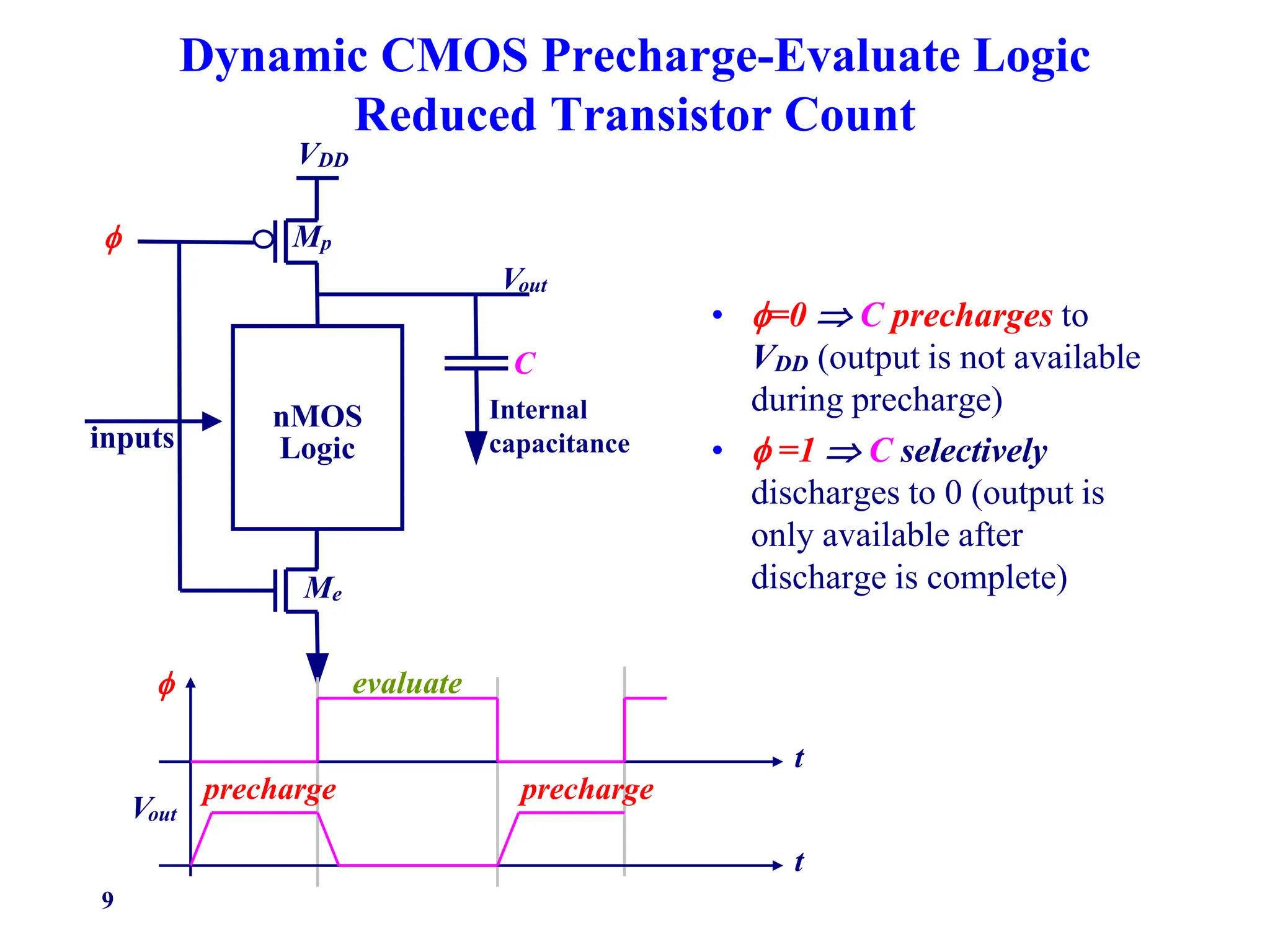

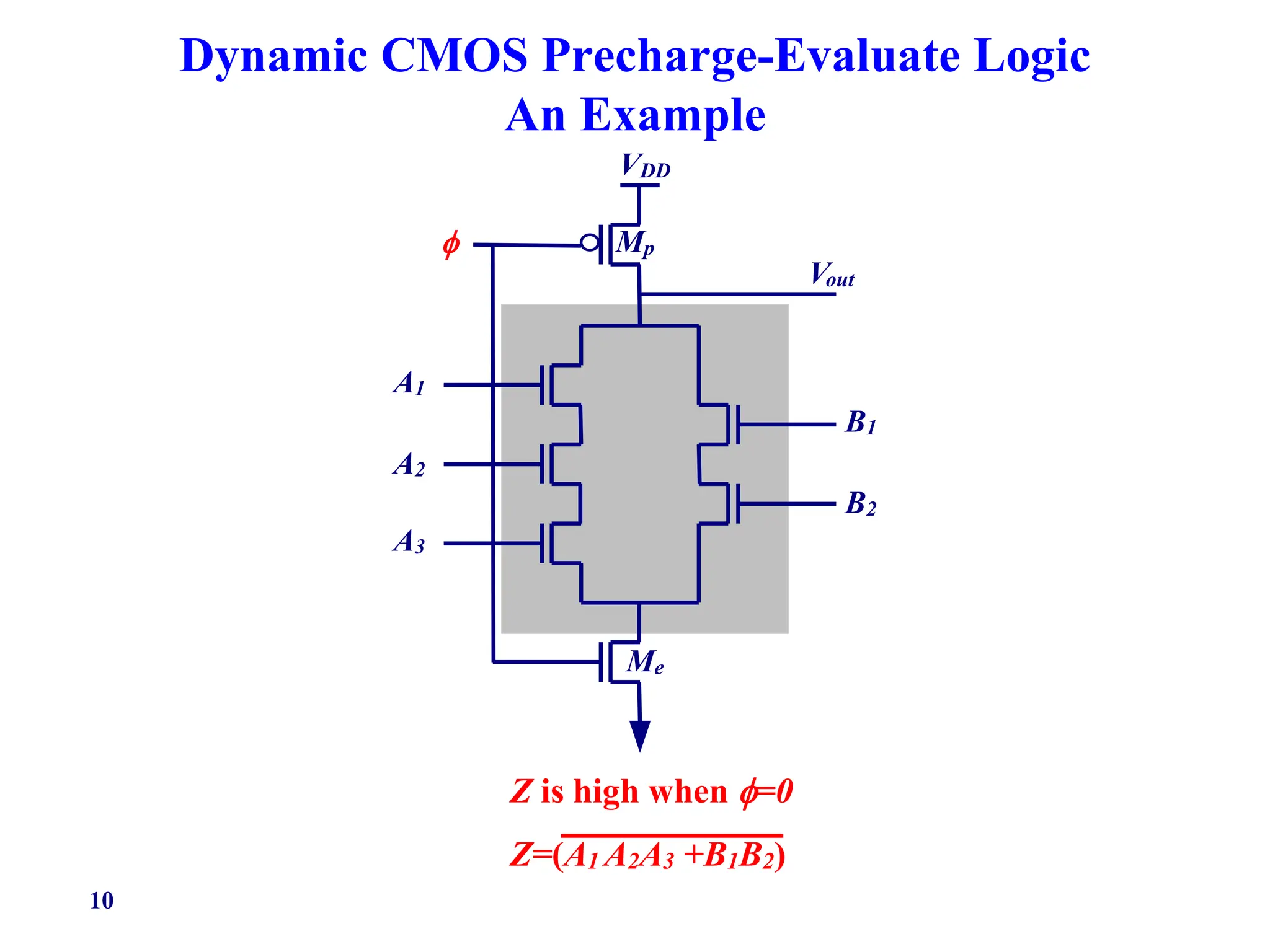

The document discusses the principles of pass transistor circuits, focusing on the transfer of logic '1' and '0', highlighting current flow, saturation, and effects such as substrate bias. It describes transmission gates as effective switches for both digital and analog applications, enabling bidirectional current flow with constant on-resistance. Additionally, it covers dynamic CMOS precharge-evaluate logic, emphasizing its advantages, such as reduced transistor count and low static power dissipation, alongside disadvantages like time constraints for output availability.