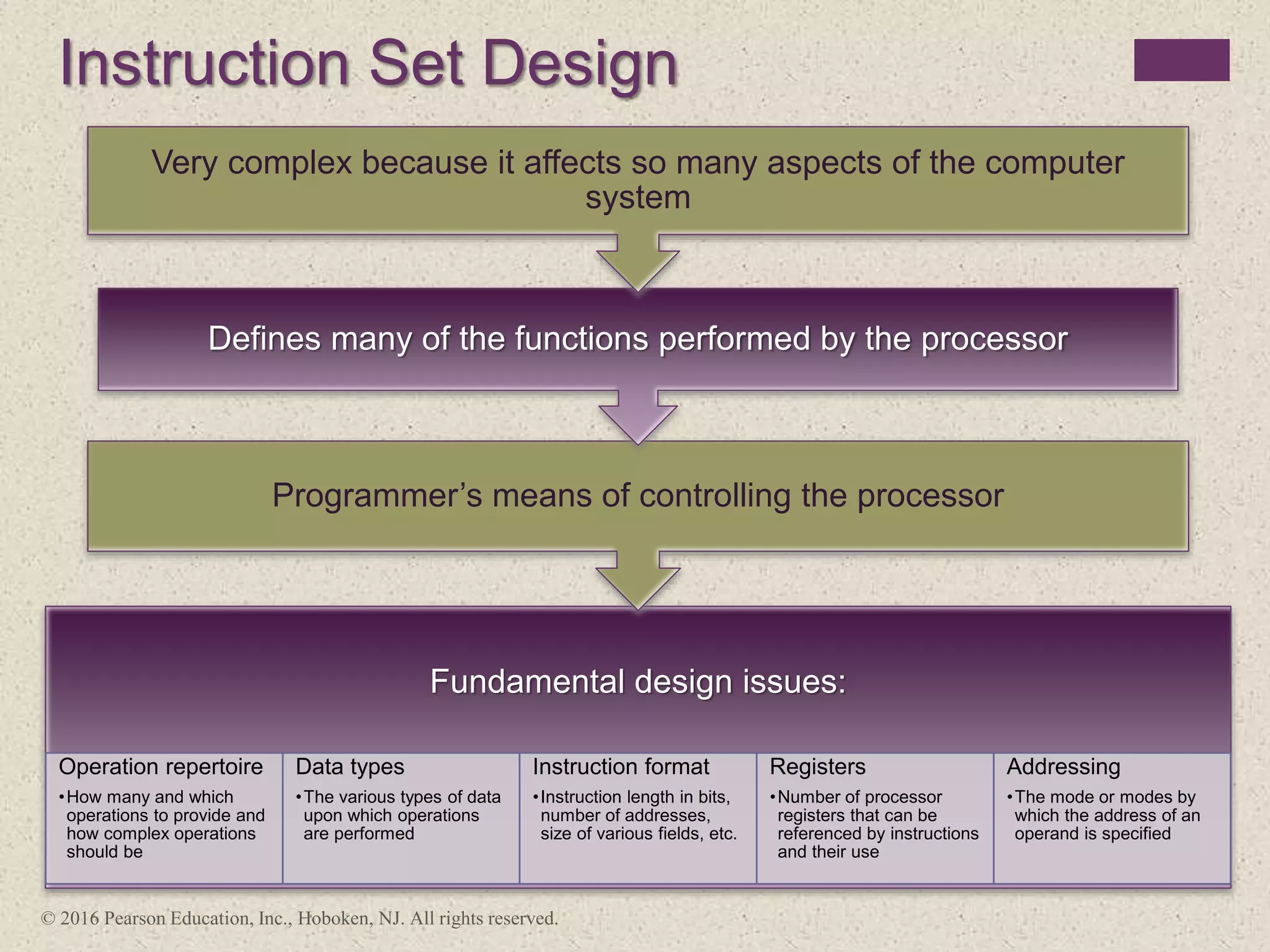

The document discusses machine instruction characteristics and representation. It covers the following key points:

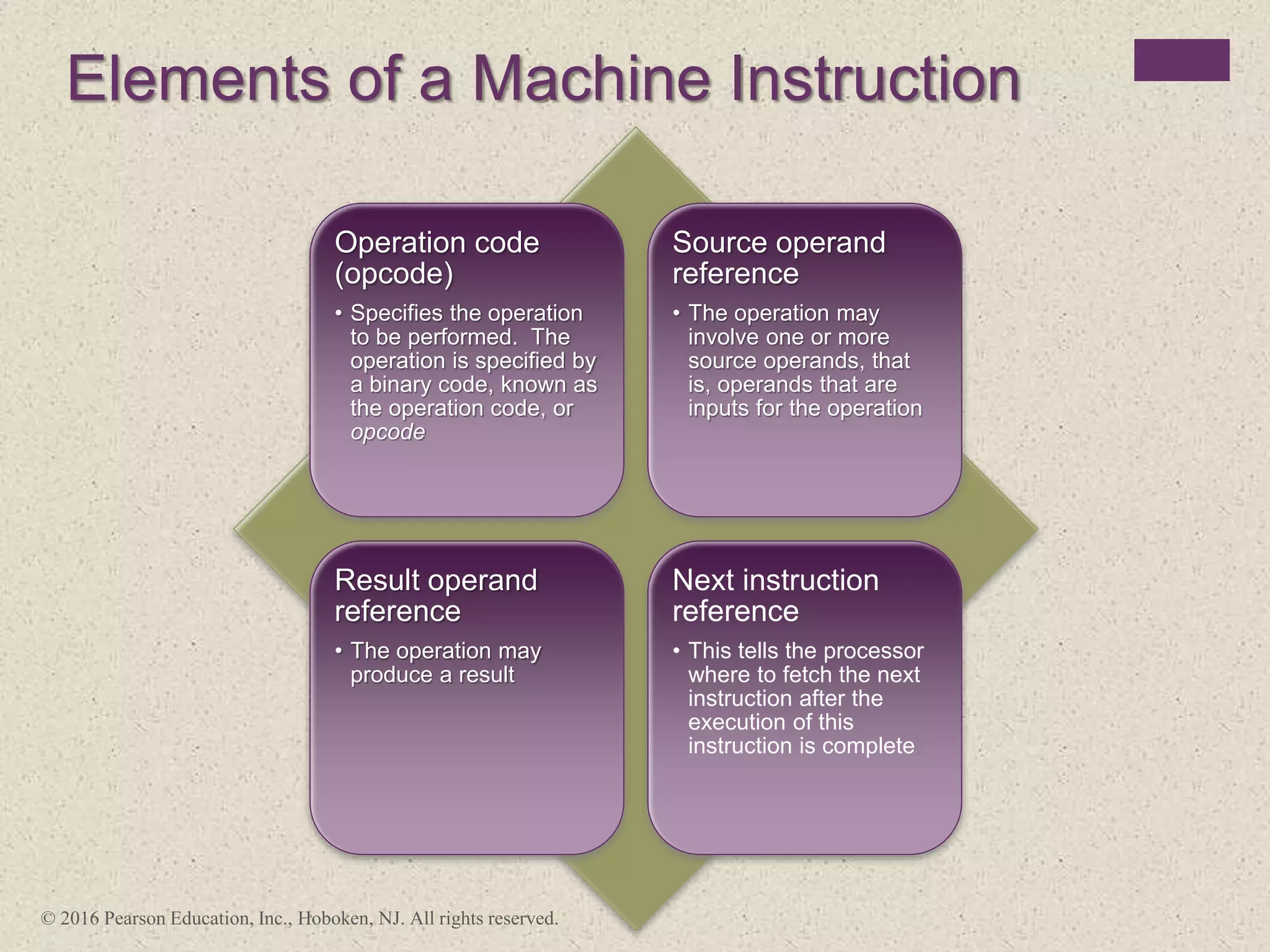

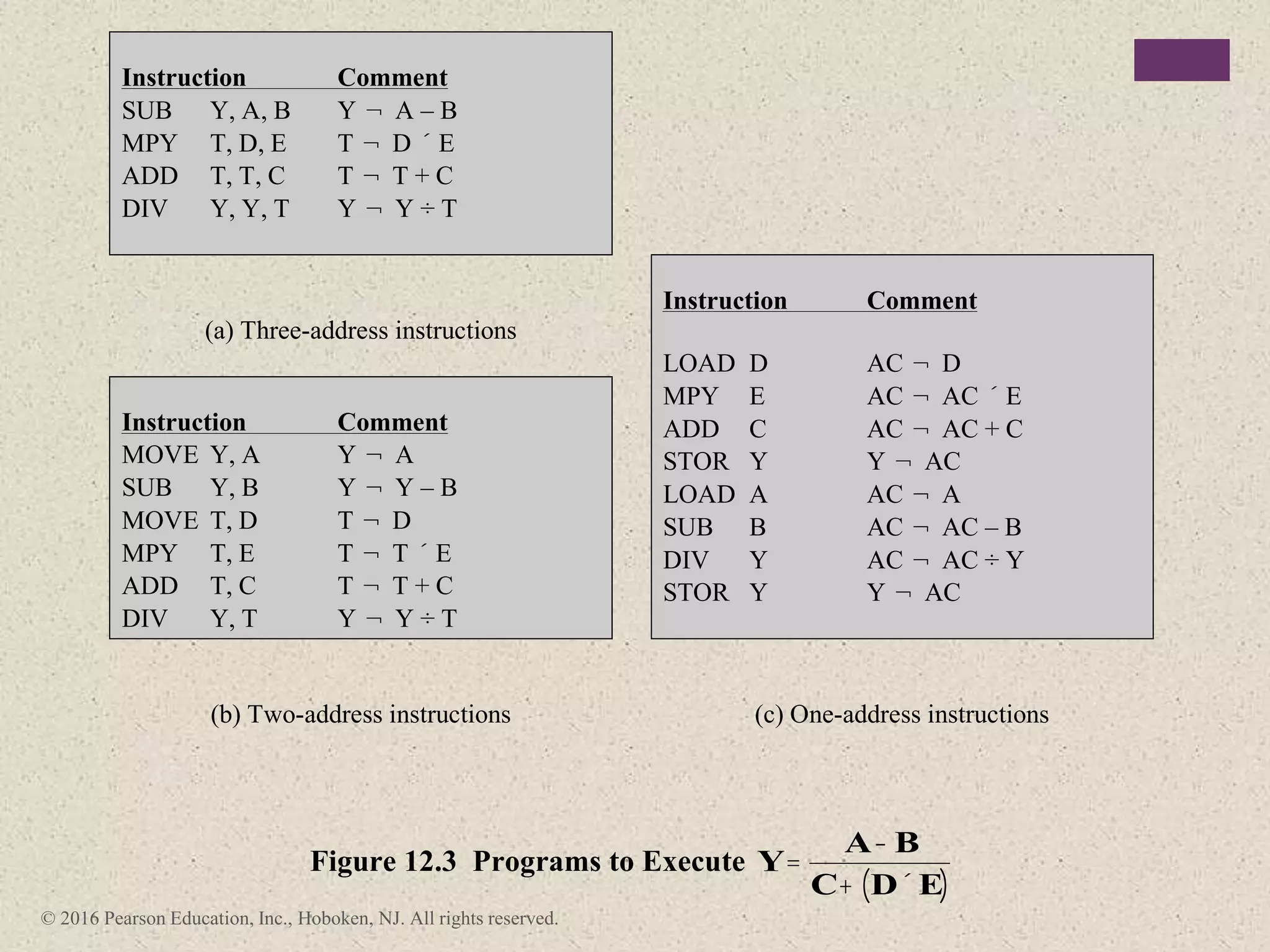

1) Machine instructions contain an operation code that specifies the operation to be performed, as well as references to source and result operands.

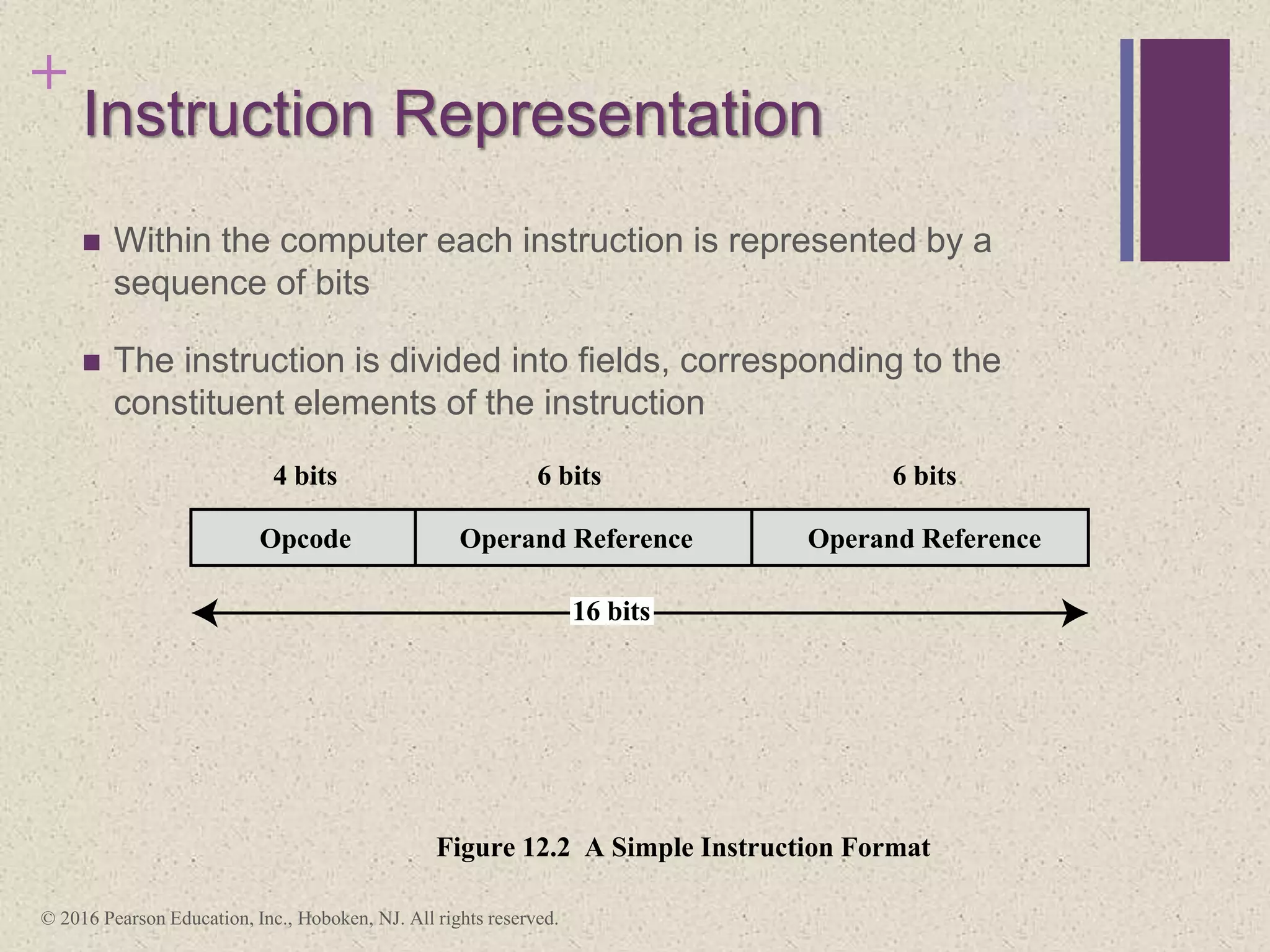

2) Each instruction is represented by a sequence of bits divided into fields corresponding to the instruction elements.

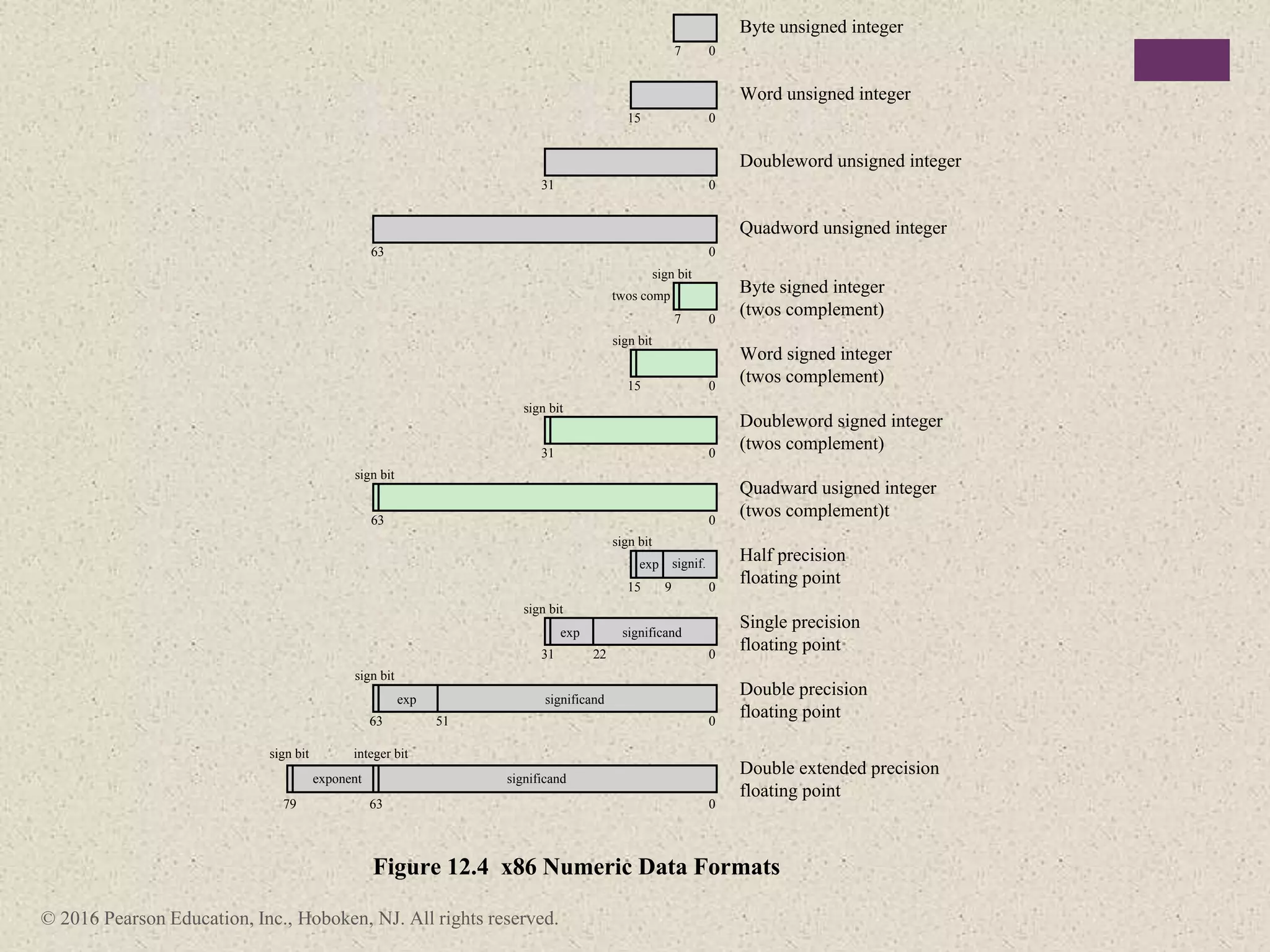

3) Common data types that can be used as operands include numbers, characters, and logical data represented as bit strings. Numeric formats can be integer, floating point, or packed decimal.