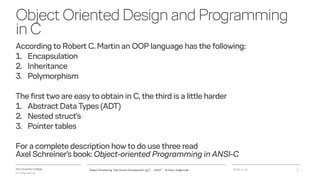

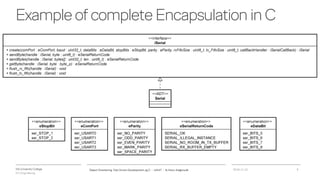

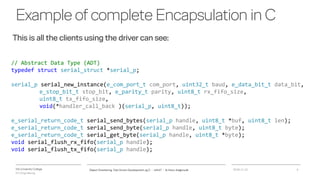

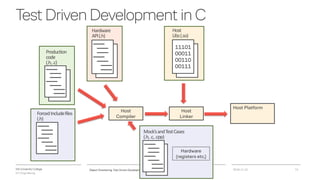

This document discusses challenges with hardware-near programming and proposes solutions like object-oriented design, test-driven development, and mocking hardware for testing in C. It provides examples of encapsulating hardware registers in C and writing tests that check register values and function outputs without the physical hardware. The document concludes that while setting up the tools is an initial investment, TDD is possible and helps create safe, maintainable low-level software.

![VIA University College

ICT-Engineering

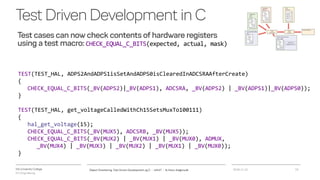

TestDrivenDevelopmentinC

All what’s needed to cheat the toolchain for the ATMEGA2560 MCU:

2018-11-21Object Orientering, Test Driven Development og C - InfinIT - Ib Havn, iha@via.dk 13

#include <stdint.h>

#define __AVR_LIBC_DEPRECATED_ENABLE__

#define __AVR_ATmega2560__

#define _AVR_SFR_DEFS_H_ 1

// 0x136 is highest address of registers in ATMEGA2560

#define _HIGHEST_REGISTER_ADD0x136

// These global variables (fake hardware registers) needs to be accessible from both C and C++

// Therefore they must be declared in C scope if it is the C++ compiler that access

#ifdef __cplusplus

extern "C" {

#endif

extern uint8_t __avr_reg[_HIGHEST_REGISTER_ADD];

#ifdef __cplusplus

}

#endif](https://image.slidesharecdn.com/objectorienteringtestdrivendevelopmentogc-190101171302/85/Object-orientering-test-driven-development-og-c-13-320.jpg)

![VIA University College

ICT-Engineering

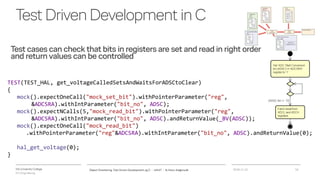

TestDrivenDevelopmentinC

All what’s needed to cheat the toolchain for an ATMEGA2560 MCU:

2018-11-21Object Orientering, Test Driven Development og C - InfinIT - Ib Havn, iha@via.dk 14

// Macros to access the fake hardware registers

#define _SFR_MEM8(mem_addr) (*(uint8_t *)(&__avr_reg[mem_addr]))

#define _SFR_IO8(io_addr) (*(uint8_t *)(&__avr_reg[io_addr]))

// Byte value from bit_no

#define _BV(bit) (1 << (bit))

// Interrupt

#define _AVR_INTERRUPT_H_

#define ISR(vector, ...) void ISR_##vector(void)

#define sei() SREG |= _BV(SREG_I)

#define cli() SREG &= ~_BV(SREG_I)](https://image.slidesharecdn.com/objectorienteringtestdrivendevelopmentogc-190101171302/85/Object-orientering-test-driven-development-og-c-14-320.jpg)