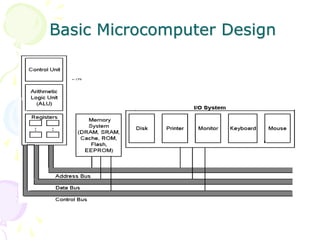

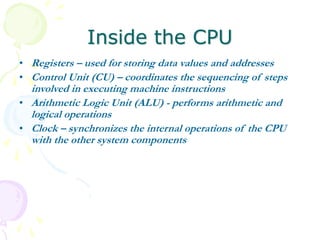

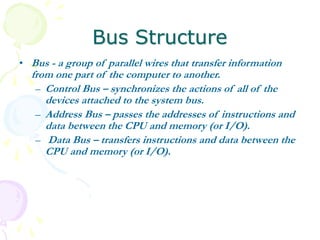

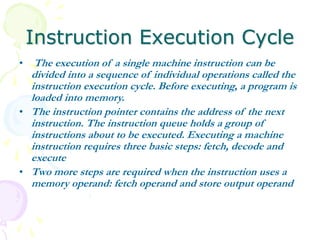

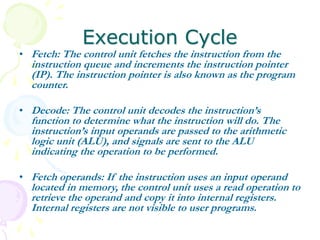

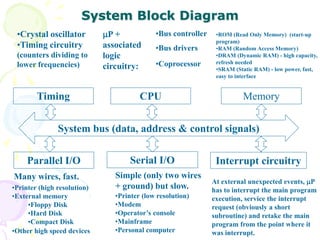

This document provides an overview of microcomputer structure and operation. It describes the basic components of a CPU including registers, control unit, and ALU. It explains the bus structure used to transfer information between components. It also details the instruction execution cycle and how instructions are fetched, decoded, and executed. Finally, it includes a system block diagram showing how various components like memory, I/O devices, and timing circuitry interface with the CPU and bus.

![Rana Mukherji

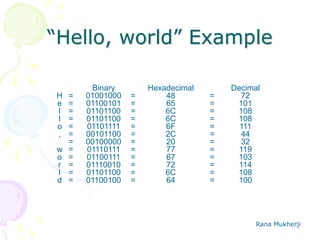

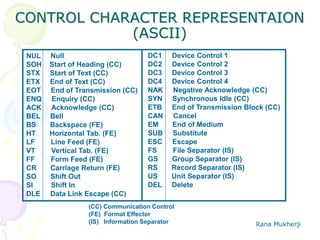

CHARACTER REPRESENTATION

ASCIIASCII (American Standard Code for Information Interchange) Code

Other Binary codes

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

NUL

SOH

STX

ETX

EOT

ENQ

ACK

BEL

BS

HT

LF

VT

FF

CR

SO

SI

SP

!

“

#

$

%

&

‘

(

)

*

+

,

-

.

/

0

1

2

3

4

5

6

7

8

9

:

;

<

=

>

?

@

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

X

Y

Z

[

]

m

n

‘

a

b

c

d

e

f

g

h

I

j

k

l

m

n

o

P

q

r

s

t

u

v

w

x

y

z

{

|

}

~

DEL

0 1 2 3 4 5 6 7

DLE

DC1

DC2

DC3

DC4

NAK

SYN

ETB

CAN

EM

SUB

ESC

FS

GS

RS

US

LSB

(4 bits)

MSB (3 bits)](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-73-320.jpg)

![Rana Mukherji

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-75-320.jpg)

![Rana Mukherji

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL

Most significant bit

Least significant bit](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-76-320.jpg)

![Rana Mukherji

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL

e.g., ‘a’ = 1100001](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-77-320.jpg)

![Rana Mukherji

95 Graphic codes

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-78-320.jpg)

![Rana Mukherji

33 Control codes

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-79-320.jpg)

![Rana Mukherji

Alphabetic codes

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-80-320.jpg)

![Rana Mukherji

Numeric codes

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-81-320.jpg)

![Rana Mukherji

000 001 010 011 100 101 110 111

0000 NULL DLE 0 @ P ` p

0001 SOH DC1 ! 1 A Q a q

0010 STX DC2 " 2 B R b r

0011 ETX DC3 # 3 C S c s

0100 EDT DC4 $ 4 D T d t

0101 ENQ NAK % 5 E U e u

0110 ACK SYN & 6 F V f v

0111 BEL ETB ' 7 G W g w

1000 BS CAN ( 8 H X h x

1001 HT EM ) 9 I Y i y

1010 LF SUB * : J Z j z

1011 VT ESC + ; K [ k {

1100 FF FS , < L l |

1101 CR GS - = M ] m }

1110 SO RS . > N ^ n ~

1111 SI US / ? O _ o DEL

Punctuation, etc.](https://image.slidesharecdn.com/up1-200322133146/85/microprocessor-82-320.jpg)