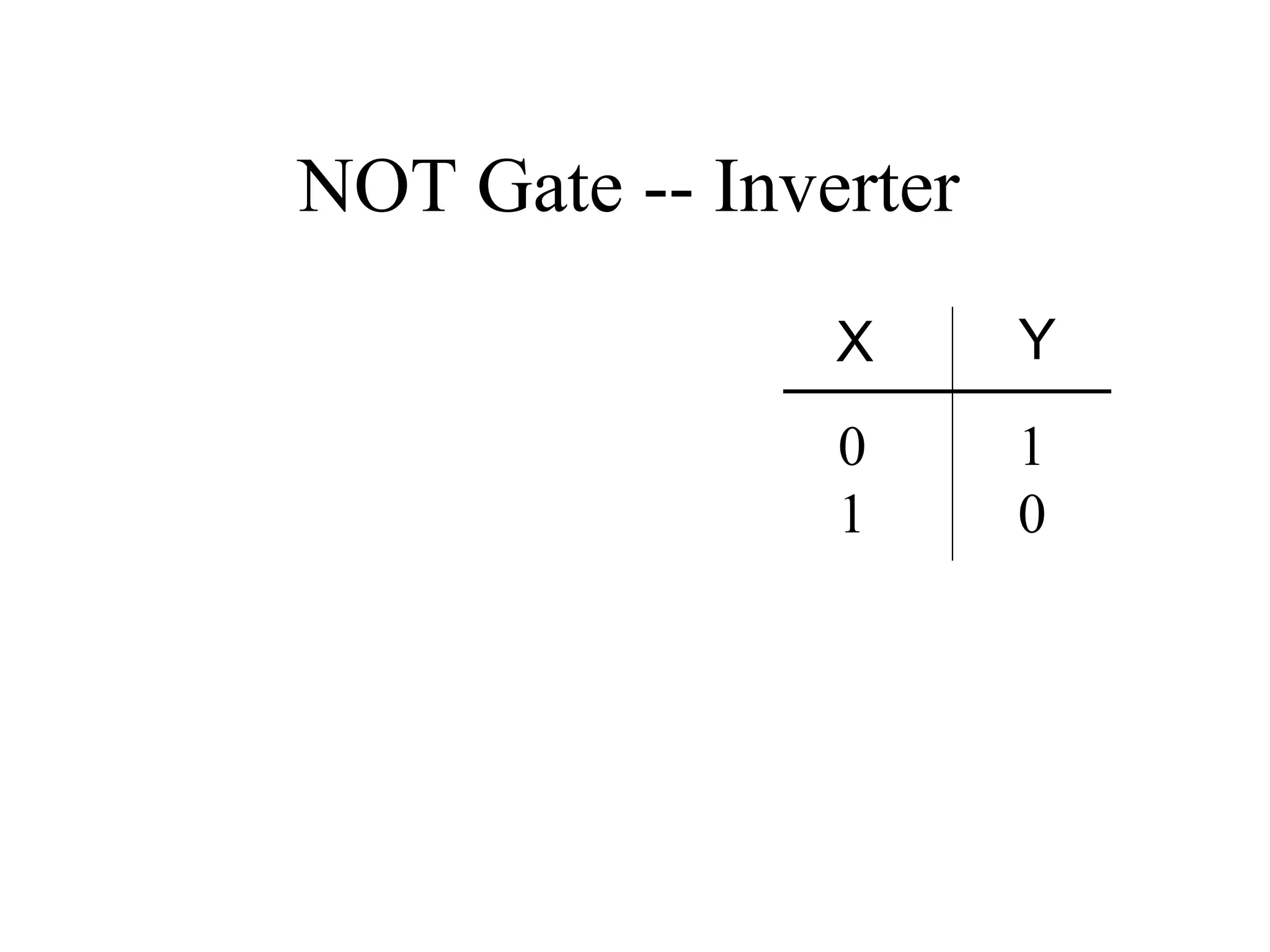

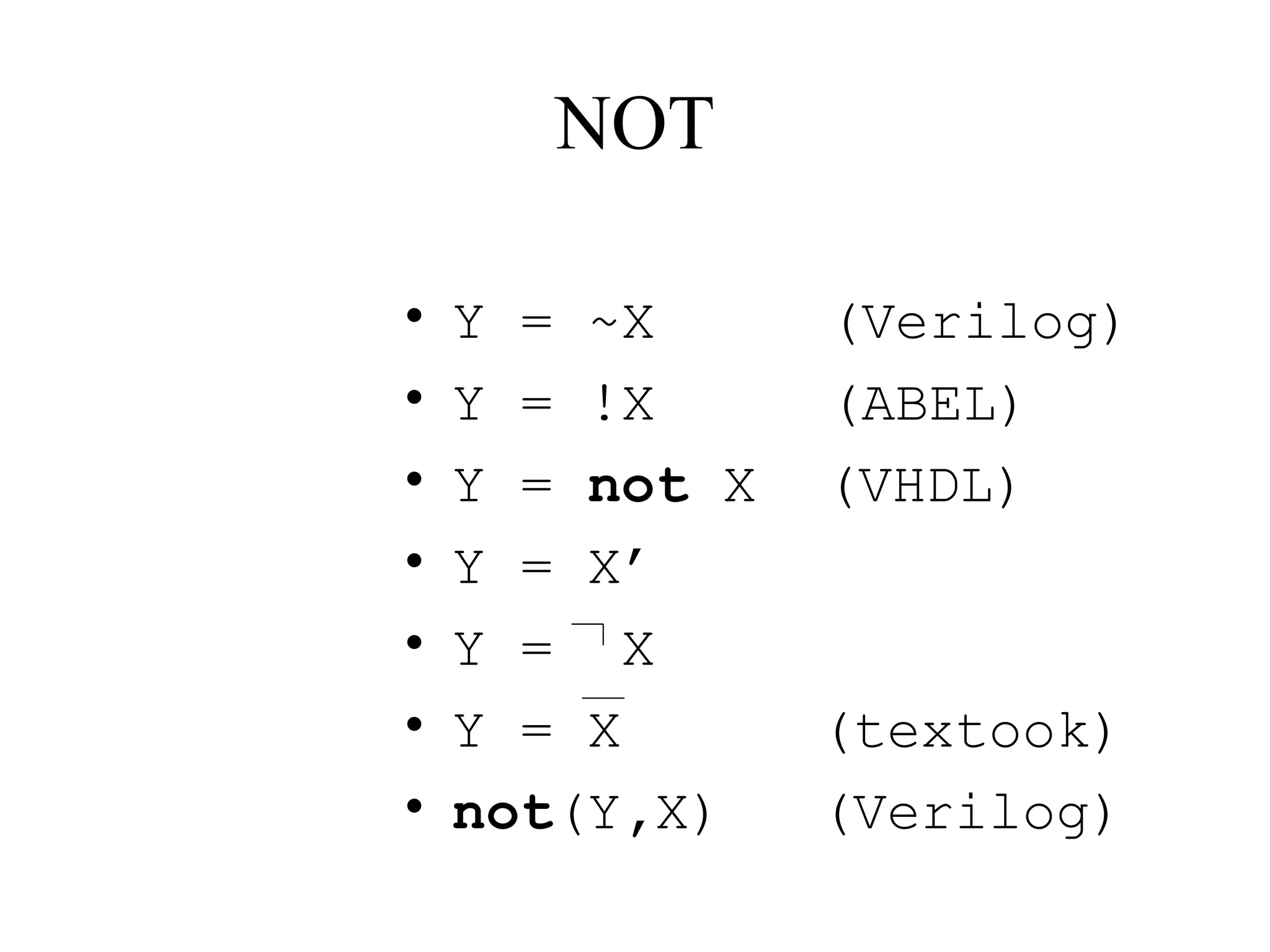

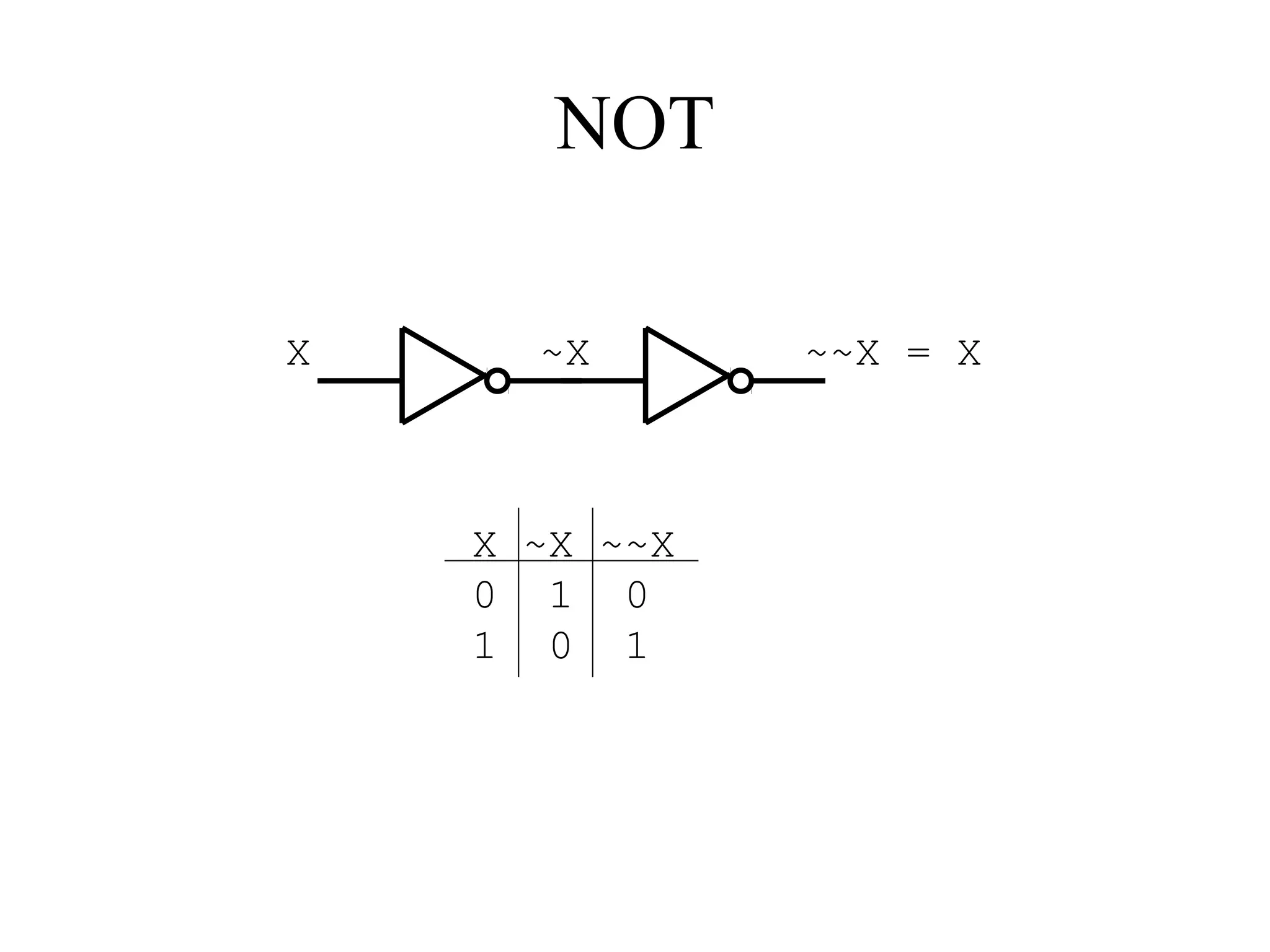

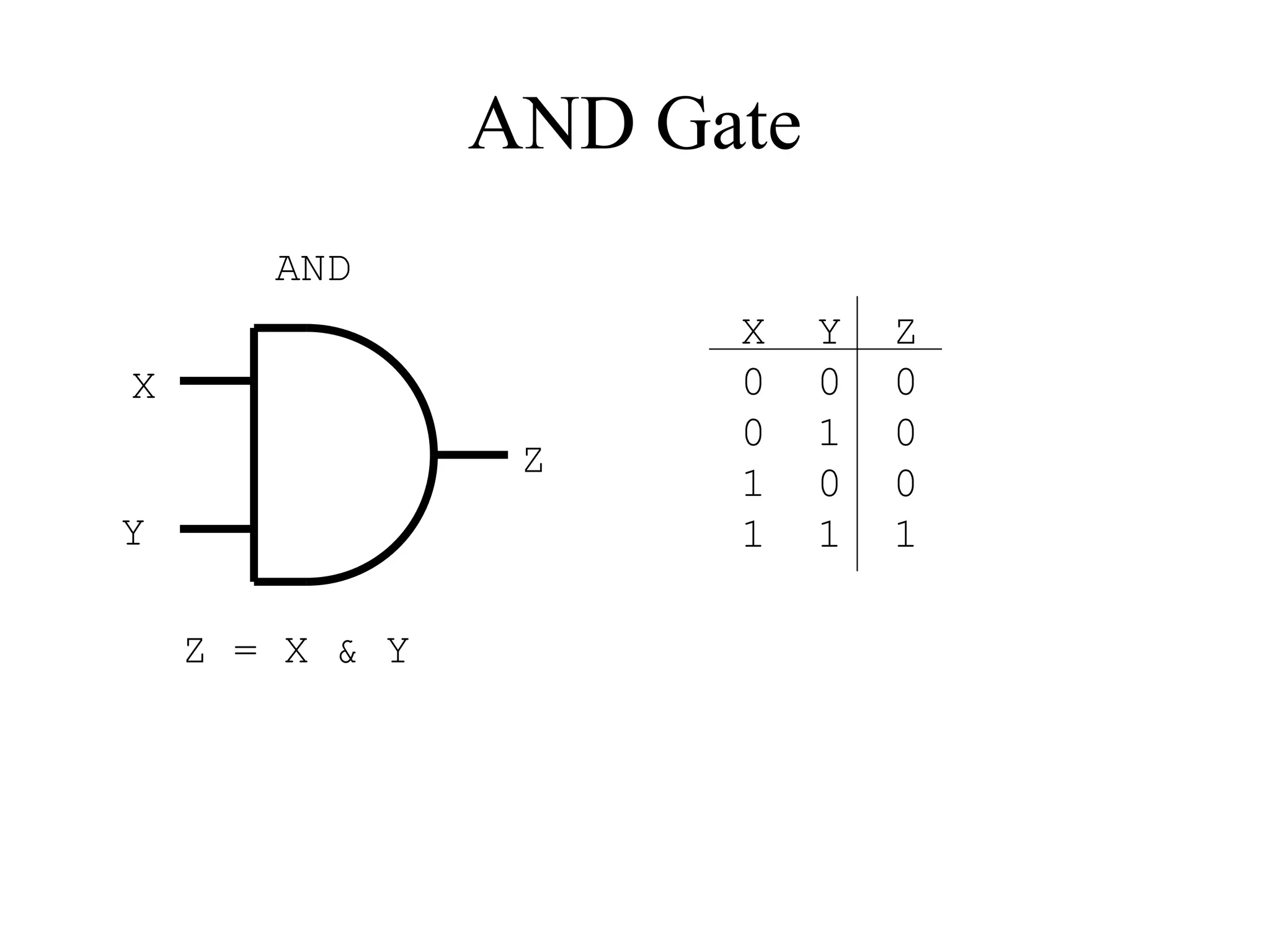

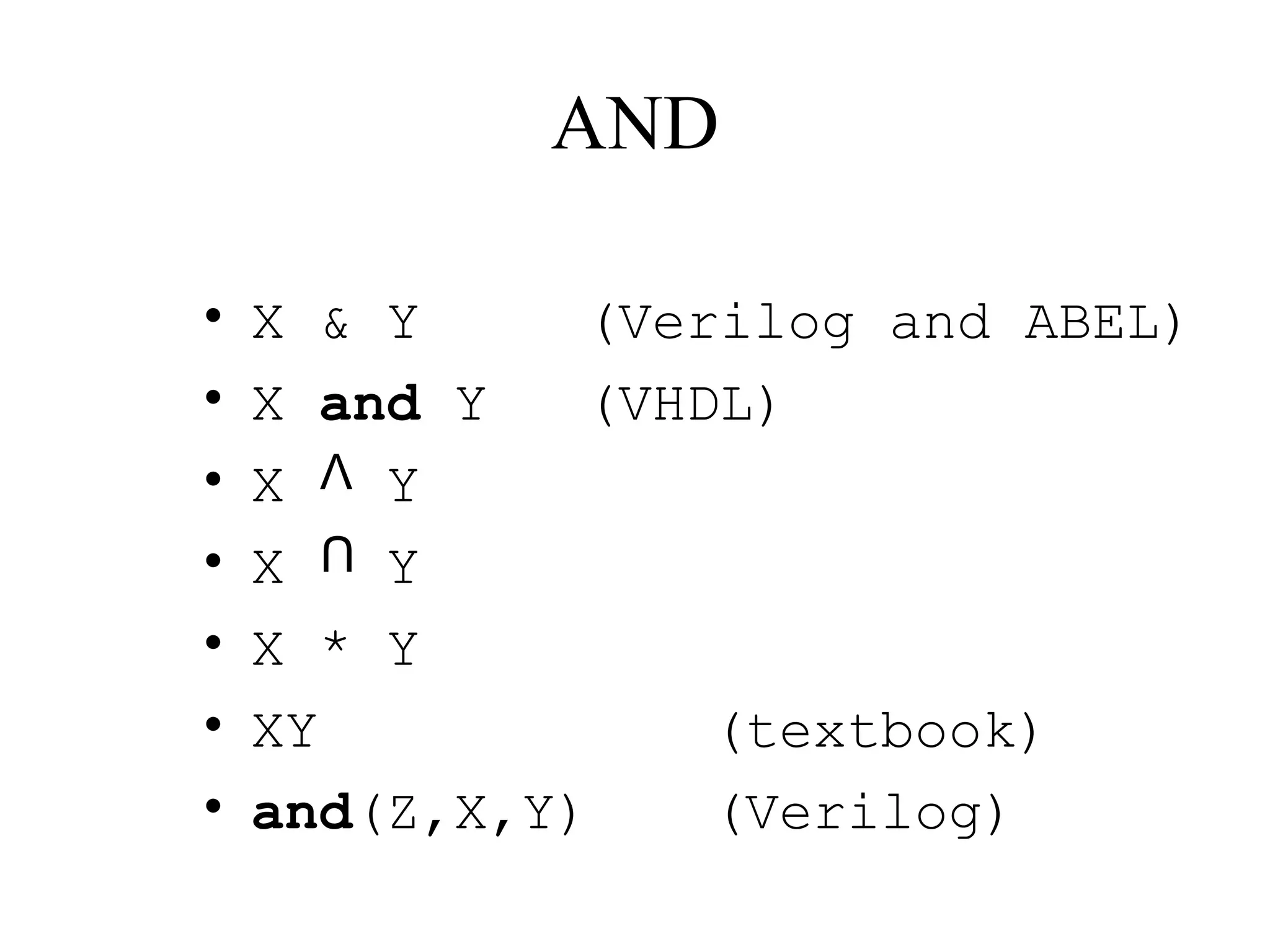

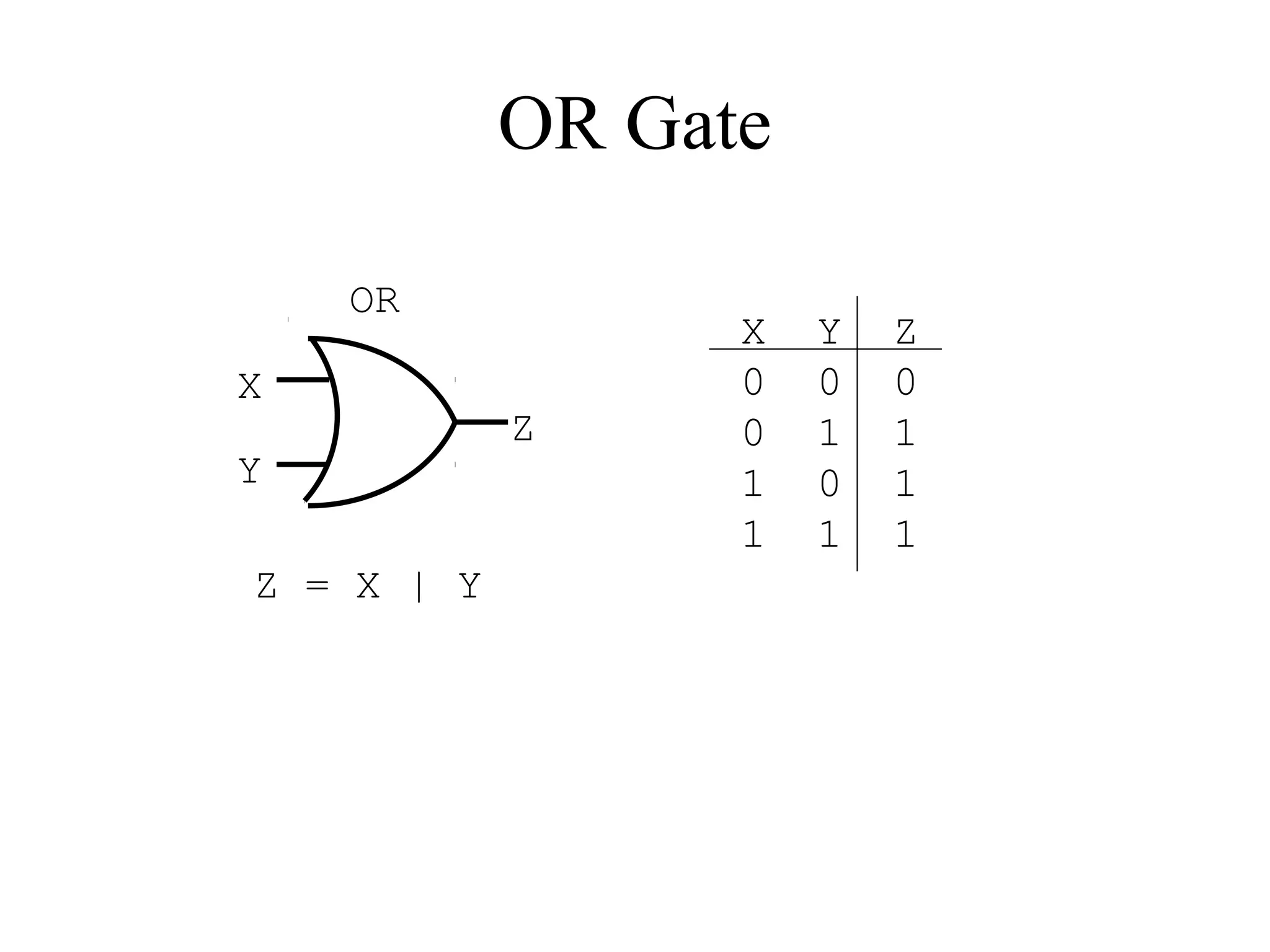

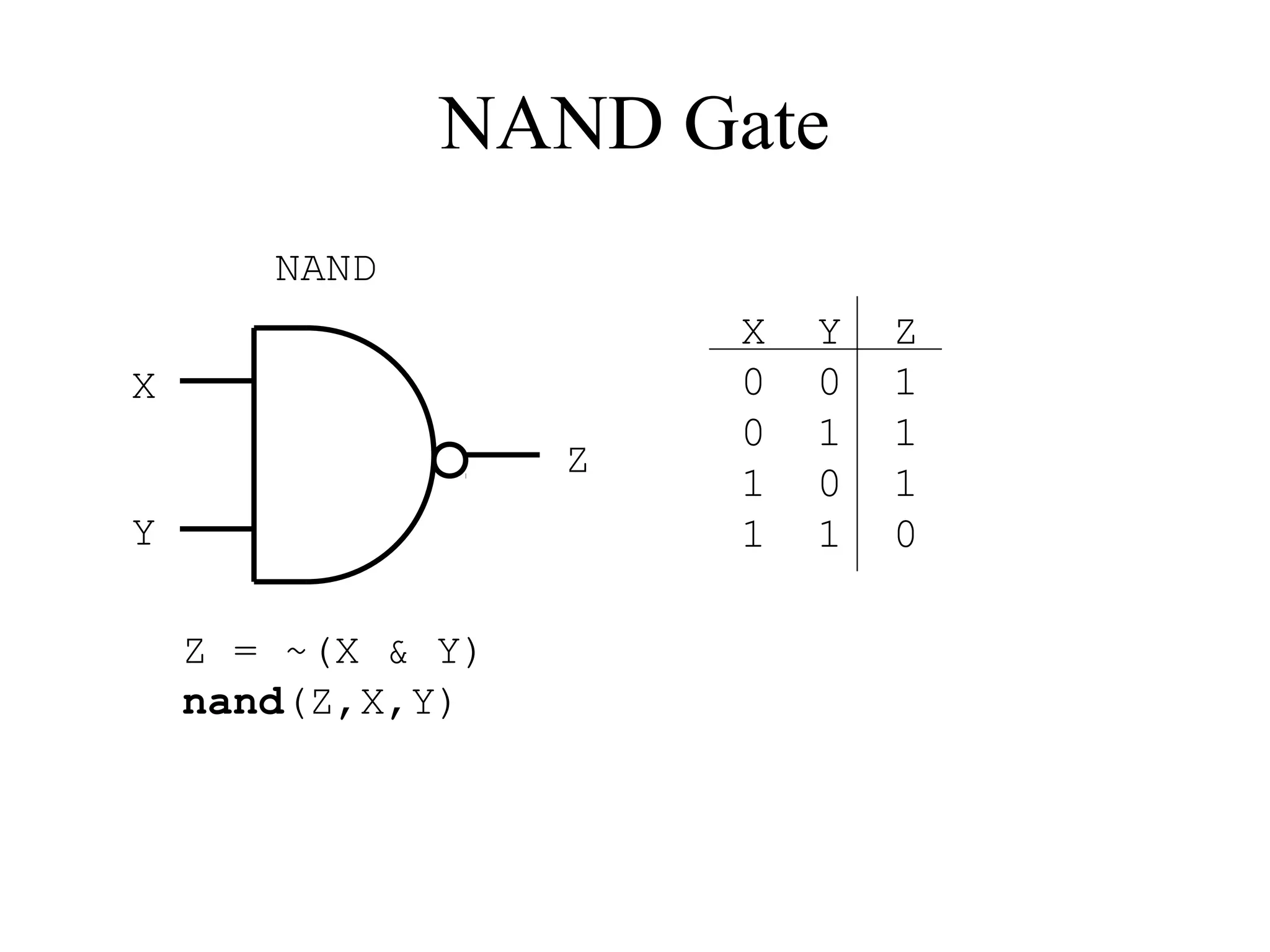

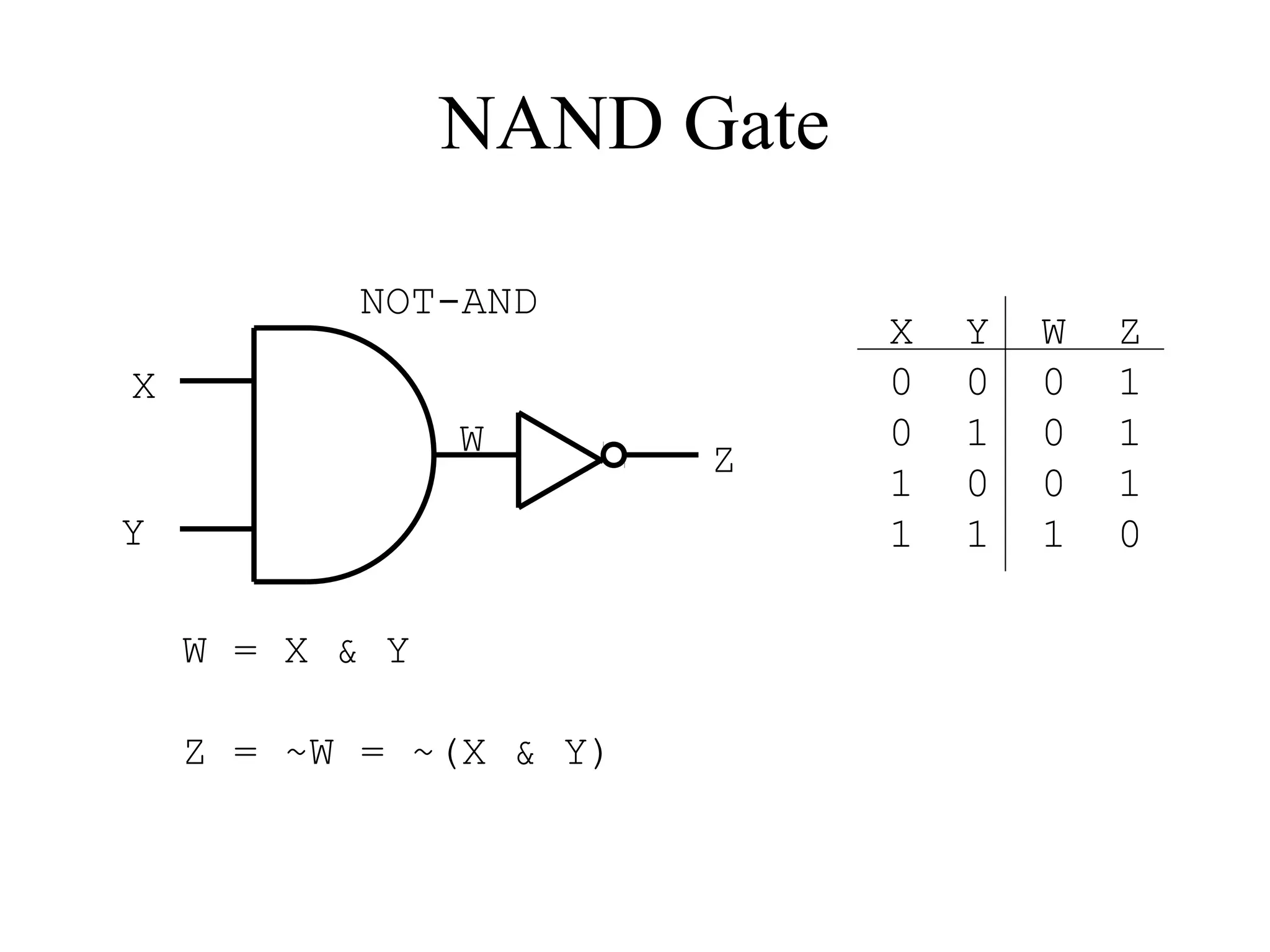

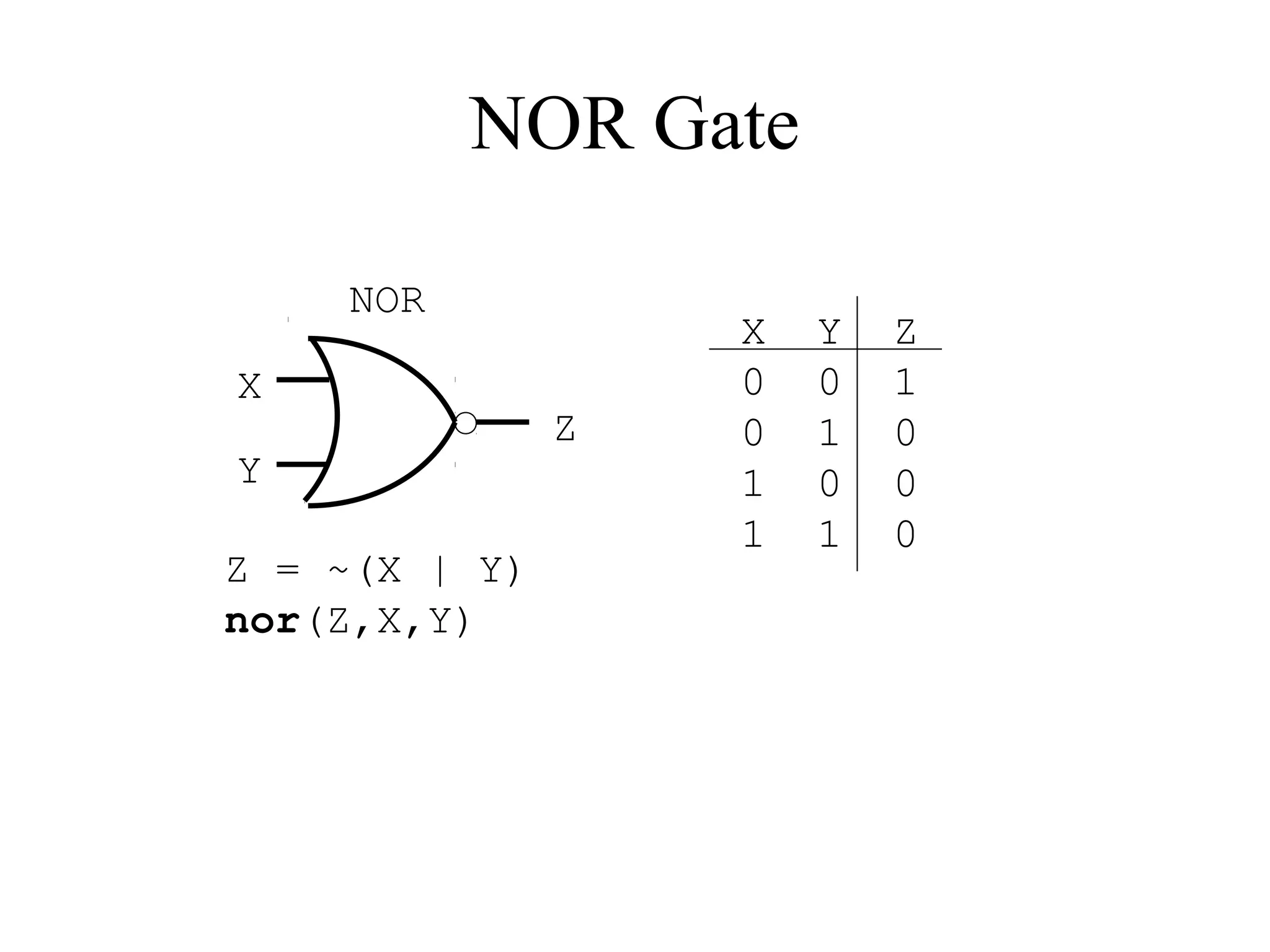

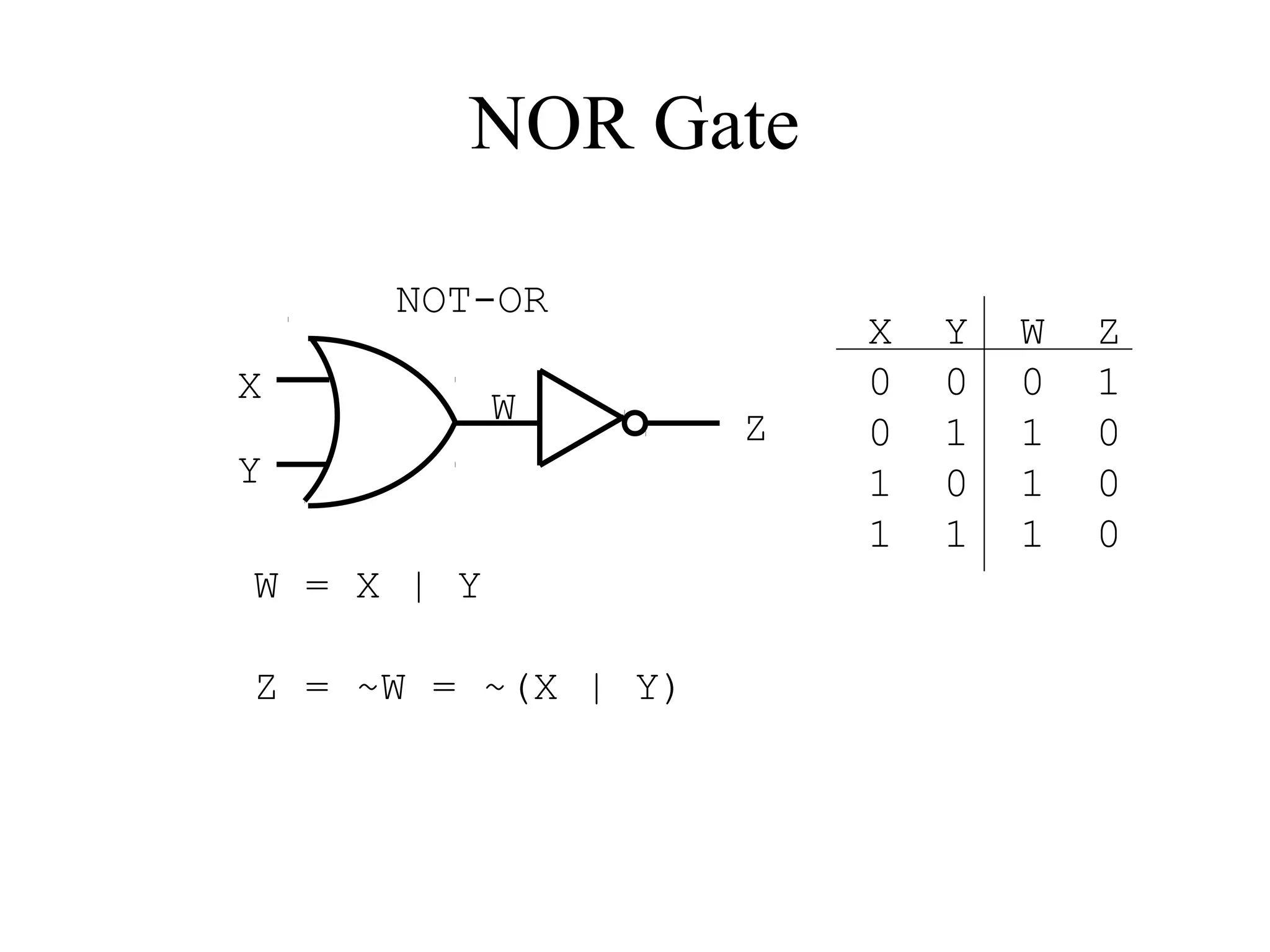

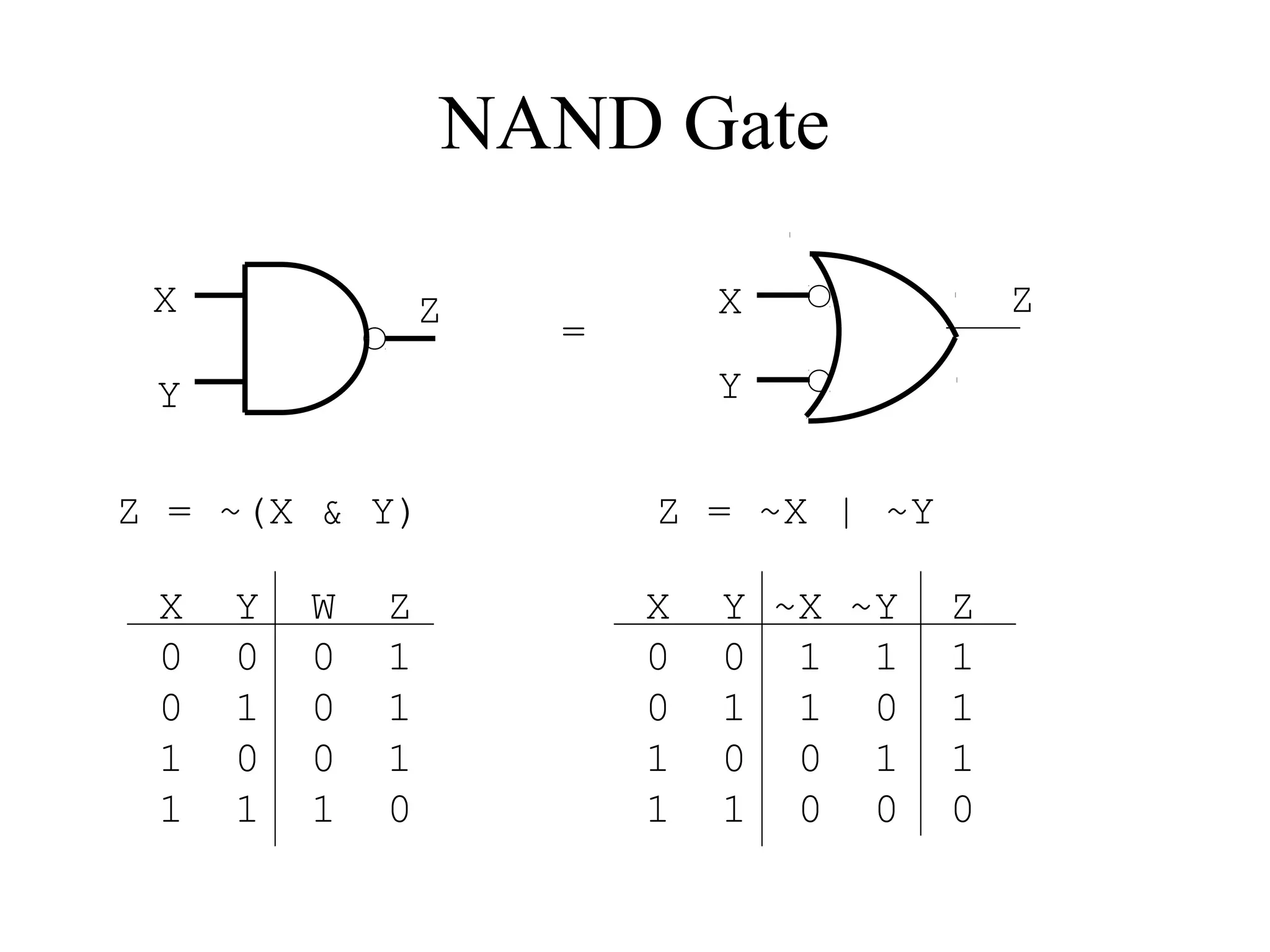

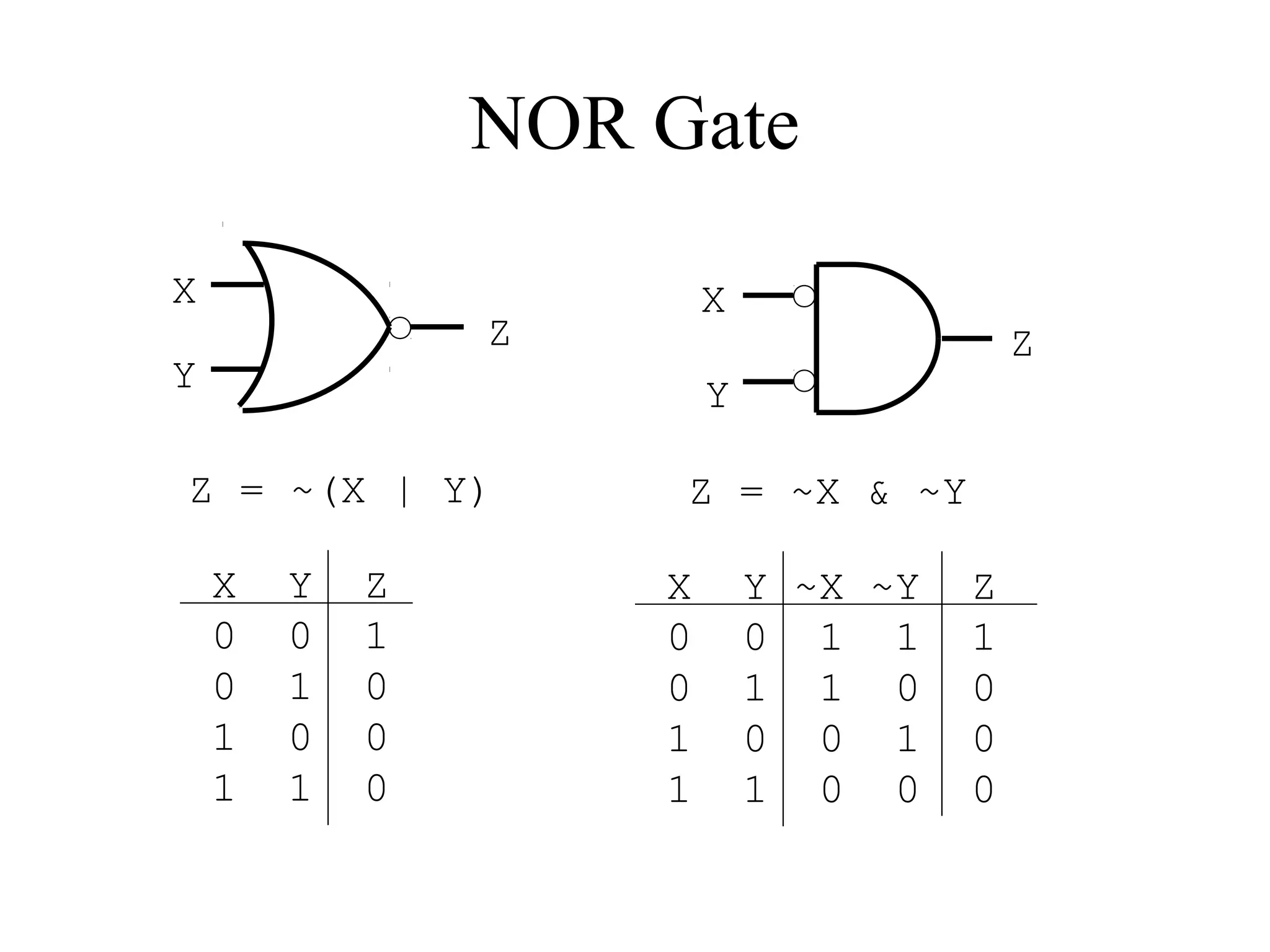

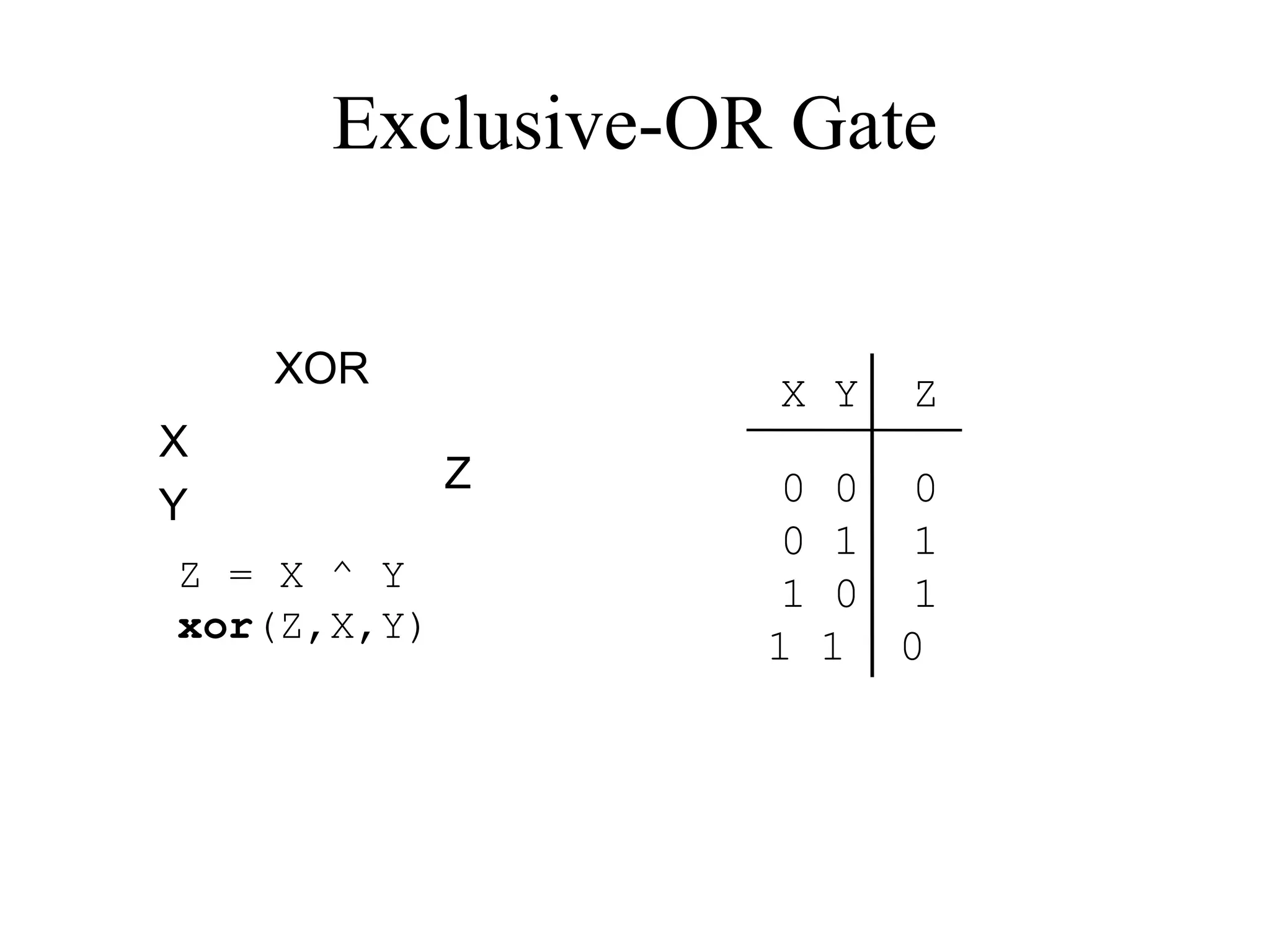

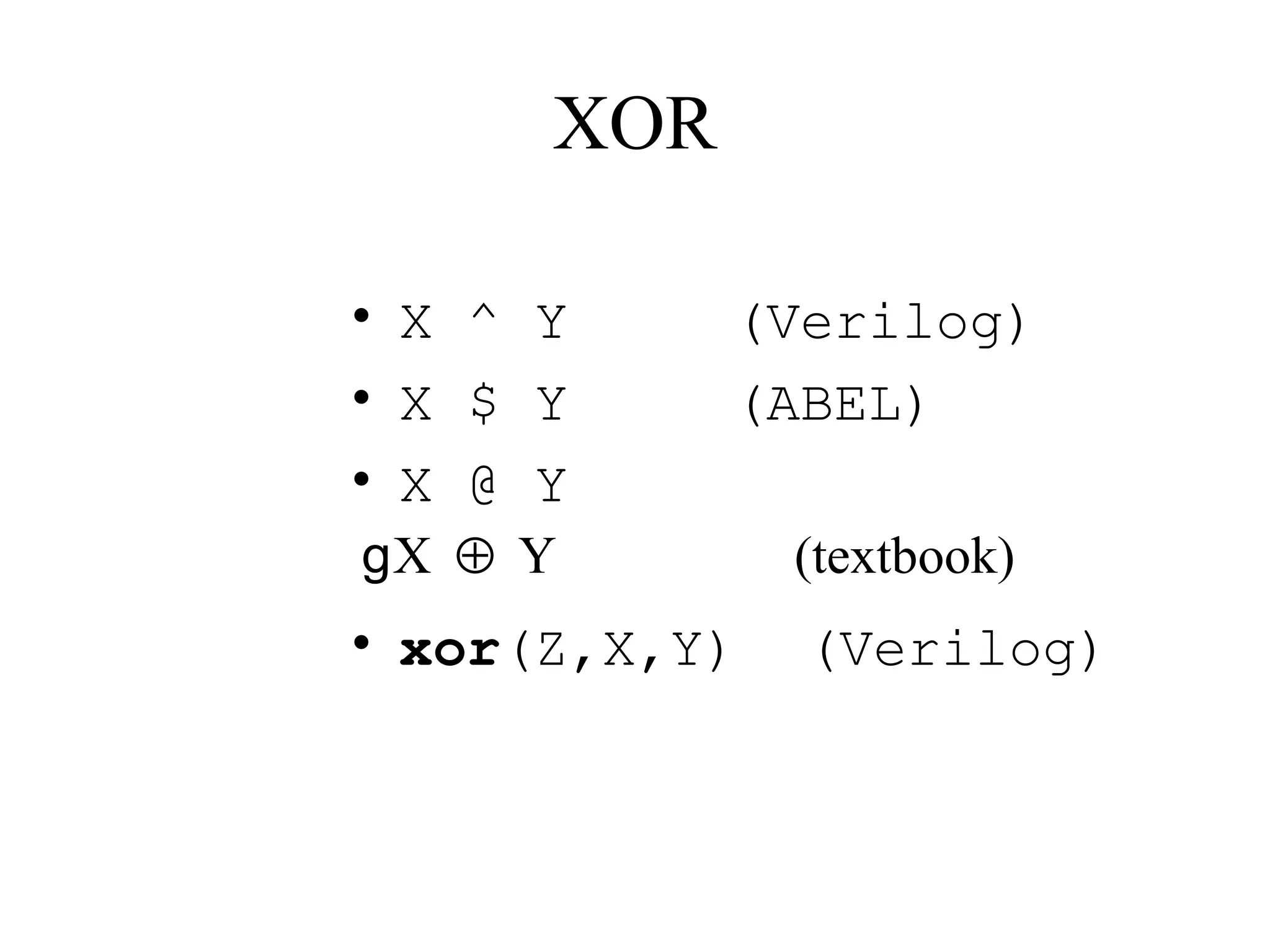

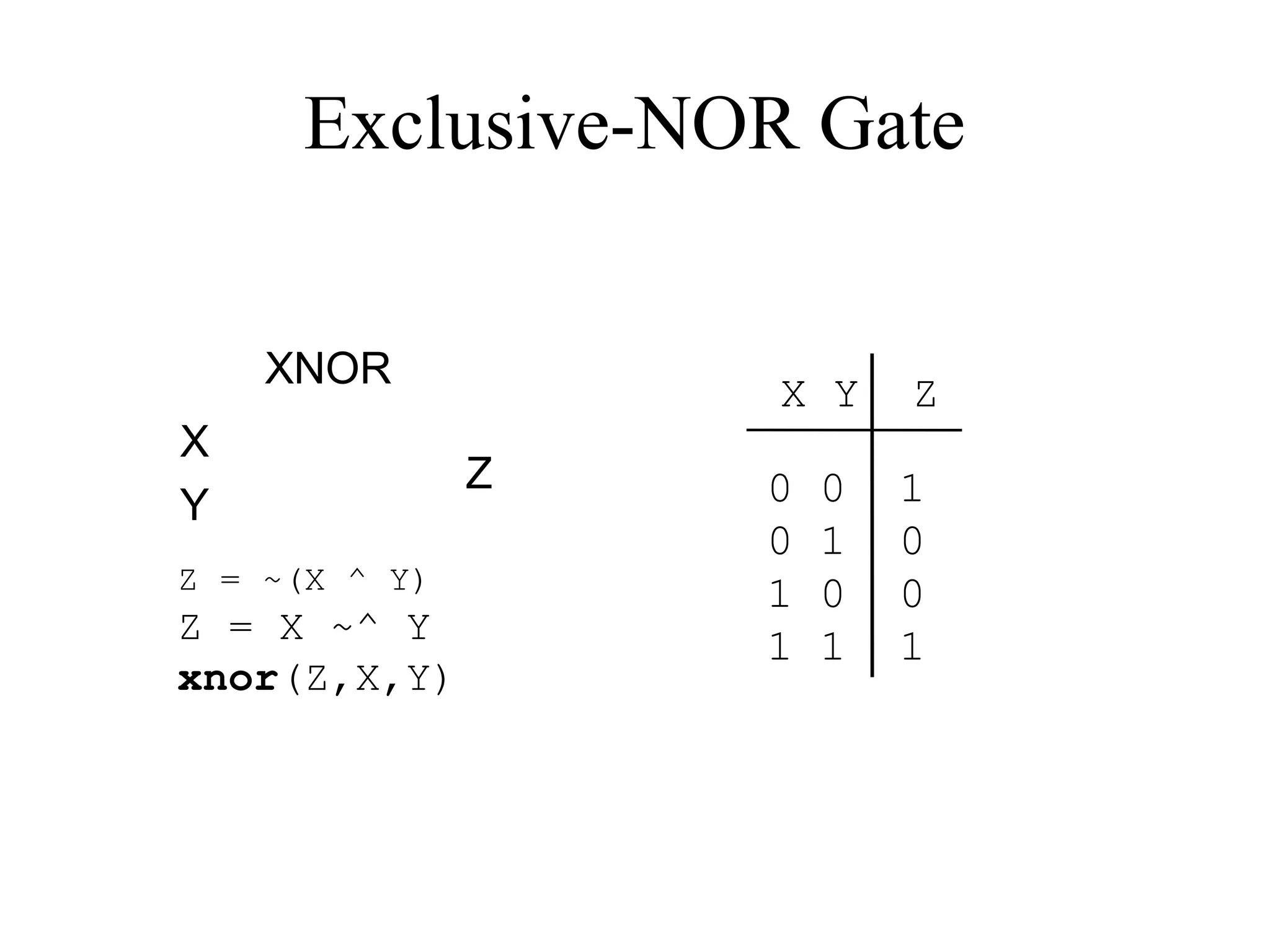

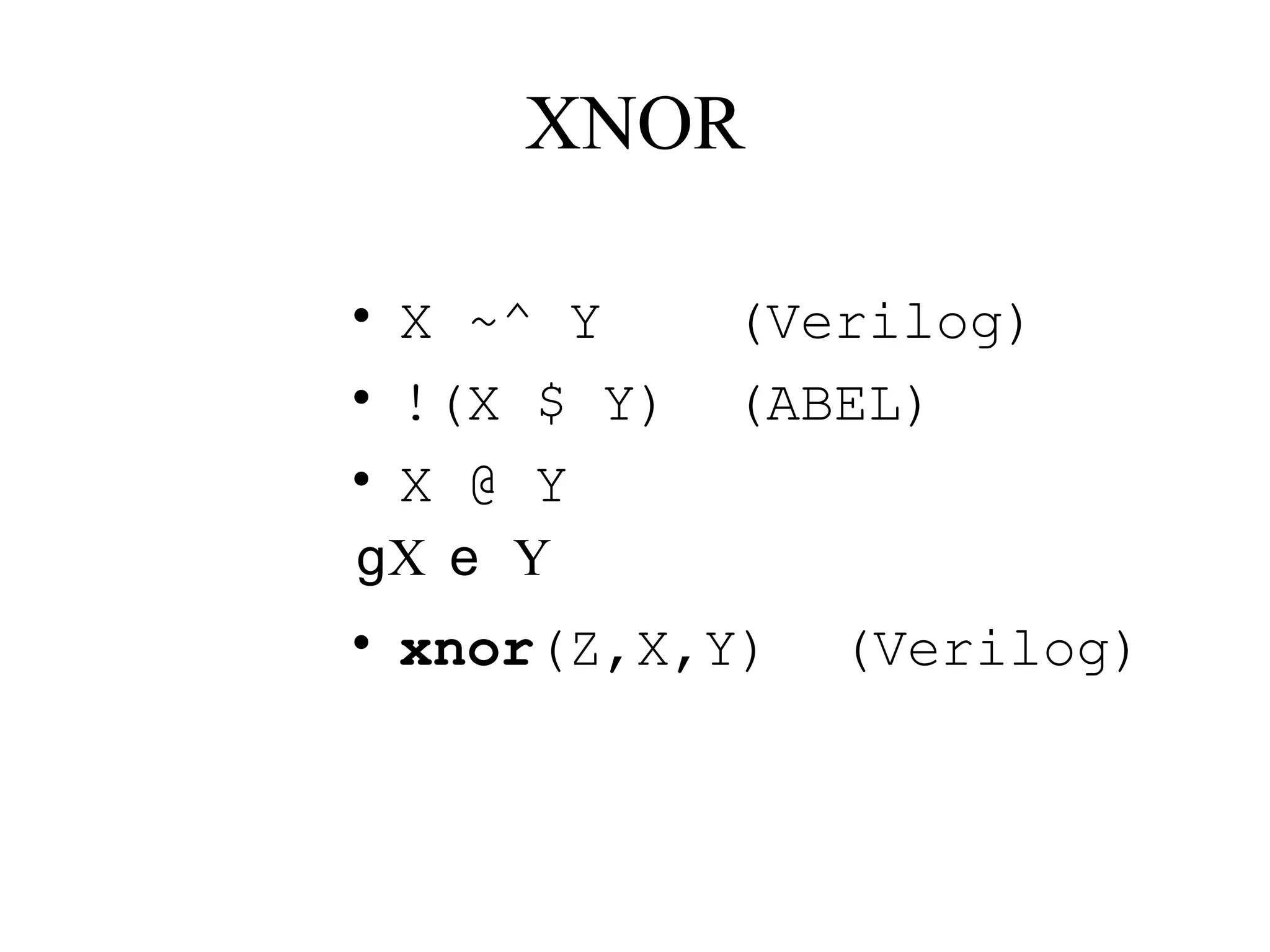

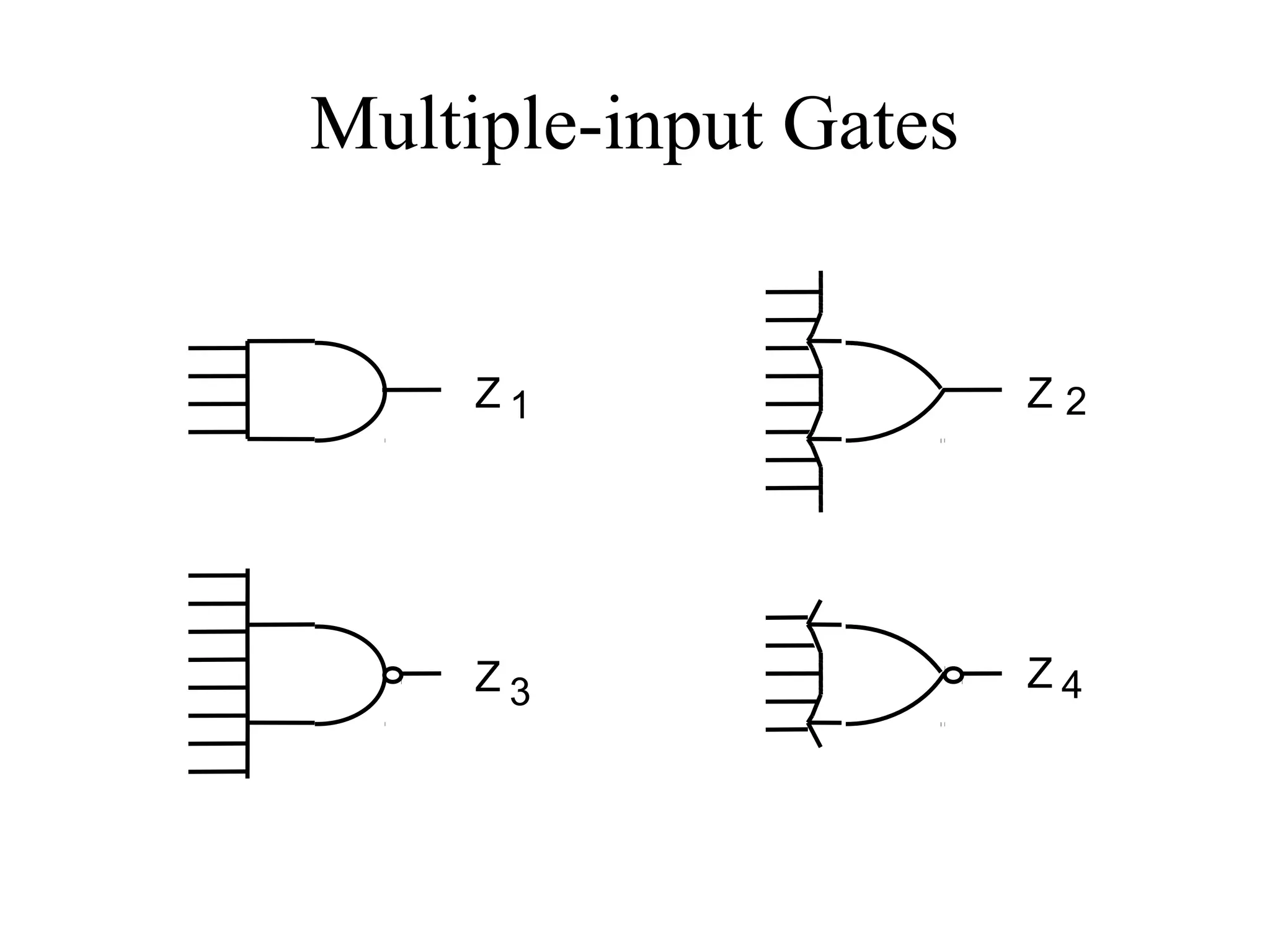

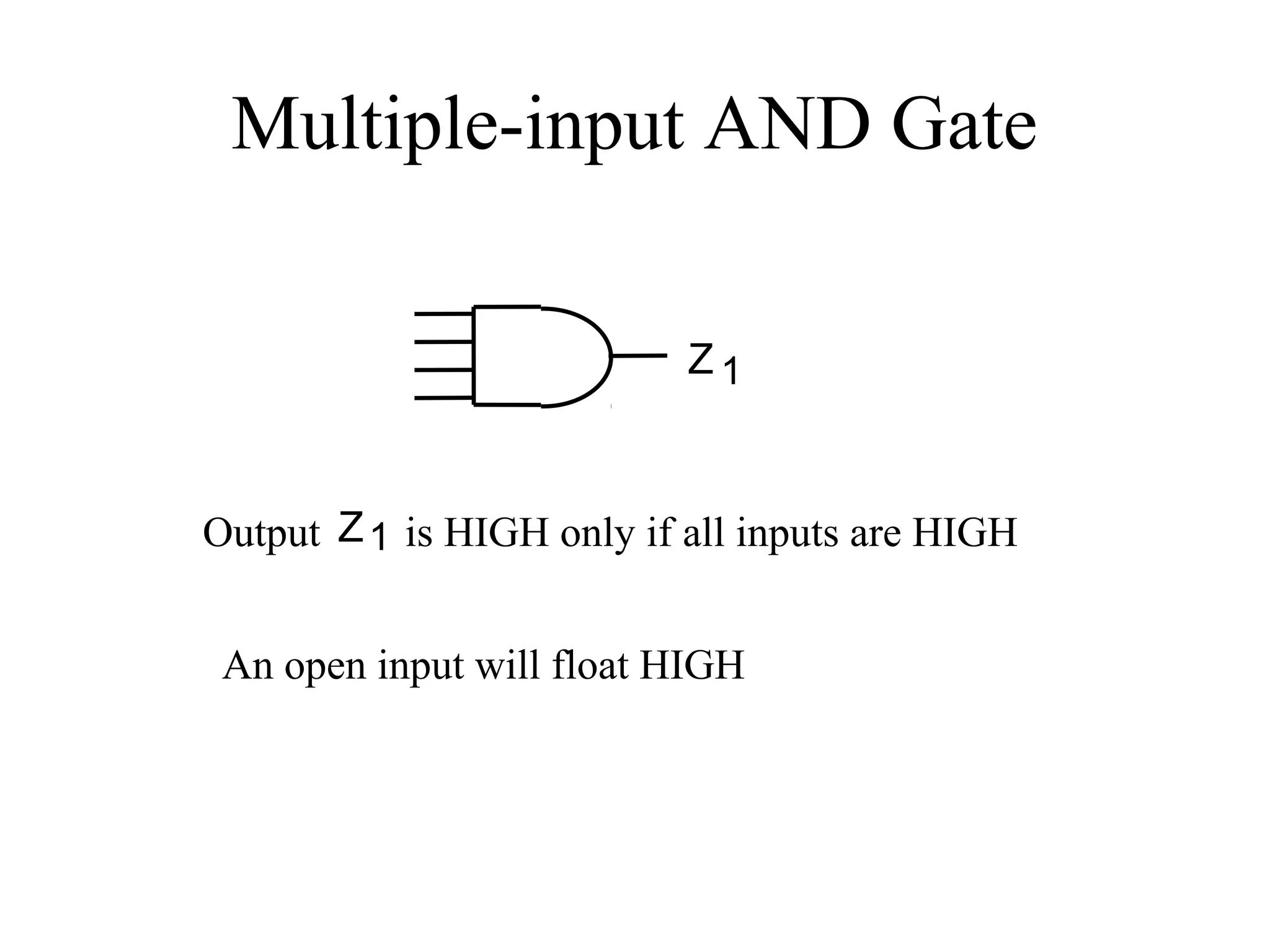

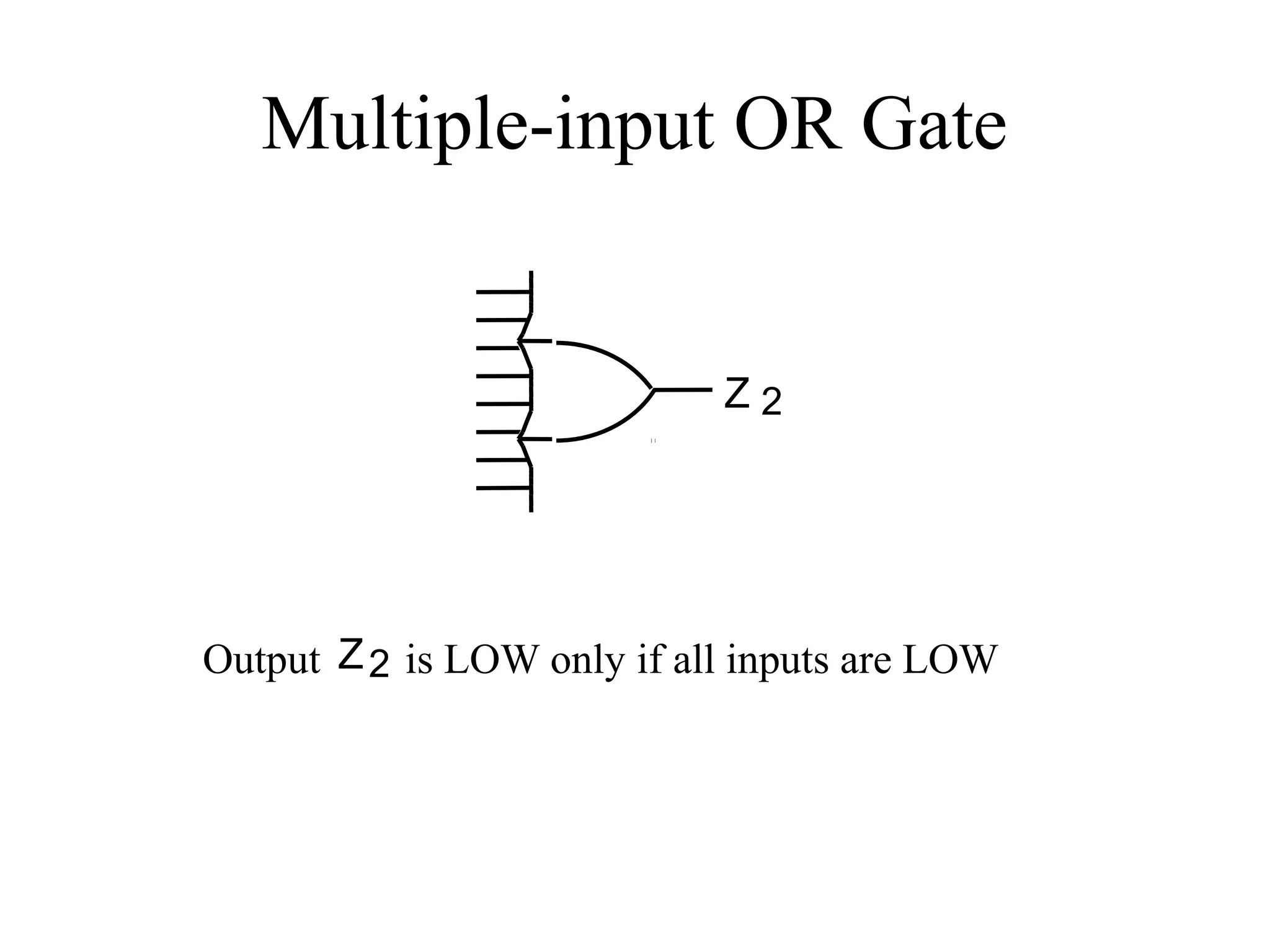

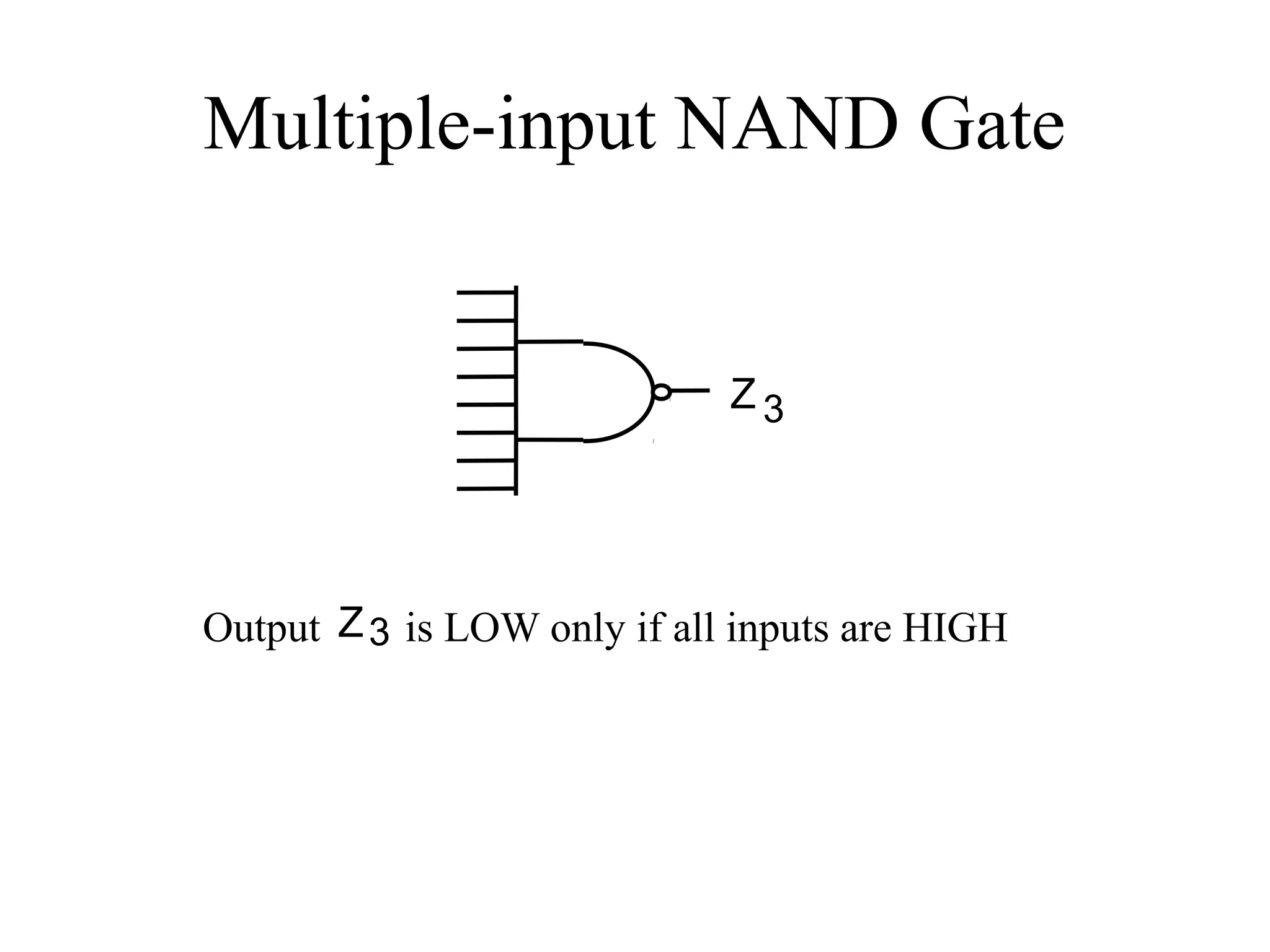

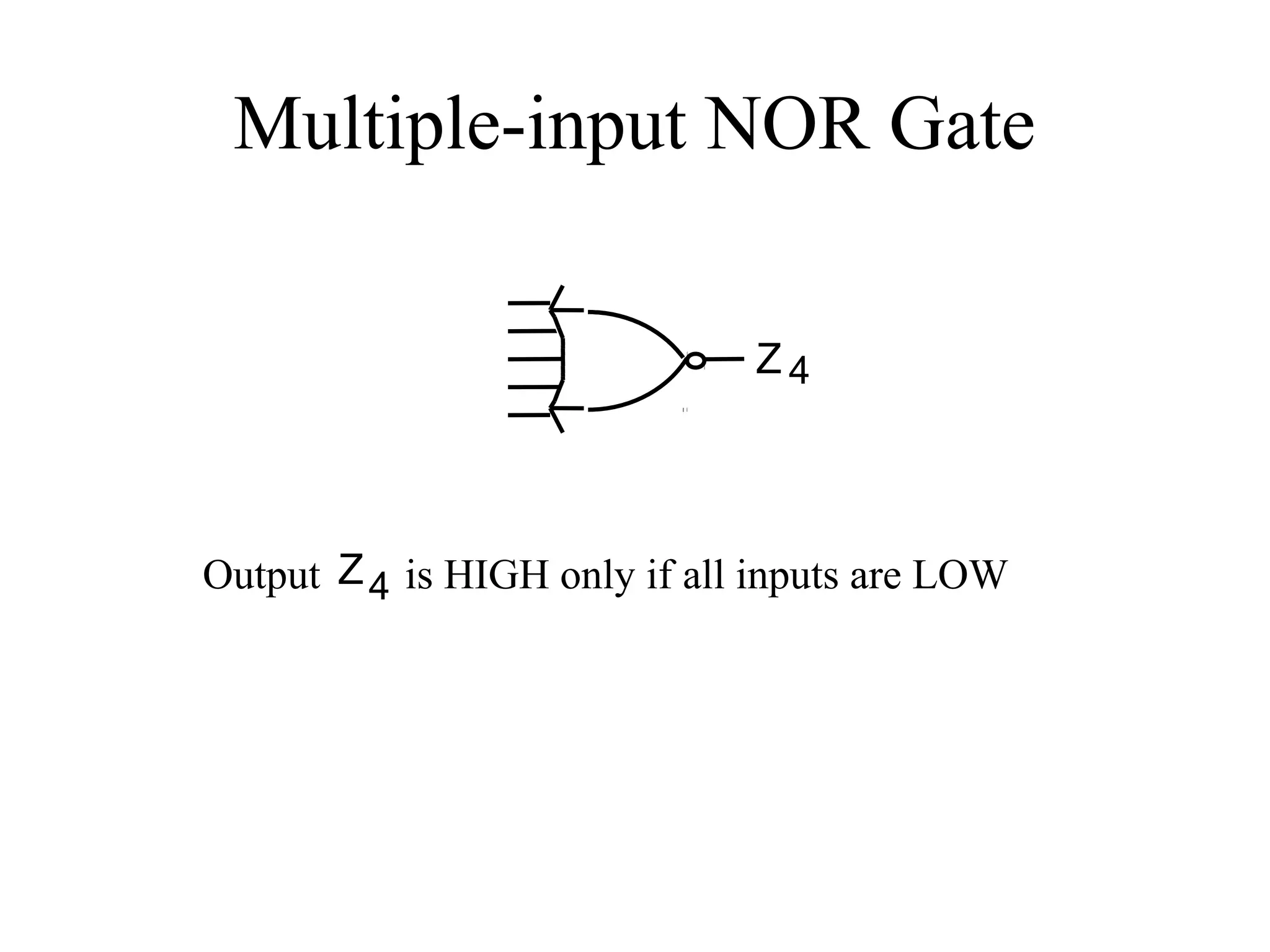

This document provides an overview of basic digital logic circuits including NOT, AND, OR, NAND, NOR, XOR, and XNOR gates. It describes the truth tables and logic expressions for each gate. De Morgan's theorems are explained which allow converting between AND/OR and NAND/NOR logic. Multiple input gates such as AND, OR, NAND and NOR are also introduced. The document references common computer organization and digital design textbooks for additional information.