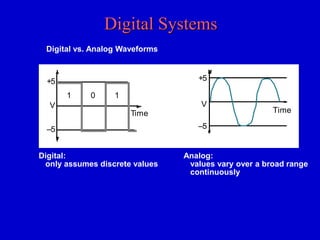

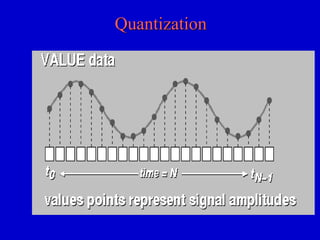

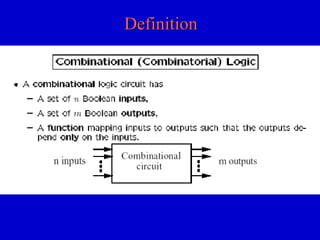

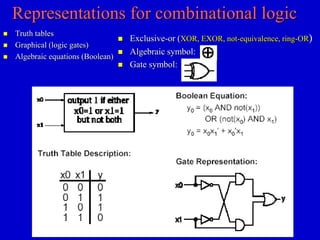

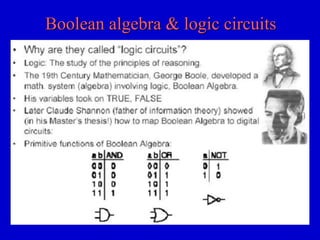

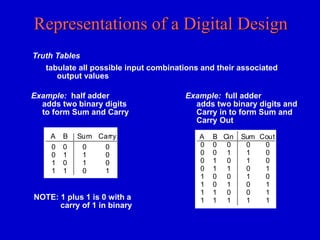

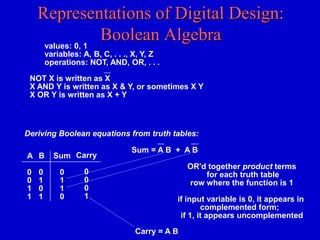

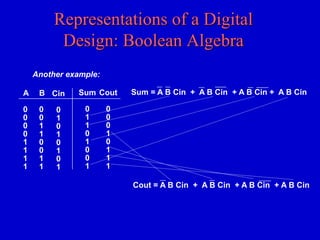

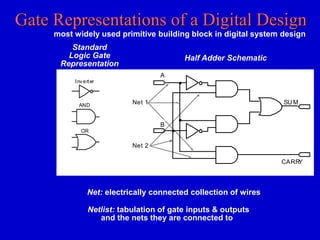

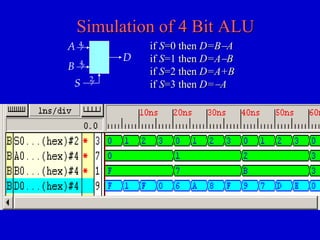

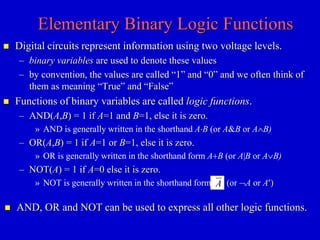

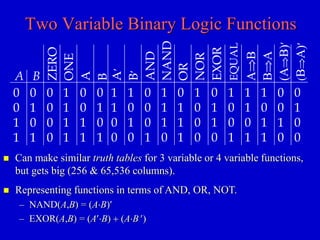

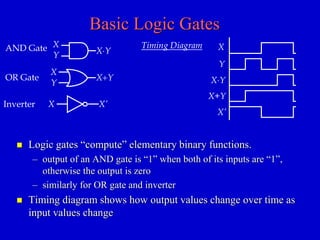

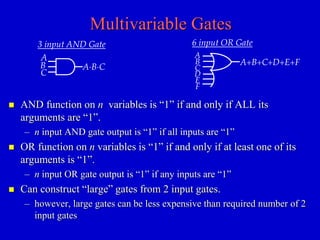

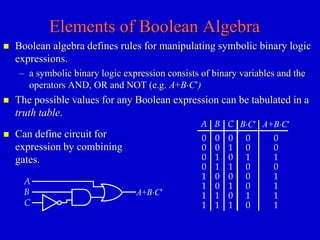

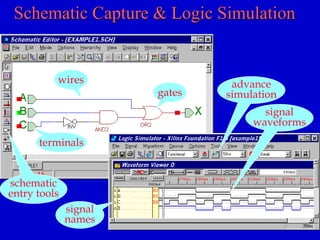

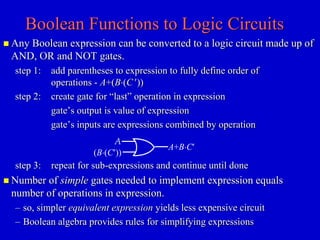

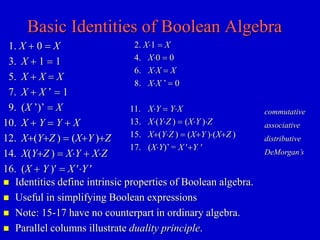

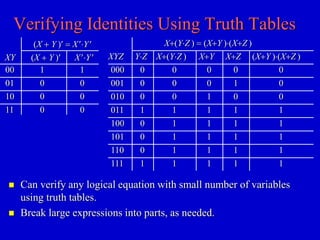

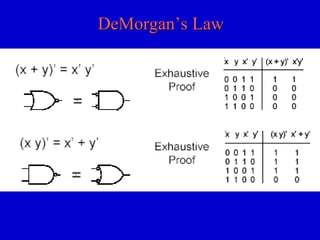

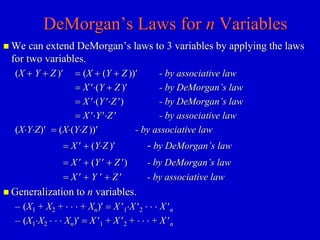

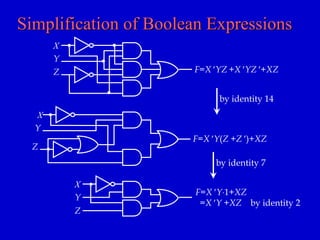

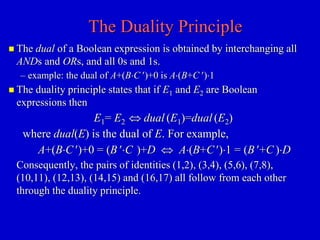

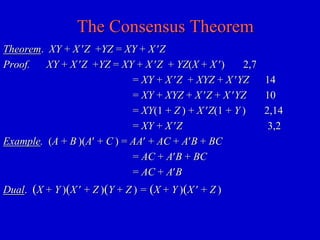

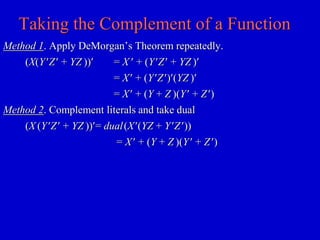

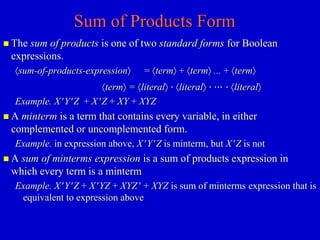

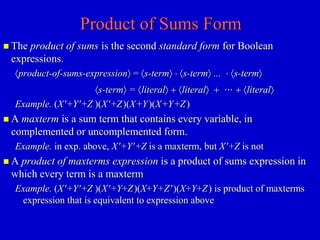

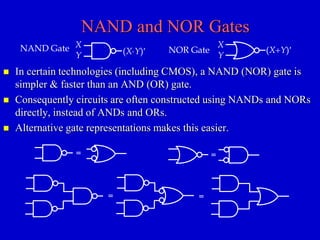

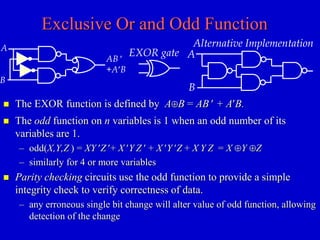

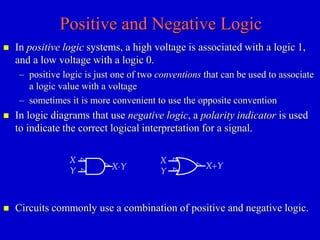

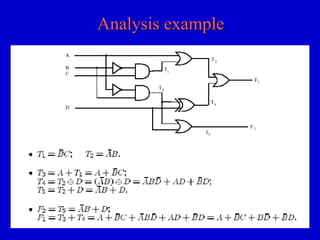

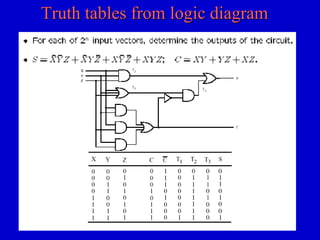

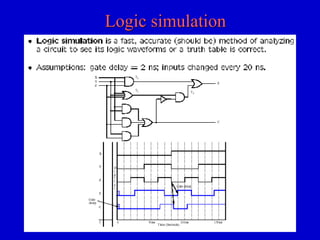

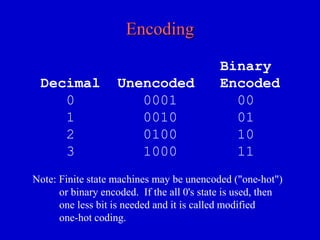

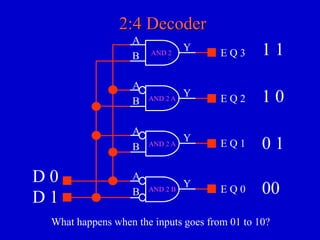

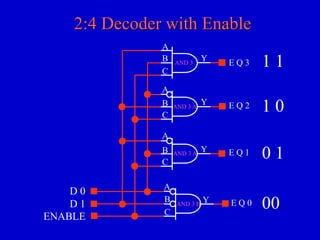

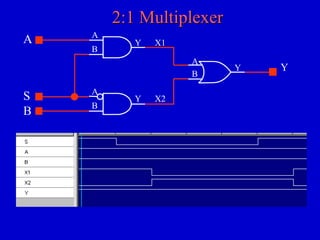

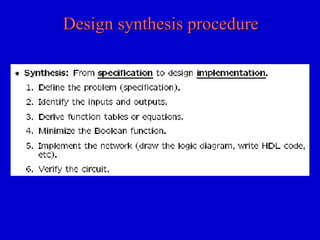

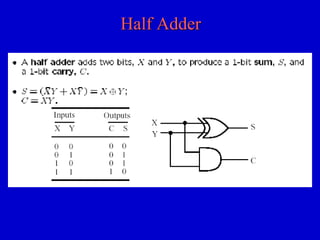

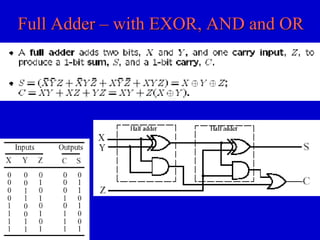

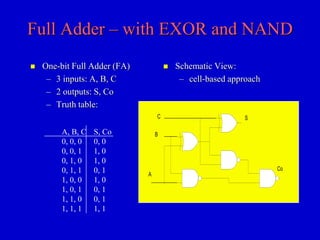

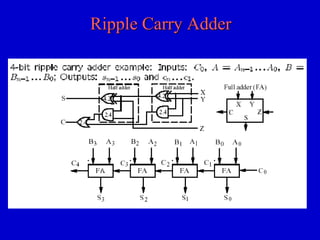

This document provides an overview of digital logic circuits and digital systems. It discusses binary logic, logic gates like NAND and NOR, Boolean algebra, decoders, adders, and the differences between analog and digital signals. It also covers representations of digital designs using truth tables, Boolean algebra, logic gate schematics, and logic simulations. Common logic gates, functions, identities, simplification techniques, and the duality principle of Boolean algebra are described.