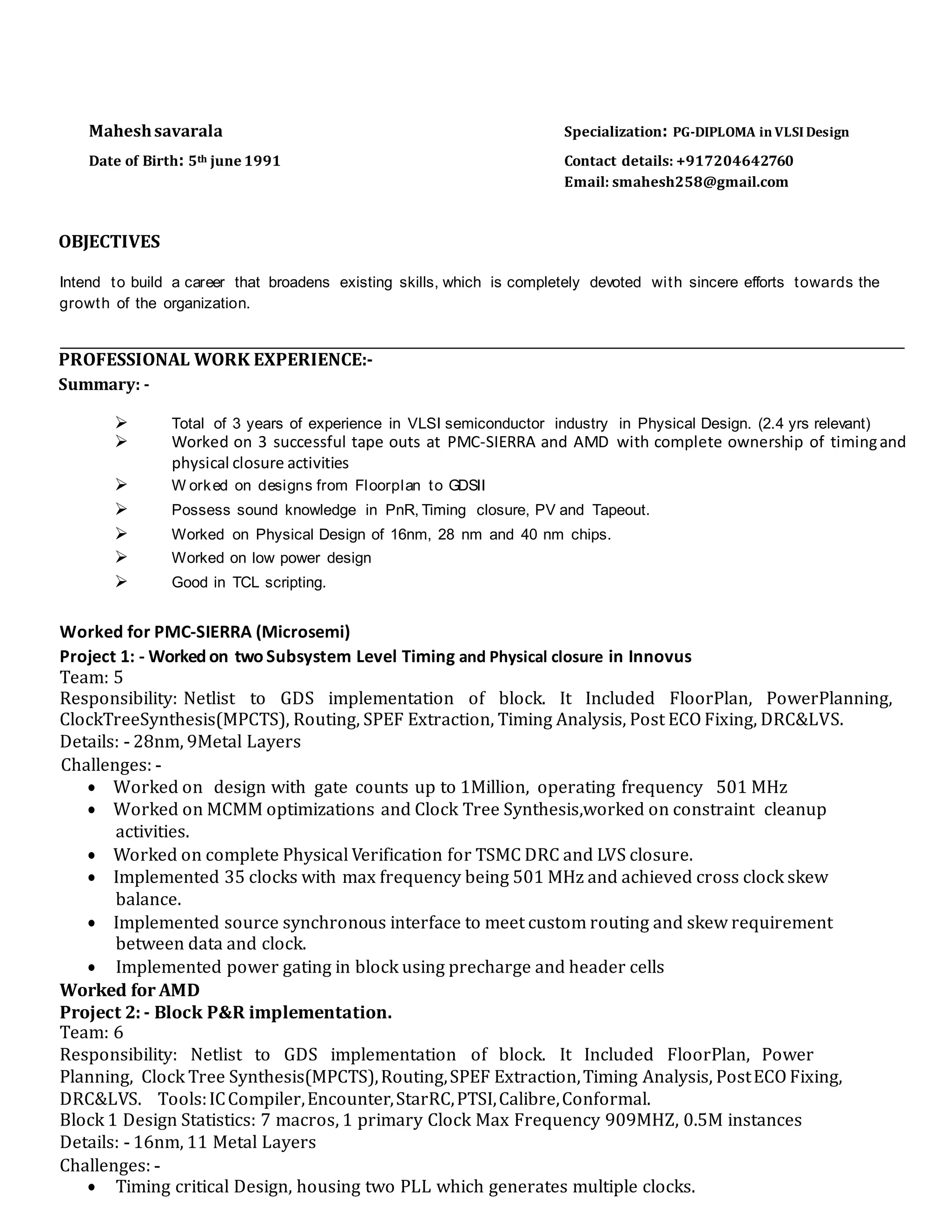

- Mahesh has over 3 years of experience in VLSI semiconductor industry in physical design. He has worked on designs from floorplanning to GDSII.

- He has worked on two successful tapeouts at PMC-Sierra and AMD with timing and physical closure activities. At PMC-Sierra, he implemented power gating and clock trees on 28nm chips.

- At AMD, he routed clocks and implemented shielding on a critical 16nm design with multiple clocks up to 909MHz.