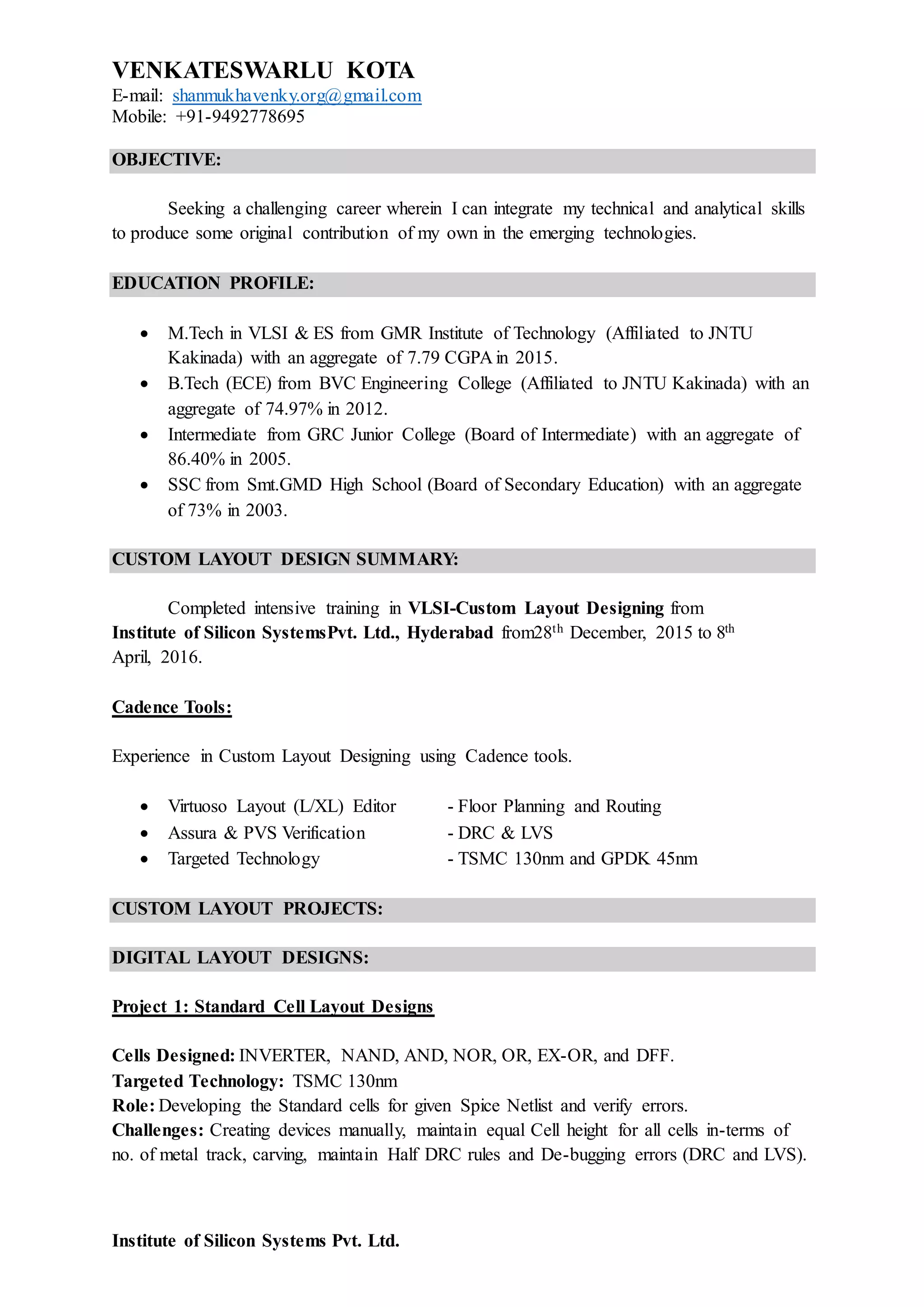

This document contains the resume of Venkateswarlu Kota. It summarizes his objective of seeking a challenging career in emerging technologies, and lists his educational qualifications including an M.Tech in VLSI & ES with a 7.79 CGPA and a B.Tech in ECE with 74.97%. It also outlines his custom layout design training and 6 digital and analog layout projects completed with challenges addressed for each. Finally, it provides details of an academic MIPS processor design project and personal details.