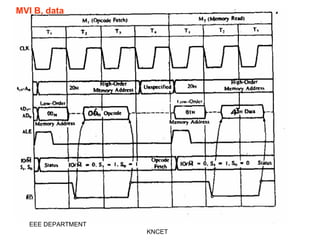

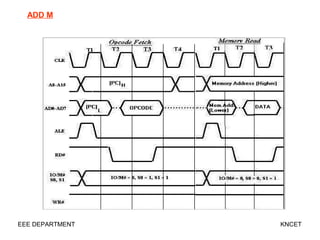

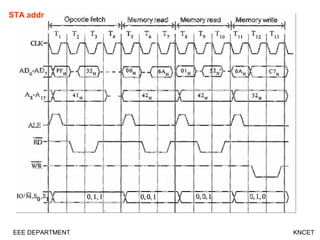

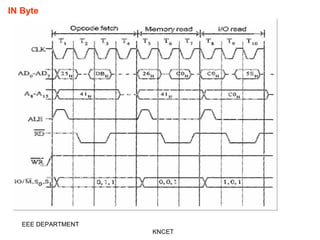

This document discusses machine cycles and timing diagrams in microprocessors. It focuses on the 8085 microprocessor. It describes that a machine cycle is the time required to access memory or input/output devices, while an instruction cycle is the time to execute an instruction. For the 8085, there are 5 basic machine cycles - opcode fetch, memory read, memory write, I/O read, and I/O write. Each takes a certain number of T-states. For example, the opcode fetch cycle takes 4 T-states to fetch the opcode from memory. The document provides details on the timing and signals involved in each type of machine cycle.