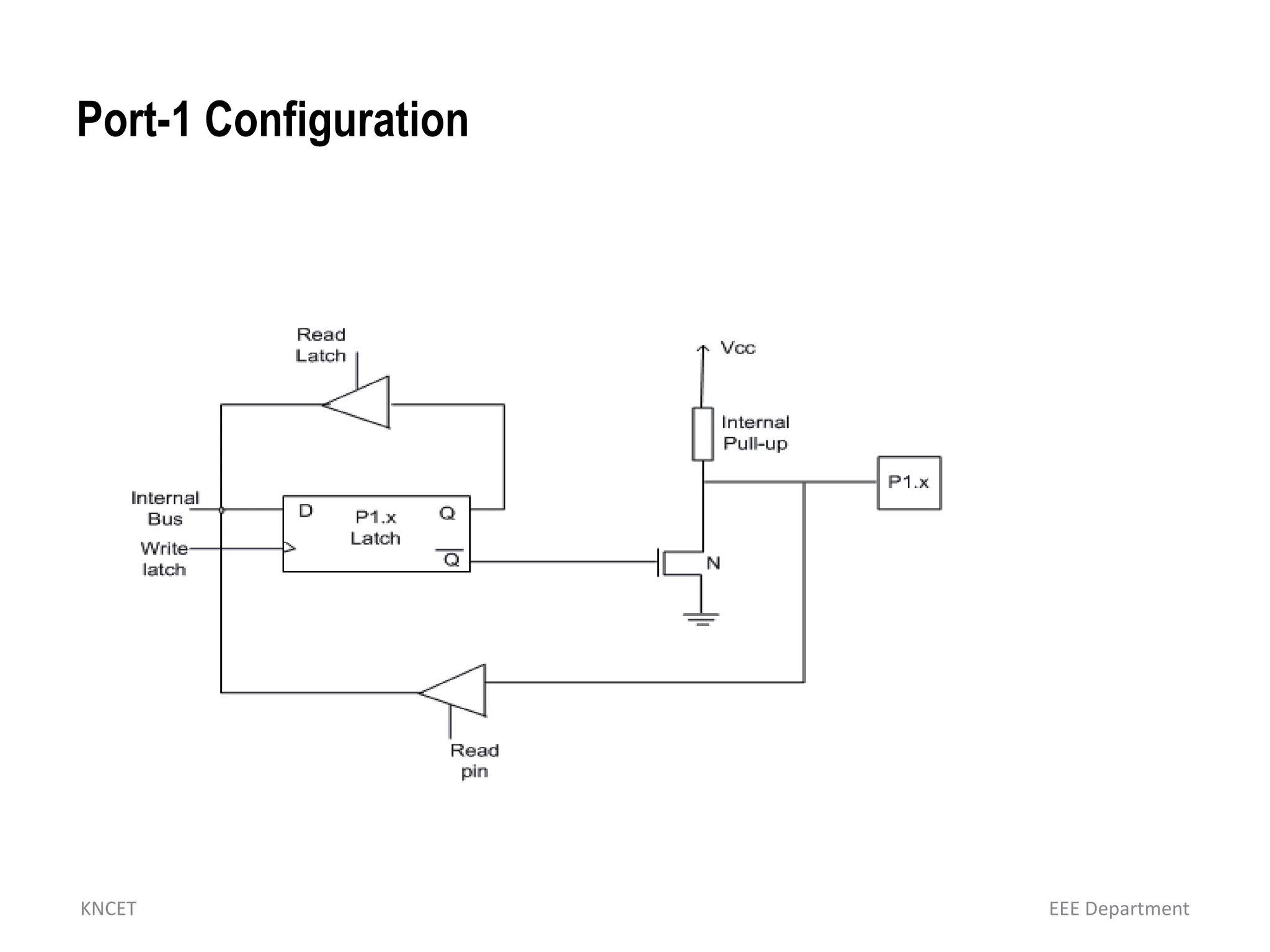

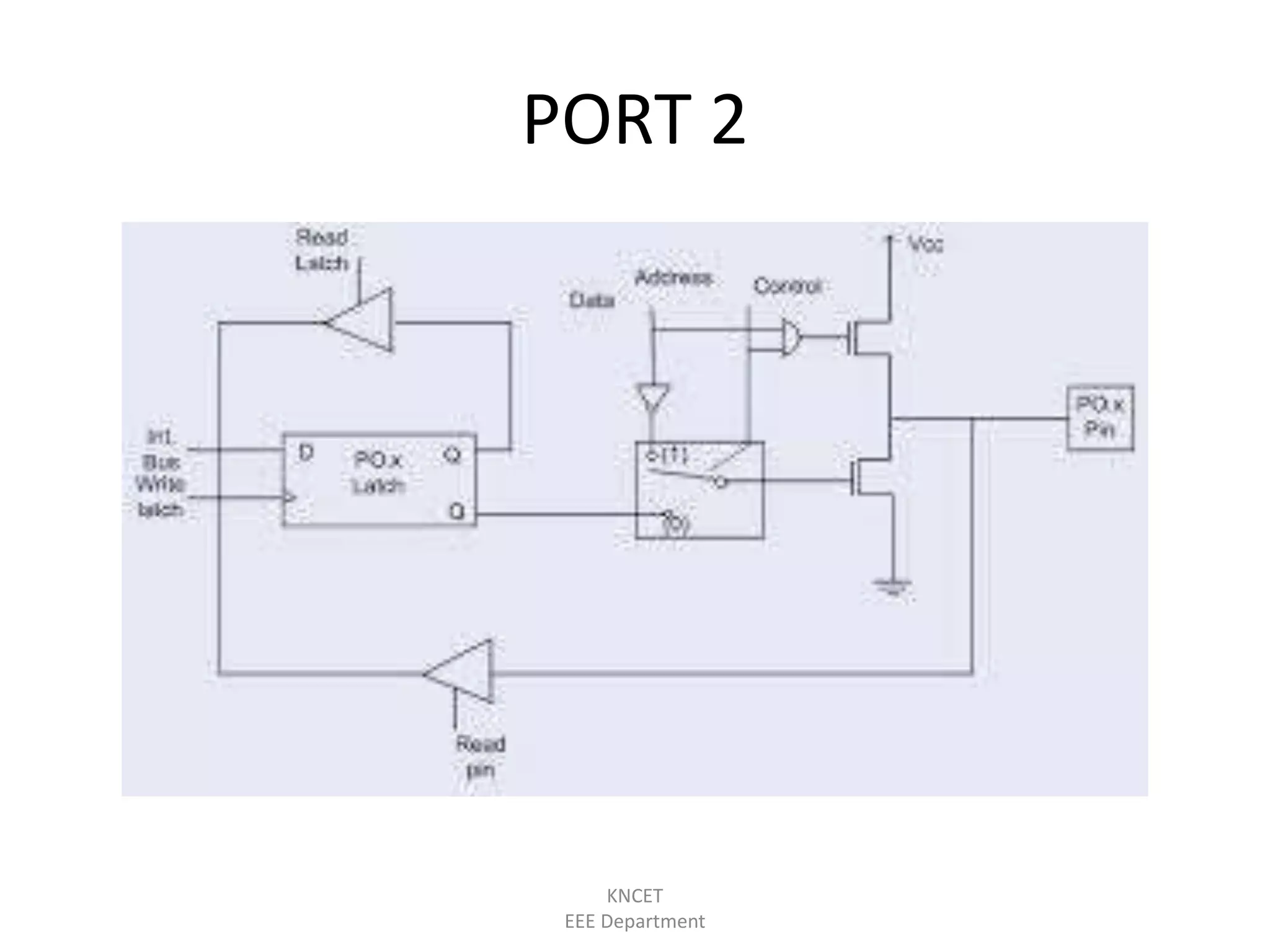

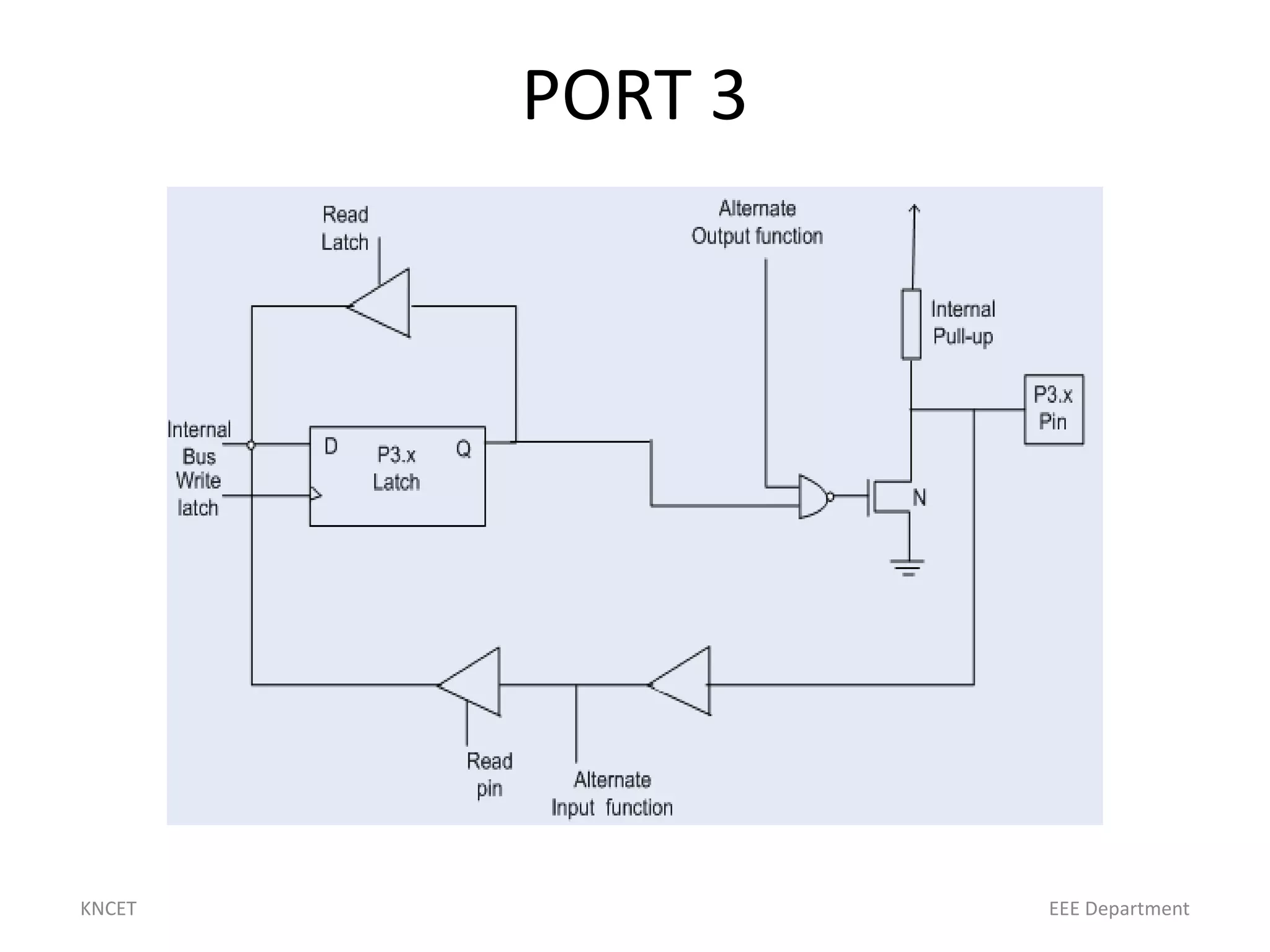

Port 1 of the 8051 microcontroller is a bidirectional I/O port with internal pull ups. It has 3 FETs that allow it to be used as either an input or output port. When used as an input, the logic level is loaded into a latch, turning off FET 1 and floating the pin. When used as an output, the latch value turns on or off FET 1 to either ground or drive the pin high. Port 2 is similar and can also be used for external memory addressing. Port 3 pins have alternate functions that are individually programmable under latch or SFR control.