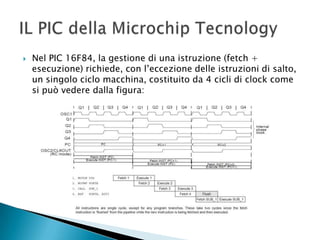

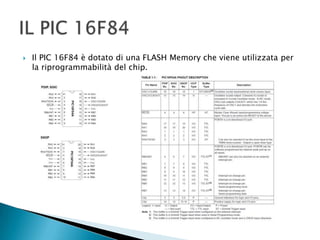

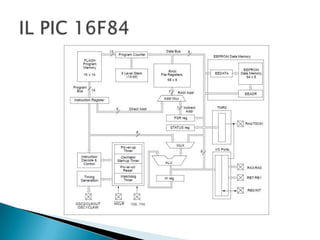

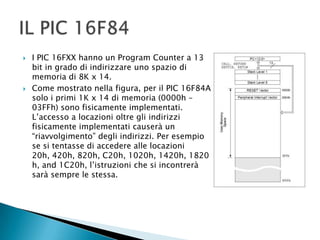

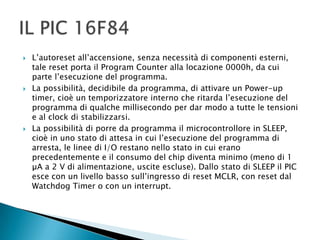

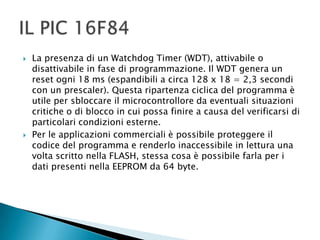

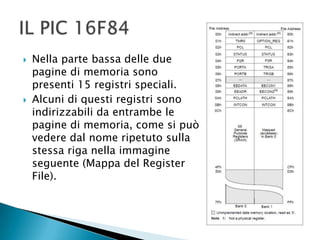

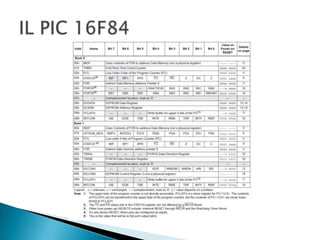

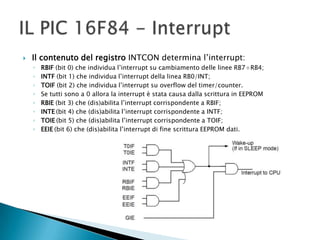

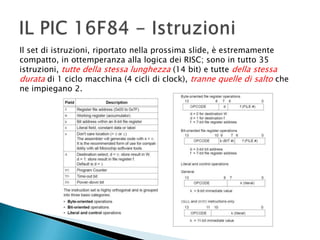

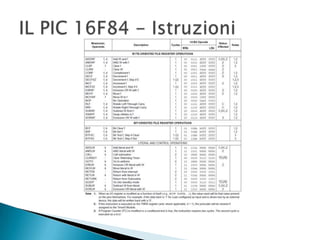

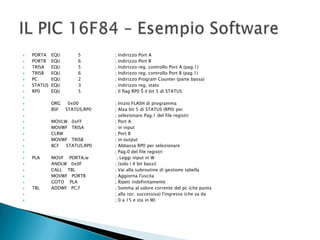

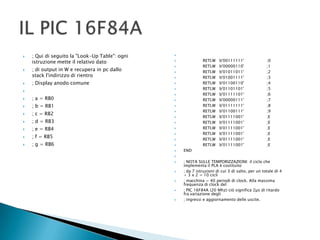

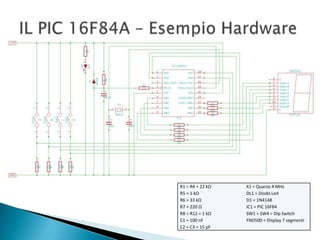

Il microcontrollore PIC 16F84 è un dispositivo a microprocessore integrato che include CPU, memoria, e periferiche I/O, progettato secondo un'architettura Harvard. Con un set ridotto di istruzioni e una memoria flash programmabile, offre vari vantaggi in termini di velocità ed efficienza. Inoltre, dispone di funzioni avanzate come sleep mode, watchdog timer e gestione di interruzioni, rendendolo adatto per applicazioni embedded.