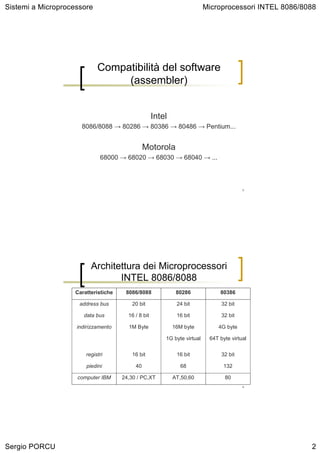

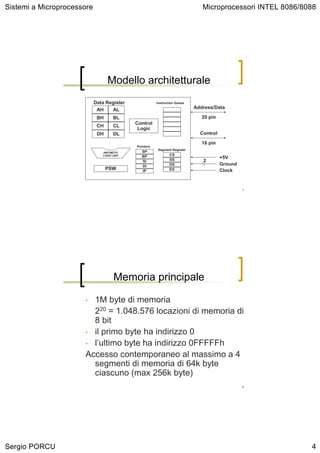

Il documento analizza l'architettura dei microprocessori Intel 8086/8088, evidenziando le loro caratteristiche tecniche come i bus di indirizzo e dati. Viene trattata la compatibilità con le versioni successive e la struttura dei registri, inclusi i registri di segmento e di stato. Si discute anche il funzionamento delle unità di esecuzione e interfaccia del bus, nonché la gestione della memoria e delle operazioni di I/O.