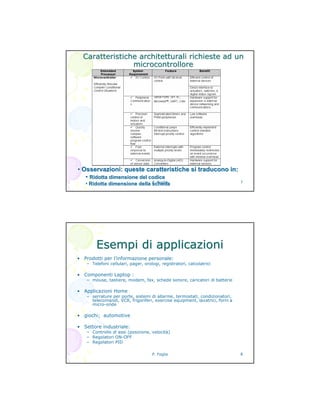

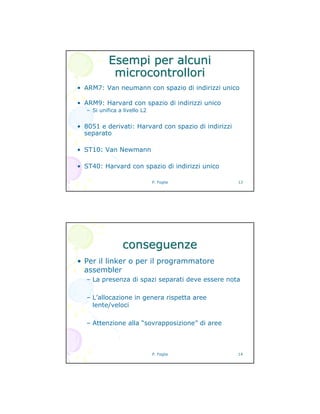

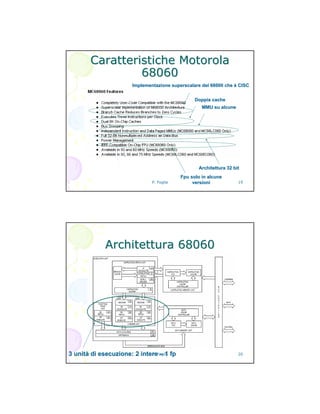

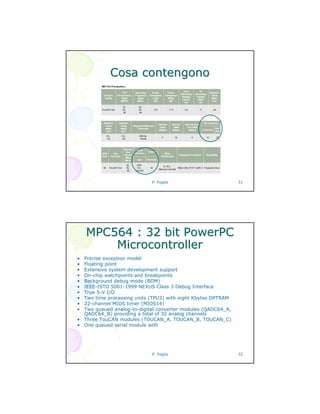

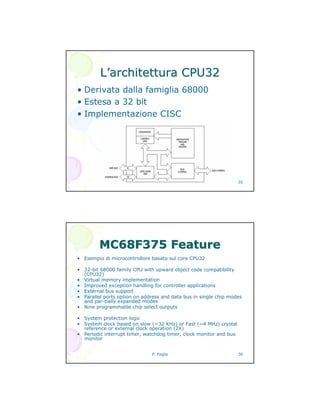

I microcontrollori costituiscono circa il 99% del mercato dei microprocessori, raggruppando CPU, memoria, porte I/O e altre funzionalità su un unico chip. Essi sono utilizzati in una vasta gamma di applicazioni, dalle automobili agli elettrodomestici, grazie ai loro vantaggi in termini di dimensioni, costi e consumo energetico. La loro architettura può essere basata su modelli CISC o RISC, influenzando prestazioni e consumo di potenza.