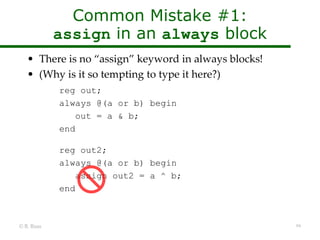

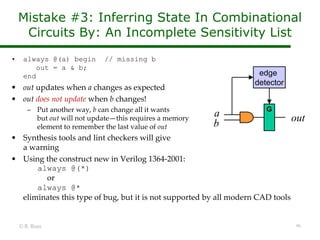

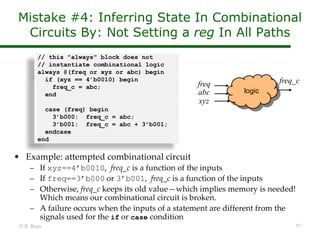

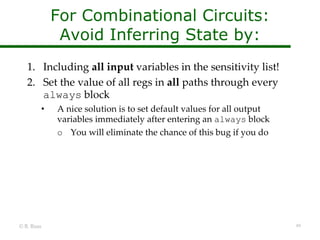

The document discusses common mistakes made when writing Verilog code. It describes 4 common mistakes: 1) Using the "assign" keyword in always blocks, 2) Setting the same reg in multiple always blocks, 3) Inferring state in combinational circuits by using an incomplete sensitivity list, and 4) Inferring state in combinational circuits by not setting a reg in all paths through an always block. The key to avoiding these mistakes is to include all input variables in the sensitivity list, and to set the value of all regs in all code paths within always blocks.