This document provides an introduction to SystemVerilog assertions in Japanese. It discusses what assertions are, the different types of assertions including concurrent and immediate assertions. It covers the SystemVerilog assertion checker library, how to write custom assertions, advanced assertion features like implication and repetition operators. It also provides examples of how to use assertions to check behaviors like interface protocols, temporal relationships and FSM operations.

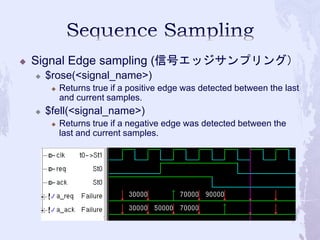

![ Sequence (シーケンス)

##t1, ##[t1:t2], ##[t1:$]

[*r1:r2], [->r1:r2], [=r1:r2]

and, or, throughout, intersect, within, first_match, |->, |=>

Function (ファンクション)

$rose, $fell, $stable

System (システム)

$isunknow, $info, $error, $warning, $fatal, $past, $countones,

$onehot, $onehot0

Keyword (キーワード)

bind, sequence, property, assert, not, ended, matched

endsequence, endproperty, assert property, cover property](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-11-320.jpg)

![ Verify Directives

assert, cover, bind,…

Property Operators

|->, |=>, disable iff, not,…

Sequence Operators

And, or, ##t, ##[t1:t2], …](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-12-320.jpg)

![ Specifying Delays

Fixed time

##1

##0: Special case used to joint two sequences

Time interval

##[1:3]

Open ended, eventually

##[1:$]: Next clock cycles to the end of simulation

The delay is in clock cycles, not nanoseconds](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-14-320.jpg)

![ How to use?

req ##2 ack

ack should be high two cycles after req

req ##2 ack ##3 !ack

ack will remain high for only 3 cycles

req ##2 ack ##3 !ack ##[1:3] $fell(done)

done falls 1 to 3 clocks after ack is removed](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-15-320.jpg)

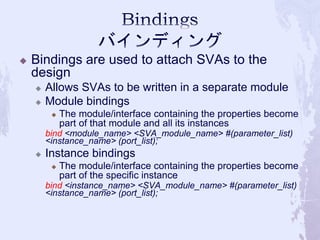

![ Bindings are easy way to use checker libraries

Verification engineers developing complex properties to verify

interfaces should write properties in a separate module/interface and

bind it to the design

module check_par(clk, parity, data);

input clk, parity; input [31:0] data;

property p_check_par;

@(posedge clk) ^(data^parity) == 1’b0;

endproperty

a_check_par: assert property(p_check_par);

endmodule

bind data_bus check_par a1(m_clk, m_parity, m_data);

bind top.mid.u1 check_par a2 (i_clk, i_parity, i_data);](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-31-320.jpg)

![ Sequence repetition operators

Consecutive repetition [*n]

Range repetition [*min:max]/ [*min:$]

Go to repetition [->n]

Non-consecutive repetition [=n]

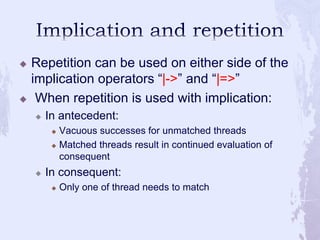

Implication and repetition

Repetition as an antecedent

Repetition as an consequence](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-33-320.jpg)

![ A[*1]: A ##1 A

A[*n]: A ##1 A ##1 A ##1 A …. ##1 A

A[*1:$]: A[*1], A[*2], A[*3], …

A[*min:max]

A[->1] (!A[*0:$] ##1 A)

A[->n] (!A[*0:$] ##1 A)[*n] A[->1][*n]

A[->1:3] A[->1] or A[->2] or A[->3]

A[->min:max] A[->min] or A[->(min+1)] or… A[->(max-

1)] or A[->max]

A[=1] (A[->1] ##1 !A[*0:$])

A[=n] (A[->n] ##1 !A[*0:$])](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-34-320.jpg)

![ Use the repetition operator to loop on a

sequence or Boolean expression

sequence [*n] // n = integer number of

iterations

There is an implicit ##1 between each loop

“ready asserted for 3 consecutive cycles”

ready ##1 ready ##1 ready

property p_ready_3;

@(posedge clk) ready[*3];

endproperty](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-35-320.jpg)

![ Same as consecutive but with an upper bound

sequence [*min:max]

Generates (max – min) + 1 threads

There is an implicit ##1 between each loop

“ ready repeated 1 to 3 times”

ready or ready ##1 ready or #ready ##1 ready ##1 ready

property p_ready_13;

@(posedge clk) ready[*1:3];

endproperty

A[*1:$]: A[*1], A[*2], A[*3], …

Upper bound $: the sequence repeats at least the number

of times specified by the lower bound.](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-36-320.jpg)

![ Non-consecutive exact repetition' operator for

Boolean expression

It checks if a Boolean expression has been true

for specified number of times but not necessarily

on consecutive clock cycles.

The sequence starts with the first occurrence of

the Boolean expression and ends with the last

A[->1] (!A[*0:$] ##1 A)

A[->n] (!A[*0:$] ##1 A)[*n] A[->1][*n]

A[->1:3] A[->1] or A[->2] or A[->3]

A[->min:max] A[->min] or A[->(min+1)] or… A[->(max-1)] or

A[->max]](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-37-320.jpg)

![ Similar to the [-> ] operator

When the ends with the last true value of

the operand, [= ] operation may extend

beyond such last true value.

A[=1] (A[->1] ##1 !A[*0:$])

A[=n] (A[->n] ##1 !A[*0:$])](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-38-320.jpg)

![property p_antecedent;

@(posedge clk) req[*3] |=> ack;

endproperty

property p_antecedent;

@(posedge clk) req[*1:3] |=> ack;

endproperty](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-40-320.jpg)

![property p_consequence;

@(posedge clk) $rose(gnt) |-> ack[*2:3] ##1 !ack;

endproperty](https://image.slidesharecdn.com/systemverilogassertion-221006041311-342f9875/85/SystemVerilog-Assertion-pptx-41-320.jpg)