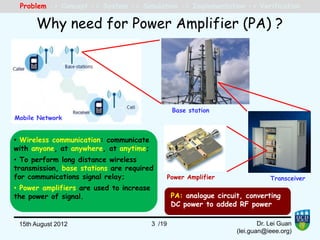

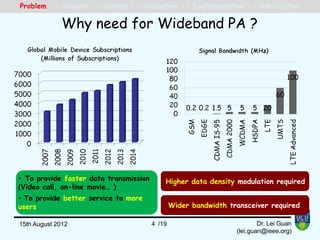

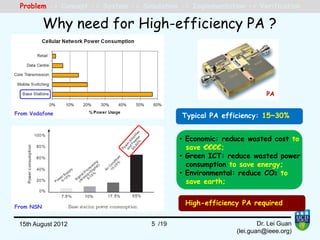

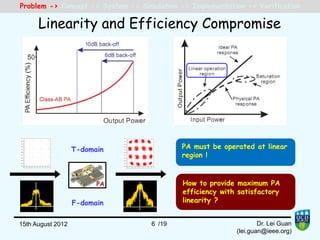

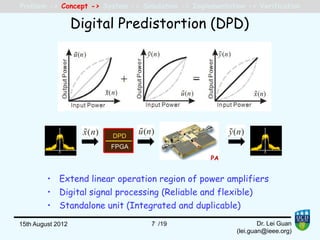

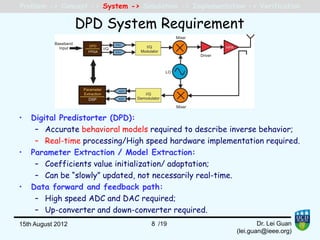

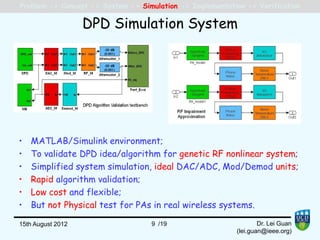

The document discusses the importance of high-performance digital predistortion (DPD) for wideband RF power amplifiers, focusing on the need for linearity and efficiency to enhance signal transmission in mobile networks. It outlines the challenges and solutions for implementing DPD systems, including simulation, hardware requirements, and validation procedures. The paper also highlights DPD's effectiveness in compensating for nonlinear distortion in various electronic systems.

![Low-cost DPD Implementation

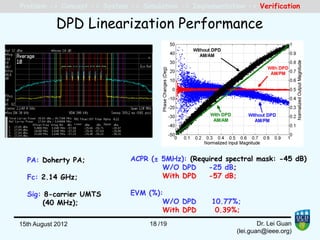

1. LUT-assisted Gain Indexing:

Memory is much cheaper than hardware multipliers

2. TDM-based Multiplier Sharing:

FPGA clock is faster than required data rate

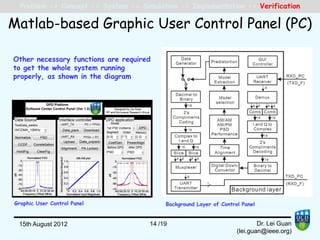

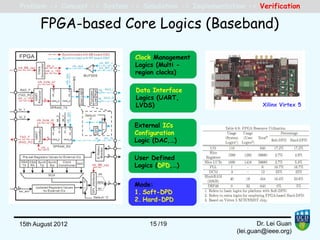

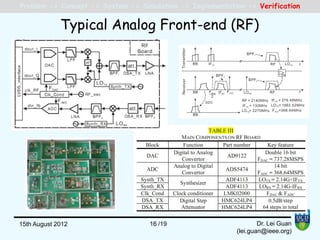

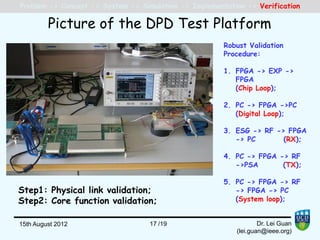

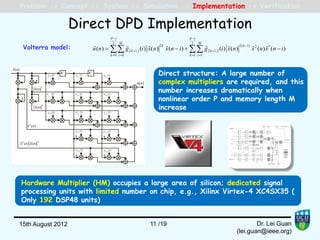

Problem -> Concept -> System -> Simulation -> Implementation -> Verification

1 1

2 2

2 2( 1) 2 *

2 1,1 2 1,2

0 0 1 1

( ) ( ) ( ) ( ) ( ) ( ) ( ) ( )

P P

M M

k k

k k

k i k i

u n g i x n x n i g i x n x n x n i

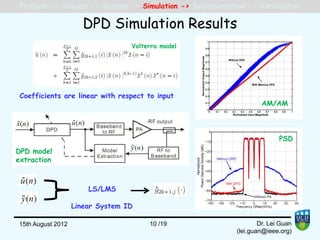

Volterra model:

/1915th August 2012 12

[L. Guan, WO 2010/136114 A1]

Dr. Lei Guan

(lei.guan@ieee.org)](https://image.slidesharecdn.com/highperformancedigitalpredistortionforwidebandrfpoweramplifiers-151221220607/85/High-performance-digital-predistortion-for-wideband-RF-power-amplifiers-12-320.jpg)

![DPD Validation Platform Design

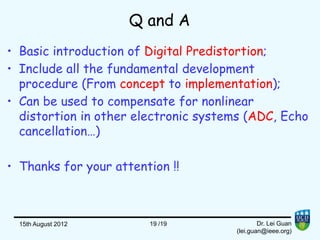

Problem -> Concept -> System -> Simulation -> Implementation -> Verification

• Practicability: Focus on Fundamental units

• Flexibility: 2-Mode DPD (soft & Hard)

Hardware (e.g., FPGA) + Software (e.g., Matlab)

• Expandability: Design each function independently

• Practicability: Focus on Fundamental units

• Flexibility: 2-Mode DPD (soft & Hard)

Hardware (e.g., FPGA) + Software (e.g., Matlab)

• Expandability: Design each function independently

/1915th August 2012 13

[L. Guan, et al., EI project report]

Dr. Lei Guan

(lei.guan@ieee.org)](https://image.slidesharecdn.com/highperformancedigitalpredistortionforwidebandrfpoweramplifiers-151221220607/85/High-performance-digital-predistortion-for-wideband-RF-power-amplifiers-13-320.jpg)