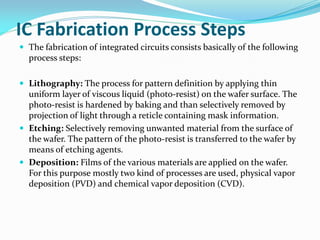

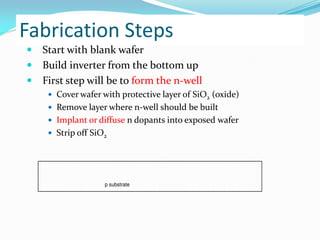

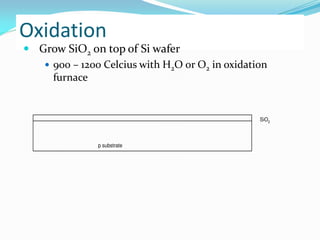

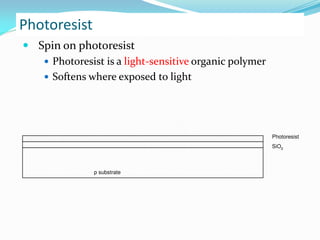

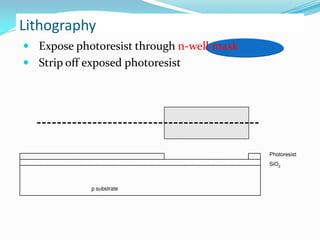

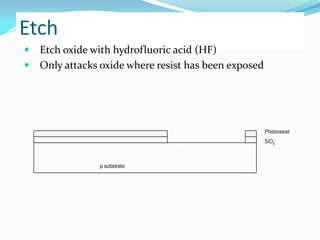

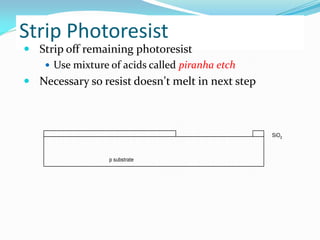

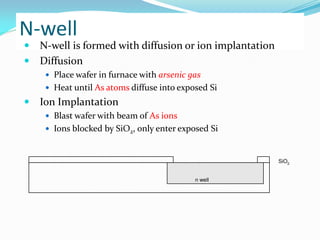

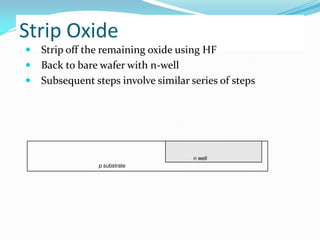

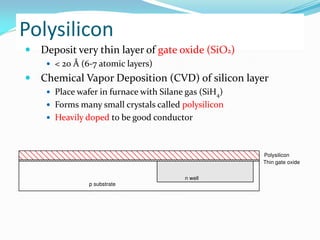

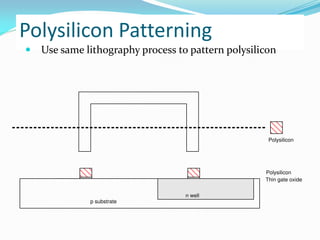

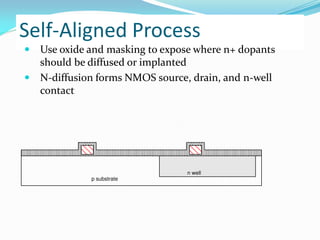

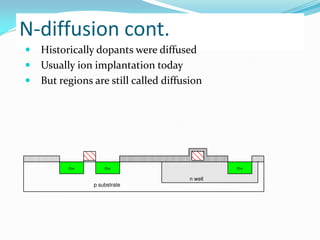

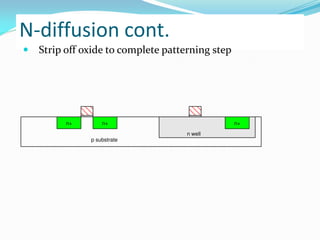

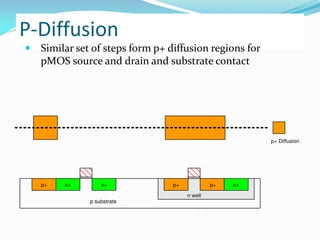

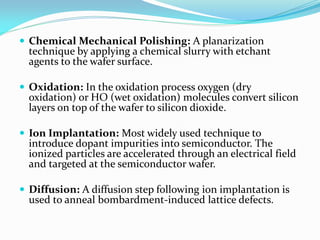

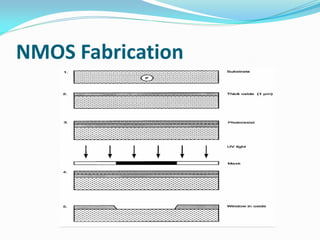

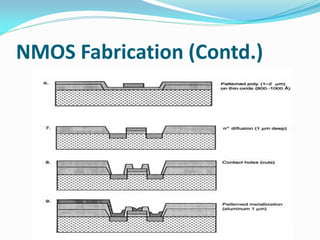

The fabrication process of integrated circuits involves key steps of lithography, etching, and deposition. Lithography uses photo-resist to define patterns on the wafer which are then transferred via etching. Deposition is used to apply thin films of various materials. The fabrication of an NMOS transistor similarly involves patterning via lithography and etching, deposition of thin films like oxide and polysilicon, and doping via diffusion or implantation to form the transistor components in sequence from the substrate up.